Author: Браммер Ю.А. Пащук И.Н.

Tags: электротехника импульсные устройства цифровая электроника

ISBN: 5-06-004354-1

Year: 2003

Text

Ю.А. БРАММЕР

И.Н. F1ALUVK

Zy\bCJ-JbJE

УДК 621.374

ББК 32.847

Б87

Рецензент — В.В. Морозов, преподаватель Московского

техникума автоматики и телемеханики

Браммер, Ю.А.

Б87 Импульсные и цифровые устройства: Учеб, для студен-

тов электрорадиоприборостроительных сред. спец. учеб, за-

ведений/Ю. А. Браммер, И.Н. Пащук — 7-е изд., перераб.

и доп. — М.: Высш, шк., 2003. — 351 с.: ил.

ISBN 5-06-004354-1

В книге описываются импульсные и цифровые сигналы, современная

элементная база импульсных и цифровых устройств, формирователи, уси-

лители и генераторы импульсов, триггеры, цифровые функциональные

узлы и устройства.

Седьмое издание (6-е -— 2002 г.) дополнено новым материалом по

цифровой технике, цифровым узлам и устройствам.

Для студентов электрорадиоприборостроительных средних специаль-

ных учебных заведений.

УДК 621.374

ББК 32.847

ISBN 5-06-004354-1 © ФГУП «Издательство «Высшая школа», 2003

Оригинал-макет данного издания является собственностью издательст-

ва «Высшая школа», и его репродуцирование (воспроизведение) любым

способом без согласия издательства запрещается.

ПРЕДИСЛОВИЕ

В книге изложены основы современной импульсной и циф-

ровой техники.

Книга состоит из введения и девяти глав. В гл. 1 рассматрива-

ются параметры и спектры импульсов, структуры импульсных

и цифровых сигналов, а также основные соотношения алгебры

логики, приемы составления логических функций и их минимиза-

ция.

В гл. 2 описываются усилители импульсов на транзисторах

и в интегральном исполнении; рассматриваются искажение ими

формы импульсов и коррекция этих искажений, типовые каскады

и специфика структуры интегральных усилителей. Завершается

данная глава описанием различных типов ключей на биполярных

и полевых транзисторах.

В гл. 3 рассматривается элементная база импульсных и циф-

ровых устройств. Здесь описываются структура микросхем опе-

рационных усилителей и компараторов, основные схемы их вклю-

чения и параметры, структура базовых логических элементов

разных классов, их параметры и сравнительные характеристики.

В гл. 4 излагаются дифференциаторы, интеграторы и ограни-

чители амплитуды, реализованные на пассивных элементах и на

микросхемах операционных усилителей, а также формирователи

импульсов на линиях и на логических элементах.

В гл. 5 рассматриваются генераторы прямоугольных импуль-

сов: транзисторные и интегральные мультивибраторы в различ-

ных режимах, мультивибраторы на логических элементах и мик-

росхемах операционных усилителей, блокинг-генераторы на

транзисторах и специализированных микросхемах.

В гл. 6 описываются генераторы пилообразного напряжения

и тока разных типов на транзисторах, микросхемах операцион-

ных усилителей и на специализированных микросхемах.

В гл. 7 рассматриваются транзисторные триггеры, а также

различные типы триггеров на логических элементах и в микро-

схемном исполнении.

В гл. 8 описываются выполненные на микросхемах узлы

цифровых и импульсных устройств: различного типа счетчики

импульсов и регистры, дешифраторы и шифраторы, распредели-

тели и коммутаторы, цифровые компараторы, аналого-цифровые

и цифроаналоговые преобразователи, полупроводниковые запо-

минающие устройства, сумматоры и таймеры.

В гл. 9 приводятся примеры цифровых и импульсных

устройств. Здесь описываются преобразователи кодов, цифровая

индикация, электронные часы, цифровой вольтметр, запомина-

ющее устройство микропроцессорной системы, символьный дис-

плей, селекторы импульсов и некоторые другие устройства.

Учебник содержит примеры, способствующие углубленному

изучению материала. Одни из них — числовая иллюстрация при-

веденных соотношений, другие имеют самостоятельное значение

и, в частности, ставят цель продемонстрировать приемы решения

некоторых практических задач.

Материал учебника соответствует программам ряда специ-

альностей. Поэтому его содержание может несколько выходить

за рамки каждой из них.

Авторы признательны рецензенту В. В. Морозову, преподава-

телю Московского техникума автоматики и телемеханики, за

ценные замечания. Пожелания по книге просим направлять по

адресу: 101430, Москва, ГСП-4, Неглинная ул., 29/14, издательст-

во «Высшая школа».

Авторы

ВВЕДЕНИЕ

В импульсной технике используются кратковременные преры-

вистые электрические колебания. Она является составной частью

радиоэлектроники и служит, в частности, базой радиолокации,

радионавигации, телевидения, многоканальной связи. На основе

импульсной техники созданы электронные цифровые вычисли-

тельные машины.

Рассмотрим кратко перечисленные области использования

импульсной техники.

Импульсная радиолокационная станция излучает кратковре-

менные электромагнитные колебания (радиоимпульсы), которые

отражаются от цели и принимаются той же станцией. По време-

ни распространения каждого радиоимпульса до цели и обратно

(с учетом известной скорости распространения радиоволн) опре-

деляют дальность цепи. Аналогично измеряется высота полета

самолета, облачного покрова и т. д. Радиолокация широко ис-

пользуется в системах навигации кораблей и летательных ап-

паратов, в радиоастрономии, при освоении космического про-

странства.

При телевизионных передачах изображение на экране прием-

ной трубки формируется, как известно, построчно (подобно то-

му, как глаз человека пробегает страницу книги). Чтобы на

строках экрана телевизора изображение размещалось аналогично

тому, как оно размещается по «строкам» передаваемого пред-

мета (и на специальном электроде передающей трубки), в телеви-

зионном сигнале присутствуют, в частности, синхронизирующие

импульсы. Только благодаря этому совпадают положения строк

изображения на приемной и передающей сторонах тракта.

Радиолокационная и телевизионная аппаратура содержит уз-

лы, вырабатывающие импульсы различной формы.

Прерывистость импульсных колебаний дает возможность осу-

ществить многоканальную связь. Используя один канал, импуль-

сы, передающие одно сообщение, размещаются в паузах между

импульсами, передающими другое сообщение.

Перечень областей науки, техники и производства, где эффек-

тивно используются импульсные методы, можно продолжить.

К ним относятся управление на расстоянии (телеуправление),

измерения электрических и неэлектрических величин, облада-

ющая скрытностью и помехозащищенностью кодированная ра-

диосвязь, промышленная автоматика и т. д.

В последние десятилетия импульсная техника обогатилась

новой быстро развивающейся областью — цифровой техни-

кой — основой электронных цифровых вычислительных машин,

станков с числовым программным управлением, роботов и т. д.

Она подняла на новую качественную ступень средства связи,

радиолокацию, вызвала появление автоматизированных систем

управления предприятиями и целыми отраслями народного хо-

зяйства, комплексов для обработки различных видов информа-

ции. Этому в немалой степени способствовало создание новой

элементной базы, что привело к резкому снижению габаритов

и массы импульсных устройств.

Своему становлению и развитию импульсная техника обязана

трудам специалистов многих стран мира, среди которых значи-

тельная роль принадлежит отечественным ученым.

Впервые импульсные методы были использованы изобрета-

телем телеграфа — нашим соотечественником П. Л. Шиллин-

гом. Импульсный искровой передатчик сконструировал в 1895 г.

изобретатель радио А. С. Попов. В 1907 г. Л. И. Мандельштам

(впоследствии известный советский академик) разработал

принцип получения временного масштаба, что нашло примене-

ние в осциллографах при наблюдении кратковременных импульс-

ных процессов. В этом же году профессор Б. Л. Розинг впервые

использовал электронно-лучевую трубку для приема изображе-

ния, что обусловило развитие электронного телевидения.

В 1918 г. научный руководитель Нижегородской радиолаборато-

рии М. А. Бонч-Бруевич (впоследствии член-корреспондент Ака-

демии наук СССР, автор многочисленных изобретений и печат-

ных работ) создал и проанализировал устройство, послужившее

основой импульсных схем — триггеров и мультивибраторов.

В 30-х годах М. А. Бонч-Бруевич, Д. Е. Маляров, К. И. Кры-

лов, В. П. Илясов создали магнетрон — прибор для генерации

электромагнитных колебаний сверхвысоких частот, сыгравший

огромное значение в совершенствовании радиолокаторов.

К тем же годам относятся работы советских ученых

С. И. Катаева, Г. В. Брауде, Г. В. Тимофеева, Д. А. Черныше-

ва, П. В. Шмакова, заложившие основы современного телевиде-

ния.

В 1931 г. В. А. Котельников сформулировал и доказал те-

орему, ставшую фундаментальным положением импульсной эле-

ктро- и радиосвязи.

В 1934 г. П. К. Ощепковым была начата разработка импульс-

ной радиолокации, в 1937 г. Ю. Б. Кобзаревым и его сотруд-

никами создана локационная станция, в которой использовался

импульсный режим работы.

Разработка теории импульсных колебаний и переходных про-

цессов в радиотехнических цепях связана с именами советских

ученых во главе с Л. И. Мандельштамом и Н. Д. Папалекси.

6

Труды А. А. Андронова, А. А. Витта, И. С. Гоноровского,

С. И. Евтянова, Я. С. Ицхоки, Н. Н. Крылова, В. И. Сифорова,

А. А. Харкевича и многих других советских ученых послужили

теоретической базой для создания импульсных и цифровых

устройств.

В ближайшие годы еще шире будут развиваться многопрог-

раммное телевидение, радиовещание и телефонная связь через

искусственные спутники Земли, радиолокационные системы, вы-

числительная техника, средства и системы сбора, передачи и об-

работки информации, робототехника, системы автоматического

управления с использованием микропроцессоров, будут продол-

жаться работы по формированию единой автоматизированной

системы связи страны.

Развитие этих областей связано с дальнейшим совершенст-

вованием импульсной и цифровой техники и подготовкой квали-

фицированных кадров радиоспециалистов.

ГЛАВА 1

СИГНАЛЫ ИМПУЛЬСНЫХ И ЦИФРОВЫХ УСТРОЙСТВ

§ 1.1. ОБЩИЕ СВЕДЕНИЯ

Сигналом называют физический процесс, несущий информа-

цию. Сигналы могут быть звуковыми, световыми, электричес-

кими.

Информация сосредоточена в изменениях параметров физи-

ческого процесса. Если параметры процесса не меняются, то он

не является сигналом. Так, неизменные звук, световой поток,

синусоидальное электрическое колебание никакого сообщения не

содержат. Наоборот, в изменениях громкости и тона звука, ярко-

сти и цвета светового излучения, амплитуды, частоты и фазы

электрического колебания запечатлена информация. Информа-

тивным является также появление или окончание, например,

электрического колебания, т. е. его изменения.

Сигналы на выходе микрофона, передающей телекамеры, раз-

личного рода датчиков аналогичны по своему «рисунку» воздей-

ствиям на эти устройства — звуковому давлению, распределе-

нию освещенности, температуре и т. д. Поэтому подобные сиг-

налы называют аналоговыми. Между минимальным и мак-

симальным значениями аналоговый сигнал может иметь любое

значение. Обычно аналоговые сигналы являются непрерывными.

Устройства, в которых действуют такие сигналы, называют ана-

логовыми.

Расстояние, на которое передается электрический сигнал, мо-

жет быть как весьма малым (в пределах устройства), так и чре-

звычайно большим (например, при исследовании космического

пространства).

Скорость распространения электрических сигналов близка

скорости света, что и обусловило их широкое применение в раз-

личных областях техники.

По проводам электрические сигналы могут передаваться

в том виде, в каком они снимаются с источника. При передаче

сигнала через открытое пространство сигналом модулируют вы-

сокочастотное колебание, за счет чего обеспечиваются эффектив-

ные излучение и прием.

Информация, которую переносит сигнал, может являться со-

общением о событии, о режиме технологического процесса, пред-

8

Т 1 г i Т

г) 3) е)

Рис. 1.1

ставлять команду на включение или выключение какой-либо

аппаратуры и т. д. Выражается информация различным обра-

зом, в частности, речью, изображением, звуком, электрическим

колебанием.

§ 1.2. СИГНАЛЫ ИМПУЛЬСНЫХ УСТРОЙСТВ

Под электрическим импульсом понимают отклонение на-

пряжения или тока от некоторого постоянного уровня (в частно-

сти, от нулевого), наблюдаемое в течение времени, меньшего или

сравнимого с длительностью переходных процессов в схеме.

Существует два вида импульсов: видеоимпульсы* и радиоим-

пульсы.

Видеоимпульсы получают при коммутации цепи постоян-

ного тока. Наиболее часто используют видеоимпульсы прямо-

угольной (рис. 1.1, а), трапецеидальной (рис. 1.1, б), экспоненци-

альной (остроконечной) (рис. 1.1, в), пилообразной (рис. 1.1, г)

и треугольной (рис. 1.1, д) форм. Различают видеоимпульсы

положительной (рис. 1.1, а, б, г, д) и отрицательной (рис. 1.1, в)

полярности, а также двусторонние — разнополярные — импуль-

сы (рис. 1.1, е). Следует иметь в виду, что реальные импульсы не

имеют формы, строго соответствующей названию.

Радиоимпульсы (рис. 1.2) представляют собой кратковре-

менные посылки синусоидального напряжения или тока. Они

снимаются с выхода высокочастотного генератора, который

Управляется (модулируется) видеоимпульсами. Поэтому форма

огибающей радиоимпульсов соответствует форме модулирую-

щих видеоимпульсов. Радиоимпульсы (рис. 1.2) — результат мо-

дуляции амплитуды высокочастотного колебания прямоуголь-

выми видеоимпульсами.

*Свое название видеоимпульсы получили из телевидения, где они широко

используются.

9

Рис. 1.2 Рис. 1.3

Импульсное колебание, параметры которого изменяются в

соответствии с передаваемой информацией, является сигналом.

Такой сигнал относят к аналоговым, так как в диапазоне своих

изменений он может принимать любое значение. Устройства, в

которых действуют электрические импульсы, называют импульс-

ными.

Параметры импульсов. Введем понятие об основных парамет-

рах импульсов на примере реального прямоугольного импульса

(рис. 1.3).

Длительность. За активную длительность импульса /„ а

принимают промежуток времени, измеренный на уровне, соот-

ветствующем половине амплитуды. Иногда длительность им-

пульсов определяют на уровне 0,1 Um (0,11т) или по основанию

импульса. В дальнейшем, если это не оговорено, длительность

импульса будет определяться по основанию и обозначаться

/и (см. рис. 1.1, а).

ДлительнЬсть импульса выражается в единицах времени: се-

кундах (с), миллисекундах (мс), микросекундах (мкс) и наносекун-

дах (нс)*.

Амплитуда. Наибольшее значение напряжения или тока им-

пульса данной формы является его амплитудой. Амплитуда им-

пульса Um (1т) выражается в вольтах (В), киловольтах (кВ), мил-

ливольтах (мВ), микровольтах (мкВ) или амперах (А), миллиам-

перах (мА), микроамперах (мкА).

Длительность и крутизна фронта импульса. Импульс

имеет передний фронт и срез, последний также называют за-

дним фронтом.

Длительность переднего фронта импульса определяется вре-

менем нарастания импульса, а длительность среза — временем

спада импульса.

Наиболее часто пользуются понятием активной длительности

фронта /ф, за которую принимают время нарастания импульса от

0,1(7„ до 0,9 Um; аналогично, длительность среза tc — время спада

импульса от 0,9 Um до 0,1 Um (рис. 1.3).

*1ж=10-9с.

Обычно длительность /ф и tc составляет единицы процентов от

длительности импульса. Чем меньше /ф и tc по сравнению с tu, тем

больше форма импульса приближается к прямоугольной. Иногда

вместо 1ф и tc фронты импульса характеризуют скоростью нарас-

тания (спада). Эту величину называют крутизной 5 фронта

(среза) и выражают в вольтах в секунду (В/с), киловольтах в се-

кунду (кВ/с) и т. д. Для прямоугольного импульса приближенно

5= ит/(ф.

Участок импульса (рис. 1.3) между фронтами называют плос-

кой вершиной. На рисунке показан спад плоской вершины (ACT),

а также отрицательный выброс.

Мощность в импульсе. Энергия W импульса, отнесенная

к его длительности, определяет мощность в импульсе: Ри= №/(я.

Она выражается в ваттах (Вт), киловаттах (кВт).

Период повторения импульсов. Импульсы, повторяю-

щиеся через разные промежутки времени, образуют периодичес-

кую последовательность. Промежуток времени между началом

двух соседних однополярных импульсов (см. рис. 1.1) называют

периодом повторения (следования) импульсов. Он выражается

в единицах времени: с, мс, мкс.

Величину, обратную периоду повторения, называют частотой

повторения (следования) импульсов f Она определяет количество

периодов в течение 1 с и выражается в герцах (Гц), килогерцах

(кГц) и т. д.

Коэффициент заполнения. Часть периода Т занимает па-

уза — отрезок времени между окончанием и началом двух сосед-

них импульсов (см. рис. 1.1, а), т. е. tK=T—t„.

Отношение длительности импульса к периоду повторения

называют коэффициентом заполнения: y — t^T. Коэффици-

ент заполнения — величина безразмерная, меньшая единицы.

Величину, обратную коэффициенту заполнения, называют

скважностью импульсов: <у = 1/у = 77/и

Скважность тоже безразмерная величина, но большая едини-

цы. Например, для последовательности импульсов на рис. 1.1, е

9=2.

Среднее значение импульсного колебания. При опре-

делении среднего за период значения импульсного колебания

^ч> (Л-р) импульс напряжения или тока распределяют равномерно

на весь период так, чтобы площадь прямоугольника 1^ Т (рис. 1.4) была

равна площади импульса 5И.

Так, для прямоугольного импульса

>>и=/т/и и = Imt^ T=Imy = Im]q, т. е.

среднее значение тока (напряжения)

прямоугольного импульсного колеба-

пия в q раз меньше амплитудного.

Средняя мощность. Энергия W

Рис. 1.4

импульса, отнесенная к периоду Т, определяет среднюю мощ-

ность импульса: P^WjT.

Сравнивая выражения Ри и Р^, получим

РЯ^ = Р^Т, Pa=PepT/ta=Pepq и Рср=Р^и/7’=Ри/?,

т. е. средняя мощность и мощность в импульсе отличаются в q раз.

Отсюда следует, что мощность в импульсе, которую обес-

печивает генератор, может в q раз превосходить среднюю мощ-

ность генератора.

Пример 1.1. Пусть генератор со средней мощностью 7^=20 Вт вырабаты-

вает импульсы длительностью )и=1 мкс с частотой следования /=2 кГц. Тогда

Т=1//=1/(2 103) = 0,5 10'3=500 мкс; ?=Т/ги = 500 10"6/(1 10'6) = 500; Ри =

= Реп? = 20'500 = 10 000 Вт=10 кВт.

Элементы цепи, по которым должна пройти эта импульсная последователь-

ность, можно выбирать по средней мощности Р^, которая много меньше мощ-

ности в импульсе Ря.

Спектр периодической импульсной последовательности. Извест-

но, что периодическое несинусоидальное колебание можно пред-

ставить бесконечным тригонометрическим рядом Фурье, кото-

рый в общем случае содержит постоянную и гармонические

составляющие.

Результат воздействия на схему каждой составляющей опре-

деляется сравнительно просто. Пользуясь принципом наложения,

можно действие импульса на линейную цепь заменить суммар-

ным действием всех его составляющих.

Часто используется следующая форма математической запи-

си ряда Фурье:

f (t) = A0/2 + Ai cosa)it+A2cos2соа + ... +

+ Ап cos neoit + .Bi sin ct)i t +

+ Д sin 20V+ ... + /?„ sin ncolt + ...,

где f (/) — функция, раскладываемая в ряд; (o{ — 2nf{, а./ = l/T} —

частота следования импульсов.

12

Коэффициенты ряда определяют следующими выражениями:

Ло__1

2 ~ Т

т

f(t) dt-

О

Ап=-

т

т

«

f (t) CGSnCDi tdt9

B.=2T

т

т

*

f (0 sin по it dt,

(1.2)

(1.3)

(1-4)

О

о

где n= 1, 2, ... .

В некоторых случаях разложение в ряд Фурье упрощается.

Так, если кривая симметрична относительно оси ординат,

т. е. если f (t)=f (~t) (рис. 1.5, а), то,в разложении будут отсут-

ствовать синусоидальные составляющие. Для доказательства

этого на рис. 1.5, б показано суммирование косинусоидальной

и синусоидальной составляющих. Как видно, наличие второй из

них нарушает указанную симметрию.

Если кривая симметрична относительно начала координат

(примером является синусоида), т. е. если f (t)— (рис. 1.6,

а), то в разложении отсутствуют косинусоидальные гармоники

и постоянная составляющая. Действительно, при наличии в раз-

ложении косинусоидальных составляющих кривая перестанет

быть симметричной относительно начала координат (рис. 1.6, 6).

Аналогичным образом можно убедиться, что в разложении кри-

вой (рис. 1.6, а) отсутствует постоянная составляющая.

Рис. 1.6

Рис. 1.7

13

Наконец, если кривая симметрична относительно оси абсцисс

(рис. 1.7, а), т. е. если f (t) = —f (t + T/2), то в разложении отсут-

ствуют постоянная составляющая и гармоники четных номеров.

О последнем свидетельствует результирующая кривая на рис. 1.7,

б, являющаяся суммой первой и второй гармоник. Аналогичным

образом можно убедиться в том, что в разложении отсутствует

постоянная составляющая.

Совокупность гармоник, составляющих данное несинусои-

дальное колебание, представляет собой спектр этого колебания.

Графическое изображение спектра колебания называют спект-

ральной диаграммой.

На спектральной диаграмме каждая гармоника изображается

вертикальной линией. Длина этой линии пропорциональна амп-

литуде гармоники, а ее положение на оси абсцисс определяется

частотой гармоники. Спектральная диаграмма дает наглядное

представление о зависимости амплитуд гармоник от их частот.

Наряду с временной диаграммой, векторным и аналитическим

выражениями функции спектральная диаграмма широко исполь-

зуется для характеристики различных колебательных процессов.

На рис. 1.8, а, б, в приведены соответственно временная,

векторная и спектральная диаграммы функции и = Umsina>t.

Определим спектры и построим спектральные диаграммы для

нескольких последовательностей видеоимпульсов.

Пример 1.2. На рис. 1.9, а приведена временная диаграмма импульсного

напряжения прямоугольной формы с периодом повторения Т= 1 мс и длитель-

ностью импульса Ги=20 мкс. Указанная последовательность симметрична от-

носительно оси ординат, поэтому в состав ее спектра (разложения) синусоидаль-

ные составляющие не входят, т. е. u(r)=[/o+[/mlcosa>1z+t/m2cos2<0|^ + --.

... + Um„cosna>lt+... .

if t

Рис. 1.8

Рис. 1.9

Как следует из рис. 1.9, а, в интервале времени — (в пределах

одного периода Т) функция и (t) = U„, а в интервале времени от ц до t2 (т. е.

в паузе) напряжение и (0 = 0. Поэтому при вычислении амплитуд гармоник (коэф-

фициентов ряда) будем интегрировать только в пределах от — ги/2 до <я/2, где

значение функции и (0^0. Отметим также, что в силу симметрии заданной

функции относительно оси ординат

Ги/2 'и/2

J и (0 dt = 2 J и (0 dt.

0

В данном случае на основании формулы (1.2) постоянная составляющая

где у — коэффициент заполнения.

В соответствии с выражением (1.3), учитывая, что Ш] = 2л/Г, получим амп-

литуду л-й гармоники:

'и/2

2 Г 4

6^ = 2- Umcos,na>\idi—-^ Um

в

х sin

^и/2

f 2л 4

cos n — tdt*=~

I T T

sin п IntjT 1я/2 2Um

=-------------------x

0 nn

э -Г

2nn)T

0

ЛЛ1И 2t/m .

----=------sin илу.

T nn

(1.5)

С увеличением номера гармоники л знаменатель выведенного выражения

возрастает по линейному закону, а числитель изменяется по закону синуса,

который не может быть больше единицы. Поэтому с увеличением номера гармо-

ник их амплитуды имеют тенденцию к уменьшению.

При ппу—кп, где Л=1, 2, ..., sin илу = 0, т. е. амплитуды гармоник превраща-

ются в нуль. Номера этих гармоник ло(, лщ, ..., фактически выпавших из разложе-

ния, определяются из равенства ппу = кп, откуда

«01 =k/y = kq. , (1.6)

Скважность рассматриваемой последовательности 9=Г/1И= 1 • 10~3/(20 х

х 10-6) = 50, поэтому в соответствии с формулой (1.6) ло( = 5О, ло2 = 1ОО, «оз = 15С

и т. д.

Частоты этих гармоник обратно пропорциональны длительности импульса:

1 к

fok = nokfl=kq

где /( — частота основной гармоники.

В данном случае/о| = 1/(20 10-6) = 50 кГц,/о2 = ЮО кГц и т. д.

Легко убедиться, что при n<«oi значения sin ппу положительны, а при

л02>п> л0, (/o2>/>/oi) значения sin ппу отрицательны. Очевидно, такое изменение

знака sin ппу будет происходить всякий раз после того, как амплитуда гармоники

обратится в нуль.

Подставляя в выражение (1.5) значения п, равные 1, 2, 3,..., можно определить

амплитуду любой гармоники:

JT 2Um . Um .

uml=----sxnny, Um2 —— smlny,

n n

2Um .

UmjS=--- sin Злу,

Зя

Таким образом, разложение заданной функции имеет вид

,ч ТГ 2Um . Um 2Um .

и (t) = Umy-i—— annycostoj/H---sinzny cos2zuj/ + ... +-sin49irycos49aiji—

« я 49л

2Um 2Um ‘ 2Um

—sin 51ny cos51<M|/——sjn52ffycos52a>ji—...— sin 99 яу cos 99<o( t +

2Um

+----anlOlrtvcoslOlaji/H-... ,

101л

Спектральная диаграмма, соответствующая рассмотренной

последовательности импульсов, показана на рис. 1.9, б.

Положительные знаки перед членами ряда указывают на то,

что начальная фаза гармоники равна +90°, отрицательные знаки

указывают на то, что начальная фаза гармоники равна — 90° (рис.

1.9, 6). Таким образом, каждый раз при переходе амплитуды

гармоники через нуль (/oi,/o2» > ft*) ее начальная фаза меняется

на 180°.

Часто спектральную диаграмму чертят только над осью абс-

цисс (рис. 1.9, в), имея по-прежнему в виду, что начальные фазы

гармоник, расположенных по разные стороны от частот /ы, сдви-

нуты на 180°.

Пример 1.3. На рис. 1.10, а приведена временная диаграмма разнополярного

импульсного напряжения прямоугольной формы с q=2.

Симметрия его относительно начала координат приводит к тому, что в раз-

ложении не будет косинусоидальных гармоник и постоянной составляющей,

а симметрия относительно оси абсцисс обусловливает отсутствие гармоник чет-

ных номеров. Поэтому разложение будет содержать только синусоидальные

составляющие нечетных номеров.

На основании формулы (1.4) амплитуды этих гармоник

т

2 Г

17тя=—J и (f) sin ntoytdl.

t|

На рис. 1-10, а видно, что в пределах одного периода

u (l) = Um при 0 t < Т/2,

и (t) = — Vm при ?72< t < Т.

Поэтому

Т/2 Г

L^sinnaii/dt— UnSmna^tdt =

е , ? .. , * 772

U, т 1

' t:; ,4-----cosntuif

' - mui T/2j

---- COSn<D|t

nan

Заменив <0j на 2л/Г и подставив пределы, по-

лучим

lUm

Um„=---------------(l-cosnn).

пп

Очевидно, что при л=1, 3, 5, ... cosnn= —I,

t/mB=4t/,B/(nn), а при л = 2, 4, 6, cosmt = l,

[/да, =0, т. е. гармоники четных номеров, как было

сказано, отсутствуют.

Таким образом, в спектре рассматриваемой

последовательности содержится бесконечное коли-

чество нечетных синусоидальных гармоник, амп-

литуды которых обратно пропорциональны номе-

ру гармоники. С увеличением его они уменьшают-

ся по гиперболическому закону, что и отражено на

спектральной диаграмме (рис. 1.10, б).

Гармоники разных частот по-разно-

му влияют на форму импульсов. Низкочастотные составляющие,

имея пологие склоны и тупую вершину, в основном участвуют

в образовании плоской вершины импульса. Склоны кривых вы-

сокочастотных гармоник имеют большую крутизну и преимуще-

ственно определяют фронты импульса. 'Поэтому если радиотех-

ническое устройство плохо пропускает Низкочастотные состав-

ляющие, то это выражается в искажении плоской вершины на

выходе; искажение фронтов связано с ограниченным прохождени-

ем через устройство высокочастотных составляющих. Чтобы из-

бежать больших искажений формы импульсов, устройства для их

усиления, передачи или трансформации следует выполнять широ-

кополосными. Несмотря на то что спектр импульса бесконечен,

можно наметить верхнюю границу полосы пропускания устрой-

ства, т. е. ограничить спектр импульсов определенной частотой.

Для прямоугольных видеоимпульсов 95% всей энергии сигнала

сосредоточивается в диапазоне частот до Если верхняя

частота полосы пропускания устройства соответствует этому

значению, то искажение фронтов передаваемого импульса будет

в большинстве случаев допустимым. Такую ширину спектра на-

зывают активной.

Спектры, показанные на рис. 1.9 и 1.10, состоят из отдельных

гармоник и являются дискретными (линейчатыми).

Располагая полученными сведениями, выясним, от чего зави-

сит плотность спектра.

Ширина частотного интервала А/ (см. рис. 1.9, б), ограничен-

ного гармониками, которые обращаются в нуль, равна Уо(*-п) —

~fok, а число гармоник в пределах его

m = (fo(k+i)~fok)lfi—foilf,

где/—частота первой гармоники.

Если длительность импульса /и о^тагЦйьЖММенйбй^ а период

2—- 2493 1 т

повторения Т увеличить, то ширина указанного интервала со-

хранится (foi = l/4), а интервал между двумя соседними гармо-

никами, равный частоте первой гармоники, уменьшится (/1 = 1/7).

В результате количество гармоник в пределах одного частотного

интервала увеличится — спектр станет более плотным (рис. 1.11).

При дальнейшем увеличении периода повторения импульсов

и сохранении их длительности спектр становится еще плотнее

(рис. 1.11). Если, увеличивая период, перейти к предельному

случаю Т’-юо (/-+0), т. е. от последовательности перейти к оди-

ночному импульсу, то его спектр будет содержать составляющие

всех частот, т. е. станет сплошным. В этом случае, как следует из

выражений (1.3), (1.4), при Т-юо амплитуды гармоник будут

бесконечно малыми.

Наоборот, если, уменьшая период, перейти к предельному

случаю Т-+0 (/'-+00), то все импульсы на временной диаграмме

сольются и изобразятся прямой, параллельной оси абсцисс, т. е.

в их спектре останется лишь постоянная составляющая.

Отмеченные свойства спектра импульсов имеют большое пра-

ктическое значение. В частности, благодаря дискретности спектра

и периодичности следования его составляющих можно один

и тот же канал связи использовать для одновременной передачи

нескольких сообщений, т. е. уплотнить его. Например, система

совмещения цветного телевидения с черно-белым предполагает

одинаковую ширину спектра телевизионного сигнала для цвет-

ной и черно-белой передачи. При этом дополнительные (по срав-

нению с черно-белой передачей) сведения о цвете путем специаль-

ных преобразований размещаются в пределах ширины спектра

черно-белого сигнала между его составляющими.

Остановимся теперь на спектре радиоимпульсов, к кото-

рому проще перейти рассматривая модуляцию высокочастотного

колебания напряжением одной частоты. Если колебания высокой

частоты /о модулируются по амплитуде синусоидальным напря-

Рис. 1.11

Рис. 1.12

18

жением низкой частоты j\, то спектр модулированного колебания

содержит, как известно, гармонику несущей частоты f0 и две

боковые гармоники fa+f и f0—f (рис. 1.12).

Если высокочастотные колебания модулируются видеоим-

пульсами, то от каждой составляющей их спектра получается

пара боковых частот. Поэтому спектр радиоимпульса содержит

две боковые полосы частот (рис. 1.13) по обе стороны от fQ.

Нетрудно заметить, что полоса пропускания устройства, по

которому проходят радиоимпульсы, должна быть вдвое больше,

чем при видеоимпульсах, представляющих собой огибающие

этих радиоимпульсов.

Следует подчеркнуть, что по сравнению с видеоимпульсом

спектр радиоимпульса имеет не только большую ширину, но

и смещен на f0 в область высоких частот.

Структура импульсных сигналов. Для сокращения написания

сигналы импульсных устройств будем называть импульсными.

Случаи, когда это может привести к смещению понятий, будут

отмечены особо.

Ранее подчеркивалось, что информация запечатлевается в из-

менениях электрического колебания. Импульсная последователь-

ность становится сигналом, когда в соответствии с передаваемой

информацией изменяются ее параметры: амплитуда импульсов,

их длительность или фаза. В частном случае информация может

выражаться появлением импульса, изменением его длительности

или временного положения относительно опорного импульса.

Различают амплитудно-импульсную (АИМ), широтно-им-

пульсную (ШИМ) и фазоимпульсную (ФИМ) модуляции. При

каждом виде модуляции один из параметров импульсной после-

довательности принимает значение, пропорциональное величине

непрерывного модулирующего сигнала в момент присутствия

импульса.

Рис. 1.14 иллюстрирует амплитудную модуляцию импульсной

последовательности непрерывным сигналом (на рисунке его

форма показана пунктиром).

Импульсный сигнал (рис. 1.14) называют дискретным, так

как он составляется элементами — импульсами, действующими

в отдельные (дискретные) моменты времени. Эти импульсы

Рис. 1.13

Рис. 1.14

являются выборками (отсчетами) непрерывного сигнала. Про-

цесс взятия отсчетов называется дискретизацией непрерывного

сигнала, а их период — периодом дискретизации.

Вместо передачи непрерывного сигнала можно передавать

соответствующий ему дискретный сигнал. В основе этого утвер-

ждения лежит теорема отсчетов, сформулированная и доказанная

советским академиком В. А. Котельниковым и ставшая фунда-

ментальным положением теории связи. Суть ее состоит в том,

что сигнал, спектр которого не имеет частот выше/и, однозначно

определяется своими мгновенными значениями (выборками, от-

счетами), разделенными одинаковыми интервалами, не превыша-

ющими 1/(2/от). Это означает, что на каждый период наивысшей

частотной составляющей сигнала должно быть по меньшей мере

два отсчета. Иными словами, частота отсчетов должна по мень-

шей мере вдвое превышать высшую частоту спектра^,.

Так как амплитуды гармоник сложного колебания уменьша-

ются с увеличением их частоты, то с некоторой погрешностью

всякий спектр можно считать ограниченным, а не бесконечным.

Передачу непрерывного сигнала его выборками можно вести

потому, что на приемной стороне канала связи по этим выборкам

непрерывный сигнал однозначно восстанавливается фильтром

нижних частот, подавляющим все составляющие с частотами

выше fm.

Импульсные сигналы в радиотехнических устройствах. Им-

пульсные сигналы широко используются для передачи инфор-

мации. Они переносят команды от одного узла устройства к дру-

гому, излучаются и принимаются радиолокационными станци-

ями, обеспечивают дистанционное радиоуправление, несут ин-

формацию в составе телевизионного сигнала, передают непре-

рывную информацию в системах импульсной связи и т. д.

Заметим, что при импульсной связи имеется возможность

«уплотнить» канал, т. е. одновременно передавать по одному

каналу несколько сообщений.

Уплотнение канала состоит в следующем. Так как длитель-

ность выборки сигнала (рис. 1.14) составляет незначительную

часть периода дискретизации Тп, то между выборками одного

сигнала можно «разместить» выборки других сигналов — по од-

ному каналу связи может одновременно передаваться несколько

сигналов. Такой способ одновременной передачи сигналов назы-

вается временным уплотнением канала.

При временном уплотнении канала на его передающей и при-

емной сторонах устанавливаются коммутаторы. Коммутатор на

передающей стороне периодически на небольшое время подклю-

чает к каналу связи источники непрерывных сигналов, в резуль-

тате чего в канал поступают выборки то одного, то другого

сигнала. На приемной стороне канала устанавливаются фильтры

нижних частот, на выходе которых выделяются непрерывные

сигналы, восстановленные из поступающих выборок. К этим

фильтрам канал связи периодически подключается коммутато-

ром, работающим точно в таком же режиме, что и коммутатор

на передающей стороне. В результате к каждому фильтру посту-

пают выборки только одного передаваемого сигнала.

АИМ-сигналы (выборки непрерывного сигнала) могут пере-

даваться непосредственно по проводам. Для передачи таких сиг-

налов через открытое пространство ими модулируется высокоча-

стотное колебание. Полученные радиоимпульсы передаются на

приемную сторону канала связи, где в результате детектирования

преобразуются в видеоимпульсы — выборки передаваемого не-

прерывного сигнала. Фильтром низких частот из этих выборок

формируется непрерывный сигнал.

§ 1.3. СИГНАЛЫ ЦИФРОВЫХ УСТРОЙСТВ

Двоичная система счисления. Последующее изложение требу-

ет некоторых сведений о двоичной системе счисления, излага-

емых далее.

Напомним, что в десятичной системе счисления (в десятичном

коде) основанием системы является число 10, используемых

цифр — десять: 0, 1, 2, ..., 9, а цены («веса») единиц в соседних

разрядах отличаются в 10 раз. В этой системе любое число

представляется последовательностью коэффициентов в разложе-

нии этого числа по степеням числа 10. Так, например, число 381О

(индекс 10 указывает на запись числа в десятичной системе

счисления) выражается суммой: 381О = 3'101 + 8’ 10°, где основа-

ние системы 10 возводится в нулевую степень (в первом, млад-

шем, разряде), в первую степень (во втором разряде), а коэф-

фициентами ряда являются цифры 3 и 8, последовательное напи-

сание которых представляет рассматриваемое число.

В двоичной системе счисления основанием системы является

число 2, используемых цифр — две: 0 и 1, а веса единиц в сосед-

них разрядах отличаются вдвое. Число в двоичной системе счис-

ления представляется последовательностью коэффициентов в

разложении этого числа по степеням числа 2. Так, число 381О вы-

ражается следующим рядом по степеням 2: 381О= 1 -25+0’24 +

+ 0 23-|-1 22 + 1'21 + 0'2° = 100 1102, где индекс 2 указывает, что

данная совокупность знаков выражает число в двоичной системе

счисления (является двоичным кодом числа).

Как следует из последнего примера, двоичный код формиру-

ется так же, как десятичный; его знаки — коэффициенты в разло-

жении числа по степеням основания (в данном случае по степе-

ням 2).

Заметим, что рассмотренный двоичный код (у которого веса

21

единиц в соседних разрядах отличаются вдвое) называется нату-

ральным двоичным кодом. В таком коде было записано приве-

денное ранее число.

Преимуществом двоичной системы счисления является то, что

она использует только две цифры. Поэтому в аппаратуре для

выполнения операций над числами в двоичной системе счисления

(над двоичными числами) достаточно пользоваться двумя значе-

ниями, к примеру, напряжения. Наряду с этим в двоичной систе-

ме счисления число имеет большее количество разрядов, чем

в десятичной, что является недостатком двоичной системы.

Цифровые сигналы. Цифровым сигналом представляются дво-

ичные числа, поэтому он состоит из элементов только двух

различных значений. Одним из них представляется 1, а другим —

0. По установившейся терминологии эти элементы сигнала назы-

вают соответственно единицей и нулем.

Цифровой сигнал может быть потенциальным или импульс-

ным.

Элементами потенциального цифрового сигнала явля-

ются потенциалы двух уровней. Каждый уровень остается неиз-

менным в течение так называемого тактового интервала; на его

границе уровень потенциала изменяется, если следующая цифра

двоичного числа отличается от предыдущей. На рис. 1.15, а изоб-

ражен потенциальный цифровой сигнал, представляющий напи-

санное сверху число; высоким потенциалом отображается 1, а

низким — 0.

Элементами импульсного цифрового сигнала являются

импульсы неизменной амплитуды и их отсутствие. На рис. 1.15, б

положительный импульс представляет 1, а отсутствие импульса

представляет 0 написанного сверху двоичного числа.

Обоими цифровыми сигналами (рис. 1.15) двоичное число

10011010 выражено в последовательной форме (последователь-

ным кодом): разряды числа представляются последовательно,

друг за другом. При этом

потенциалы (импульсы), со-

ответствующие разрядам

числа, передаются по одной

линии и обрабатываются

устройством последователь-

но.

При представлении дво-

ичного числа в параллель-

ной форме (параллельным

кодом) его разряды предста-

вляются одновременно. При

этом количество линий пе-

редачи, а также однотипных

элементов устройства, обра-

батывающих цифровой сигнал, должно

быть равно количеству разрядов числа,

т. е. существенно увеличивается. Такой

цифровой сигнал значительно быстрее

обрабатывается устройством. На рис.

1.16 изображен потенциальный цифровой

сигнал, выражающий двоичное число

10011010 в параллельной форме.

Заметим, что кроме использованного

соответствия (в цифровом сигнале эле-

ментом с большим значением представ-

ляется единица числа, а элементом с

меньшим значением — нуль) применяет-

ся и обратное (элемент сигнала с боль-

шим значением представляет нуль, а эле-

мент с меньшим значением — единицу

числа). Первое соответствие называется

классом положительной, а второе —клас-

сом отрицательной логики.

Цифровой сигнал может быть сфор-

мирован из непрерывного сигнала анало-

го-цифровым преобразователем (АЦП),

который нередко называют преобразова-

телем аналог — код или аналог — циф-

Рис. 1.16

ра. Такое преобразование сводится к тому, что из непрерывного

сигнала периодически производятся выборки мгновенных зна-

чений; каждая выборка округляется до ближайшего разрешен-

ного уровня, а код этого уровня (двоичное число) представляется

элементами цифрового сигнала. Совокупность таких двоичных

чисел, выраженных элементами цифрового сигнала, — цифровой

сигнал, соответствующий преобразуемому непрерывному сиг-

налу.

Рассмотрим переход от дискретного сигнала (см. рис. 1.14) к

цифровому. Весь диапазон возможных изменений непрерывного

сигнала разбивается на конеч-

ное число равноотстоящих

уровней (называемых уров-

нями квантования), кото-

рые дискретный сигнал толь-

ко и может принимать. Каж-

дая выборка сигнала округля-

ется до ближайшего разре-

шенного уровня (рис. 1.17, а).

Эта операция называется

квантованием сигнала по

Уровню или просто кванто-

ванием.

Рис. 1.17

Квантованный дискретный сигнал имеет конечное (счетное)

количество значений. Благодаря этому каждому из них может

быть присвоен какой-то код (число). Эту операцию называют

кодированием.

Если квантованные уровни (рис. 1.17, а) кодировать числами

двоичной системы счисления, то последовательность их составит

двоичный код сигнала: 0010; 0100, 0101, ..., 1001, 1010, 1000, ОНО.

После кодирования операцию над непрерывным сигналом можно

заменить соответствующей операцией над кодами его уровней.

Так, при передаче сигнала (рис. 1.17, а) надо последовательно

в моменты времени 12,..., t„ передавать информацию о записан-

ных числах. Это осуществляется цифровым сигналом, один эле-

мент которого представляет 1 каждого числа, а другой — 0.

На рис. 1.17, б изображен цифровой сигнал, соответствующий

квантованному дискретному сигналу (рис. 1.17, а).

Так как в отношении передаваемой информации цифровой

сигнал эквивалентен непрерывному, из которого он сформиро-

ван, то вместо операций над непрерывным сигналом (передачи,

преобразования, хранения) можно производить операции над

соответствующим ему цифровым сигналом. Во многих случаях

это оказывается более эффективным.

Обратное преобразование цифрового сигнала в непрерывный

осуществляется цифроаналоговым преобразователем (ЦАП).

На входы такого преобразователя одновременно поступают по-

тенциалы, представляющие разряды кода каждой выборки. По-

тенциалы, соответствующие единицам, открывают ключи, через

которые на выход поступают напряжения, пропорциональные

весам единиц разрядов. Так на выходе формируется напряжение,

пропорциональное весу кода каждой выборки.

Аналого-цифровые и цифроаналоговые преобразователи опи-

саны в гл. 8.

Устройства, в которых действуют цифровые сигналы, называ-

ют цифровыми. Цифровые сигналы используются в устрой-

ствах различного назначения. В электронных вычислительных

машинах (ЭВМ) и в цифровой автоматике входная информация

представляется цифровыми сигналами, над которыми эти

устройства осуществляют необходимые действия.

В системах радиосвязи цифровыми сигналами передаются

сообщения, имеющие разную форму: звуковую, печатную, форму

изображения и т. д. Такая связь отличается скрытностью и поме-

хоустойчивостью .

Последнее обусловлено тем, что такой сигнал имеет- только

два различимых уровня. Поэтому когда значение сигнала попада-

ет между ними, то это фиксируется как помеха. Если помеха

меньше половины разности уровней сигнала, то она легко раз-

личается и значения уровней просто восстанавливаются регенера-

торами.

24

Непрерывный сигнал очистить от помехи значительно слож-

нее, что объясняется следующим. Мгновенные значения непре-

рывного сигнала, разделенные бесконечно малым временным

интервалом, отличаются на бесконечно малую величину, т. е.

непрерывный сигнал имеет несчетное (бесконечное) количество

значений. Поэтому, искаженный помехой, он может быть принят

за полезный.

На передающей стороне канала цифровой связи непрерывный

сигнал преобразуется в цифровой с помощью аналого-цифрового

преобразователя. Цифровой сигнал может непосредственно пе-

редаваться по проводам. Для передачи по радиоканалу им моду-

лируется высокочастотное колебание.

На приемной стороне радиоканала цифровой связи принятые

радиоимпульсы преобразуются детектором в видеоимпульсы —

цифровой сигнал. Этот сигнал может быть использован непо-

средственно (например, введен в ЭВМ) или преобразован в ис-

ходный непрерывный сигнал с помощью цифроаналогового пре-

образователя.

Логические сигналы. Цифровые сигналы, рассмотренные

в предыдущем разделе, отражают числовые значения физических

величин, например напряжения.

Наряду с ними в цифровых устройствах действуют сигналы,

появление которых связано с наступлением или ненаступлением

какого-либо события. Чтобы ощутить разницу между этими

видами сигналов, обратимся к аналого-цифровому преобразова-

телю и сравнивающему устройству.

Когда на входе АЦП присутствует напряжение, на выходах

появляется его эквивалент — цифровой сигнал в виде многораз-

рядного параллельного двоичного кода. Увеличение входного

напряжения вызывает пропорциональное (в отсутствие погреш-

ностей) увеличение этого кода.

Наряду с этим после окончания преобразования на одном из

выводов АЦП появляется потенциал определенной величины —

сигнал «Конец преобразования». Какими бы ни были входное

напряжение и выходной код, величина этого сигнала остается

неизменной. Он свидетельствует о наступлении события — окон-

чании преобразования.

АЦП не начнет новый цикл, пока не получит извне сигнал

«Начать преобразование». Этот сигнал неизменной величины

является подтверждением того, что сформированный в предыду-

щем цикле код уже обработан другими элементами устрой-

ства — указанное событие наступило.

Рассмотрим сравнивающее устройство — компаратор. Когда

Два кода на его входах окажутся равными, на одном из выходов

появится потенциал определенного уровня — сигнал, свидетель-

ствующий о наступлении события, — равенстве кодов. Точно

такой же сигнал появится ца этом выводе при равенстве кодов

55

совсем другой величины. Такой же сигнал будет на другом

выводе компаратора, если один код меньше другого, причем

величина их разности никакого влияния на величину этого сиг-

нала не оказывает.

На выводах АЦП и выводах компаратора описанные сигналы

имеют одинаковые значения. Разработчики аппаратуры предус-

матривают их появление как ответ на’ наступление того или

иного события вне зависимости от его содержания (одно число

стало больше другого, преобразование закончилось и т. д.), важ-

ны лишь истинность события или его ложность.

Наличие или отсутствие описанных сигналов и порождающие

их условия связаны выражениями типа «если ..., то...» и другими

логическими связями. Поэтому такие сигналы называются логи-

ческими. Это название связано с тем, что аналогичные условия

между причиной и следствием являются предметом обсуждения

и изучения в логике.

Формальная логика — наука о законах и формах человечес-

кого мышления — оперирует с высказываниями вне зависимости

от их содержания, учитывая только их истинность или ложность.

Истинные высказывания: «Электрический ток существует только

в замкнутой цепи», «Архангельск расположен в северном полу-

шарии», ложные: «Кит — теплолюбивое растение», «Ангара —

приток Волги».

Высказывания могут быть простыми и сложными. Простое

содержит только один факт, не зависящий от других фактов, т. е.

сам по себе может быть истинным или ложным. В приведенных

выше примерах высказывания — простые. Сложное высказыва-

ние содержит несколько простых высказываний, например: «Я

пойду в кино, если не будет дождя и со мной пойдет приятель».

Введение в формальную логику ограниченного числа логичес-

ких связок (они будут описаны далее), допускающих строго

определенное толкование, позволило однозначно представлять

сложное высказывание совокупностью простых, а введение сим-

волов, обозначающих простые высказывания, — решать логичес-

кие задачи математическими средствами. Их совокупность со-

ставляет содержание алгебры логики, или булевой алгебры, на-

званной так в честь ее создателя — английского математика

Джорджа Буля. В соответствии с ней истинному высказыванию

(наступлению события) приписывается, ставится в соответствие

символ 1 (логическая 1), а ложному (ненаступлению события) —

символ 0 (логический 0).

Необходимо отметить, что символы 0 и 1 никакого отноше-

ния к числовому значению сигнала не имеют. Они лишь описыва-

ют качественное состояние события, и поэтому к ним непримени-

мы арифметические операции. В электрических цепях эти сим-

волы обычно представляются так же, как аналогичные в циф-

ровом сигнале: логическая 1 — высоким, а логический 0 — низ-

26

ким уровнем потенциала. Такую логику называют положи-

тельной. Наряду с ней используют и отрицательную логику,

в которой логическому 0 ставят в соответствие более высокий

потенциал, чем логической 1.

Рассмотрим высказывание: «Автомат сработает, когда будут

нажаты кнопки К1 и К2 или нажата кнопка КЗ и не нажата кнопка

К4». Здесь простые высказывания (состояния кнопок) внедрены

в сложное высказывание (срабатывание автомата) с помощью

союзов — связок И, ИЛИ, НЕ; состояния кнопок играют роль

аргументов (переменных), над ними эти союзы осуществляют

такие функциональные преобразования, которые формируют

функцию — условие срабатывания автомата.

Далее простое высказывание (событие) будем обозначать сим-

волом х, а сложное событие, являющееся функцией простых, —

символом у.

Из изложенного ранее следует, что булева алгебра оперирует

с переменными, принимающими только два значения: 0 и 1, т. е.

с двоичными переменными. Функция двоичных переменных, при-

нимающая те же два значения, называется логической функ-

цией (переключательной функцией, функцией алгебры логики).

Логическая функция может быть выражена словесно, в алгеб-

раической форме и таблицей, называемой переключательной

таблицей или таблицей истинности.

Любое самое сложное логическое высказывание, в частности,

функционирование устройства, электрической цепи и т. д., мож-

но описать, используя три логические операции: сложение (дизъ-

юнкцию), умножение (конъюнкцию) и отрицание (инверсию), —

которыми могут быть связаны простые высказывания. В указан-

ном смысле этот набор логических функций называют функци-

онально полным набором или базисом.

Базисные логические функции. Логическое сложение

(дизъюнкция) переменных хь х2, , х„ записывается в виде

у = х1 + х2 + ...+х„. (1.7)

Значение у — 0 имеет место только при х, = х2 —... = х„ = 0.

Если хотя бы одно слагаемое равно единице (х, = 1 — событие

наступило), то у= 1. Сумма наступивших событий (х, + х2 +..., где

xi = l, х2— 1, ...) означает наступление события, т. е. при любом

числе слагаемых, равных единице, сумма их равна единице: у= 1,

если Х! = 1, или х2=1, или xf=l, или все переменные х равны

единице. Этим объясняется еще одно название рассматриваемой

операции — операция ИЛИ.

Табл. 1.1 —таблица истинности операции ИЛИ двух пере-

менных. В каждой ее строке записаны значения переменных Xi и

•Хг и соответствующее им значение функции у.

27

Две двоичные переменные имеют

четыре сочетания. В общем случае п

двоичных переменных дают 2" сочета-

ний.

Кроме знака « + » дизъюнкция обо-

значается знаком V : у=х1 V х2 V ...

... V х„.

Элемент, выполняющий дизъюнк-

Таблица 1.1

XI х2 У

0 0 1 1 0 1 0 1 0 1 1 1

цию, называется дизъюнктором или элементом ИЛИ.

Электрическая реализация операции ИЛИ дана на рис. 1.18, а.

Замкнутое состояние ключа будем представлять логической еди-

ницей (Кл = 1), разомкнутое — логическим нулем (Кл=0). Лам-

почка будет светить (Л = 1), если выполняются условия: ключ

Кл1 замкнут, ключ Кл2 разомкнут (первое простое высказыва-

ние)— Кл1 = 1, Кл2 = 0 ИЛИ ключ Кл1 разомкнут, ключ Кл2

замкнут (второе простое высказывание) ИЛИ ключ Кл1 замкнут,

ключ Кл2 замкнут (третье простое высказывание).

Высказывание «лампочка светит, если...» может быть представ-

лено простыми высказываниями, соединенными операцией ИЛИ:

y=xt +х2,

где х, соответствует состоянию ключа Кл1, х2 — состоянию клю-

ча Кл2, а у — состоянию лампочки.

Логическое умножение (конъюнкция) переменных запи-

сывается в виде

y = XiX2... х„. (1.8)

Из приведенного выражения следует, что если хотя бы одна из

переменных равна нулю, то функция равна нулю. Только в том

случае, когда Х] = 1, И х2= 1, И, ..., И х„ — 1, у = 1. Поэтому данная

Таблица 1.2

О

О

1

1

О

О

о

1

операция называется также операци-

ей И.

Табл. 1.2 — таблица истинности

операции И двух переменных.

Кроме приведенной встречается

следующая форма записи конъюнкции:

у=Х| ах2а ... лх„. Элемент, выполняю-

щий конъюнкцию, называется конъюн-

ктором или элементом И.

Х[ х2

Рис. 1.18

На рис. 1.18, б показана электрическая реализация операции

И. Лампочка будет светить (у=1), если замкнуть ключ Кл1

(Xi = l) и замкнуть ключ Кл2 (х2=1). Логическое уравнение, вы-

ражающее состояние лампочки, имеет вид

У = х1х2,

где значения х, и х2 соответствуют состояниям ключей Кл1

И Кл 2 • _ я б л и тг я 1 3

Логическое отрицание (инвер- ц 1

сия) записывается в виде у = х и называ- -------------

ется также операцией НЕ, читается «у------------------

НЕ х». Табл. 1.3 — таблица истинности

операции НЕ.

Элемент, выполняющий инверсию, на-

зывается инвертором или элементом НЕ.

Электрическая реализация операции НЕ показана на рис. 1.18,

в. Если ключ Кл замкнут (Кл= 1), то лампочка не светит (Л = 0),

при Кл = 0 Л = 1.

Если в выражении (1.7) дизъюнкцию заменить на конъюнк-

цию и проинвертировать все переменные х, то результат окажет-

ся инверсией прежнего значения функции. Действительно, пусть

Xj = x2 = l, х3 = х4=... = х„ = 0 и поэтому yi = i; после инверсии Х! =

=х2 = 0, х3 = х4=... =х„= 1 и конъюнкция этих переменных у2=0,

т. е. равна инверсии у,. Аналогично, если в выражении (1.8)

конъюнкцию заменить на дизъюнкцию и проинвертировать все

переменные, то результат окажется инверсией прежнего значения

функции. Указанные свойства выражают принцип двойственности

алгебры Буля.

Основные соотношения алгебры логики. Приводимые

далее соотношения записаны в основном для частного случая двух

переменных. Они справедливы для любого числа переменных.

Основные тождества алгебры логики:

х + 0=х; х + 1 = 1;х+х = х; х + х=1;

х 0 = 0; х1=х; х х = х; х х = 0;х = х.

Их справедливость легко установить, подставляя вместо х

значения 0 и 1.

Последнее выражение первой строчки тождеств (х + х=1) —

закон исключения третьего: из двух противоположных высказы-

ваний (х и х) одно обязательно должно быть истинным (третьего

не дано), поэтому их логическая сумма истинна.

Предпоследнее выражение второй строчки тождеств (х х =

=0) — закон противоречия: два противоположных высказыва-

ния не могут быть одновременно истинными.

Основные законы алгебры логики, действующие при сложе-

нии и умножении переменных:

переместительный закон: х1 + х2 = х2+х1; х1х2=х2хь

сочетательный закон: (х{ 4- х2) + х3 = Xi + (х2 + х3); (xi х2) х3 =

= xt (х2х3);

распределительный закон: Xi (х2 4- х3) = xi х2 4- Х[ х3; Xi + х2 х3 =

= (х1+х2) (х,4-х3).

Справедливость последнего равенства (не имеющего аналога

в обычной алгебре) просто доказать, используя тождества Xj =

= Xi (1 4- х2 + х3), Xt=XfX2. Действительно, х1 + х2х3=х| (1 + х2 +

4- х3) 4- х2х3 — Xi + Xi х2+%1 х3 Ч- х2х3 = Xi X] + Х[ х2 4- Xi х3 4- х2х3 — (xi +

4-х2) (xi4-x3)-

Закон поглощения: х14-х1х2 = х1; X! (х1+х2) = х1. Оба этих ра-

венства доказываются просто: Х|4-Х|Х2=х1 (1+х2) = х1; Xi (xj +

4-х2) = х1х1 + х1х2=х1 +х1х2 = х1 (1 4-x2) = Xj.

Закон склеивания: х1х24-х1х2 = хь (х|+х2) (х|4-х2) = х!.

Справедливость этих равенств легко установить:

Х|Х24-х1х2=х1 (x2 + x2) = Xi; (Xi + x2) (Xi+x2) =

= XiXi +x1x24-x1x2 + x2x2=x1 (1 4-x24-x2)=X!,

Закон отрицания (закон инверсии, теорема де Моргана):

Xi 4- х2 = Xj х2; Х( х2 = Х[ + х2,

или в другой форме, получающейся инверсией обеих частей каж-

дого равенства: х14-х2=х1х2; Х!Х2 = Х!Х2.

Справедливость этих выражений следует из принципа двойст-

венности алгебры Буля.

Составление логических функций. Простую логическую

функцию иногда можно записать в аналитической форме непос-

редственно из словесного определения. В общем случае для полу-

чения аналитической формы используют таблицы истинности.

Пусть логическая функция задана в табл. 1.4. Чтобы на набо-

рах 1, 2, 3, 6 было у= 1, единице должна_быть равна каждая из

конъюнкций: х3х2хь или х3х2хь или х3х2хн или х3х2хн где х; за-

писывают в инверсной форме, если он в этом наборе равен нулю

(иначе конъюнкция не будет равна единице).

Таблица 1.4

Номер набора *3 х2 *1 У

0 1 1 1 0

1. 1 1 0 1

2 1 0 1 1

1 0 0 1

4 0 1 1 0

5' 0 1 0 0

е 0 0 1 1

7 0 0 0 0

30

Таким образом,функцию, представляемую табл. 1.4, следует

записать в виде

у = Х3Х2^1 + Х3Х2Х[ + Х3Х2Х, + Х3Х2ХЬ (1-9)

Такая форма логической функции называется совершенной

дизъюнктивной нормальной формой (СДНФ). Она пред-

ставляется логической суммой простых конъюнкций, каждая из

которых содержит все переменные в прямом или инверсном виде

не более одного раза; в такие конъюнкции не входят суммы

переменных, а также отрицания произведений двух переменных

или более. Входящие в СДНФ конъюнкции называются минтер-

мами или конституентами единиц.

Логическая сумма конъюнкций, отличающаяся от (1.9) тем,

что все конъюнкции или некоторые из них не содержат всех

переменных (в прямом или инверсном виде), представляет собой

дизъюнктивную нормальную форму (ДНФ) функции.

Логическая функция может быть составлена не только по

единичным, но и по нулевым значениям. Из табл. 1.4 следует, что

на наборах 0, 4, 5, 7 у = 0. Чтобы на каждом указанном наборе

.имело место у = 0, нулю должна равняться дизъюнкция перемен-

ных из этого набора, т. е. каждое слагаемое дизъюнкции; если

в данном наборе переменная равна единице, то в дизъюнкцию

должна входить ее инверсия. На всех указанных наборах функция

из табл. 1.4 будет равна нулю, если осуществить конъюнкцию

составленных дизъюнкций:

у = (х3 + х2 + х1) (хз + Хг + Xi) (х3 + х2 + xj (х3 + х2 + х!). (1-Ю)

Здесь у=0 обеспечивают: первый сомножитель при х3 = х2 =

=Xi = 0 (при x3 = x2 = Xi = l, т. е. на наборе 0), второй сомножи-

тель при х3 = х2 = х1 = 0 (при х3 = 0; x2 = Xj = 1, т. е. на наборе 4),

третий сомножитель при х3 = х2 = Xi = 0 (при х3 — Xi = 0; х2 = 1, т. е.

на наборе 5), четвертый сомножитель при х3 = х2 = Х! = 0, т. е. на

наборе 7.

Форма, в которой выражена функция (1.10), называется со-

вершенной конъюнктивной нормальной формой

(СКНФ). Она представляется логическим произведением дизъюн-

кций, каждая из которых содержит все переменные в прямом или

инверсном виде не более одного раза. Входящие в произведение

сомножители — дизъюнкции — называются макстермами или

конституентами нулей.

Логическое произведение дизъюнкций, отличающееся от (1.10)

тем, что все дизъюнкции или некоторые из них не содержат всех

переменных (в прямом или инверсном виде), представляет собой

конъюнктивную нормальную форму (КНФ) функции.

Так как одна и та же логическая функция, выраженная опре-

деленной таблицей истинности, записывается в СДНФ и СКНФ,

31

то каждую из этих форм можно преобразовать в другую. Логи-

ческая функция имеет единственные СДНФ и СКНФ, что непо-

средственно следует из методики их получения.

В качестве примера рассмотрим следующую логическую за-

дачу.

В четырех точках конструкции установлены термодатчики.

Деформация ее может наступить при’одновременном перегреве

в точках 4 иЗ. Однако если при этом возникает перегрев и в точке

2, то конструкция не деформируется, а при одновременном пере-

греве в точках 4, 3, 2, 1 опасность возникает вновь. Кроме того,

опасен перегрев в точке 2, если он не сочетается с перегревом

в точке 1, а одновременный перегрев в точках 2, 1, 3 вызывает

деформацию. По условию эксплуатации сочетания перегревов

в других точках невозможны. При наступлении опасной ситуации

должен быть подан сигнал тревоги.

Отметим особенности задачи. Одна состоит в том, что ин-

терес представляет не конкретное значение температуры, а факт

превышения допустимого уровня, т. е. наступление или ненасту-

пление определенного события. Другая особенность в том, что

сигнал тревоги должен быть подан при одновременном наступле-

нии определенных ситуаций и не должен подаваться при других

ситуациях. Это свидетельствует о том, что данная задача принад-

лежит к типу логических.

Превышение допустимого уровня температуры в точках 4, 3,

2, 1 обозначим соответственно х4=1, х3 = 1, х2=1, х, = 1, а тот

факт, что в указанных точках температура ниже допустимого

уровня, обозначим как х4 — 0, х3 = 0, х2—0, х2=0.

Все возможные комбинации четырех двоичных переменных

приведены в переключательной табл. 1.5.

Таблица 1.5

п х4 хз х2 *1 У

0 1 1 1 1 1

1 1 1 1 0 0

2 1 1 0 1 —

3 1 1 0 0 1

4 1 0 1 1 —

5 1 0 1 0 .—_

6 1 0 0 1 —

7 1 0 0 0 .—-

8 0 1 1 1 1

9 0 1 1 0 —

10 0 1 0 .1 —

И 0 1 0 0 ——

12 0 0 1 1 0

13 0 0 1 0 1

14 0 0 0 1 —

15 0 0 0 0 —

32

По условиям задачи опасными являются превышения тем-

пературы в точках 4, 3, 2, 1 ИЛИ, 4, 3 ИЛИ, 3, 2, 1 ИЛИ, 2.

Поэтому против комбинаций х4 = 1, х3=1, х2=1, х^1; х4=1,

хэ=1, х2=0, х1 = 0; х4 = 0, х3=1, х2 = 1; Xj = l; х4=0, х3=0, х2=1,

Xj = O в графе у поставлены единицы.

Комбинации х4=1, х3 = 1, х2 = 1, Xt = 0; х4 = 0, х3 = 0; х2=1,

Xi = 1 не являются опасными (у = 0). Прочерки в графе у сделаны

против тех комбинаций, которые по условиям задачи не являют-

ся реальными, т. е., по существу, запрещены:

х4= 1, х3= 1, х2 —0, Xi = l; х4 = 1, х3 = 0, х2= 1, Xi = l;

х4= 1, х3 = 0, х2= 1, х1 = 0; х4=1, х3 = 0, Х2 = 0, Xi = 1;

х4= 1, х3 = 0, х2 = 0, xt = 0; х4 = 0, х3=1, х2=1, xt = 0;

х4=0, х3 = 1, х2 = 0, х, = 1; х4=0, х3 = 1, х2 = 0, X! = 0;

х4=0, х3 = 0, х2 = 0, Xi = 1; х4=0, х3 = 0, х2=0, х3 = 0.

Пользуясь табл. 1.5, можно составить логическую функцию.

Она будет содержать четыре четырехбуквенные конъюнкции,

объединенные дизъюнкцией. Окончательный ее вид приведем

далее после рассмотрения вопроса о минимизации функций.

Минимизация логических функций. Минимизацией на-

зывают процедуру упрощения логической функции, с тем чтобы

она содержала минимальное количество членов при минималь-

ном числе переменных.

В некоторых простых случаях минимизацию можно осущест-

вить непосредственно используя основные законы булевой алгеб-

ры. В качестве примера упростим выражение (1.9), используя

закон склеивания:

у=х3х2х1 + х3х2х1 + х3х2х]-ЬХзХгх^ХзХ! (х2 + х2) + x2xi (х34-х3)=

= х3х1 + х2х1.

Полученное выражение равносильно исходному, но значите-

льно проще его.

Пусть имеется логическая функция

У = Х3Х2Х, + X3X2Xi + Х3Х2Х! + Х3Х2Х!.

Добавим дважды к ее правой части уже имеющийся член

x3x2Xi (отчего функция не изменится); тогда

У = X3X2Xi + Х3Х2Х, + Х3Х2Х1 + Х3Х2Х! + х3х2х14-

+ ХзХ2Х, = х3х2 (х, + Х1).+ х3х1 (х2 + х2) +

+ Х2Х! (Хз + Х3) = Х3Х2 + Х3Х1+Х2Х].

И это выражение значительно проще исходного.

Следует отметить, что такие элементарные приемы миними-

3 — 2493 13

зации удается использовать не часто — при малом количестве

членов функции и небольшом числе переменных. В других случа-

ях применяются специальные методы минимизации, облегча-

ющие поиск склеивающихся членов. К ним относится метод

минимизации с помощью карт Карно.

Карта Карно построена так, что в ее^ соседние клетки попада-

ют смежные члены функции — члены, отличающиеся значением

одной переменной: в один член эта переменная входит в прямой

форме, а в другой — в инверсной. Благодаря этому возникает

наглядное представление о различных вариантах склеивания

смежных членов.

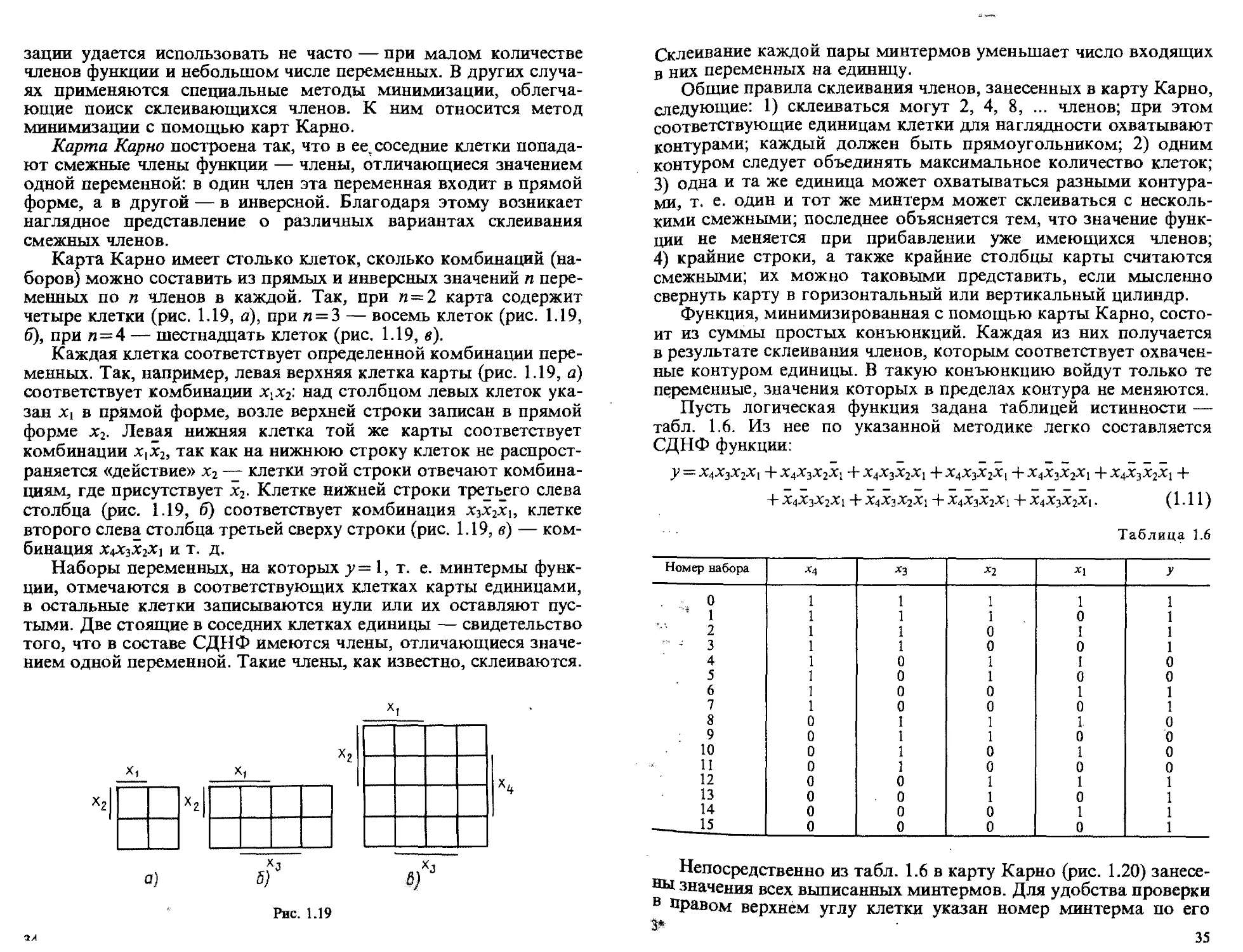

Карта Карно имеет столько клеток, сколько комбинаций (на-

боров) можно составить из прямых и инверсных значений п пере-

менных по п членов в каждой. Так, при п — 2 карта содержит

четыре клетки (рис. 1.19, а), при и = 3 — восемь клеток (рис. 1.19,

б), при и=4 — шестнадцать клеток (рис. 1.19, в).

Каждая клетка соответствует определенной комбинации пере-

менных. Так, например, левая верхняя клетка карты (рис. 1.19, а)

соответствует комбинации х{х2: над столбцом левых клеток ука-

зан Xi в прямой форме, возле верхней строки записан в прямой

форме х2. Левая нижняя клетка той же карты соответствует

комбинации Х|Х2, так как на нижнюю строку клеток не распрост-

раняется «действие» х2 — клетки этой строки отвечают комбина-

циям, где присутствует х2. Клетке нижней строки третьего слева

столбца (рис. 1.19, б) соответствует комбинация х3х2хь клетке

второго слева столбца третьей сверху строки (рис. 1.19, в) — ком-

бинация Х4Х3Х2Х] и т. д.

Наборы переменных, на которых у= 1, т. е. минтермы функ-

ции, отмечаются в соответствующих клетках карты единицами,

в остальные клетки записываются нули или их оставляют пус-

тыми. Две стоящие в соседних клетках единицы — свидетельство

того, что в составе СДНФ имеются члены, отличающиеся значе-

нием одной переменной. Такие члены, как известно, склеиваются.

Рис. 1.19

Склеивание каждой пары минтермов уменьшает число входящих

в них переменных на единицу.

Общие правила склеивания членов, занесенных в карту Карно,

следующие: 1) склеиваться могут 2, 4, 8, ... членов; при этом

соответствующие единицам клетки для наглядности охватывают

контурами; каждый должен быть прямоугольником; 2) одним

контуром следует объединять максимальное количество клеток;

3) одна и та же единица может охватываться разными контура-

ми, т. е. один и тот же минтерм может склеиваться с несколь-

кими смежными; последнее объясняется тем, что значение функ-

ции не меняется при прибавлении уже имеющихся членов;

4) крайние строки, а также крайние столбцы карты считаются

смежными; их можно таковыми представить, если мысленно

свернуть карту в горизонтальный или вертикальный цилиндр.

Функция, минимизированная с помощью карты Карно, состо-

ит из суммы простых конъюнкций. Каждая из них получается

в результате склеивания членов, которым соответствует охвачен-

ные контуром единицы. В такую конъюнкцию войдут только те

переменные, значения которых в пределах контура не меняются.

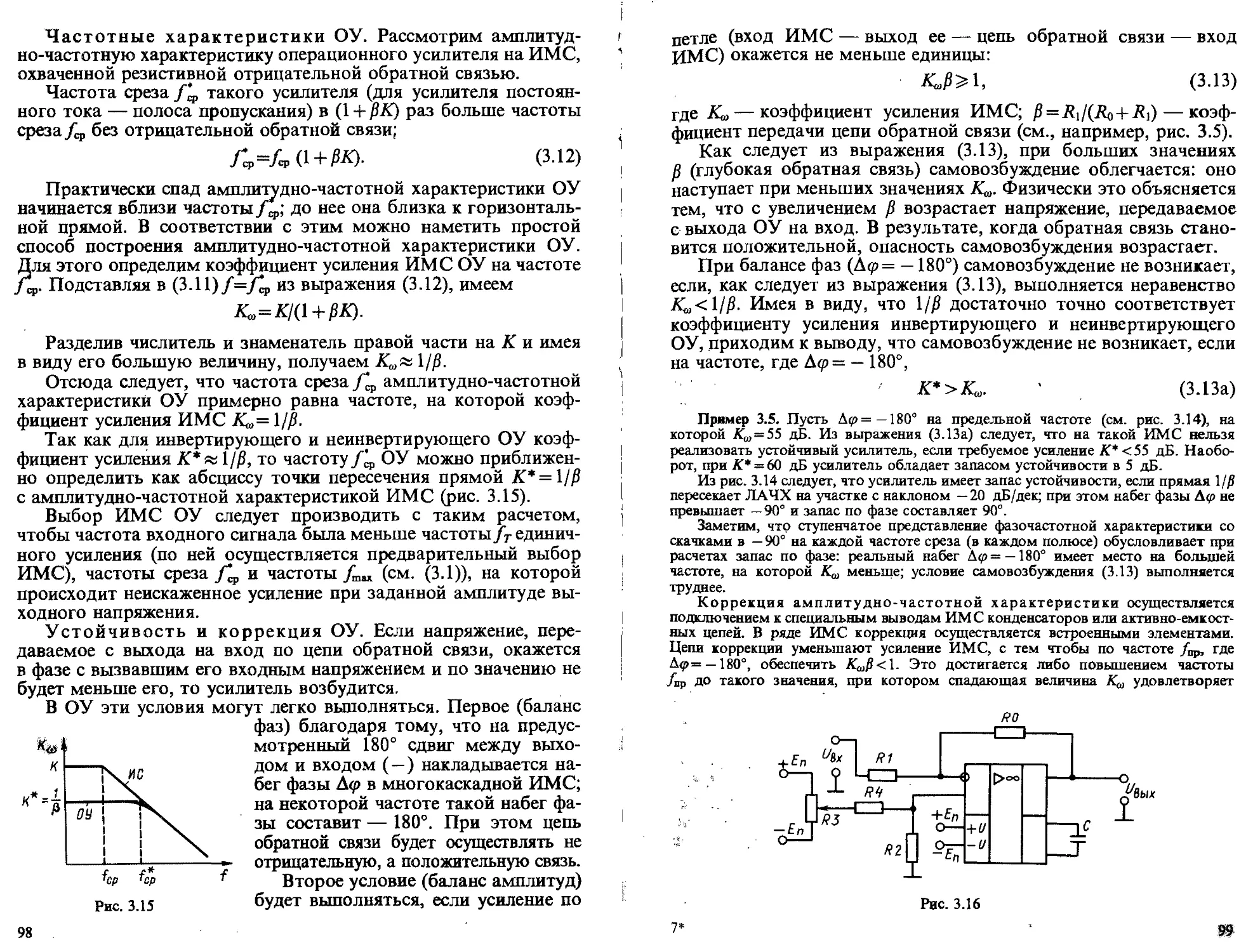

Пусть логическая функция задана таблицей истинности —

табл. 1.6. Из нее по указанной методике легко составляется

СДНФ функции:

У = Х4Х2Х2Х[ + X4X3X2Xi + Х4Х3Х2Х[ + Х4Х3Х2Х, + Х4Х3Х2Х1 + Х4Х3Х2Х[ +

+ Х4Х3Х2Х1 +Х4Х3Х2Х1 +Х4Х3Х2Х! +Х4Х3Х2Х|. (1.11)

Таблица 1.6

Номер набора -Ч *3 Х2 ^1 У

0 1 1 1 1 1

j 1 1 1 0 1

2 1 1 0 1 1

, 3 1 1 0 0 1

4 1 0 1 1 0

5 1 0 1 0 0

6 1 0 0 1 1

7 1 0 0 0 1

8 0 1 1 1. 0

9 0 1 1 0 0

10 0 1 0 1 0

11 0 1 0 0 0

12 0 0 1 1 1

13 0 0 1 0 1

14 0 0 0 1 1

15 0 0 0 0 1

Непосредственно из табл. 1.6 в карту Карно (рис. 1.20) занесе-

иы значения всех выписанных минтермов. Для удобства проверки

в правом верхнем углу клетки указан номер минтерма по его

3»

35

Рис. 1.20 Рис. 1.21

месту в табл. 1.6. Контурами охвачены единицы, соответству-

ющие склеиваемым минтермам. Ниже приведены номера мин-

термов и результаты их склеивания: 0, 1,2, 3: х4х3; 6, 2, 3, 7: х4х2;

12, 13, 14, 15: х4х3.

В_ результате функция (1.11) представляется в виде у = х4х3 +

+х4х2+х4х3.

Полученная форма функции проще первоначальной. Интерес-

но отметить, что она не содержит переменной х,.

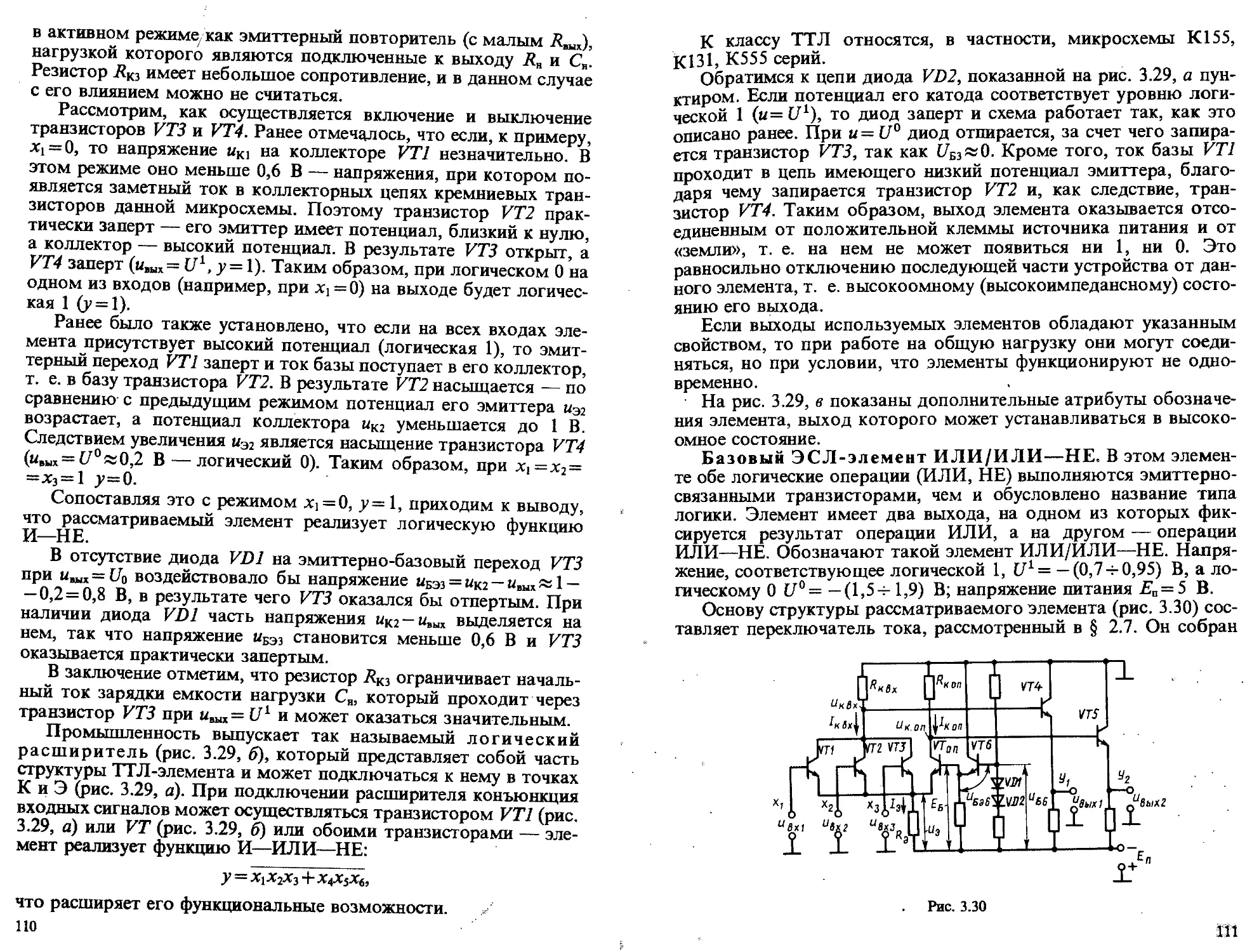

В карту Карно (рис. 1.21) внесены значения минтермов фу-

нкции

У = Х4Х3Х2Х1 +ХцХ3Х2Х1 + X4X3X2Xj +Х4Х3Х2Х! +

+х4х3х2х1 Ч-ХфХэХгХ!.

Склеивание минтермов 5,6; 5,4; 1,2;_1,3 дает следующую ми-

нимизированную функцию: y = x3x2x1+x4x3x2 + x3x2xi+x4x2Xj.

Склеивание_минтермов 5,6; 4,3; 1,2 приводит к другой форме:

y = x3x2xi + x4x3xl+x3x2x1, что проще полученной первоначально.

Из приведенного примера следует, что минимизация с помо-

щью карт Карно не приводит к однозначной форме и для получе-

ния наиболее простой формы необходимо рассматривать всевоз-

можные варианты склеивания.

При числе аргументов, большем четырех, используют обычно

другие методы минимизации — применение карт Карно стано-

вится трудоемким.

Встречается необходимость минимизировать функцию, значе-

ния которой при некоторых комбинациях переменных не опреде-

лены. Такой случай может иметь место, если значение функции

при этих комбинациях безразлично или если определенные ком-

бинации переменных невозможны по условиям задачи. На таких

избыточных (запрещенных, факультативных) комбинациях мож-

но придать функции любое значение — 0 или 1. Рациональное

доопределение функции может оказаться весьма эффективным

для ее минимизации и, следовательно, для упрощения устрой-

ства, реализованного в соответствии с ней.

36

Рис. 1.22

12 0 rv । f i 9 0 I'T

0е* I'l o'

-T3 r!

Le 7 T7«

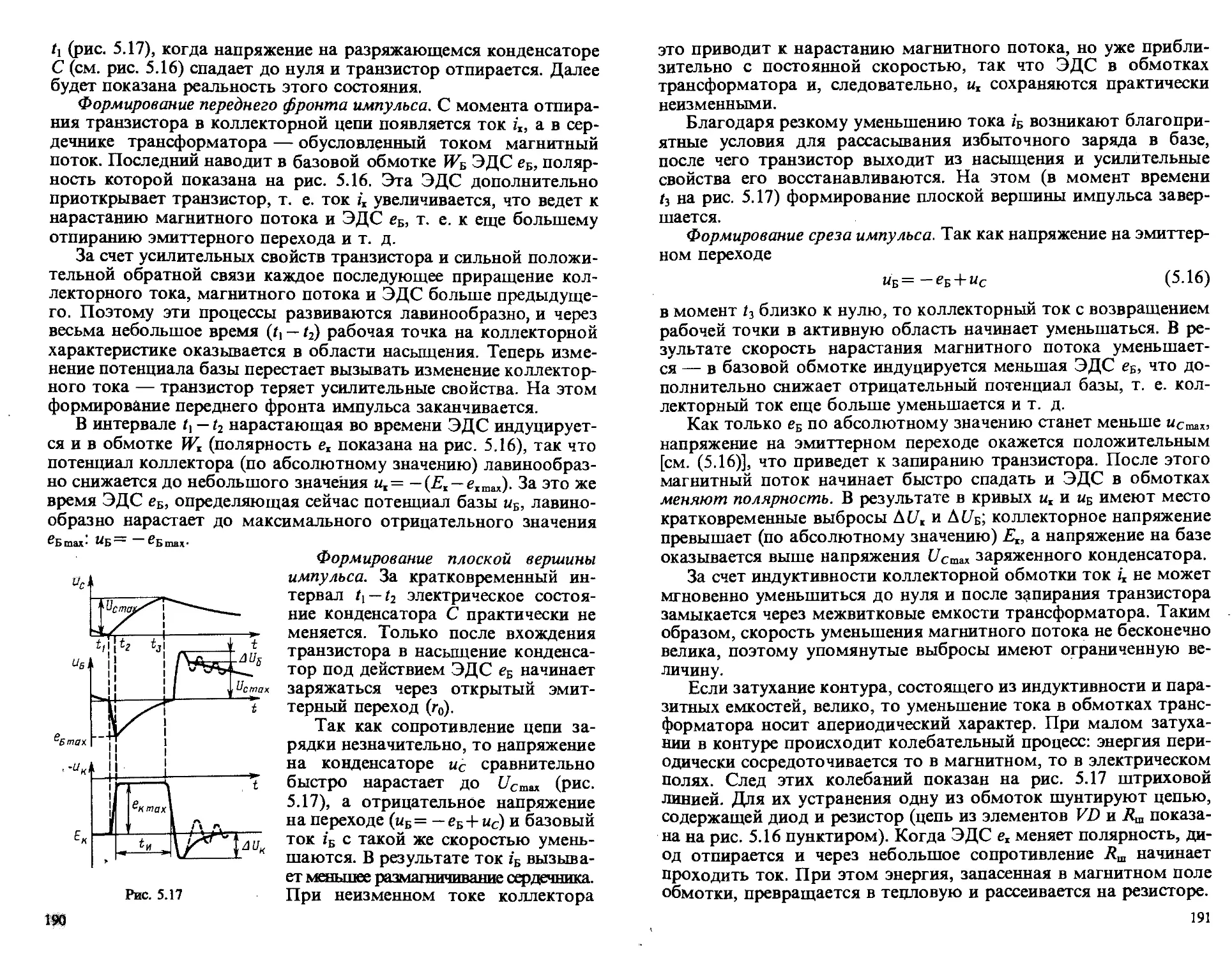

Такое доопределение функции произведем в ходе решения

ранее сформулированной задачи о возможной деформации кон-

струкции.

После перенесения данных из табл. 1.5 в карту Карно (рис.

1.22, а) заметим, что с целью минимизации выгодно доопреде-

лить функцию, положив ее равной 1 на наборах 5, 7, 15, 6, 2, 14,

10, 11 и равной 0 на наборах 4, 9 (рис. 1.22, 0._При этом ми-

нимизированное значение функции у=х3х1 + х2+х3х1. Такую функ-

цию должно реализовать устройство, включающее сигнал тревоги.

КОНТРОЛЬНЫЕ ВОПРОСЫ И УПРАЖНЕНИЯ

1. Определить амплитуду импульсного напряжения, если известно, что его

среднее значение = 1 В, импульсы длительностью = 1 мкс следуют с часто-

той/^ 1 кГц и имеют форму равнобедренных треугольников.

2. Как изменится спектр импульсной последовательности, если: а) увеличить

вдвое длительность импульса; б) уменьшить вдвое период следования импуль-

сов?

3. Пользуясь законами алгебры Буля, -Минимизировать следующие логичес-

кие функции: a) y=x3x2xj+x3X2*i+x3X2Xj+x3X2Xi; б) у = x3x2xi+х3х2-<1 +

+ X1X2Xl+XjX2Xl; в) у = Х4Х3Х2Х1 + Х4*3*2*1 + *4*3X2*I +X4X3*2*i; Г) У = Х4Х3Х2Х1 +

+ X4X3X2JCI +X4X3*2X| +X4XJX2X1; д) у = ХфХ3Х2Х1 +X4X2X2Xl+X4X3X2Xl+X4XiX2Xi.

4. С помощью карт Карно минимизировать логические функции yt, у2, Уз,

заданные табл. 1.7.

5. С помощью карт Карно минимизировать логические функции, заданные

табл. 1.8.

Таблица 1.7

Номер набора *3 *2 X1 У1 У1 УЗ

0 1 1 1 1 0 1

1 1 1 0 1 0 1

t 1 0 1 0 0 .

3 1 0 0 1 0 1

4 0 1 1 0 1 . —

5 0 1 0 0 1 —

6 0 0 1 0 1 —•

7 0 0 0 1 1 0

37

Таблица 1.8

Номер набора х4 х3 *2 *1 я У2 УЗ У4

0 1 1 1 1 1 1 1 —

1 1 1 1 0 1 1 1 1

2 1 1 0 1 "1 1 1 —

3 1 1 0 0 1 . 1 1 1

4 1 0 1 1 1 0 0 0

5 1 0 1 0 0 0 0 —

б 1 0 0 1 1 0 0 -—

7 1 0 0 0 0 0 0 —

8 0 1 1 1 1 1 0 0

9 0 1 1 0 1 1 0 -—

30 0 1 0 1 1 1 0 —

11 0 1 0 0 1 1 0 —

12 0 0 1 1 0 1 1 —

13 0 0 1 0 0 0 1 1

14 0 0 0 1 0 1 1 0

15 0 0 0 0 0 0 1 0

ГЛАВА 2

ИМПУЛЬСНЫЕ УСИЛИТЕЛИ и ключи

2.1. ОБЩИЕ СВЕДЕНИЯ

Импульсные усилители обеспечивают усиление импульсов

с допустимыми искажениями их формы. Ключевые каскады ис-

пользуются для коммутации электрических цепей, а также явля-

ются составной частью более сложных импульсных устройств.

Спектр импульсной последовательности весьма широк. По-

этому импульсные усилители делают резисторными, так как они

являются наиболее широкополосными.

Искажения формы импульсов можно оценить по переходной

характеристике усилителя (рис. 2.1, а). Она соответствует отклику

каскада на перепад напряжения (или тока) на входе. По переход-

ной характеристике в области малых времен (рис. 2.1, б) —

отклику каскада непосредственно на скачок — судят о времени tn

нарастания фронта импульса, добавляемом усилителем. По пере-

ходной характеристике в области больших времен (рис. 2.1, в) —

отклику каскада на постоянное напряжение после скачка — судят

об искажении плоской вершины импульса.

Время нарастания фронта, добавляемое самим усилителем,

1н = 2,2тв, (2.1)

где тв — постоянная времени усилителя в области малых времен

(верхних частот).

Постоянная времени тв и верхняя частота полосы пропуска-

ния /в (на которой усиление уменьшается в у/2 раз) связаны

Рис. 2.1

соотношением тв= 1/сов= 1/(2л/в). Используя выражение (2.1), по-

лучим