Author: Зотов В.Ю.

Tags: полупроводниковые устройства проектирование автоматизация вычислительная техника цифровые устройства

ISBN: 5-93517-136-8

Year: 2003

Text

В. Ю. Зотов

Проектирование цифровых устройств

на основе ПЛИС

Фирмы num

В САПР ____ |А_

WetMCI ISE

ББК 32.852.3

3 88

Рецензент каш) тех». наук В. Б. Стешенки

Зотов В. Ю.

$88 Проектирование цифровых устройств па основе ПЛИС фирмы XILINX в САПР

WcbPACK ISE. - М.: Горячая линия-Телеком. 2003. — 624 с., ил.

ISBN 5-93517-136-8.

Киша предназначена ,1ля самое гоя тельною изучения методики проектирования специали-

зированных цифровых устройств па базе программируемых •кимческпх ни гора и>иых схем

(ПЛИС) фирмы XjlinxB выполняемою в рамках свободно распространяемого пакета

WebPACK™ ISEru версии 5 I Применение САПР WebPACK ISIi позволяе! реализован» пол-

ный никл СКПОТИО1О проектирования устройшва пл рабочем столе разработчика, включая про-

|ра.ммнровапне кристалла. бет .мгпсрналы/Ш' aupar ла яршра.мхнюе обеспечение Рассмснрси

процесс созлаипя исходного описания разрабатываемого устроПсыза в схемотехнической п ал-

гор|Импческой (|юрмс Краткий справочник по у инфицированным библиотекам схемотехниче-

ского редактора. вюиочепиый к виде приложения, позволяет разработчикам использовать наи-

более привычный способ представления проема. Обзор шаблонов VHDL облегчает изучение

nolo языка описания аппаратуры и ускоряет создание законченных VHDL-oiuicauiui простои.

Приведено описание системы НОГ-модслировання ModdShn*w корпорации Model

Technology64 (одного из ширэъчеленип компании McmorGraphies®) и ее применения и процессе

функциональной п временной верификации разрабатываемого устройства.

Материал. изложенный в кише, также может быть использован в процессе самое гоя цель-

ного освоения системы проектирования Foundation1'1 ISE фирмы Xilinx.

Для нижепсрио-гехппческнх работников, может быть полезна студентам и аспирантам

специализирующимся в облает разработки цифровых систем.

ББК 32.852.3

Адрес издательства в Интернет www.techbook.ru

e-mail: radiosjit@nitu~net.ru

11ропзводст пенное издание

Зотов Валерий Юрьевич

Проектирование цифровых устройств

на основе ПЛИС фирмы XILINX в САПР WcbPACK ISE

Компьютерная вершка И. Н. Чумакова

Корректор Е.Н. Кочубеи

(iit.tviKKU художники В I Снгимкова

ДР № 1)71825 от 16 марта 1999 г.

Подписано в печать 05.05.2003. Формат 70x100/16

Усл. печ. л. 48Д Тираж 2000 экз. Изд. 136. Заказ № 1825

Отпечатано с готовых диапозитивов во ФГУП ИПК «Улышпвскин

Дом печати». 432980, г. Ульяновск, ул. Гончарова, 14

ISBN 5-93517-136-8 © Зотов В. Ю.. 2003

© Оформление излательегва

«Горячая линия-Телеком». 2003

Предисловие

Одной из тенденций развития цифровой текинки на современном этапе является широкое

применение ресурсов программируемой логики ие только для реализации отдельных блоков,

но и проектируемых устройств в целом, вплоть до создания систем на кристалле. Програм-

мируемые логические интегральные схемы (ПЛИС) и соответствующие средства проектиро-

вания, выпускаемые фирмой Xilinx®, позволяют выполнить жесткие требования, предъяв-

ляемые ко времени разработки, и в сжатые сроки создавать цифровые устройства и системы

с различным уровнем сложности и степенью интеграции.

Данное издание знакомит с технологией проектирования цифровых устройств па основе

ПЛИС фирмы Xilinx иа примере использования свободно распространяемого пакета

WebPACK™ ISE™ (Integrated Synthesis Environment), Несмотря на то, что этот пакет являет-

ся бесплатным, он представляет собой полнофункциональную систему автоматизированного

проектирования (САПР), которая позволяет выполнить все этапы разработки, начиная с соз-

дания проекта и заканчивая программированием кристалла. В отличие от свободно распро-

страняемых средств проектирования других фирм WebPACK ISE не имеет ограничений по

времени его использования.

Структура книги включает в себя пятнадцать глав и два приложения. В главе I лается

краткая характеристика продукции фирмы Xilinx, рассматриваются особенности перспектив-

ных серий ПЛИС и САПР. Во второй главе подробно описываются процедуры получения и

установки свободно распространяемой системы проектирования. Третья глава знакомит с

описанием характеристик и пользовательского интерфейса основных программ пакета

WebPACK ISE. Глава 4 начинается с обсуждения этапов процесса проектирования цифровых

устройств на основе ПЛИС. Затем рассматривается структура проекта и выполнение началь-

ных этапов разработки. Пятая глава посвящена вопросам создания исходных описаний про-

ектируемого устройства в схемотехнической форме и с применением языков HDL. Дальней-

шие этапы проектирования рассматриваются раздельно для случаев использования кристал-

лов семейств CPLD и FPGA. В главах 6-10 поочередно представлены этаны синтеза, реали-

зации, моделирования и загрузки конфигурационных данных проектов, выполняемых на базе

ПЛИС CPLD. Главы 11-15 освещают выполнение этих же этапов при использовании кри-

сталлов семейств FPGA.

Читателям, не имеющим опыта работы с системами разработки устройств на основе

ПЛИС, рекомендуется начинать изучение с более простого процесса проектирования, вы-

полняемого на базе кристаллов семейств CPLD. Для этого достаточно продолжать знакомст-

во с материалами книги в порядке следования номеров глав. Если же разработчика в первую

очередь интересует процесс проектирования цифровых устройств иа основе ПЛИС семейств

FPGA, то после изучения пятой главы следует перейти к гл. 11-15.

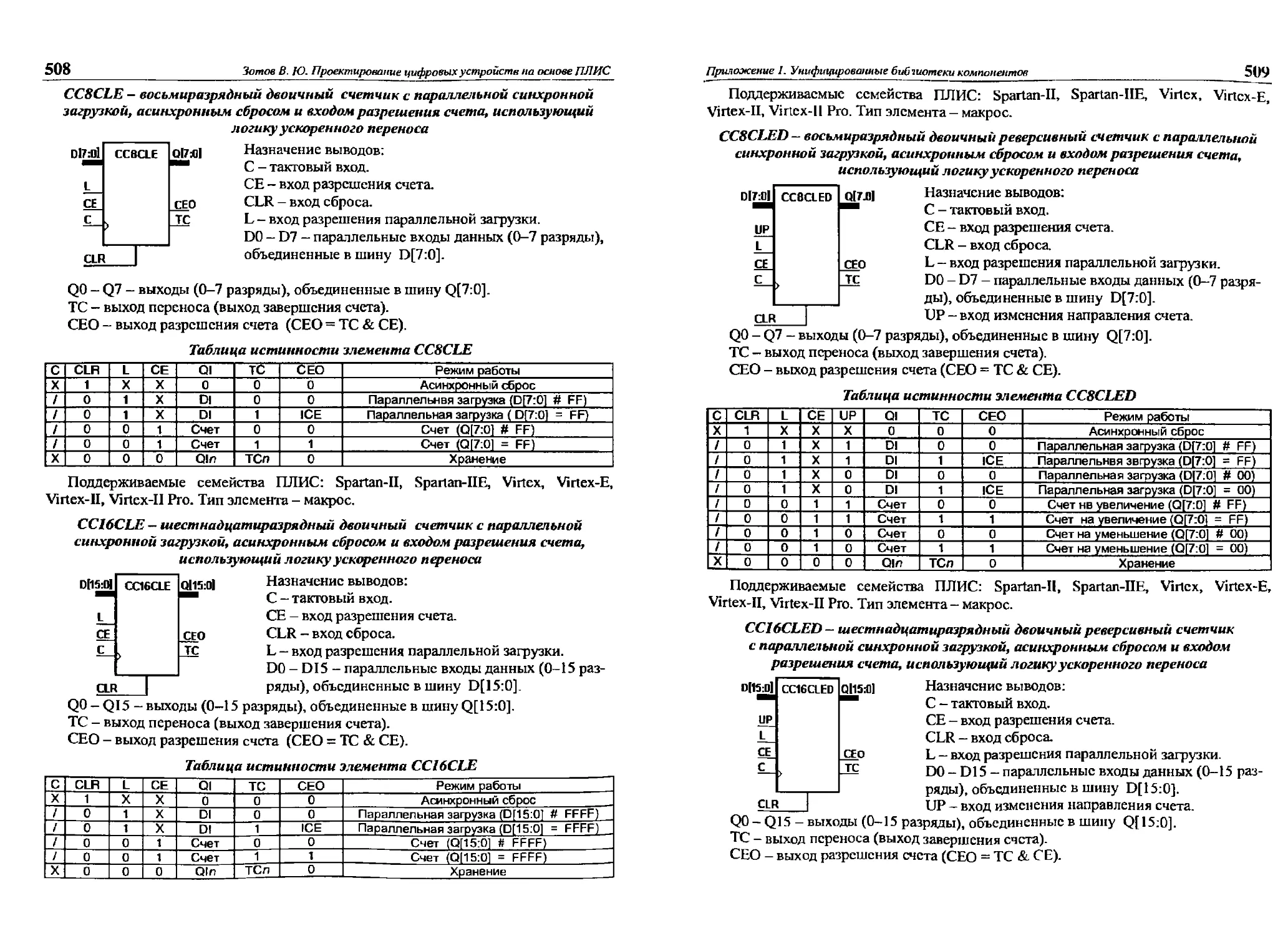

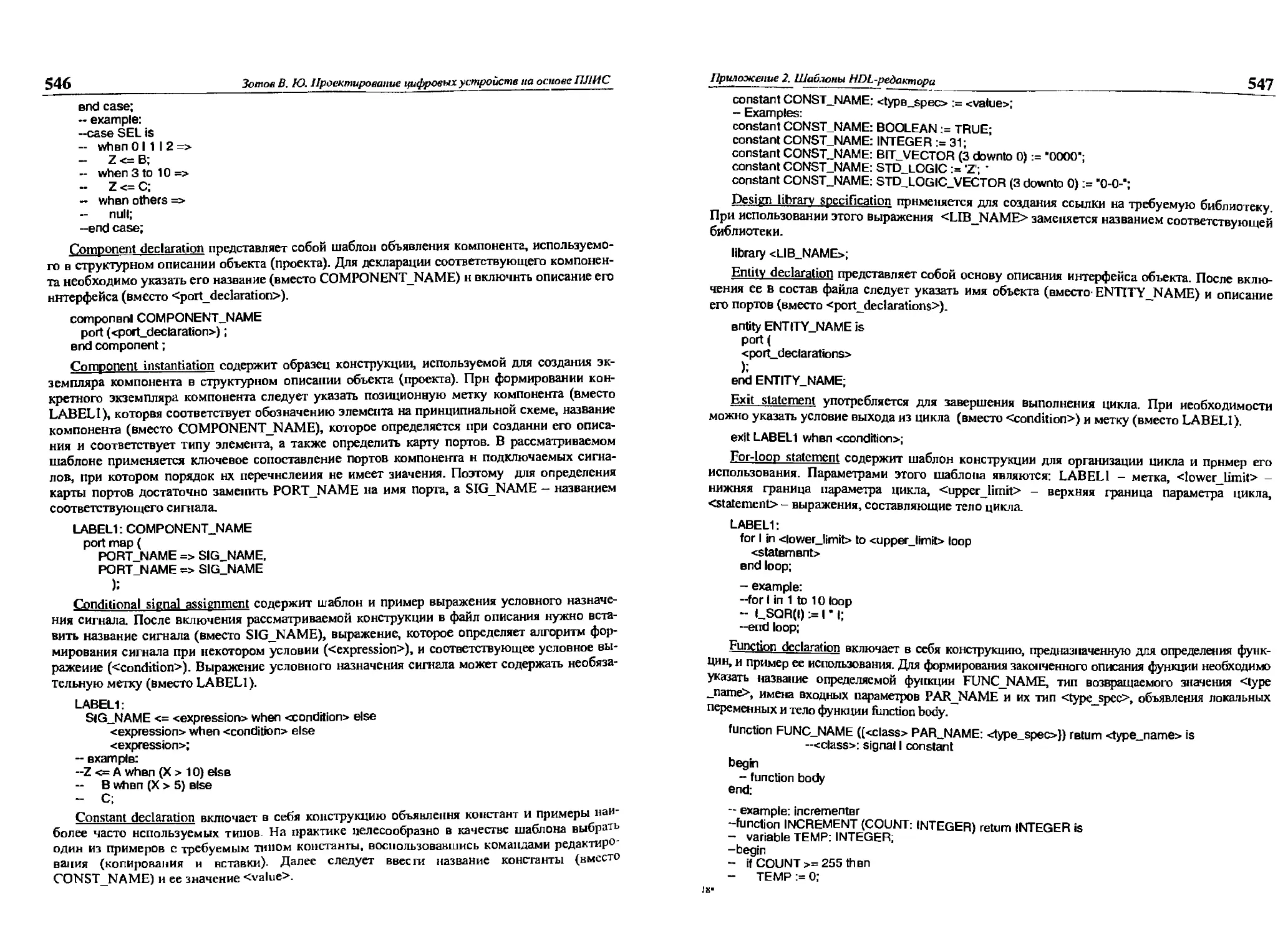

Приложение 1 представляет собой краткий справочник по основным функциональным

группам элементов унифицированных библиотек схемотехническою редактора. Для каждого

компонента приводится его условный графический образ, назначение выводов, таблица ис-

тинности и способ реализации. В Приложении 2 рассмотрены шаблоны языка VHDL, пре-

доставляемые интегрированным HDL-редактором пакета WebPACK ISE. Здесь же приводит-

ся описание процедуры создания разработчиком собственных I IDL-шаблонов.

Автор выражает благодарность замесшгелю генерального директора фирмы

1NL1NEGROUP (официального дистрибьютора фирмы Xilinx) Д. А. Кнышеву и ведущему

специалисту М. О. Кузелину за информационно-техническую поддержку в процессе работы

Над книгой.

1. Характеристика основных семейств ПЛИС

и средств проектирования, выпускаемых

фирмой Xilinx

1.1. Общая характеристика ПЛИС фирмы Xilinx

Программируемые логические интегральные схемы (ПЛИС) все более широко

используются для создания цифровых систем различного назначения. Фирма Xilinx,

являясь ведущим мировым производителем ПЛИС, предоставляет разработчикам

широкий спектр кристаллов с различной технологией производства, степенью инте-

грации, архитектурой, быстродействием, потребляемой мощностью и напряжением

питания, выпускаемых в различных типах корпусов и в нескольких вариантах ис-

полнения, включая промышленное, военное и радиационностойкое [1-8]. Кристал-

лы, выпускаемые фирмой Xilinx, в полной мерс реализуют преимущества ПЛИС по

сравнению с "жесткой логикой":

• высокое быстродействие;

• возможность перепрограммирования непосредственно в системе;

• высокая степень интеграции, позволяющая разместить цифровое устройство в

одном кристалле и тем самым снизить время и затраты на трассировку и произ-

водство печатных плат;

• сокращение времени цикла разработки и производства устройства;

• наличие мощных инструментов САПР, позволяющих устранить возможные

ошибки в процессе проектирования устройства;

• сравнительно низкая стоимость (в пересчете на один логический вентиль).

В настоящее время каталог продукции фирмы Xilinx включает в себя пять серий

ПЛИС с архитектурой FPGA (Field Programmable Gate Array), две серии кристаллов

CPLD (Complex Programmable Logic Device) и две серии ПЗУ/ППЗУ, предназначен-

ные для хранения конфигурационных данных.

В кристаллах CPLD конфигурационные данные хранятся во внутренней энерго-

независимой памяти. Соответствующая информация заносится в процессе програм-

мирования ПЛИС, которое может осуществляться непосредственно в системе с по-

мощью загрузочного кабеля, подключаемого к JTAG-nopiy. В состав этого сегмента

ПЛИС, выпускаемых фирмой Xilinx, входят следующие серии кристаллов CPLD:

• ХС9500, представленная семействами ХС9500, XC9500XL, XC9500XV;

• CoolRunncr™, содержащая семейства CoolRunner XPLA3™ и CoolRunncr-II.

ПЛИС серий FPGA выполнены на основе статического ОЗУ. Так как информация о

конфигурации кристалла записывается во внутреннее "теневое" ОЗУ, то при выключении

источника питания эти данные не сохраняются. Поэтому для хранения конфигурацион-

ной последовательности используются внешние элементы ПЗУ и ППЗУ, данные из кото-

рых заносятся в “теневое” ОЗУ в процессе инициализации ПЛИС, выполняемой при

включении напряжения питания или подаче специального сигнала. Линейка выпускае-

мых кристаллов FPGA представлена следующими сериями:

I. Характеристика основных семейств ПЛИС и средств проектирования 5

• Spartan™, включающей семейства Spartan, SpartanXL, Spartan-]] и Spartan-UE;

• Virtex™, состоящей из семейств Virtex, Virtex-E, Virtcx-11 и Virtex-II Pro™;

• XC4000, содержащей семейства ХС4000Е, ХС4000ЕХ, XC4000XL, XC4000XLA

XC4000XV;

• ХС5200;

• ХС3000, включающей семейства ХС3000А. XC3000L, ХСЗЮОА, XC3100L.

Для хранения конфигурационных данных кристаллов серий FPGA фирма Xilinx

предоставляет следующие разновидности ПЗУ:

• серию однократно программируемых ПЗУ ХС1700;

• серию перепрограммируемых в системе ППЗУ ХС18V00.

Учитывая, что серии ХСЗООО, ХС5200 и ХС4000 считаются морально устарев-

шими, соответствующие семейства далее не рассматриваются. Несмотря на то, что

кристаллы этих серий продолжают выпускаться, в большинстве своем они не реко-

мендуются для использования в новых проектах. Вместо них следует использовать

ПЛИС семейств Spartan и Virtex.

В последующих разделах рассматриваются характерные особенности актуаль-

ных (рекомендуемых для применения в новых разработках) серий ПЛИС.

1.2. Краткая характеристика основных семейств ПЛИС

CPLD фирмы Xilinx

1.2.1. Серия ХС9500

Серия ХС9500 включает в себя три семейства ПЛИС CPLD, основанных на тех-

нологии производства Fast Flash. В состав семейства ХС9500 входят шесть типов

ПЛИС емкостью от 36 до 288 макроячеек (соответственно от 800 до 6400 эквива-

лентных логических вентилей), выпускаемых в различных корпусах. Отличитель-

ными особенностями этого семейства являются;

• возможность реализации проектов с системными частотами до 125 МГц;

минимальная задержка распространения сигнала от входного контакта до выход-

ного через комбинационную логику - 5 нс;

• возможность раздельного управления длительностью фронтов выходных сигна-

лов для каждого вывода ПЛИС, позволяющая снизить уровень помех на выходах

кристалла;

• использование передовых технологий защиты конфигурационных данных от

несанкционированного копирования и случайного стирания;

• возможности фиксации пользовательских выводов перед трассировкой;

• возможность установки программируемого режима пониженной потребляемой

мощности для каждой макроячейки;

• не менее 10 000 циклов перепрограммирования;

• гарантированный срок хранения запрограммированной конфигурации не менее

20 лет;

* полная поддержка протокола периферийного сканирования в соответствии со

стандартом IEEE Ski 1149.1 (J TAG);

Зотов В. Ю. Проектирование цифровых устройств на основе ПЛИС

сравнительно мощные выходные буферы, обеспечивающие максимальный ток

до 24 мА;

совместимость с 3.3 В и 5 В логикой по входу и выходу, позволяющая использо-

вать ПЛИС в схемах со смешанным питанием;

напряжение питания ядра кристалла - 5 В.

Архитектура ПЛИС семейства ХС9500 показана па рис. 1.1. Ес основу составля-

хг совокупность функциональных блоков (Function Block, FB), блоков ввода/вывода

Input/Output block, ЮВ), и быстродействующая переключающая матрица. Количе-

тво функциональных блоков и блоков ввода/вывода определяется типом кристалла.

JTAG f

Порт]

(V

Е

Рис. 1.1. Архитектура ПЛИС семейства ХС9500

Каждый функциональный блок включает в себя программируемую матрицу ло-

гических произведений, распределитель термов и восемнадцать независимых мак-

роячеек. Матрица логических произведений Позволяет формировать до 90 термов на

основе 72 прямых и инверсных сигналов, полученных из 36 входных сигналов

функционального блока. Распределитель термов выполняет функции назначения

термов для всех макроячеек. Каждая макроячейка позволяет реализовать как комби-

наторную, так и регистровую функцию.

Блоки ввода/вывода предназначены для организации интерфейса между внут-

ренними сигналами кристалла и выводами ПЛИС. Они выполняют функции буфе-

ризации всех входных и выходных сигналов, управления выходами и формирования

программируемого "общего" вывода.

Быстродействующая переключающая матрица обеспечивает коммутацию сигна-

лов, покупающих из блоков ввода/вывода н выходов функциональных блоков, на

входы FB с минимальными задержками.

L Характеристика основных семейств ПЛИС и средств проектирования 7

Семейство XC9500XL является результатом дальнейшего развития ПЛИС ХС9500 на

основе применения технологии 0.35 мкм. Общая архитектура кристаллов XC9500XL не

отличается от предшествующего семейства. Изменения коснулись отдельных ее элемен-

тов. Основными отличиями семейства XC9500XL от ХС9500 являются:

• снижение напряжения питания "ядра" кристалла до 3.3 В;

• повышение производительности (возможность реализации проектов с систем-

ными частотами до 208 МГц);

• расширение возможностей функционального блока;

• применение усовершенствованной матрицы переключений Fast CONNECT™ II;

• наличие схем удержания последнего состояния в блоках ввода/вывода;

• применение усовершенствованных технологий защиты конфигурационных дан-

ных от несанкционированного копирования и случайного стирания;

• расширенная линейка типов корпусов, включающая корпуса малого размера

VQFP, TQFP и CSP (Chip Scale Package).

• совместимость по входу со стандартами сигналов 2.5 В, 3.3 В и 5 В и по выхо-

ду - с 2.5 В и 3.3 В;

• снижение стоимости кристаллов.

Постоянное совершенствование технологии производства обусловило появление

семейства XC9500XV, оптимизированного для применения в высокоскоростных

системах с напряжением питания 2.5 В. Кристаллы семейства XC9500XV в полной

мере реализуют перечисленные возможности предыдущего семейства и, кроме того,

обладают следующими преимуществами по сравнению с XC9500XL:

• более высокой производительностью, которая, в частности, выражается в повы-

шении системных частот до 275 МГц;

• организацией блоков ввода/вывода в виде банков в кристаллах с большим коли-

чеством ячеек;

• пониженной потребляемой мощностью;

• совместимостью по входу со стандартами сигналов 1.8 В, 2.5 В и 3.3 В, по выхо-

ду-с 1.8 В и 2.5 В.

Семейства XC9500XL и XC9500XV в отличие от ХС9500 содержат по четыре

типа кристаллов с логической емкостью 36, 72, 144 и 288 макроячеек.

ПЛИС всех семейств серии ХС9500 обладают совместимостью по выводам в

одинаковых корпусах. Кристаллы этой серии рекомендуется применять для реали-

зации логических функций многих переменных при небольшом количестве тригге-

ров, например, для построения специализированных быстродействующих дешифра-

торов, мультиплексоров, счетчиков, арифметико-логических устройств.

1.2.2. Серия CoolRunner

Серия CoolRunner представлена семействами ПЛИС CoolRunner XPLA3

(extended Programmable Logic Array), выпускаемых no технологии EEPROM 0.35

мкм, и CoolRunner-Il с технологией производства 0.18 мкм.

; Зотов В. Ю. Проектирование цифровых устройств на основе ПЛИС

В состав семейства CooIRunner XPLA3 входят шесть типов ПЛИС емкостью

it 32 до 512 макрояческ (соответственно от 800 до 12800 эквивалентных логиче-

:ких вентилей).

Кристаллы этого семейства характеризуются следующими особенностями:

। применение технологии FZP™ (Fast Zero Power), обеспечивающее достижение

минимального уровня потребляемой мощности в сочетании с высоким быстро-

действием;

• возможность реализации проектов с системными частотами до 200 МГн;

• ультранизкое значение мощности, потребляемой в статическом режиме (не более

100 мкА);

• минимальная задержка распространения сигнала от входного контакта до выход-

ного через комбинационную логику - 5 нс;

• функция раздельного управления длительностью фронтов выходных сигналов

для каждого вывода ПЛИС, позволяющая снизить уровень помех па выходах

кристалла;

• использование передовой технологии защиты конфигурационных данных от не-

санкционированного копирования и случайного стирания;

• расширенные возможности фиксации пользовательских выводов перед выполнением

этапа реализации (Implementation) в сочетании с полной трассировкой проекта;

• наличие сигнала разрешения синхронизации в каждой макроячейке;

• возможность асинхронного сброса или установки триггера макроячейки;

• возможность комплексного асинхронного тактирования элементов проектиру-

емого устройства с использованием 20 тактовых сигналов, формируемых внутри

логического блока, и 4 глобальных тактовых сигналов, поступающих с выводов

кристалла;

• нс менее 1 000 циклов перепрограммирования;

• гарантированный срок хранения запрограммированной конфигурации не менее

20 лет;

• полная поддержка протокола периферийного сканирования в соответствии со

стандартом IEEE Std 1149.1 (JTAG);

• совместимость с 3.3 В и 5 В логикой по входу и выходу, позволяющая использо-

вать ПЛИС в схемах со смешанным питанием;

• расширенный типовой ряд используемых корпусов;

• возможность перепрограммирования в системе с напряжением питания 3 В;

я совместимость выходов ПЛИС со стандартом РС1 3.3 В;

• напряжение питания ядра кристалла составляет 3.3 В;

• все кристаллы обладают совместимостью по выводам при использовании

одинаковых корпусов.

На рис. 1.2 представлена архитектура ПЛИС семейства CooIRunner XPLA3.

В структурном отношении она практически нс отличается от архитектуры семейств

ХС9500 и включает в себя блоки ввода/вывода, функциональные блоки и быстро-

действующую переключающую матрицу. Принципиальные отличия состоят в спо-

собе реализации этих структурных элементов.

I. Характеристика основных семейств ПЛИС и средств проектирования 9

Функциональный

блок FB1

Функциональный

блок FB3

Функциональный

блок FBn-1

36,

.16

.16

36,

.16

,16

Функциональным

блок FB2

Функциональный

блок FB4

Блоки

Ввода/

вывода

ЮВ

PLA-

матрица

МС1

МС2

МС16

Функциональный

блок FBn

Р LA-

матрица

МС1

МС2

МС16г—

Блоки

ввода/

вывода

ЮВ

Рис. 1,2. Архитектура ПЛИС семейства CooIRunner XPLA3

В состав каждого функционального блока входят программируемая PLA-матрица

логических произведений и шестнадцать независимых макроячеек. Использование

PLA-матрииы позволяет оптимизировать разделение н совместное использование

ресурсов кристалла при реализации проекта. Ее 36 прямых и инверсных входов,

подключенных непосредственно к выходам переключающей матрицы, позволяют

сформировать 48 термов, часть которых может использоваться в качестве управ-

ляющих сигналов для любой макроячейки функционального блока. Для использова-

ния в макроячейках дополнительных термов применяются специальные мультип-

лексоры VFM (Variable Function Multiplexer). Каждая макроячейка может быть

сконфигурирована для выполнения как комбинаторной, так и регистровой функции,

причем триггер, входящий в ес состав, может быть реализован как D- или Т-триггер

или как защелка. Коммутация сигналов, поступающих из блоков ввода/вывода,

входных и выходных сигналов функциональных блоков осуществляется с помощью

переключающей матрицы Zero-power Interconnect Array (Z1A), обеспечивающей ми-

нимизацию потребляемой мощности в сочетании с высоким быстродействием.

Семейство CoolRunncr-II представляет собой новое поколение ПЛИС с архитек-

турой XPLA3. использующих технологию FZP. По сравнению с семейством

CooIRunner XPLA3 кристаллы CoolRunncr-II обладают следующими отличиями:

• напряжение питания ядра кристалла составляет 1.8 В;

• более высокая производительность, позволяющая реализовать проекты с

системными частотами до 303 МГц;

• оптимизированная архитектура, обеспечивающая повышение эффективности

процесса логического синтеза;

О Зотов В. Ю. Проектирование цифровых устройств на основе ПЛИС

увеличение быстродействия проектируемых устройств за счет использования

триггеров, тактируемых фронтом и спадом сигнала синхронизации;

применение усовершенствованной коммутационной матрицы Advanced Interconnect

Matrix (AIM) обеспечивает высокую скорость переключений при низкой

потребляемой мощности;

। наличие встроенного делителя тактового сигнала с коэффициентами деления 2,

4,6, 8, 10, 12, 14, 16;

> использование методики CooICLOCK, позволяющей добиться снижения потреб-

ляемой мощности за счет сочетания деления тактовой частоты и применения

триггеров, тактируемых фронтом и спадом сигнала синхронизации;

• организация блоков ввода/вывода в виде банков в кристаллах с большим

количеством макроячеек;

в блоках ввода/вывода имеется возможность выборочной установки во входных

цепях триггеров Шмидта, обеспечивающих снижение влияния помех;

• применение технологии DataGATE позволяет добиться дополнительного умень-

шения потребляемой мощности за счет блокировки неактуальных или неизмс-

ияюшихся сигналов в ячейках ввода/вывода;

Цепи периферийного сканирования

Рис. 1.3. Архитектура кристаллов семейства CooIRunner-Il

• возможность формирования выходов с открытым стоком;

• расширенный типовой ряд используемых корпусов, включающий Chip Scale

Package (CSP), BGA, Fine Line BGA.TQFP, PQFP, VQFP и PLCC;

• четыре независимых уровня защиты конфигурационных данных от несанкцио-

нированного копирования, обеспечивающих охрану прав интеллектуальной соб-

ственности;

• поддержка конфигурирования по стандарту IEEE Std 1532;

/. Характеристика основных семейств ПЛИС и средств проектирования 1 j

• возможность перепрограммирования в системе с напряжением питания 1.8 В;

• совместимость с логическими уровнями стандартов цифровых сигналов 1.5 В,

1.8 В, 2.5 В и 3.3 В позволяет реализовывать устройства со смешанным

питанием.

ПЛИС серии CoolRunner, обладающие микро.мошным потреблением, рекоменду-

ется использовать, в первую очередь, для применения в мобильных системах, с ав-

тономными источниками питания ограниченного ресурса. Кристаллы этих семейств

позволяют реализовать, например, специализированные контроллеры, в том числе

для организации различных интерфейсов ввода/вывода, кодирующие и декодирую-

щие устройства.

1.3. Краткая характеристика основных семейств ПЛИС

FPGA фирмы Xilinx

1.3.1. Серия Virtex

Семейство Virtex представлено девятью типами кристаллов, содержащими от

384 до 6144 конфигурируемых логических блоков (соответственно от 50 000 до

1 000 000 системных вентилей), которые производятся по технологии 0.22 мкм с

пятислойной металлизацией.

Характерными особенностями семейства Virtex являются:

• высокая производительность, допускающая реализацию проектов с системными

частотами до 200 МГц;

• применение четырех специальных схем цифровой автоподстройки задержек

(DDL), выполняющих функции умножения, деления и сдвига фаз тактовых час-

тот, обеспечивает расширенные возможности управления синхронизацией;

• использование четырех глобальных сетей предоставляет возможность распреде-

ления сигналов синхронизации внутри кристаллов с малыми разбегами фронтов;

• наличие двух видов внутренней оперативной памяти: распределенной Distributed

RAM, реализуемой на базе четырсхвходовых таблиц преобразования (LookUp

Table, LUT) конфигурируемых логических блоков (Configurable Logic Block,

CLB), и встроенной блочной памяти Block SelectRAM, которая может быть орга-

низована как синхронное двухпортовое ОЗУ;

• возможность реализации быстрых внутренних интерфейсов к внешним

высокопроизводительным элементам памяти (ОЗУ или ПЗУ);

• применение специальной логики ускоренного переноса для выполнения

высокоскоростных арифметических операций;

• специальная поддержка реализации умножителей;

• наличие цепочек каскадирования обеспечивает возможность реализации функ-

ций с большим количеством входных переменных;

• наличие внутренних шин с тремя состояниями;

• полная поддержка протокола периферийного сканирования в соответствии со

стандартом IEEE Std 1149.1;

• совместимость со стандартами PCI 3.3 В 66 МГц;

2 Зотов В. Ю. Проектирование цифровых устройств на основе ПЛИС

поддержка функции Hot-swap для Compact PCI;

использование технологии Virtex Sclectl/O™ позволяет поддерживать шестна-

дцать цифровых сигнальных стандартов по вводу-выводу, в частности, LVTTL,

LVCMOS2, PCI33_5, PCI66_5, PCI33_3, РС166_3, GTL, GTL+, SSTL2(I),

SSTL2(II), SSTL3(I), SSTL3(II), HSTL(I), HSTL(U), HSTL(HI), AGP, CTT;

неограниченное количество циклов загрузки конфигурационных данных;

четыре режима конфигурирования ПЛИС (Slave-serial, Master-serial, SelectMAP.

Boundary-scan mode);

напряжение питания ядра кристалла составляет 2.5 В.

Основу архитектуры кристаллов Virtex составляет массив конфигурируемых ло-

ических блоков CLB, окруженных программируемыми блоками ввода/вывода ЮВ

ис. 1.4). Кроме того, в нес входят схемы цифровой автоподстройки задержек DLL

। блоки выделенной памяти Block SelectRAM. Все соединения между основными

[рхитектурными элементами ПЛИС осуществляются с помощью иерархической

ггруктуры трассировочных ресурсов.

Блоки ввода/вывода

10В

Трассировочные ресурсы VersaRing

ш

£

га

и

Массив

конфигурируемых

логических

блоков

CLB

со

та

с

£

га

и

га

о

га

i

о

§

Трассировочные ресурсы VersaRing ь

Блоки ввода/вывода

ЮВ

DLL

Рис. 1.4. Архитеюура кристаллов семейства Virtex

Конфигурируемый логический блок ПЛИС семейства Virtex состоит из двух сек-

ций, каждая из которых включает в себя две однотипные логические ячейки (Logic

Cell, LC). В состав логической ячейки входит чстырсхвходовый функциональный

генератор (таблица преобразований), триггерный элемент и логика ускоренного пс-

/ Характеристика основных семейств I'1ЛИС и средств проектирования 13

реноса. Кроме того, конфигурируемый логический блок содержит дополнительную

логику, позволяющую конфигурировать ресурсы функциональных генераторов для

реализации функций пяти и шести переменных. Основными элементами иерархиче-

ской структуры трассировочных ресурсов являются: трассировочные ресурсы обще-

го назначения, включающие главные трассировочные матрицы (General Routing

Matrix, GRM) и коммутационные цепи различного типа, локальные трассировочные

линии VersaBlock, окружающие каждый конфигурируемый логический блок, и до-

полнительные трассировочные ресурсы для коммутации блоков ввода/вывода

VersaRing.

Семейство Virtex-E, являющееся результатом дальнейшего развития архитектуры

Virtex на основе применения технологии 0.18 мкм с шестислойной металлизацией,

содержит тринадцать ПЛИС с логической емкостью от 384 до 16 224 конфигури-

руемых логических блоков (соответственно от 70 000 до 4 000 000 системных вен-

тилей). Семейство Virtex-E, обладая в полной мере возможностями предыдущего

семейства, имеет ряд существенных отличий по сравнению с Virtex:

• повышение быстродействия кристаллов позволяет выполнять па их основе про-

екты с системными частотами до 240 МГц;

• увеличение максимальной эквивалентной логической ёмкости в 3 раза;

• расширение максимальной ёмкости блочной памяти до 1120 Кбит;

• максимальный объем распределенной памяти составляет 1 Мбит;

• двукратное увеличение количества блоков цифровой автоподстройки задержек

DLL (до восьми) предоставляет дополнительные возможности для организации

эффективного механизма управления синхронизацией;

• увеличение максимального числа блоков ввода-вывода (до 804) и их быстродей-

ствия в 1.5 раза;

• усовершенствованная технология Virtex Sclectl/O обеспечивает поддержку 20

различных стандартов сигналов, включающих LVTTL, LVCMOS2, LVCMOS18,

PCI33_3, PCI66_3, GTL, GTL+, SSTL2(I), SSTL2(II), SSTL3(I), SSTL3(II),

HSTL(I), HSTL(II), HSTL(III), AGP, TTL, LVDS, BLVDS, LVPECL, TTL;

• применение новых типов корпусов, позволяющих, в частности, значительно уве-

личить количество пользовательских выводов кристалла;

• снижение напряжения питания "ядра" кристалла до 1.8 В.

Архитектура ПЛИС семейства Virtex-E содержит те же структурные элементы,

что и кристаллы Virtex, но изменено их взаимное расположение (рис. 1.5). Модифи-

кация топологии ресурсов кристаллов позволяет добиться увеличения ёмкости

блочной памяти.

Семейство Virtex-II является представителем нового поколения высокопро-

изводительных кристаллов большой емкости, реализующего концепцию Platform

FPGA, согласно которой ПЛИС становится основным компонентом цифровой сис-

темы. В состав этого семейства входят одиннадцать типов кристаллов, производи-

мых по технологии 0,15/0,12 мкм с восьмислойпой металлизацией.

14

Зотов В Ю Проектирование цифровых устройств на основе ПЛИС

DLL DLL DLL DLL

Трассировочные ресурсы VersaRing

Трассировочные ресурсы VersaRing

DLL DLL

DLL DLL

Рис. 1.5. Архитектура кристаллов семейства Virtex-E

Основные технические характеристики Virtex-11 по праву позволяют считать его

наиболее перспективным и широко используемым в настоящее время семейством

FPGA для построения систем передачи данных и цифровой обработки сигналов:

• высокое быстродействие, позволяющее применять внутренние тактовые частоты

до 420 МГц;

• широкий диапазон логической емкости - от 64 до 11648 конфигурируемых

логических блоков (соответственно от 40 000 до 8 000 000 системных вентилей)

на кристалле;

• высокая скорость обмена данными, достигающая более 840 Мб/с по одному ка-

налу ввода/вывода стандарта LVDS (Low-Voltage Differential Signaling);

• расширенный объем внутренней оперативной памяти двух видов: распределен-

ной Distributed RAM, реализуемой на базе четырсхвходовых таблиц преобразо-

вания LUT конфигурируемых логических блоков CLB, до 1,5 Мбит и встроенной

блочной памяти Block SclcctRAM, выполненной в виде секций двухпортового

ОЗУ по 18 Кбит, до 3 Мбит;

• поддержка высокоскоростных интерфейсов к модулям внешней памяти, в част-

ности, к DDR-SDRAM, FSRAM. QDR™-SRAM, Sigma RAM;

• наличие встроенной логики ускоренного переноса, предназначенной для выпол-

нения высокоскоростных арифметических операций;

• включение в структуру кристаллов блоков аппаратных умножителей 18x18 бит,

позволяющих реализовать быстродействующие устройства, использующие функ-

ции умножения;

/. Характеристика основных семейств /UIHC и средств проектирования 15

• применение специальной логики каскадирования для реализации функций с

большим количеством входных переменных;

• наличие встроенных быстродействующих цифровых модулей управления син-

хронизацией (Digital Clock Manager, DCM), выполняющих точную подстройку

фронтов тактовых сигналов как внутри кристалла, так и на уровне печатной пла-

ты, умножение и деление частоты синхросигналов, а также сдвиг фаз с высоким

разрешением;

• внедрение технологии внутренних соединений Active Interconnect™ Technology,

основанной на сегментированной структуре трассировки четвертого поколения,

позволяет получить прогнозируемые задержки распространения сигналов,

независящие от коэффициента разветвления по выходу;

• возможность программирования нагрузочной способности каждого вывода в

диапазоне от 2 до 24 мА;

• применение блоков ввода/вывода с программируемым импедансом позволяет

исключить использование внешних согласующих резисторов;

• совместимость со стандартами шин PCI-133 МГц, PCl-бб МГц и PCI-33 МГц;

• поддержка стандартов дифференциальной передачи сигналов со скоростью

840 Мбит/с LVDS (Low-Voltage Differential Signaling), BLVDS (Bus LVDS), LDT

(Lightning Data Trans-port), LVPECL (Low-Voltage Posi-tive Emitter-Coupled

Logic);

• неограниченное количество циклов загрузки конфигурационных данных;

• пять режимов конфигурирования ПЛИС (подчиненный последовательный режим

Slave-serial, ведущий последовательный режим Master-serial, подчиненный па-

раллельный режим Slave SelectMAP, ведущий параллельный режим Master Select

МАР, периферийного сканирования Boundary-scan mode (IEEE 1532));

• надежная система защиты конфигурационных данных от несанкционированного

копирования, основанная на шифровании конфигурационной последовательно-

сти по стандарту TRIPLE Data Encryption Standard (DES);

• возможность частичного реконфигурирования кристаллов;

• поддержка периферийного сканирования в соответствии со спецификацией

стандарта IEEE Std 1149.1 и конфигурирования по стандарту IEEE Std 1532;

• напряжение питания ядра кристалла 1.5 В, блоков ввода-вывода от 1.5 до 3.3 В

(в зависимости от выбранного сигнального стандарта).

Архитектура ПЛИС семейства Virtex-П представляет собой регулярную структу-

ру, основными элементами которой являются: блоки ввода/вывода ЮВ, конфигури-

руемые логические блоки CLB, секции блочной памяти Block SclectRAM, блоки

аппаратных умножителей, цифровые модули управления синхронизацией DCM и

трассировочные ресурсы (рис. 1.6).

Программируемые блоки ввода-вывода ЮВ выполняют функции коммутации и

буферизации сигналов, поступающих со входных контактов кристалла на входы

конфигурируемых логических блоков и с выходов CLB на выходные контакты

ПЛИС. Использование в блоках ЮВ встроенных входных и выходных регистров с

удвоенной скоростью передачи данных обеспечивает реализацию высокоскорост-

ных режимов передачи информации в проектируемой системе.

Каждый конфигурируемый логический блок включает в себя четыре одинаковые

секции и два буфера с тремя состояниями. В состав каждой секции CLB входят два

функциональных генератора, реализованных в виде четырехвходовых таблиц пре-

образования LUT, два запоминающих элемента, конфигурируемых как D-триггеры

или триггеры-защелки, и логика ускоренного переноса и каскадирования.

Каждый блок памяти Block SelectRAM представляет собой двухпортовое ОЗУ с

информационной емкостью 18 Кбит, которое может конфигурироваться с различной

организацией (разрядностью шины данных и шины адреса). Каскадное объединение

блоков Block SelectRAM позволяет реализовать массивы оперативной памяти боль-

шого объема непосредственно на кристалле.

Блоки аппаратных умножителей сопряжены с соседними блоками памяти Block

SelectRAM. Такая структура позволяет нс только использовать умножитель с раз-

личными источниками двух восемнадцатиразрядных операндов, но и оптимально

реализовать выполнение операции умножения с содержимым одного из портов

блочного ОЗУ.

Цифровые модули управления синхронизацией DCM позволяют наиболее эф-

фективно организовать формирование сетки тактовых сигналов с требуемыми ха-

рактеристиками, используя операции синтеза частот и сдвига фаз формируемых

сигналов. В модулях DCM применяется дискретный механизм подстройки фазы с

шагом, составляющим 1/256 тактового периода. Модули DCM выполняют функции

устранения временных перекосов при распространении сигналов синхронизации нс

только внутри кристалла, по и на печатной плате. Кроме того, каждый DCM спосо-

бен управлять четырьмя глобальными тактовыми мультиплексорами, нозволяющи-

/. Характеристика основных семейств ПЛИС и средств проектирования ~Y]

ми выбирать один из двух входов синхронизации и переключать их без создания

импульсной помехи.

Новое поколение программируемых трассировочных ресурсов, основанных на

технологии Active Interconnect Technology, осуществляет коммутацию рассмотрен-

ных выше элементов архитектуры кристаллов. Трассировочные ресурсы образуют

иерархическую структуру, основным элементом которой является главная трассиро-

вочная матрица GRM. Все блоки ввода/вывода, конфигурируемые логические блоки,

секции блочной памяти, аппаратные умножители и цифровые модули управления

синхронизацией используют единую сеть внутренних соединений и единый доступ

к глобальной трассировочной матрице.

Применение технологии 0.13 мкм/0,09 мкм с девятислойной металлизацией вхо-

де дальнейшего совершенствования архитектуры Virtex-Il, позволившее разместить

на кристалле ядро процессора IBM® PowerPC® RISC, привело к созданию семейст-

ва более высокого уровня Virtex-П Pro. В состав этого семейства входят десять ти-

пов ПЛИС, которые содержат от 352 до 13904 конфигурируемых логических блоков.

Новое семейство обладает всеми характерными особенностями кристаллов

Virtcx-II, отличаясь от него рядом дополнительных преимуществ, среди которых,

прежде всего, следует выделить:

• наличие до двадцати четырех встроенных высокоскоростных приемопередатчи-

ков Rocket I/O™, основанных на технологии Mindspeed's SkyRail™ и обладаю-

щих скоростью обмена данными до 3.125 Мб/с;

• включение в архитектуру кристаллов до четырех процессорных блоков РРС405

(PowerPC RISC);

• увеличение максимального объема внутренней оперативной памяти каждого ви-

да: распределенного ОЗУ до 1,7 Мб и встроенного блочного ОЗУ до 10 Мб;

• расширение максимальной логической емкости кристаллов до 13904 конфигури-

руемых логических блоков;

• более чем трехкратное увеличение количества блоков аппаратных восемнадцати-

разрядных умножителей;

• использование технологии SelectI/0-Ultra™ обеспечивает поддержку семнадцати

однополюсных и пяти дифференциальных сигнальных стандартов.

Архитектурные особенности ПЛИС семейства Virtcx-11 Pro позволяют опти-

мальным образом выполнять на их основе разработку "систем на кристалле" (Sys-

tem-on-Chip). При этом в одном корпусе ПЛИС удается полностью реализовать

функции процессора и всех периферийных устройств, включая различные интер-

фейсы ввода/вывода. Гибкая комплексная система трассировочных ресурсов кри-

сталлов семейства Virtcx-11 Pro создает эффективный механизм сопряжения процес-

сорных блоков и окружающей программируемой логики. Реализация процессорных

функций на аппаратном уровне, в виде встроенных блоков РРС405 (PowerPC RISC),

обеспечивает достижение высокой производительности проектируемых систем.

Архитектура ПЛИС Virtcx-11 Pro отличается от предшествующего семейства в

основном наличием интегрированных процессорных блоков PowerPC и блоков

приемопередатчиков Rocket I/O (рис. 1.7).

ПЛИС семейств Virtex могут успешно использоваться для создания высокоско-

ростных вычислительных и телекоммутационных устройств, шинных интерфейсов

(например, PCI, PCI-X, FlexBus-4, USB, FireWire), сетевых устройств и контролле-

ров. Наличие аппаратных умножителей позволяет наиболее эффективно реализовы-

вать на основе ПЛИС семейства Virtex-П и Virtex-II Pro системы цифровой обработ-

ки сигналов.

1.3.2. Серия Spartan

В состав семейства Spartan входят пять типов кристаллов, содержащих от 100 до

784 конфигурируемых логических блоков (соответственно от 5 000 до 40 000 сис-

темных вентилей), выпускаемых по технологии 0.5 мкм с трехслойной металлиза-

цией, с напряжением питания 5 В. ПЛИС этого семейства предоставляют возмож-

ность реализации проектов с системными частотами до 80 МГц, обладающих со-

вместимостью по вводу/выводу с РС1, с использованием синхронного двухпортово-

го ОЗУ информационной емкостью от 3 Кбит до 25 Кбит и встроенной логики уско-

ренного переноса. Семейство SpartanXL включает пять кристаллов с аналогичными

ресурсами, технологией производства 0.35 мкм с пятислойной металлизацией и на-

пряжением питания 3.3 В, обладающих совместимостью с пятивольтовой логикой

по входам и выходам. ПЛИС семейств Spartan и SpartanXL имеют структуру, которая

базируется на архитектуре серии ХС4000, и неуклонно вытесняются более совер-

шенными семействами этой же серии. Поэтому более подробно характеристики кри-

сталлов семейств Spartan и SpartanXL нс обсуждаются.

Усовершенствование технологии производства и применение архитектуры се-

мейства Virtex (см. рис. 1.4) привело к созданию семейств Spartan-Il и Spartan-llE.

/. Характеристика основных семейств ПЛУС и средств проектирования 19

ПЛИС этих семейств присущи основные особенности кристаллов Virtex, рассмот-

ренные выше. Поэтому далее приводятся только те характеристики, в которых про-

являются отличия этих семейств. Семейство Spartan-П представлено шестью типами

кристаллов, выпускаемых по технологии 0.18/0.22 мкм с шестислойной металлиза-

цией. Для этого семейства характерны следующие показатели:

• диапазон логической ёмкости кристаллов составляет от 96 до 1176 конфигури-

руемых логических блоков (соответственно от 15 000 до 200 000 системных вен-

тилей);

• максимальный объем внутренней распределенной оперативной памяти

Distributed RAM, которая может быть реализована па базе четырехвходовых таб-

лиц преобразования LUT конфигурируемых логических блоков CLB, находится в

пределах от 6 до 75 Кбит;

• предельная информационная емкость встроенной блочной памяти Block

SelectRAM, организованной в виде секций ОЗУ по 4 Кбит, составляет от 16 до

56 Кбит;

• более низкая стоимость по сравнению с кристаллами семейства Virtex;

• напряжение питания ядра кристалла - 2.5 В.

Семейство Spartan-BE основано на технологии 0.18 мкм с шсстислойной метал-

лизацией. В настоящее время в это семейство входят семь типов кристаллов. Основ-

ными отличиями семейства Spartan-lIE от Spartan-Il являются:

• использование архитектурных и технологических особенностей семейства

Virtcx-E;

• увеличение верхней границы диапазона эквивалентной логической ёмкости кри-

сталлов до 3 456 конфигурируемых логических блоков (600 000 системных вен-

тилей);

• расширение максимальной емкости встроенной блочной памяти до 288 Кбит;

• возрастание максимально возможного объема ОЗУ, реализуемого в виде распре-

деленной памяти;

• повышение производительности кристаллов;

• увеличение количества пользовательских выводов кристаллов;

• поддержка девятнадцати сигнальных стандартов, включая LVTTL, LVCMOS,

HSTL, SSTL, AGP, CTT, GTL, LVDS и LVPECL;

• снижение потребляемой мощности;

• напряжение питания ядра кристалла - 1.8 В.

ПЛИС серии Spartan (прежде всего семейств Spartan-П и Spartan-ПЕ) представ-

ляют собой альтернативу применению специализированных интегральных схем

ASIC (applications specific integrated circuit). Кристаллы этой серии могут использо-

ваться, например, для реализации проектов, включающих блоки устройств цифро-

вой обработки сигналов, в том числе и DSP-процессоров, различных интерфейсов,

включая РС1 и USB, RISC-микропропсссоров, специализированных микроконтрол-

леров.

20 Зотов В. Ю. Проектирование цифровых устройств на основе ПЛИС

1.4. Обзор семейств конфигурационных ПЗУ и ППЗУ

фирмы Xilinx

1.4.1. Серия однократно программируемых ПЗУ ХС1700

Серия однократно программируемых ПЗУ ХС1700 включает в себя шесть се-

мейств, отличающихся, прежде всего, напряжением питания и информационной

емкостью: ХС1700Е, XC1700EL, XC17S00, XC17S00XL, XC17S00A и XC17VO0.

Конфигурационные данные записываются в ПЗУ этой серии с помощью аппаратно-

го программатора, например, HW-130, выпускаемого фирмой Xilinx.

Семейство ХС1700Е составляют четыре типа ИС емкостью от 36 до 256 Кбит и

напряжением питания 5 В. ПЗУ этого семейства выпускаются в корпусах PDIP-8,

SOIC-8, VOIC-8 и PLCC-20.

В семейство XC1700EL входят четыре элемента постоянной памяти с информа-

ционной емкостью от 65 до 512 Кбит и напряжением питания 3.3 В. Это семейство

использует ту же линейку корпусов, что и предыдущее.

Семейство XC17S00 предназначено для хранения конфигурационных данных

ПЛИС семейства Spartan. Оно содержит пять типов ПЗУ с информационной емко-

стью от 65 до 524 Кбит и напряжением питания 5 В. ИС этого семейства выпуска-

ются в корпусах PDIP-8, VOIC-8 и SOIC-20.

В состав семейства XC17S00XL входят пять типов ИС, предназначенных для со-

вместной работы с кристаллами семейства Spartan-XL. Напряжение питания эле-

ментов этого семейства составляет 3.3 В. Диапазон информационной емкости и ти-

повой ряд используемых корпусов ПЗУ XC17SO0XL не отличаются от предыдущего

семейства.

Семейство XC17S00A представлено одиннадцатью типами ПЗУ с информацион-

ной емкостью от 197 до 1 875 Кбит и напряжением питания 3.3 В, которые предна-

значены для записи конфигурационной последовательности ПЛИС семейств

Spartan-II и Spartan-IIE. Элементы этого семейства выпускаются в корпусах PD1P-8,

SOIC-20, VOIC-8 и VQFP-44.

Семейство XC17V00 содержит пять типов ПЗУ большой емкости (от 1 до 16 Мбит)

е напряжением питания 3.3 В. ИС этого семейства выпускаются в корпусах VQFP-

44, PLCC-44, PLCC-20, VO1C-8 и SOIC-20.

1.4.2. Серия перепрограммируемых в системе ППЗУ XC18V00

Серия перепрограммируемых в системе ППЗУ XC18V00 представлена пятью

элементами с информационной емкостью от 256 Кбит до 4 Мбит и напряжением

питания 3 В, которые предназначены для хранения конфигурационной последова-

тельности ПЛИС семейств FPGA.

Отличительными особенностями этой серии являются:

• поддержка режимов последовательного и параллельного конфигурирования

ПЛИС с частотой до 33 МГц;

• совместимость по входу с уровнями сигналов 5В, 3.3 В и 2.5 В, по выходу - с 3.3 В

и 2.5 В;

• не менее 20 000 циклов перепрограммирования;

I. Характеристика основных семейств ПЛИС и средств проектирования

21

программирование и считывание информации с помощью унифицированных

загрузочных кабелей, используемых для конфигурирования ПЛИС фирмы Xilinx,

• полная поддержка протокола периферийного сканирования в соответствии со

стандартом IEEE Std 1149.1 (JTAG);

использование корпусов VQFP-44, PLCC-44, PLCC-20 и SOIC-20.

Болес подробная информация о ПЛИС и конфигурационной памяти, а также ре-

комендации по их применению содержится в [1-8].

1.5. Краткий обзор основных средств проектирования

фирмы Xilinx

Кроме широкого спектра ПЛИС, основанных на применении передовых техно-

логий производства, фирма Xilinx предоставляет современное программное обеспе-

чение, необходимое для разработки проектов и конфигурирования кристаллов.

В начале 2002 года завершен полный переход к новому поколению систем автомати-

зированного проектирования ISE™ (Integrated Synthesis Environment), которые до

того момента применялись в качестве альтернативы предыдущей серии САПР

Foundation Series™. Применение программных средств 1SE позволяет значительно

сократить время разработки и повысить уровень эффективности результатов за счет

применения усовершенствованных методов проектирования, алгоритмов синтеза,

размещения и трассировки проекта в кристалле.

Средства проектирования ISE выпускаются в четырех конфигурациях:

Foundation™ ISE, BaseX™ ISE Alliance™ ISE и WebPACK™ ISE. Основное отличие

между этими конфигурациями заключается в количестве поддерживаемых кристал-

лов и наборе дополнительных инструментов проектирования.

Программные средства Foundation ISE представляют собой наиболее полную

систему сквозного проектирования, которая поддерживает весь спектр ПЛИС, вы-

пускаемых фирмой Xilinx.

Экономичная конфигурация средств проектирования BaseX ISE имеет более низ-

кую стоимость по сравнению с Foundation ISE, но поддерживает не все типы ПЛИС.

Пакет BaseX ISE позволяет выполнять проекты на основе всех кристаллов семейств

CPLD и ПЛИС серий FPGA с логической емкостью не более 300 000 системных

вентилей.

Для сопряжения с САПР других производителей предназначена конфигурация

Alliance™ ISE. Она не содержит средств ввода исходных описаний проектов и синтеза.

Эта копфшурация поддерживает все кристаллы, предоставляемые фирмой Xilinx.

Свободно распространяемая (бесплатная) модификация САПР WebPACK ISE

поддерживает те же кристаллы, что и BaseX ISE. Основное отличие пакета WebPACK

ISE от конфигурации BaseX ISE состоит в отсутствии генератора логических ядер

CORE Generator и топологического редактора FPGA Editor.

Все конфигурации средств проектирования ISE (за исключением Alliance™ ISE}

имеют одинаковую структуру и пользовательский интерфейс. Поэтому после освое-

ния наиболее доступной конфигурации САПР WebPACK ISE, используя материал

данной книги, можно, при необходимости, без труда перейти к наиболее полному

пакету Foundation ISE.

22 Зотов В. Ю. Проектирование цифровых устройств на основе ПЛИС

1.6. Основные характеристики пакета WebPACK ISE

Программные средства WebPACK ISE представляют собой систему сквозного

проектирования, которая реализует полный цикл разработки цифровых устройств на

основе ПЛИС, включающий этапы создания исходных описаний проекта, синтеза,

моделирования, размещения и трассировки, а также программирования кристалла.

Версия 5.1г САПР WebPACK ISE предназначена для проектирования цифровых уст-

ройств на базе ПЛИС фирмы Xilinx следующих семейств:

CPLD: ХС95ОО (ХС9536, ХС9572, ХС95108, ХС95144, XC952I6, ХС95288),

XC9500XL (XC9536XL, XC9572XL, XC95144XL, XC95288XL), XC9500XV

(XC9536XV, XC9572XV, XC95144XV, XC95288XV), CoolRunner XPLA3

(XCR3O32XL, XCR3064XL, XCR3128XL, XCR3256XL, XCR3384XL,

XCR3512XL), CoolRunner-Il (ХС2С32, ХС2С64, ХС2С128, ХС2С256, ХС2С384,

ХС2С512);

. FPGA: Spartan-II (XC2S15, XC2S30, XC2S50, XC2SI00, XC2S150, XC2S200),

Spartan-IIE (XC2S5OE, XC2S100E, XC2S150E, XC2S200E, XC2S300E), Virtex-E

(XCV50E, XCVIOOE, XCV200E, XCV300E), Virtex-II (2V40, 2V80 и 2V250),

Virtex-II Pro (XC2VP2).

Кроме того, модуль программирования iMPACT™, входящий в состав пакета,

может применяться для конфигурирования практически всех кристаллов, выпускае-

мых фирмой Xilinx. Для создания конфигурационной последовательности при этом

используются другие средства проектирования, предоставляемые фирмой Xilinx.

Отличительные особенности пакета:

• поддержка различных методов описания проектируемых устройств (графиче-

ских, в форме принципиальных схем или диаграмм состояний, и текстовых, с

использованием языков описания аппаратуры HDL (Hardware Description

Language));

• возможность использования проектов, подготовленных в других системах

проектирования;

• наличие схемотехнического редактора, укомплектованного набором обширных

библиотек;

• интеллектуальные средства создания HDL-описаний, формирующие шаблоны на

основании информации, предоставляемой пользователем, для языков описания

аппаратуры VHDL™, Verilog™ и ABEL™ HDL;

• высокоэффективные встроенные средства синтеза HDL-просктов, поддержи-

вающие языки VHDL, Verilog и ABEL HDL;

• интегрированный интерфейс для средств синтеза "третьих" фирм, обеспечиваю-

щий возможность применения, например, пакетов Synplicity Synplify™/Pro и

LconardoSpectrum™, поддерживающих языки VHDL и Verilog;

• развитые средства верификации проекта, позволяющие сократить полное время

разработки устройства за счет обнаружения возможных ошибок на более ранних

стадиях проектирования и сокращения длительности и количества возможных

итераций;

/, Характеристика основных семейств ПЛИС и средств проектирования 23

• автоматические средства трассировки проекта в кристаллы различных семейств

ПЛИС Xilinx с учетом оптимизации проекта по различным параметрам;

• единые средства программирования кристаллов всех семейств ПЛИС Xilinx,

выполненных по различной технологии (CPLD и FPGA), и конфигурационных

ППЗУ, поддерживающие несколько типов загрузочных кабелей JTAG-

интерфейса;

• встроенный комплект вспомогательных программных средств, позволяющих

повысить эффективность процесса проектирования, включающий анализатор

статических временных характеристик Timing Analyzer™, интерактивный графи-

ческий редактор размещения Floorplanner™, модуль оценки потребляемой мощ-

ности XPower™, "мастер" подготовки описаний блоков синхронизации, выпол-

няемых на основе DCM, Architecture Wizard™, интерактивный графический ре-

дактор топологических ограничений РАСЕ™ (Pinout and Area Constraints Editor)',

• доступный для разработчика пользовательский интерфейс и наличие в каждом

модуле пакета справочной системы, сокращающие время освоения САПР;

наличие интегрированного с пакетом САПР набора инструментов и утилит дру-

гих фирм, предоставляющих дополнительные удобства в процессе проектирова-

ния, включающего утилиту генерации тестовых сигналов HDL Bencher™, про-

грамму моделирования ModelSim ХЕ II Starter™ и редактор диаграмм состояний

StateCAD™.

2. Получение и установка программных модулей

пакета WebPACK ISE

2.1. Требования к операционной системе и аппаратным

ресурсам компьютера

Версия 5.И пакета WebPACK ISE предназначена для работы под управлением

операционных систем Windows 2000™ и Windows ХР™. Исключение поддержки

операционной системы Windows 98™ делает невозможным установку этой версии

средств проектирования на компьютеры, нс обладающие достаточными ресурсами

для использования указанных операционных систем. В среде Windows 98 можно

использовать предыдущую версию пакета WebPACK ISE (4.2i), работа с которой

рассмотрена в [15-25].

Для нормального функционирования версии 5. li пакета WebPACK ISE в ОС

Windows 2000 необходим компьютер с процессором не ниже Pentium™ 200 МГц и

ОЗУ не менее 64 Мбайт (рекомендуется 256 Мбайт). Размер свободного пространст-

ва на жестком диске для установки WebPACK 1SE и ModelSim ХЕ Starter в полном

объеме должен составлять не менее I Гбайт. Кроме того, при установке пакета же-

сткий диск, который обычно используется для создания временных файлов, должен

иметь не менее 500 Мбайт свободного пространства.

2.2. Получение программного обеспечения

WebPACK ISE

Для получения программного обеспечения WebPACK 1SE необходимо открыть

страницу www.xilHtx.com/sxpressoAvebpack.htm и выполнить процедуру бесплатной

регистрации, воспользовавшись кнопкой Register for ISE WebPACK (рис. 2.1). При

этом пользователю присваивается введенный им идентификационный код (UserID) и

пароль (Password), которые затем следует указать при выполнении процедуры ска-

чивания пакета или его обновлений. Если эта процедура уже однажды выполнялась,

то повторной регистрации нс требуется. Достаточно воспользоваться уже имеющи-

мися идентификационным кодом и паролем. Чтобы перейти к процессу копирования

программных средств, следует нажать кнопку Download ISE WebPACK. Учитывая

большой объем копируемых данных, рекомендуется использовать специальные про-

граммы скачивания, позволяющие продолжить этот процесс после разрыва и вос-

становления соединения с сервером.

Дистрибутив версии 5.li пакета включает в себя два файла, каждый из которых

представляет собой самораспаковывающийся архив. После их копирования следует

поочередно запустить на выполнение каждый из полученных файлов. По окончании

распаковки каждого архива автоматически запускается процесс установки

WebPACK ISE или ModelSim ХЕ 11 Starter, в ходе которого необходимо последова-

тельно выполнить вес инструкции каждой программы инсталляции.

2. Получение и установка программных модулей пакета WebPACK /SE

25

Free ISE WebPACK 5.1i

The free ISE WebPACK 5.1i is the

most complete, easy-to-use

software solution to complete a

Xilinx CPLD or low-density FPGA

design

Web* CIC ./

Important: To access ISE WebPACK, please use a

JavaScript-enabled browser version equal to or greaierthan IE

'4.0 or Netscape Navigator 4.7.

Register:

In order to use ISE WebPACK, we ask that you first register with

us.

"Л Registration allows Xilinx to monitor the

Register tor. I . , . • . .

ise WebPACK | software demand and provide update

-!x notifications, if desired.

Download:

If you have already registered for the ISE WebPACK. please click

the download button.

Download

ISE WebPACK

Рис. 2.1. Регис грация и копирование пакета WebPACK ISE

Для выполнения завершающих этапов разработки (конфигурирования кристал-

лов) потребуется загрузочный кабель, который можно изготовить самостоятельно,

воспользовавшись схемой, представленной в документации на следующих Web-

страницах: http://www.xilinx.com/support/sw__manuals/xilinx5/download/pac.zip

и http://www.plis.ru /pic/zip/JTAG__cable.pdf

2.3. Установка программных средств

пакета WebPACK ISE

После распаковки архива пакета WebPACK ISE автоматически запускается "мас-

тер" его установки на жесткий диск компьютера. Работа "мастера" начинается с вы-

вода диалоговой панели, содержащей лицензионное соглашение по использованию

устанавливаемого программного обеспечения, вид которой приведен на рис. 2.2.

Необходимо принять условия лицензии, поместив курсор на поле индикатора

/ accept the terms of this software license, и щелкнув левой кнопкой мыши. При этом в

поле индикатора отобразится соответствующий маркер и станет активной кнопка

Ца.чее (Next), расположенная в нижней части диалоговой панели (рис. 2.2). Эта кноп-

ка позволяет перейти к следующей диалоговой панели "мастера", в которой нужно

указать имя диска и каталога, используемого для размещения программ пакета,

26

Зотов В. Ю. Проектирование цифровых устройств на основе ПЛИС

та, а также название раздела (программной группы), создаваемого в меню Пуск/Про-

граммы (Start/Programs) (рис. 2.3).

JUcept Software Нсеме - ХШпи Software JmkalMftftt

Accept the Software License

Please lead the Mowing Seflwere License Agreemert and cfick the checkbox bewi to

indcate That you accept the teem cf the bgreemeri

INSTALL CHECKLIST

Wefcoftw

Ac&ptScfawe License

..Ldtr :«й ZviilD

f!"

Л .Х$гй?.;;л8?1,‘

Орг й? “г-К<ПГ*Г?

hr- л«е

Соруг^Н (С) 2002 Хйпх. Inc. Al

r®H»ie*erved.

Tiademyfcs -and Patartt

H3LIMXIIWE BASED SOFTWARE LICENSE"~ Я

please READ THIS DOCUMENT CAREFULLY BEFORE USING the software.

BY USING THE SOFTWARE.YOU ARE AGREEING 10 BE BOUND BY THE TERMS

OF THIS LICENSE. IF YOU DO NOT AGREE TO THE TERMS OF THIS LICENSE. _

YOU ARE NOT PERMITTED TD USE THE SOFTWARE.IF YOU HAVE ALREADY •

PURCHASED THE SOFTWARE, PROMPTLYRETURN THE SOFTWARE TO THE

PLACE WHERE YOU OBTAINED IT AND YOUR MONEY WILL BE REFUNDED.

IF YOU HAVE OBTAMED THIS SOFTWARE AS AN UPDATE TO SOFTWARE FOR

WHICH YOU HAVE PREVIOUSIYOBTAJNED A LICENSE. T HE TERMS OF THAT

PRIOR LICENSE WILL CONTINUE TO CONTROL YOUR USE OF THE SOFTWARE.

IF YOU ARE A QUALIFIED UNIVERSITY USER. YOU MAY OBTAIN AN EXTENSION

OF THS LICENSE BY REGISTERING WITH THE MLMXUNIVERSITYPRCeRAM.

p e* te"14 Q* th* wftwarefceme.1

| — NeA > | Cancel |:

Рис. 2.2. Диалоговая панель, содержащая лицензионное соглашение по использованию

пакета WebPACK ISE

Select Destination Directory - Ж0ПК

Select a Destination Directory

Select the decctcey where you wert the totowre eet«fed

Ekwbc.

Note: If rinsing ever on existingXtalSE 5 inSaWicn where аХйтх Service Peck has

been installed. theXfinx Service P«k «*4 need to be teagpfed alter completing this

гиШЛйп

INSTALL CHECKLIST

Welcome

Accept Scflweie Lcense

Enter Registration ID'

4 Select Destination 0 rectcsy

»

lie-gas trei

Select a Program Folder

The name Hete w> apoear rt the Start Menu->Pic»grar«S fct on ytw desktop.

|xirwlSE 5

—a

¥ .TS

Cowyhl (C) 2002 XiVw. Inc. 41

rights reserved

Frademarks yid Patents

<£ock j Nexi> ] Cancel |

Рис. 2.3. Определение полного названия Karanoia, в котором разметаются программы пакета

WebPACK ISE, и соответствующе! о радела в меню Пуск/Профаммы (StarUProgiams)

2. Получение и установка программных модулей пакета WebPA СК ISE *2,7

Полное имя каталога, включающее путь доступа к нему, указывается в поле ре-

дактирования Select a Destination Directory, расположенном в верхней части панели.

По умолчанию предлагается каталог Xilinx на диске С. Изменить название диска или

каталога можно с помощью клавиатуры после активизации этого поля редактирова-

ния или кнопки Browse, которая открывает стандартную панель выбора каталога.

Название раздела, создаваемого в меню Пуск/Программы и используемого для вызо-

ва программ пакета, определяется в поле редактирования Select a Program Folder.

Рекомендуется использовать название Xilinx ISE 5, предлагаемое по умолчанию. При

необходимости его изменения следует использовать клавиатуру. После нажатия

кнопки Далее (Next) в нижней части диалоговой панели (рис. 2.3) открывается оче-

редная диалоговая панель "мастера", вид которой показан на рис. 2.4.

select Software Modules to Install - Х1Ьпк Software Inst';T ; .

Select Xilinx Modules

ДСРШ Design Envionment

INSTALL CHECKLIST

V/elccme

Accept Software License

Enter Registration ID

Select Destination Directory

* Select Xifrw Modules

I, С-...ЕП* «'Глр-тЧ

Be Sh ч

•/;CPLD Proyamming Tools

Jr XPower and ChipViewer Tods

>FPGA Design Environment

v FPGA Programming Tools

/Parallel Cable Drivers

y'-MultiUNX Cable Driver

^Documentation

Copyright (C) 2002 X^inx. Inc. Al

rights reserved.

. Tradema ks and Patents

|Г_' Select/DeselectAII

DiskSpaceReqdred: 5B0S25KB

Disk Space Available: 9974600 KB

i-Desctiplion 7Г735Г-

I Installs Design Entry, Synthesis, and Implementation Tools for

XiSnxCPLDs.

aitik^. .згас'.'ет

< fiack | Next > J Cancel |

Рис. 2,4, Выбор устанавливаемых компонентов (групп программ) пакета WebPACK 1SE

В этой панели указывается состав устанавливаемых компонентов пакета

WebPACK ISE. Наличие маркера на поле индикатора, расположенного в строке с

названием группы программ, указывает на то, что эти модули пакета будут установ-

лены на диск. Для изменения состояния индикатора на противоположное следует

поместить курсор на соответствующую строку списка компонентов и щелкнуть ле-

вой кнопкой мыши. В случае пропуска указанной диалоговой панели пакет устанав-

ливается в полном объеме. Перейдя к следующей диалоговой панели (рис. 2.5), не-

обходимо определить значения параметров, управляющих установкой переменных

окружения и путей доступа к программам пакета в системных файлах. Определение

28 Зотов В. К). Проектирование цифровых устройств иа основе ПЛИС

значений переменных XILINX и PATH необходимо для нормального функциониро-

вания модулей пакета в пакетном режиме и в режиме командной строки.

UpdMe Environment - ХЙпи Softwarelr»t >« -ц*- л.

Update Environment

z. .(HIHitO

INSTALL CHECKLIST

Vr'efcoie

Accept Soflwa e License'

Enter Regstfeticn ID

Select Destination Director

Select Xibnx Modules

wUpdate Environment

P £Syp&»>0UNX vaWJd

This variable is required fa the Xifiru software to wok properV. If you check Ibis

bos. the instater wfi autonalicaiy tvdate fhe registry lie (V/indowsXP/2000(RD with

the proper values. И you uncheck this box, you must ensue that this environment

variable is property set.

P SeVUpdate PATH variable

This PATH variable must be updated for the Хйгх software to wok proper^. If you

check this box. the installer veil automatic Jh update the registry file (Windows

XPZ2000P)) with the proper values. If you uncheck this box. you roust ensue that

foie environment variable is property set.

СсруггдЫргтгХШпх. Inc, All

ligh'.s reserved.

Trademarks and Patents

<£ack | ijexty | Cancel |

Рис. 2.5. Выбор режима автоматической установки переменных окружения

для программ пакета WebPACK ISE в системных файлах

Параметр Set/Update XILINX variable используется для управления установкой

или заменой переменных окружения в системных файлах. Значение "включено”,

установленное по умолчанию, разрешает автоматическое определение переменной

окружения XILINX.

Значение параметра Set/Update PATH variable управляет установкой путей дос-

тупа к программам пакета в системных файлах. По умолчанию этот параметр нахо-

дится в состоянии "включено", разрешающем автоматическое определение пере-

менной окружения PATH, которая описывает путь доступа к программам пакета

WebPACK ISE. Для этих двух параметров рекомендуется использовать значение

"включено", установленное по умолчанию.

Очередная диалоговая панель, отображаемая после нажатия кнопки Далее (Next)

(рис. 2.5), содержит список указанных параметров процесса установки пакета (рис. 2.6).

Для изменения каких-либо значений следует вернуться к предыдущим шагам, нажав

кнопку Назад (Back). Если все параметры установлены корректно, то следует нажать

кнопку Установка (Install), которая активизирует собственно процесс инсталляции про-

1рамм пакета. При этом па экран выводится информационная панель (рис. 2.7), в верхней

части которой отображается индикатор выполнения этою процесса.

2. Гкпучение и установка программных модулей пакета WebPACK 1SE

29

Begin Installatton “ МЙгос Software trvuKMfon

Begin InrtaHatfon

A jvmmaiy cf nhrt has been selected can be found in fieieLM 7о view this

Be. invoke theXWc System Checkei liom the Accessories folder in the Хйх

IS£ & Piogvn Gnxjp. «пб tdect the fletetM optran.

Options Summary:

lNS7AH£H£tXUS7

Wekome

Accept Scflwwe Lnerise

Enter Reflirtration ID

Select DestinalKn Oeectap

Select XJrx ModUet

Update Enviorrrert

Begn Inrtatakr?

Inrta* Luxation: C \X»ra

Program Group: Xir» ISE 5

Srib'Up&tePATH variable

SeMJpdaieXlUNX variable

CPLD D«ipn Envictmeri

CrtD Progammirg 1 ooh

XPower and Ch©V«*er T ock

FPGA D&tgn Envvomeri

FPGA Piogwnmng Tools

J . •

Ccp/^^jZOEXibJrK; A!

rights reserved

TrafemaksendPritente

< Back I Instal I Careel

Рис. 2.6. Диалоговая панель запуска процесса инсталляции пакета WebPACK 1SE

Begin Installation - Minx Software ItHtrfaUan

Lntfairg

j INSTALLOlECXUSr

, Welcome

Accept Sck«4«e License

Enlet Registration ID

Sefect Dertination Directory

Select ЗДгк Mpdites

Update Enswoanent

Beflnfnrtafction

Cop/i^i(2]2002XinAlnc A!

1 reserved

£ T taderraiks and Parents__

V4ttUiMlVWA

еялот'юл tw'nt

Рис. 2.7. Информационная панель процесса инсталляции пакета WebPACK 1SE

После завершения инсталляции программ пакета WebPACK ISE последовательно вы-

водятся два однотипных запроса о замене драйверов (рис. 2.8). Для нормальной работы

загрузочных кабелей рекомендуется ответить на эти запросы утвердительно (Уез).

30 Зотов В. Ю. Проектирование цифровых устройств на основе ПЛИС

Xilinx 5.Н Set up Д]

sf \ Setup has detected an existing version of the driver file

C:\Xilinxlhnlnt)win<4'vr.sys

in the system directory

C:\WINNpsystem32\drivers\winchvr.sys

Do you want to overwrite this file (Xlinx recommends that you overwrite this file)?

|i Vps j| No |

Рис. 2.8. Панель запроса о необходимости установки (или замене) драйвера,

обеспечивающего корректную работу загрузочного кабеля

Далее выводится диалоговая панель с предложением установки программных

средств Java Runtime Environment для просмотра отчетов в формате HTML

(рис. 2.9). Рекомендуется отказаться от инсталляции этих программных средств,

нажав кнопку Отмена (Cancel).

Xilinx 5-li Setup . '' ,e(fr . ...^. ...... ,. xl

: In order to view HTML reports for CPLDs, the Java Runtime Environment needs to be installed on your system.

|l-~ Cancel |

Рис. 2.9. Диалоговая панель запуска процесса инсталляции

программных средств Java Runtime Environment

Затем появляется диалоговая панель, в которой предлагается открыть страницу

Web-сервера, содержащую информацию о возможности обновления пакета и других

программных средствах разработки фирмы Xilinx (рис. 2.10). Чтобы отказаться от

немедленного открытия этой страницы, следует нажать кнопку Закрыть (Close).

Setup complete - see whi^snejsb.,. X1

Visit the Software Updates Center for the the latest information on

software updates. IP, future releases, and other Xilinx development

tools.

View Now iI Close

Рис, 2.10. Панель запроса о немедленном открытии страницы Internet,

содержащей информацию о возможности обновления пакета и других программных

средствах фирмы Xilinx

2. Получение и установка программных модулей пакета WebPA СК 1SE 31

Далее отображается сообщение об успешном окончании процесса инсталляции

(рис. 2.11), которое закрывается кнопкой ОК.

Xilinx 5.1i Setup „ . х|

Install has completed successfully.

Рис. 2.11. Панель сообщения об успешном завершении процесса

инсталляции пакета WebPACK ISE

Процесс установки завершается запросом о необходимости перезагрузки компь-

ютера (рис. 2.12). Для немедленной перезагрузки следует нажать кнопку Yes.

’.”"s <мяммма .

Xilinx5.1iSetup ...... ‘ ' I

/ Setup has cpdated system files and Windows must be restarted.

г X/

i Would you like to do that now?

I

I p 2П no I

Рис. 2.12. Панель запроса о необходимости перезагрузки компьютера

2.4. Обновление программных средств

пакета WebPACK ISE

Обновление программных средств пакета WebPACK 1SE выполняется с помо-

щью модулей Service Pack, которые следует скопировать, обратившись на страницу

www.xilinx.coin/supportl, и воспользовавшись идентификационным кодом и паролем,

указанными ранее, в процессе регистрации. Полученный модуль обновления уста-

навливается поверх существующей версии. К моменту написания данной книги на

web-серверс фирмы Xilinx был представлен Service Pack 3. Этот модуль представля-

ет собой самораспаковывающийся архив, после развертывания которого автомати-

чески запускается "мастер" инсталляции Service Pack (рис. 2.13).

В процессе установки модуля обновления Service Pack необходимо указать диск

и каталог, в котором расположены программные средства пакета WebPACK ISE, ис-

пользуя соответствующую диалоговую панель "мастера”, вид которой показан на

рис. 2.14.

32 Замов В. Ю. Проектирование цифровых устройств на основе ПЛИС

Рис. 2.13. Стартовая панель "мастера" инсталляции Service Раск

SelectDeshnabonDirectory-Х*пнSoftware .<. ”*1 ->Г~ I х|

Select a Destination Directory

Select the duectoty where you want the software instated

~ 7i a,°"a l

J&fbX i ИЙ " 5

INSTALL CHECKLIST

Select Destnation Dtectoiy

ЗедоНг-ги&з&оХ

Copyright (CJ 2002Xinx Inc. Al

trghts reserved

Trademarks and Patents

17 Create Backup before ^staffing update.

Selecting this option wl Ajw you Io irinsleS this Service Pack update al a later time by

selecting SUrt->Programs->Xfcw ISE 5->AccessoiiesoUrw»tan Service Pack.

Note This wi double the amount d space teqtied for Ihis service pack.

| flext> | Cancel |

Рис. 2.14. Определение полного названия каталота. в котором размещаются программы

пакета WebPACK. 1SE

2. Получение и установка программных модулей пакета WebPA СК ISE 33

Ввод названия каталога осуществляется с помощью клавиатуры после активиза-

ции поля редактирования Select a Destination Directory или кнопки Browse, которая

открывает стандартную панель выбора каталога. В этой же диалоговой панели со-

держится параметр Create Backup before installing update, который управляет созда-

нием резервных копий изменяемых файлов. По умолчанию для этого параметра ис-

пользуется значение "включено", позволяющее при необходимости впоследствии

отменить изменения, выполненные в процессе обновления пакета.

Перед началом копирования файлов выводится панель, в которой приведены зна-

чения параметров инсталляции (рис. 2.15).

9ефпirtftaflsticm-ХйпмSoftwareIhrtdbtton. '-г-. -I Iх!

d Begin Installation

Cick the Intldl button Io begn (he Seivce Pack rislafeton.

Options Summary •

INSKU. CHECKLIST ЕыыЗ&ТсЛ*»----------------------------2

Select Desfrieticn Directory

. * Begin Inhalation I

Copyright (Ц 2002Kifew, tnc Al

limits reserved

T tademaks and Patents

< fiack [ [ndet | Canccf |

Рис. 2.15. Диалоговая панель запуска процесса инсталляции Service Pack

При необходимости внесения изменений следует вернуться к предыдущим ша-

гам, нажав кнопку Назад (Back). Если все значения параметров установлены верно,

то следует нажать кнопку Установка (Install), которая активизирует собственно

процесс инсталляции файлов обновления Service Pack.

Дальнейший ход процесса установки модуля обновления сопровождается выво-

дом диалоговых панелей, приведенных на рис. 2.7-2.8, 2.10-2.12, которые подробно

рассмотрены в предыдущем разделе.

2.5. Установка системы HDL-моделирования

ModelSim ХЕ Starter

Процесс установки системы IIDL-моделировапия ModelSim ХЕ Starter выполняется

также с помощью "мастера", который активизируется после автоматической распаковки

инсталляционного архива. В стартовой диалоговой панели, вид которой показан на

2 Зотов В. К).

34 Зотов В. fO Проектирование цифровых устройств иа основе ПЛИС

рис. 2.16, следует выбрать редакцию устанавливаемой системы ModcISim. Для инстал-

ляции свободно распространяемой версии ModelSim ХЕ Starter нужно нажать кноп-

ку МХЕ Starter - Limited version МХЕ (Free). Переход к следующему шагу установки

программных средств ModcISim осуществляется нажатием кнопки Датее (Next) в

нижней части диалоговой панели (рис. 2.16).

Рис. 2.16. Выбор редакции устанавливаемой системы HDL-моделирования ModelSim

Очередная диалоговая панель "мастера" установки содержит предупреждение о

необходимости закрытия других открытых приложений перед началом инсталляции

(рис. 2.17).

Welcome Л • *- х|

ля | Welcome to the ModelSwnXE II v5.Ba Starter Sets?)

program. This program i*iinstalModelSirn><E 11

v5.6a Starter on your comptier.

Il is strongly recommended that you exit al Wmdows programs

before running this Setup program.

Click Cared to quit Setup and then dose any programs you

have runnhg Click Next to continue wih theSetupprogram.

WARNING: This program is protected by copyright law and

international beetles.

Unauthorized reproduction or distribution ol ths program, or aqy

portion of«, may result in severe civi and criminal pendties. and

wfi be prosecuted Io the maximum extent possible under law.

J; jjext? “| Cancel J

Рис. 2.17. Панель предупреждения о необходимости завершения работы других

активизированных программ перед началом процесса инсталляции

2. Получение и установка программных модулей пакета WebPACK ISE 35

В следующей диалоговой панели "мастера" отображается текст лицензионного

соглашения об использовании программы ModelSim (рис. 2.18). Чтобы продолжить

процесс установки, необходимо принять условия лицензии, нажав кнопку fo.

Software License Agreement- .2^. .. x[

Please read the following License Agreement Press the PAGE DOWN key to see