Author: Зотов В.Ю.

Tags: полупроводниковые устройства программирование микропроцессоры

ISBN: 5-93517-165-1

Year: 2006

Text

В. Ю. Зотов

В. Ю. Зотов

Проектирование встраиваемых

микроврвцессорных систем

на основе ПЛИС фирмы

Я XILINX’

Москва

Горячая линия-Телеком

2006

ББК 32.852.3

3-88

Зотов В. Ю.

3-88 Проектирование встраиваемых микропроцессорных систем на основе

ПЛИС фирмы XILINX®. - М.: Горячая линия - Телеком, 2006. - 520 с., ил.

ISBN 5-93517-165-1.

Книга предназначена для самостоятельного изучения методики сквозного проектиро-

вания встраиваемых микропроцессорных систем на базе программируемых логических

интегральных схем (ПЛИС) фирмы Xilinx “. Представлено подробное описание характе-

ристик, архитектуры и системы команд микропроцессорных ядер семейств PicoBlaze™

и MicroBlaze™, применяемых в качестве основы встраиваемых систем. Рассмотрены эта-

пы проектирования 8-разрядных микропроцессорных систем, реализуемых на базе ПЛИС

с архитектурой FPGA, с использованием ядер семейства PicoBlaze, и их выполнение в

рамках САПР серии Xilinx ISE™ (Integrated Sowtware Environment) версии 7.1 i. Дана раз-

вернутая характеристика основных этапов разработки 32-разрядных встраиваемых сис-

тем, выполняемых на основе микропроцессорных ядер семейства MicroBlaze. Рассмотрен

процесс осуществления этих этапов с помощью комплекса средств автоматизированного

проектирования встраиваемых микропроцессорных систем Xilinx Embedded Development

Kit™ (EDK). Приведены исходные тексты VHDL-описаний микропроцессорных ядер се-

мейств PicoBlaze.

Материал, изложенный в книге, также может быть использован в процессе самостоя-

тельного освоения средств проектирования 32-разрядных встраиваемых микропроцес-

сорных систем Xilinx EDK версии 7.1i.

Для инженерно-технических работников, может быть полезна студентам и аспиран-

там, специализирующимся в области разработки микропроцессорных систем различного

назначения.

ББК 32.852.3

Адрес издательства в Интернет www.TECHBOOK.RU

e-mail: radios_hl@mtu-net.ru

Справочное издание

Зотов Валерий Юрьевич

ПРОЕКТИРОВАНИЕ ВСТРАИВАЕМЫХ МИКРОПРОЦЕССОРНЫХ СИСТЕМ

НА ОСНОВЕ ПЛИС ФИРМЫ XILINX®

Компьютерная верстка Н. В. Ивановой

Корректор Е. Н. Федоров

Обложка художника В. Г. Ситникова

ЛР № 071825 от 16 марта 1999 г.

Подписано в печать 08.02.06. Формат 70x100/16.

Усл. изд. л. 43,25. Тираж 2000 экз. Изд. № 6165. Заказ 2062.

Отпечатано в ООО ПФ «Полиграфист».

160001, г. Вологда, ул. Челюскинцев, 3, тел.: (8172) 72-55-31, 72-60-72

ISBN 5-93517-165-1

© В. Ю. Зотов. 2006

© Оформление издательства

«Горячая линия - Телеком». 2006

ПРЕДИСЛОВИЕ

Современный этап развития цифровой техники характеризуется широким при-

менением программно-аппаратных комплексов, которые строятся по принципу «сис-

тема на кристалле» (System-on-Chip). При этом в качестве элементной базы для реа-

лизации таких систем все чаще используются программируемые логические инте-

гральные схемы (ПЛИС). Такая тенденция обусловлена тем, что современные

семейства ПЛИС отличаются высоким быстродействием и значительным объемом

логических и специальных ресурсов в сочетании с относительно невысокой стоимо-

стью. Ведущими производителями кристаллов программируемой логики для под-

держки данного направления разработаны микропроцессорные ядра, а также соот-

ветствующие средства проектирования и отладки встраиваемых систем. Фирма

Xilinx® предоставляет несколько семейств микропроцессорных ядер, широкий

спектр IP-компонентов периферийных устройств, а также средства автоматизирован-

ного проектирования, позволяющие в короткие сроки и с минимальными затратами

создавать цифровые системы на кристалле, реализуемые на базе ПЛИС с различной

архитектурой.

Данное издание знакомит с технологией сквозного проектирования встраивае-

мых микропроцессорных систем на основе ПЛИС фирмы Xilinx. Приводится описа-

ние микропроцессорных ядер и соответствующих средств проектирования, позво-

ляющих выполнить все этапы разработки, начиная с создания проекта и заканчивая

программированием кристалла.

Структура книги включает в себя 14 глав и 3 приложения. В гл. 1 дается краткая

характеристика микропроцессорных ядер и систем автоматизированного проектиро-

вания (САПР), предлагаемых фирмой Xilinx. В гл. 2 подробно рассматриваются ос-

новные характеристики и архитектура базового варианта микропроцессорного ядра

семейства PicoBlaze, реализуемого на основе ПЛИС серий Spartan™-!!, Spartan-IIE,

Virtex™, Virtex-E. В гл. 3 описывается система команд этого варианта микропроцес-

сорного ядра PicoBlaze. Гл. 4 знакомит с особенностями микропроцессорного ядра

PicoBlaze, предназначенного для применения в проектах систем, реализуемых на ос-

нове ПЛИС семейства Virtex-II. В гл. 5 представлены отличия характеристик, архи-

тектуры и системы команд микропроцессорного ядра PicoBlaze, реализуемого на ос-

нове ПЛИС семейства CoolRunner-II, по сравнению с базовым вариантом. В гл. 6 рас-

смотрены отличительные особенности микропроцессорного ядра PicoBlaze,

предназначенного для реализации на основе ПЛИС семейств Spartan-3, Virtex-II,

Virtex-II PRO и Virtex-4. Гл. 7 посвящена вопросам разработки и трансляции про-

грамм на языке ассемблера микропроцессорных ядер семейства PicoBlaze. В гл. 8

представлены этапы проектирования встраиваемых систем на основе микропроцес-

сорных ядер семейства PicoBlaze и процесс их выполнения в САПР серии Xilinx

ISE™ (Integrated Synthesis Environment). Здесь же приведен пример разработки кон-

троллера с использованием ядра PicoBlaze, реализуемого в ПЛИС семейства Spar-

tan-3. Гл. 9 знакомит с характеристиками и архитектурой микропроцессорных ядер

семейства MicroBlaze. Система команд данного семейства микропроцессорных ядер

представлена в гл. 10. В гл. 11 приведено описание характеристик и пользовательско-

го интерфейса комплекса средств автоматизированного проектирования встраивае-

мых 32-разрядных микропроцессорных систем Xilinx Embedded Development Kit™

4

Зотов В. Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС

(EDK). В гл. 12 подробно рассмотрено поэтапное выполнение процесса разработки

микропроцессорных систем на основе ядер семейства MicroBlaze в САПР Xilinx

EDK. Гл. 13 представляет методику проектирования встраиваемых систем на основе

микропроцессорных ядер семейства MicroBlaze, осуществляемого с помощью масте-

ра Base System Builder Wizard™. Гл. 14 знакомит с аппаратными средствами, приме-

няемыми для отладки встраиваемых микропроцессорных систем, разрабатываемых

на основе ПЛИС фирмы Xilinx.

В прил. 1-3 приведены VHDL-описания исполнительных модулей микропроцес-

сорных ядер семейства PicoBlaze, реализуемых на базе ПЛИС семейств Spartan™-!!,

Spartan-IIE, Virtex™, Virtex-E, CoolRunner-II, Spartan-3, Virtex-II, Virtex-IIPRO и

Virtex-4. Представленные тексты VHDL-описаний могут использоваться в качестве

образцов или шаблонов при создании собственных микропроцессорных ядер, пред-

назначенных для разработки встраиваемых систем на основе ПЛИС различных се-

мейств, выпускаемых фирмой Xilinx.

При изучении материала рекомендуется воспользоваться бесплатными версиями

рассматриваемых систем проектирования, которые можно заказать, обратившись на

Web-страницу www.xilinx.com или к официальному дистрибьютору фирмы Xilinx.

Автор выражает благодарность заместителю генерального директора фирмы

InlineGROUP (официального дистрибьютора фирмы Xilinx) Д. А. Кнышеву и веду-

щим сотрудникам М. О. Кузелину, М. Ю. Гетопанову, Г. И. Алексееву, Ю. В. Митя-

кину, А. В. Перекресту за информационно-техническую поддержку в процессе рабо-

ты над книгой.

1. ХАРАКТЕРИСТИКА МИКРОПРОЦЕССОРНЫХ ЯДЕР

И СРЕДСТВ ПРОЕКТИРОВАНИЯ ВСТРАИВАЕМЫХ

МИКРОПРОЦЕССОРНЫХ СИСТЕМ НА ОСНОВЕ ПЛИС

ФИРМЫ XILINX

Постоянное внедрение передовых технологий в процесс производства кристал-

лов программируемой логики привело к значительному расширению функциональ-

ных возможностей современных семейств ПЛИС. В первую очередь эта тенденция

проявляется в ПЛИС с архитектурой FPGA [2-4]. Следствием этого стало появление

системного подхода в процессе проектирования цифровых устройств, реализуемых

на их основе. При таком подходе кристалл рассматривается как некоторое микропро-

цессорное ядро, окруженное свободными конфигурируемыми логическими ресурса-

ми. На основе этих ресурсов реализуются все необходимые периферийные устройст-

ва проектируемой системы.

Фирма Xilinx, являясь ведущим мировым производителем ПЛИС, наряду с вы-

пуском новых семейств кристаллов, отличающихся высокими техническими харак-

теристиками, предоставляет разработчикам готовые отлаженные модули микропро-

цессорных ядер с различной архитектурой. В настоящее время пользователям дос-

тупны ядра с архитектурой широко применяемых микропроцессоров различных

производителей, таких, как Z80 фирмы Zilog®, PIC семейств 125х, 1655х, 165х фир-

мы Microchip®, 8051 и др. Кроме того, фирма Xilinx предлагает семейства ядер с

оригинальной архитектурой, оптимизированной для реализации на основе ПЛИС

различных серий.

Кроме широкого спектра ПЛИС и IP-компонентов фирма Xilinx предоставляет

современное программное обеспечение, необходимое для разработки проектов циф-

ровых устройств с аппаратной реализацией операций и встраиваемых микропроцес-

сорных систем, а также для последующего конфигурирования кристаллов.

В настоящей главе дается классификация и краткая характеристика микропро-

цессорных ядер, предлагаемых фирмой Xilinx. Здесь же приводится информация о

системах проектирования, предназначенных для разработки встраиваемых микро-

процессорных систем на основе ПЛИС фирма Xilinx.

1.1. Типы микропроцессорных ядер, предназначенных

для разработки встраиваемых систем

на основе ПЛИС фирмы Xilinx

Микропроцессорные ядра, предназначенные для проектирования встраиваемых

систем на основе ПЛИС фирмы Xilinx, по способу реализации подразделяются на две

группы: конфигурируемые (Soft Processor) и аппаратные (Hard Processor). Первую

группу составляют ядра, которые формируются на основе стандартных логических

ресурсов кристаллов. Эти ядра могут применяться в ПЛИС различных серий. Данную

группу образуют семейство 8-разрядных микропроцессорных ядер PicoBlaze™ и се-

мейство 32-разрядных микропроцессорных ядер MicroBlaze™. Ко второй группе от-

носятся микропроцессорные ядра, которые выполнены в виде соответствующих ин-

тегрированных аппаратных блоков ПЛИС. Данная группа представлена семейством

6

Зотов В. Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС

микропроцессорных ядер PowerPC™ фирмы IBM®, которое присутствует в ПЛИС

семейств Virtex™-II Pro и Virtex-4.

Преимуществами конфигурируемых микропроцессорных ядер, предлагаемых

фирмой Xilinx, по сравнению с аппаратными являются высокая гибкость, низкая се-

бестоимость, относительно небольшой объем используемых ресурсов кристаллов,

возможность применения в проектах, реализуемых на базе самых распространенных

и доступных семейств ПЛИС. Таким образом, микропроцессорные ядра семейств

PicoBlaze и MicroBlaze целесообразно использовать в качестве основы недорогих

встраиваемых систем, требуемая производительность которых не должна превышать

70 и 166 D-MIPS соответственно.

Главное преимущество аппаратных микропроцессорных ядер семейства PowerPC

проявляется в возможности функционирования с высокими тактовыми частотами.

Следствием этого является более высокая производительность по сравнению с кон-

фигурируемыми микропроцессорными ядрами фирмы Xilinx. Недостатками аппарат-

ных ядер являются ограниченное число кристаллов, в которых они применяются,

и их высокая стоимость. Настоящее издание посвящено вопросам разработки встраи-

ваемых микропроцессорных систем на основе конфигурируемых ядер фирмы Xilinx.

Поэтому далее приводятся только краткие сведения об аппаратных микропроцессор-

ных ядрах семейства PowerPC.

1.2. Краткая характеристика микропроцессорных

ядер семейства PicoBiaze

Элементы семейства PicoBlaze представляют собой конфигурируемые 8-разряд-

ные микропроцессорные ядра с гарвардской архитектурой, которые предназначены

для использования в проектах встраиваемых систем, реализуемых в ПЛИС фирмы

Xilinx. Характерной особенностью гарвардской архитектуры является применение

раздельных шин для передачи данных и команд

В состав семейства PicoBlaze входят 4 варианта микропроцессорных ядер. Пер-

вый, базовый, вариант ядра PicoBlaze предназначен для применения в ПЛИС се-

мейств Spartan-II, Spartan-IIE, Virtex и Virtex-E. Второй вариант, отличающийся рас-

ширенными возможностями и повышенной производительностью по сравнению с ба-

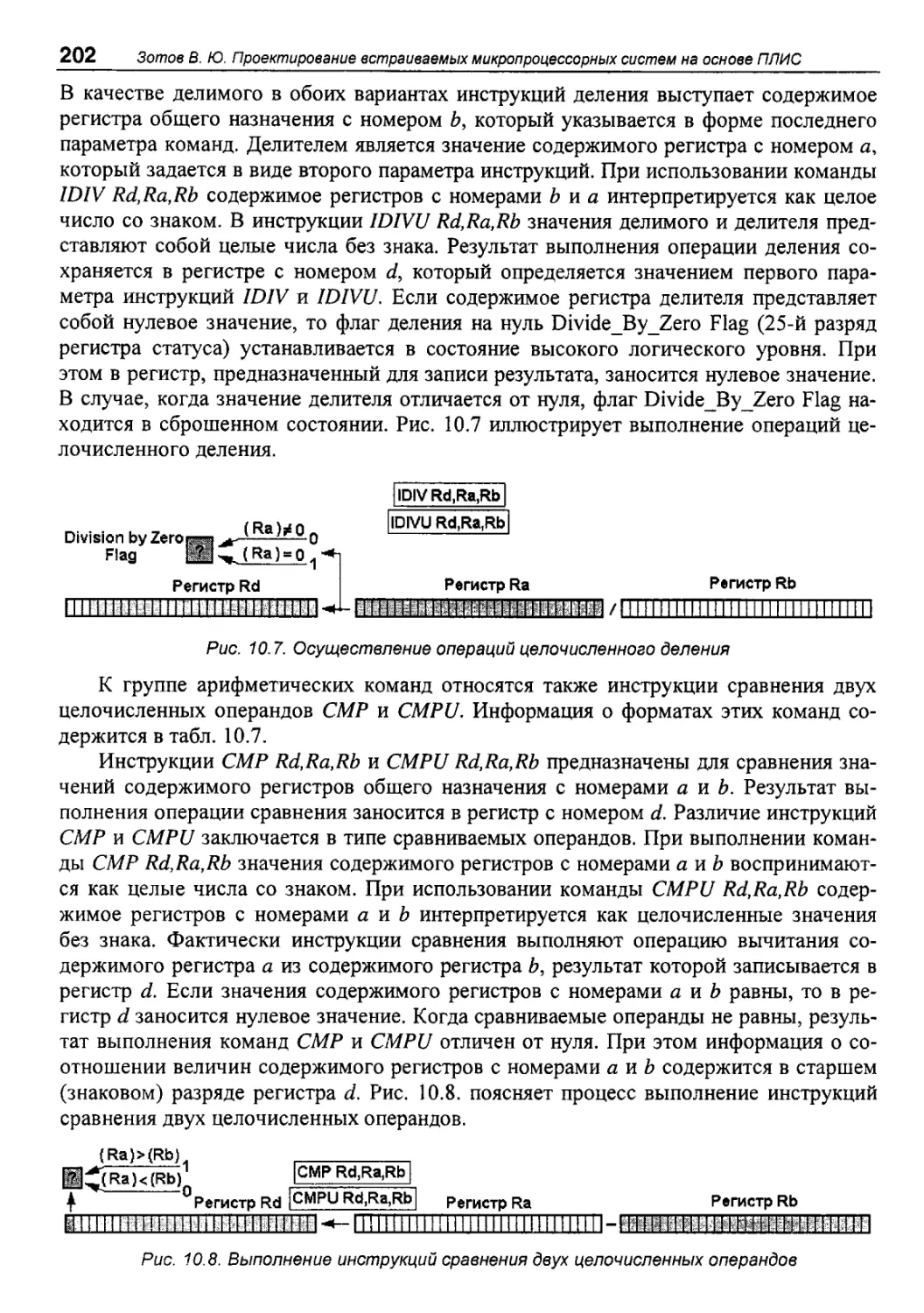

зовым, разработан прежде всего для использования в кристаллах семейства Virtex-II,

но также, при необходимости, может быть реализован в составе проектов, которые

выполняются на основе ПЛИС серии Virtex-II Pro и Virtex-4. Третья модификация

ядра, представляющая собой результат дальнейшего развития двух первых вариан-

тов, предназначена в первую очередь для разработки встраиваемых микропроцессор-

ных систем, реализуемых в ПЛИС семейства Spartan-З. Кроме того, эта версия мик-

ропроцессорного ядра может использоваться также в составе проектов систем, вы-

полняемых на основе ПЛИС семейств Virtex-II, Virtex-II Pro и Virtex-4. Наиболее

компактная модификация микропроцессорного ядра PicoBlaze предназначена для

применения в проектах, реализуемых на основе кристаллов семейства CoolRunner™-

II, которое отличается от других серий ПЛИС CPLD, выпускаемых фирмой Xilinx,

высоким быстродействием, низкой потребляемой мощностью и наличием микросхем

с достаточно большим объемом логических ресурсов [2].

ГЛАВА 1

7

Все микропроцессорные ядра семейства PicoBlaze распространяются свободно

(бесплатно) через Internet. Доступ к соответствующим ресурсам открывает Web-

страница http://www.xilinx.com/ipcenter/processor_central/picoblaze/index.htm. Чтобы

получить все необходимые материалы, относящиеся к конкретному ядру этого се-

мейства, необходимо предварительно выполнить процедуру бесплатной регистрации.

Каждый вариант ядра семейства PicoBlaze предоставляется пользователям в

форме соответствующего архива, в котором содержится комплект файлов, вклю-

чающий в себя необходимые модули VHDL-описаний, ассемблер, примеры, иллюст-

рирующие использование компонентов ядра. Кроме того, в состав комплекта боль-

шинства ядер входят дополнительные файлы описания универсального асинхронного

приемопередатчика UART (Universal Asynchronous Receiver-Transmitter), которые

могут быть использованы в составе разрабатываемых проектов встраиваемых микро-

процессорных систем.

Подробное описание архитектуры, основных характеристик и системы команд

каждого варианта микропроцессорного ядра семейства PicoBlaze дается в последую-

щих главах.

Разработка встраиваемых микропроцессорных систем на основе ядер семейства

PicoBlaze выполняется с помощью систем проектирования серии Xilinx ISE™

(Integrated Sowtware Environment). В качестве инструментов отладки разрабатывае-

мых систем используются средства моделирования, входящие в состав соответст-

вующей конфигурации САПР Xilinx ISE.

1.3. Краткая характеристика микропроцессорных ядер

семейства MicroBlaze

Семейство MicroBlaze включает в себя 32-разрядные микропроцессорные ядра с

гарвардской архитектурой, предназначенные для реализации в ПЛИС семейств

Spartan-II, Spartan-IIE, Spartan-3, Spartan-3E, Spartan-3L, Virtex-E, Virtex-II, Virtex-II

Pro и Virtex-4. Генерация ядер этого семейства осуществляется с помощью комплекса

средств автоматизированного проектирования встраиваемых микропроцессорных

систем Xilinx Embedded Development Kit™ (EDK).

Микропроцессорные ядра семейства MicroBlaze отличаются гибкой архитекту-

рой, позволяющей оптимально использовать ресурсы ПЛИС соответствующих се-

мейств, выбранных для их реализации. Ряд опций и архитектурных особенностей

этих ядер, необходимость применения которых определяется разработчиком, позво-

ляет провести дополнительную оптимизацию в соответствии с выбранным критери-

ем. К числу таких опций относится, например, использование аппаратных умножите-

лей, устройств циклического сдвига. В последних версиях микропроцессорных ядер

семейства MicroBlaze в состав архитектуры включен прецизионный блок выполнения

операций с плавающей запятой Floating-Point Unit, который соответствует специфи-

кации стандарта IEEE-754. В табл. 1.1 в качестве примера приведены параметры, ха-

рактеризующие максимальную производительность ядер семейства MicroBlaze, реа-

лизуемых на основе ПЛИС различных семейств, которая достигается при использо-

вании этих опций.

8

Зотов В. Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС

Таблица 1.1. Максимальная производительность ядер семейства MicroBlaze,

реализуемых на основе ПЛИС различных семейств

Тип ПЛИС Число используемых таблиц преобразования Тактовая частота, МГц Производительность

Virtex-4 (4VLX25-12) 1269 LUTs 180 166 DMIPS

Virtex-II Pro (2VP20-7) 1225 LUTs 150 138 DMIPS

Spartan-3 (3S1500-5) 1318 LUTs 100 92 DMIPS

Когда требуется сократить объем используемых ресурсов кристалла и обеспе-

чить максимально возможную тактовую частоту, микропроцессорные ядра семейства

MicroBlaze могут использоваться в минимальной конфигурации. В табл. 1.2 приведе-

ны значения максимальной тактовой частоты для ядер рассматриваемого семейства,

реализуемых на основе ПЛИС различных семейств в минимальной конфигурации.

Таблица 1.2. Предельные значения тактовой частоты микропроцессорных ядер

семейства MicroBlaze, реализуемых на основе ПЛИС различных семейств

Тип ПЛИС Число используемых таблиц преобразования Тактовая частота, МГц

Virtex-4 (4VLX40-12) 988 LUTs 200

Virtex-II Pro (2VP20-7) 827 LUTs 170

Spartan-3 (3S1500-5) 983 LUTs 100

В составе архитектуры микропроцессорных ядер семейства MicroBlaze применя-

ется ряд стандартных шинных интерфейсов, которые могут использоваться в различ-

ных сочетаниях для подключения периферийных устройств и памяти, реализуемых

как внутри, так и вне кристалла. Применение шины On-chip Peripheral Bus™ (ОРВ),

соответствующей стандарту архитектуры IBM CoreConnect™, позволяет использо-

вать в составе проектируемых систем широкий спектр IP-ядер периферийных компо-

нентов, разработанных не только фирмой Xilinx, но и третьими производителями.

Шинные интерфейсы Local Memory Bus™ (LMB) и Xilinx CacheLink™ (XCL) обес-

печивают возможность высокоскоростного доступа к внутренней и внешней (по от-

ношению к ПЛИС) памяти соответственно. Подробное описание архитектуры, пара-

метров и системы команд микропроцессорных ядер семейства MicroBlaze приведено

во второй части книги.

Микропроцессорные системы, выполненные на основе ядер семейства MicroBlaze,

способны поддерживать ряд операционных систем (ОС) реального времени (Real

Time Operating Systems, RTOS).

1.4. Краткая характеристика микропроцессорных ядер

семейства PowerPC

Микропроцессорные ядра семейства PowerPC, применяемые в ПЛИС фирмы

Xilinx, полностью соответствуют стандарту одноименных ядер фирмы IBM.

Характерными особенностями микропроцессорных ядер семейства PowerPC 405,

установленных в ПЛИС серий Virtex-II Pro и Virtex-4, являются:

возможность работы в системах с тактовыми частотами до 400 МГц;

высокая производительность, достигающая 600 DMIPS;

• применение специальных аппаратных блоков для выполнения операций умноже-

ния и деления;

ГЛАВА 1

9

блок регистров общего назначения, включающий 32 тридцатидвухразрядных ре-

гистра;

• наличие специального устройства управления памятью Memory Management Unit

(MMU), обеспечивающего поддержку ОС реального времени;

• применение усовершенствованного контроллера интерфейса встроенной блочной

памяти ПЛИС On-Chip Memory Block RAM;

• поддержка шинной архитектуры IBM CoreConnect™;

возможность использования кеш-памяти данных и команд объемом 16 Кбит;

наличие встроенных отладочных средств.

Структурное представление архитектуры микропроцессорного блока PowerPC

405 показано на рис. 1.1.

PLB Master Instruction

Read Interface ОСМ

Рис. 1.1. Обобщенная архитектура микропроцессорного ядра PowerPC 405

Основными элементами архитектуры являются:

центральное процессорное устройство (ЦПУ);

устройства управления памятью Memory Management Unit (MMU);

кеш-память данных;

кеш-память команд;

отладочный модуль;

таймер.

Детальное описание ПЛИС, содержащих аппаратные микропроцессорные ядра

семейства PowerPC, а также архитектуры, параметров и системы команд этих ядер

можно найти в [6-10].

Разработка проектов встраиваемых микропроцессорных систем на основе аппа-

ратных ядер семейства PowerPC выполняется средствами комплекса Xilinx EDK.

10

Зотов В. Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС

1.5. Краткий обзор основных средств проектирования,

предоставляемых фирмой Xilinx

Средства автоматизированного проектирования, предоставляемые фирмой

Xilinx, можно разбить на две группы. Первую группу образуют основные системы

разработки проектов и конфигурирования ПЛИС. Во вторую группу входят про-

граммные средства специального назначения.

Основными системами автоматизированного проектирования цифровых

устройств на основе ПЛИС фирмы Xilinx являются САПР серии Xilinx ISE, которые

заменили средства разработки предыдущего поколения Foundation Series™. Приме-

нение программных средств серии Xilinx ISE позволило значительно сократить время

разработки и повысить уровень эффективности результатов за счет применения

усовершенствованных методов проектирования, алгоритмов синтеза, размещения

и трассировки проекта в кристалле.

Программные средства серии Xilinx ISE представляют собой систему сквозного

проектирования, которая реализует полный цикл разработки цифровых устройств и

систем на основе ПЛИС, включающий этапы создания исходных описаний проекта,

синтеза, моделирования, размещения и трассировки, а также программирования кри-

сталла.

Отличительными особенностями систем автоматизированного проектирования

серии Xilinx ISE являются:

поддержка различных методов описания проектируемых устройств (графиче-

ских, в форме принципиальных схем или диаграмм состояний, и текстовых, с ис-

пользованием языков описания аппаратуры HDL (Hardware Description

Language);

возможность использования проектов, подготовленных в других системах проек-

тирования;

наличие схемотехнического редактора, укомплектованного набором обширных

библиотек;

интеллектуальные средства создания HDL-описаний, формирующие шаблоны на

основании информации, предоставляемой пользователем, для языков описания

аппаратуры VHDL™, Verilog™ и ABEL™ HDL;

• высокоэффективные встроенные средства синтеза HDL-проектов, поддержи-

вающие языки VHDL, Verilog и ABEL HDL;

интегрированный интерфейс для средств синтеза третьих фирм, обеспечиваю-

щий возможность применения, например, пакетов Synplicity Synplify™/Pro

и LeonardoSpectrum™, поддерживающих языки VHDL и Verilog;

развитые средства верификации проекта, позволяющие сократить полное время

разработки устройства за счет обнаружения возможных ошибок на более ранних

стадиях проектирования и сокращения длительности и количества возможных

итераций;

автоматические средства трассировки проекта в кристаллы различных семейств

ПЛИС фирмы Xilinx с учетом оптимизации проекта по различным параметрам;

единые средства программирования кристаллов всех семейств ПЛИС фирмы

Xilinx, выполненных по различной технологии (CPLD и FPGA), и конфигураци-

онных ППЗУ, поддерживающие несколько типов загрузочных кабелей JTAG-

интерфейса;

ГЛАВА 1

11

встроенный комплект вспомогательных программных средств, позволяющих по-

высить эффективность процесса проектирования, включающий анализатор ста-

тических временных характеристик Timing Analyzer™, интерактивный графиче-

ский редактор размещения Floorplanner™, модуль оценки потребляемой мощно-

сти XPower™, мастер подготовки описаний блоков синхронизации,

выполняемых на основе DCM, Architecture Wizard™, интерактивный графиче-

ский редактор топологических ограничений РАСЕ™ (Pinout and Area Constraints

Editor);

доступный для разработчика пользовательский интерфейс и наличие в каждом

модуле пакета справочной системы, сокращающие время освоения САПР;

наличие интегрированного с пакетом САПР набора инструментов и утилит дру-

гих фирм, предоставляющих дополнительные удобства в процессе проектирова-

ния, включающего утилиту генерации тестовых сигналов HDL Bencher™, про-

грамму моделирования ModelSim ХЕ III Starter™ и редактор диаграмм состояний

StateCAD™.

Средства проектирования серии Xilinx ISE выпускаются в трех конфигурациях:

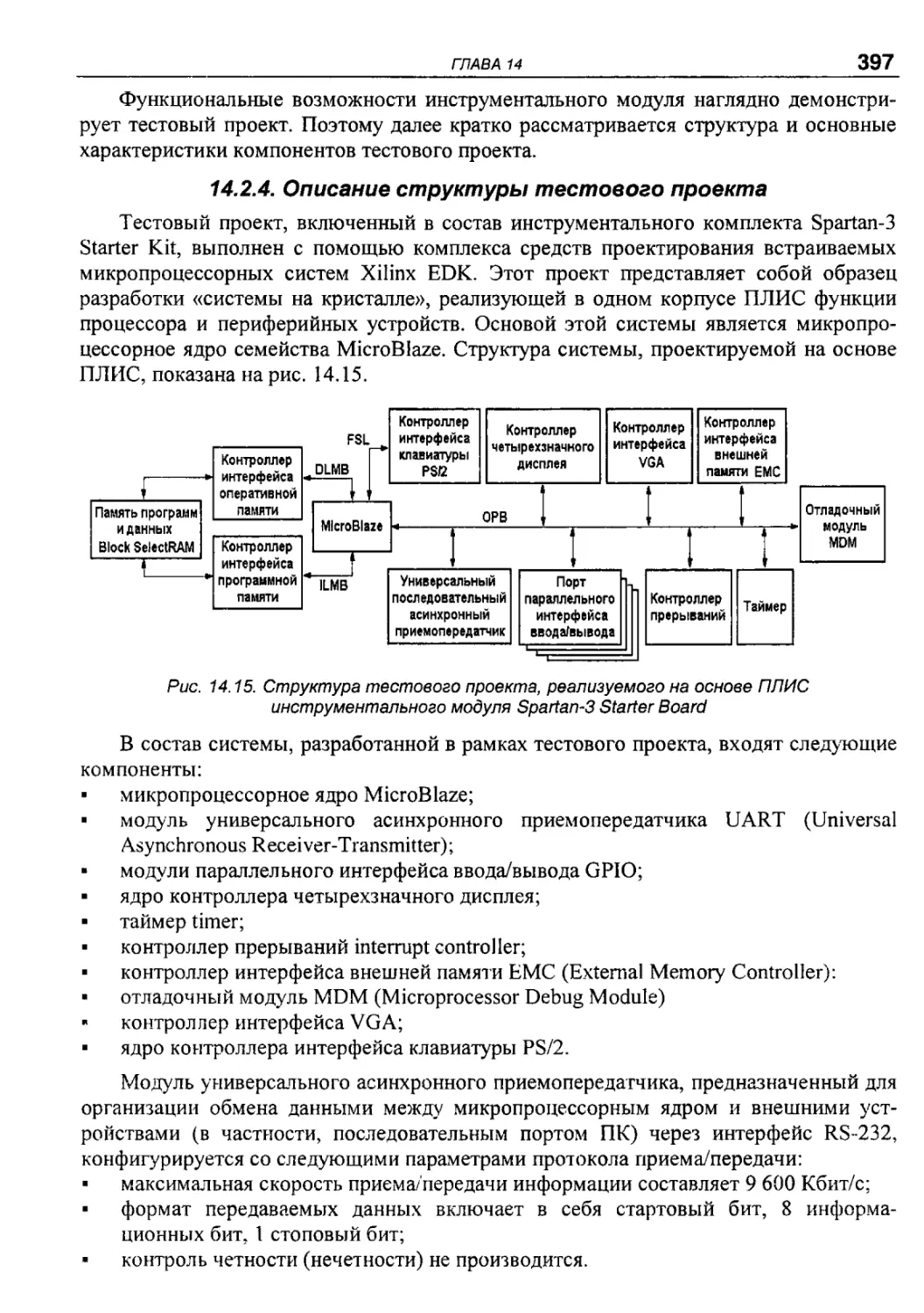

ISE Foundation™, ISE BaseX™ и ISE WebPACK™. Основное отличие между этими

конфигурациями заключается в количестве поддерживаемых кристаллов и наборе

дополнительных инструментов проектирования.

Программные средства ISE Foundation представляют собой наиболее полную

систему сквозного проектирования, которая поддерживает весь спектр ПЛИС, вы-

пускаемых фирмой Xilinx.

Экономичная конфигурация средств проектирования ISE BaseX имеет более низ-

кую стоимость по сравнению с ISE Foundation, но поддерживает не все типы ПЛИС.

Пакет ISE BaseX позволяет выполнять проекты на основе всех кристаллов семейств

CPLD и ПЛИС серий FPGA с логической емкостью не более 600 тыс. системных вен-

тилей. Кроме того, модуль программирования iMPACT™, входящий в состав пакета,

может применяться для конфигурирования практически всех кристаллов, выпускае-

мых фирмой Xilinx. Для создания конфигурационной последовательности при этом

используются другие средства проектирования, предоставляемые фирмой Xilinx.

Свободно распространяемая (бесплатная) модификация САПР ISE WebPACK

поддерживает все кристаллы семейств CPLD и ПЛИС серий FPGA с логической ем-

костью не более 300 тыс. системных вентилей. Кроме того, одно из главных отличий

пакета ISE WebPACK от конфигурации ISE BaseX состоит в отсутствии генератора

логических ядер CORE Generator и топологического редактора FPGA Editor.

Все конфигурации средств проектирования серии Xilinx ISE имеют одинаковую

структуру и пользовательский интерфейс. Поэтому переход от одной конфигурации

САПР к другой, например от свободно распространяемой системы проектирования

ISE WebPACK к полному пакету ISE Foundation, требует минимальных временных

затрат. Методика проектирования цифровых устройств в САПР ISE WebPACK дос-

таточно подробно отражена в [1].

К моменту подготовки данного материала последней версией средств проектиро-

вания серии Xilinx ISE, доступной для разработчиков, являлась версия 7. И. Инфор-

мация о семействах и типах ПЛИС, поддерживаемых различными конфигурациями

систем проектирования серии Xilinx ISE, приведена в табл. 1.3.

12 Зотов В. Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС

Таблица 1.3. Семейства и типы ПЛИС, поддерживаемые различными

конфигурациями систем проектирования серии Xilinx ISE

Семейство ПЛИС ISEWebPACK ISE BaseX ISE Foundation

Virtex XCV50 -XCV600 Bee

Virtex-E XCV50E-XCV300E XCV50E -XCV600E Bee

Virtex-II XC2V40 - XC2V250 XC2V40-XC 2V500 Bee

Virtex-II Pro XC2VP2 XC2VP2, XC2VP4, XC2VP7 Bee

Virtex-4 XC4VLX15, XC4VLX25 LX:XC4VLX15, XC4VLX25; SX: XC4VSX25, FX: XC4VFX12 Bee

Spartanll Bee Bee Bee

SpartanllE XC2S50E - XC2S300E Bee Bee

Spartan-3 XC3S50-XC3S1500 XC3S50-XC3S1500 Bee

Spartan-3E XC3S100E-XC3S500E Bee Bee

Spartan-3L XC3S1000L, XC3S1500L XC3S1000L, XC3S1500L Bee

CoolRunnerXPLA3 Bee Bee Bee

CoolRunner-ll Bee Bee Bee

CoolRunner-IIA Bee Bee Bee

XC9500 Bee Bee Bee

XC9500 XL Bee Bee Bee

XC9500 XV Bee Bee Bee

Функциональные возможности всех конфигураций САПР серии Xilinx ISE вер-

сии 7.1 i отражает табл. 1.4.

Таблица 1.4. Функциональные возможности различных конфигураций САПР

серии Xilinx ISE версии 7.1 i

Возможности САПР ISE WebPACK ISE BaseX ISE Foundation

Схемотехнический редактор + + +

Редактор HDL-кода + + +

Редактор диаграмм состояний State Diagram Editor + для MS Windows + для MS Windows + для MS Windows

Генератор параметризированных модулей CORE Generator System - + +

Графический редактор топологических ог- раничений РАСЕ (Pinout and Area Constraint Editor) + + +

Мастер формирования описаний блоков синхронизации Architecture Wizard + + +

Использование генератора системных IP- ядер Xilinx System Generator - + +

Использование EDK для разработки встраиваемых микропроцессорных систем • + +

Средства синтеза Xilinx Synthesis Technol- ogy (XST) + + +

Интегрированный интерфейс для средств синтеза Synplicity Synplify/Pro + + +

Интегрированный интерфейс для средств синтеза Leonardo Spectrum + + +

EDIF интерфейс для Synopsys DC-FPGA Compiler + + +

Средства синтеза ABEL Для CPLD MS Windows Для CPLD MS Windows Для CPLD MS Windows

ГЛАВА 1

13

Возможности САПР ISEWebPACK ISE BaseX ISE Foundation

Интерактивный графический редактор раз- мещения Floorplanner + + +

Редактор ограничений Constraints Editor + + +

Средства программирования IMPACT, System АСЕ Configuration Manager, CableServer + + +

Формирование моделей IBIS, STAMP, HSPICE и LMG SmartModels + + +

Генератор тестовых сигналов HDL Bencher + для MS Windows + для MS Windows +для MS Windows

Программа HDL-моделирования ModelSim XE III Starter + + +

Анализатор статических временных харак- теристик Static Timing Analyzer + + +

Поддержка средств ChipScope Pro + + +

Топологический редактор FPGA Editor - + +

Программа анализа потребляемой мощно- сти XPower + + +

Модульное проектирование + + +

Программа визуализациии топологии CPLD ChipViewer + + +

Возможность использования средств моде- лирования ISE Simulator - - +

Ограниченная версия средств моделирова- ния ISE Simulator Lite - + +

Поддерживаемые платформы/ ОС PC (MS Windows 2000/MS Windows XP), Red Hat Enter- prise Linux 3 PC (MS Windows 2000/ MSWindows XP), Red Hat Enter- prise Linux 3 PC (MS Windows 2000/ MS WindowsXP), Sun Solaris, Red Hat Enterprise Linux 3

В качестве инструментов моделирования в САПР серии Xilinx ISE версии 7. li

могут использоваться средства ISE Simulator™ или система ModelSim™, которая яв-

ляется самостоятельным программным продуктом, выпускаемым корпорацией Model

Technology® (одним из подразделений компании Mentor Graphics®).

Полнофункциональная версия системы HDL-моделирования ISE Simulator может

применяться только совместно со средствами проектирования ISE Foundation. При

этом следует обратить внимание на то, что эта версия системы моделирования не

входит в комплект ISE Foundation и поставляется отдельно. В состав средств разра-

ботки проектов и программирования ПЛИС ISE Foundation и ISE BaseX включена

только версия системы моделирования с ограниченными возможностями ISE

Simulator Lite.

В настоящее время ModelSim является одной из самых распространенных систем

HDL-моделирования. Это обусловлено целым рядом уникальных характеристик это-

го пакета. Пакет программных средств ModelSim предназначен для моделирования

цифровых систем, которые представлены в виде HDL-описаний, выполненных с ис-

пользованием языков высокого уровня VHDL и Verilog.

Система моделирования ModelSim выпускается в двух основных редакциях:

Special Edition (SE), функционирующей под управлением ОС UNIX™, Linux™,

Windows™ 98, Windows ME, Windows 2000, Windows NT, Windows XP и Personal

14

Зотов В. Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС

Edition (РЕ), предназначенной только для ОС семейства Windows. Кроме того, име-

ются специализированные редакции, предназначенные для интеграции с пакетами

САПР третьих фирм. Примером специализированной редакции является Modelsim

Xilinx Edition (ХЕ), которая ориентирована на интеграцию с программным обеспече-

нием фирмы Xilinx. Все конфигурации САПР серии Xilinx ISE комплектуются сво-

бодно распространяемой версией ModelSim ХЕ III Starter. Эта версия имеет одно су-

щественное ограничение - исходный текст описания не должен превышать фиксиро-

ванное число исполняемых выражений. При несоблюдении этого условия программа

моделирования сохраняет работоспособность, но функционирует с пониженной про-

изводительностью. Версия средств моделирования - ModelSim Xilinx Edition, имею-

щая ограничение 40 тыс. исполняемых выражений (примерно проект на 1 млн сис-

темных вентилей), приобретается отдельно и устанавливается в режиме функциони-

рования под управлением САПР серии Xilinx ISE.

К группе средств проектирования специального назначения относятся:

комплекс средств проектирования встраиваемых микропроцессорных систем

Xilinx EDK, позволяющий выполнять совместное проектирование аппаратной

части и программного обеспечения;

программный комплекс внутрикристальных отладочных средств ChipScope

Pro™ Software, включающий в себя, в частности, ядра логического анализатора,

анализатора состояния шин;

инструмент разработки устройств цифровой обработки сигналов System

Generator™.

Все перечисленные программные средства функционируют только в комплексе с

соответствующей конфигурацией и версией систем проектирования серии Xilinx ISE.

В настоящем издании будут подробно рассмотрены вопросы применения САПР

серии Xilinx ISE и пакета Xilinx EDK в процессе разработки встраиваемых микро-

процессорных систем, выполняемых на основе конфигурируемых ядер семейств

PicoBlaze и MicroBlaze. Для практического освоения методов проектирования

встраиваемых микропроцессорных систем, реализуемых на основе ПЛИС фирмы

Xilinx, можно воспользоваться бесплатными 60-дневными версиями пакетов САПР

Xilinx EDK и ISE Foundation. Чтобы получить данные версии указанных пакетов,

следует обращаться к официальному дистрибьютору фирмы Xilinx в России, Белару-

си и Украине, которым является центр поддержки и продаж InlineGROUP

(http://www.plis.ru/).

2. МИКРОПРОЦЕССОРНОЕ ЯДРО PICOBLAZE,

ПРЕДНАЗНАЧЕННОЕ ДЛЯ РАЗРАБОТКИ ВСТРАИВАЕМЫХ

СИСТЕМ НА ОСНОВЕ ПЛИС ФИРМЫ XILINX СЕМЕЙСТВ

SPARTAN-II, SPARTAN-IIE, VIRTEX, VIRTEX-E

Настоящая глава знакомит с основными характеристиками и архитектурой мик-

ропроцессорных ядер семейства PicoBlaze. Несмотря на то что приводимая здесь ин-

формация относится в первую очередь к базовому варианту микропроцессорного яд-

ра, предназначенному для применения в составе проектов, которые реализуются на

базе ПЛИС серий Spartan-II, Spartan-IIE, Virtex, Virtex-E, большая часть ее справед-

лива и для остальных представителей семейства PicoBlaze. Поэтому при рассмотре-

нии других модификаций микропроцессорного ядра PicoBlaze в последующих

главах основное внимание уделяется только их отличиям по сравнению с базовым

вариантом.

2.1. Основные характеристики микропроцессорного ядра

PicoBlaze (семейства Spartan-II, Spartan-IIE, Virtex, Virtex-E)

Отличительными особенностями микропроцессорного ядра PicoBlaze, предна-

значенного для применения в ПЛИС семейств Spartan-II, Spartan-IIE, Virtex, Virtex-E,

являются:

гибкая архитектура с раздельными шинами данных и команд;

разрядность шины данных - 8 бит;

разрядность шины адреса - 8 бит;

разрядность шины команд - 16 бит;

8-разрядное арифметическо-логическое устройство (АЛУ), реализующее логиче-

ские функции, операции сложения, вычитания и сдвига;

поддержка 49 команд;

постоянное время выполнения всех команд - два машинных цикла;

16 регистров общего назначения;

15-уровневый стек;

возможность поддержки до 256 входных и выходных портов;

встроенное ППЗУ микропрограмм, выполненное на основе блочной памяти

ПЛИС Block SelectRAM, объем которого составляет 256 х 16 разрядов;

поддержка прямого, косвенного и непосредственного режимов адресации;

реализация в виде модулей исходного описания на языке VHDL с учетом опти-

мального размещения и трассировки в кристалле соответствующего семейства;

минимальный объем ресурсов кристалла, используемых для реализации микро-

процессорного ядра, позволяет без труда разместить в кристалле другие функ-

циональные модули проектируемой системы, включая интерфейсы ввода/вывода

(в ПЛИС семейства Spartan-IIE ядро PicoBlaze занимает всего лишь 76 секций

(slices), что составляет 9 % от полного объема логических ресурсов кристалла

XC2S50E и 2,5 % от логической емкости ПЛИС XC2S300E);

гибкий интерфейс микропроцессорного ядра, обеспечивающий оптимальное его

сопряжение с периферийными модулями, которые реализуются на основе сво-

бодных логических ресурсов кристалла;

16

Зотов В. Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС

достаточно высокая производительность, достигающая 40 MIPS (в зависимости

от типа используемого кристалла);

наличие ассемблера, формирующего необходимые файлы различного формата,

который обеспечивает высокую скорость и наглядность процесса разработки

программ;

наличие входа сброса (инициализации), позволяющего перевести микропроцес-

сор в начальное состояние;

• полная совместимость компонентов ядра со всей линией средств разработки

проектов и программирования ПЛИС серии Xilinx ISE (ISE WebPACK [1], ISE

BaseX, ISE Foundation);

возможность моделирования ядра в составе разрабатываемых проектов с помо-

щью системы ModelSim ХЕ [1], которая включена в состав пакетов САПР серии

Xilinx ISE в ограниченной конфигурации ModelSim ХЕ Starter.

2.2. Архитектура микропроцессорного ядра PicoBlaze (семейства

Spartan-II, Spartan-IIE, Virtex, Virtex-E)

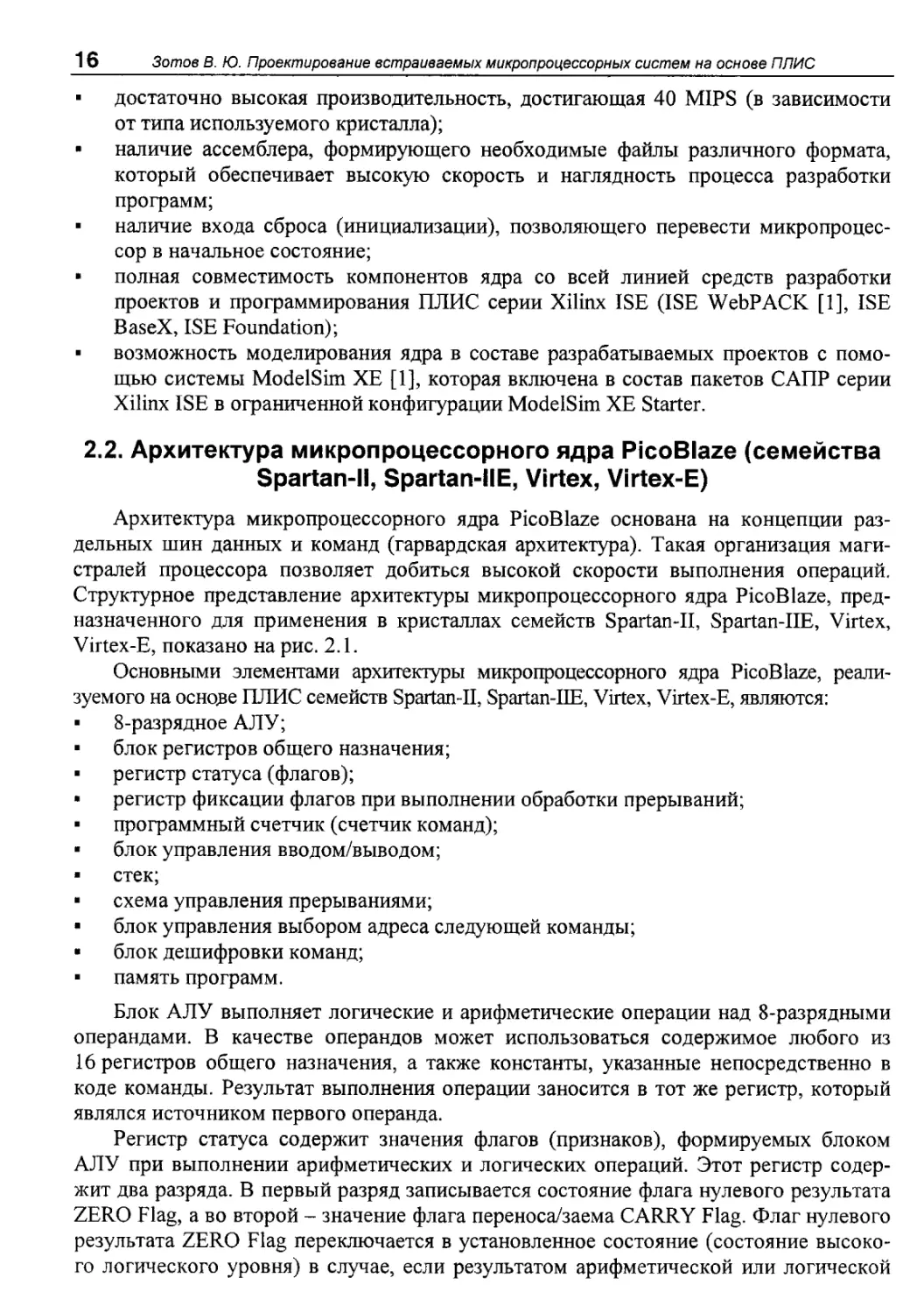

Архитектура микропроцессорного ядра PicoBlaze основана на концепции раз-

дельных шин данных и команд (гарвардская архитектура). Такая организация маги-

стралей процессора позволяет добиться высокой скорости выполнения операций.

Структурное представление архитектуры микропроцессорного ядра PicoBlaze, пред-

назначенного для применения в кристаллах семейств Spartan-II, Spartan-IIE, Virtex,

Virtex-E, показано на рис. 2.1.

Основными элементами архитектуры микропроцессорного ядра PicoBlaze, реали-

зуемого на основе ПЛИС семейств Spartan-II, Spartan-IIE, Virtex, Virtex-E, являются:

8-разрядное АЛУ;

блок регистров общего назначения;

регистр статуса (флагов);

• регистр фиксации флагов при выполнении обработки прерываний;

программный счетчик (счетчик команд);

блок управления вводом/выводом;

стек;

схема управления прерываниями;

блок управления выбором адреса следующей команды;

- блок дешифровки команд;

память программ.

Блок АЛУ выполняет логические и арифметические операции над 8-разрядными

операндами. В качестве операндов может использоваться содержимое любого из

16 регистров общего назначения, а также константы, указанные непосредственно в

коде команды. Результат выполнения операции заносится в тот же регистр, который

являлся источником первого операнда.

Регистр статуса содержит значения флагов (признаков), формируемых блоком

АЛУ при выполнении арифметических и логических операций. Этот регистр содер-

жит два разряда. В первый разряд записывается состояние флага нулевого результата

ZERO Flag, а во второй - значение флага переноса/заема CARRY Flag. Флаг нулевого

результата ZERO Flag переключается в установленное состояние (состояние высоко-

го логического уровня) в случае, если результатом арифметической или логической

ГЛАВА 2

17

операции является нуль. При получении других результатов этот флаг сбрасывается в

состояние низкого логического уровня. Флаг переноса/заема CARRY Flag устанавли-

вается в том случае, если в результате операции сложения из самого старшего разря-

да происходит перенос или образуется заем при выполнении операции вычитания.

Анализ состояния флагов, записанных в соответствующие разряды регистра статуса,

производится при выполнении условных команд. Кроме того, регистр статуса при-

нимает участие в процессе выполнения операций сдвига.

Рис. 2.1. Архитектура микропроцессорного ядра PicoBlaze, реализуемого на основе ПЛИС

семейств Spartan-ll, Spartan-IIE, Virtex, Virtex-E

Регистр фиксации флагов предназначен для сохранения текущих значений при-

знаков результата операции АЛУ, записанных в регистр статуса, перед выполнением

процедуры обслуживания прерывания.

Блок регистров общего назначения содержит 16 восьмиразрядных регистров,

обозначаемых по порядку sO-sF . Эти регистры предназначены для хранения данных,

поступающих из входных портов ввода/вывода, операндов и результатов выполнения

операций. Все регистры имеют одинаковый статус (полностью равноправны). Любой

из них может использоваться в качестве аккумулятора.

Схема управления прерываниями формирует комбинацию управляющих сигна-

лов, необходимых для выполнения процедуры обработки прерываний. Микропроцес-

18

Зотов В. Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС

сорное ядро PicoBlaze изначально содержит единственную цепь сигнала прерывания.

Для создания комплексной системы прерываний, поддерживающей комбинацию не-

скольких сигналов, следует использовать дополнительную логику, которая реализу-

ется на основе свободных ресурсов кристалла.

Блок управления вводом/выводом предназначен для формирования адреса вход-

ного или выходного порта PORT_ID[7:0], к которому производится обращение,

а также сигналов WRITE STROBE и READ STROBE, указывающих тип выполняе-

мой операции (записи или чтения в указанный порт). Адрес порта ввода/вывода мо-

жет задаваться в программе в виде абсолютного значения или в форме ссылки на

один из регистров общего назначения, содержимое которого определяет номер порта.

Во время выполнения операции ввода INPUT данные из входного порта, номер кото-

рого определяет комбинация значений сигналов в шине адреса порта PORT_ID[7:0],

могут быть загружены в любой из 16 регистров общего назначения. Эта процедура

сопровождается формированием импульсного сигнала READSTROBE. При осуще-

ствлении операции вывода OUTPUT информация из любого регистра общего назна-

чения может быть передана в выходной порт, номер которого указывает комбинация

значений сигналов в шине адреса порта PORT_ID[7:()]. Выполнение операции выво-

да сопровождается стробом записи WRITEJSTROBE.

Память программ представляет собой запоминающее устройство, реализуемое

в виде однопортового ОЗУ на основе блочной памяти кристалла Block SelectRAM,

в котором хранится последовательность выполняемых команд.

Блок дешифровки команд на основании данных, поступающих с выходов про-

граммной памяти, формирует совокупность управляющих сигналов, необходимых

для выполнения соответствующей операции, которые подаются на все блоки микро-

процессорного ядра.

Управление последовательностью выполнения команд в составе программы

осуществляется с помощью программного счетчика. Сигналы на его выходах обра-

зуют адрес выборки следующей команды. Эти сигналы по шине адресов команд пе-

редаются на адресные входы программной памяти. Режим работы программного

счетчика (счет или загрузка) определяется состоянием сигналов, формируемых в

блоке управления выбором следующего адреса команды. В основном режиме, при

отсутствии прерываний, команд переходов, вызовов и возврата из подпрограмм, со-

держимое программного счетчика автоматически увеличивается на единицу при ис-

полнении текущей операции. Таким образом реализуется последовательная выборка

и выполнение команд программы.

В процессе выполнения команд перехода в программный счетчик производится

загрузка значения, соответствующего адресу, по которому осуществляется передача

управления в программе. После исполнения команды перехода программный счетчик

продолжает работу в инкрементном режиме, но уже начиная с нового значения, ко-

торое было записано при ее выполнении.

При вызове подпрограмм также осуществляется принудительное изменение со-

держимого программного счетчика. В него загружается значение, которое соответст-

вует начальному адресу выполняемой подпрограммы. Перед этим прежнее содержи-

мое программного счетчика заносится в стек (в регистр, адрес которого определяется

ГЛАВА 2

19

текущим значением указателя стека). В процессе выполнения команд подпрограммы

производится последовательное инкрементирование нового содержимого программ-

ного счетчика. После завершения подпрограммы при выполнении команды возврата

в основную программу из стека извлекается последнее записанное значение адреса,

которое увеличивается на единицу и загружается в программный счетчик. Тем самым

осуществляется переход к выполнению очередной команды, следующей после вызо-

ва подпрограммы. Так как глубина стека составляет 15 уровней, то он может хранить

одновременно до 15 адресов возврата. Поэтому в процессе исполнения подпрограмм

допускаются вложенные вызовы других подпрограмм. При очередном вложенном

вызове подпрограммы содержимое программного счетчика заносится в следующий

регистр стека. Процесс выполнения каждой вложенной подпрограммы завершается

«выталкиванием» из стека последнего записанного значения, которое, увеличиваясь

на единицу, заносится в программный счетчик.

Процедура обработки прерывания выполняется подобно вызову подпрограммы,

но имеются несколько отличий. Одно из них заключается в том, что при наличии ак-

тивного уровня сигнала на входе прерывания в программный счетчик загружается

адрес вектора соответствующей процедуры обработки. При этом, кроме записи в стек

адреса текущей исполняемой команды, производится сохранение состояния призна-

ков результата операции АЛУ (содержимого регистра статуса) на момент прерыва-

ния в регистре фиксации флагов. После завершения процесса обработки прерывания

происходит автоматическое восстановление значений флагов в регистре статуса.

В начальный момент времени функционирования микропроцессорного ядра,

а также при подаче внешнего сигнала сброса выходы программист > счетчика уста-

навливаются в нулевое состояние (низкого логического уровня). Таким образом

управление передается первой команде программы.

2.3. Структура проекта микропроцессорного ядра PicoBlaze

(семейства Spartan-II, Spartan-IIE, Virtex, Virtex-E)

Обобщенная структура микропроцессорного ядра PicoBlaze, предназначенного

для применения в составе проектов, выполняемых на основе ПЛИС семейств Spartan-

II, Spartan-IIE, Virtex, Virtex-E, показана на рис. 2.2. Она включает в себя програм-

мную память и модуль центрального процессорного устройства (ЦПУ) (испол-

нительного устройства) PicoBlaze. В качестве ППЗУ микропрограмм используется

один модуль блочной памяти Block SelectRAM кристаллов указанных семейств, объ-

ем которого составляет 4 Кбит. Этот модуль блочной памяти конфигурируется как

однопортовое ОЗУ с организацией 256 х 16 разрядов.

Микропроцессорное ядро PicoBlaze предоставляется пользователям в виде

архива, в котором содержится комплект файлов, включающий в себя необходи-

мые модули VHDL-описаний, ассемблер, тестовые примеры, иллюстрирующие

использование компонентов ядра. Кроме того, в состав комплекта входят допол-

нительные файлы, которые могут быть использованы для включения в состав

проекта универсального асинхронного приемопередатчика UART (Universal

Asynchronous Receiver-Transmitter).

20

Зотов В. Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС

Модуль ЦПУ (исполнительный модуль) PicoBlaze

о Входные данные —— Прерывание Сброс Память программ Тактовый сигнал -i -э IN_PORT[7:0] OUT_PORT[7:0] INTERRUPT PORTJD[7:0] RESET READ.STROBE > CLK WR1TE.STR0BE INSTRUCTIONS 5:0] ADDRESS[7:0] g —* Выходные данные 8 . Адрес порта ввода/вывода > Строб чтения > Строб записи

INSTRUCTION[16:0] ADDRESS[7:0] >CLK 16,

Шина команд Шина адреса

8/

Рис. 2.2. Обобщенная структура микропроцессорного ядра PicoBlaze, реализуемого на основе

ПЛИС семейств Spartan-II, Spartan-IIE, Virtex, Virtex-E

Каждый элемент обобщенной структуры микропроцессорного ядра PicoBlaze

(рис. 2.2) представлен в форме соответствующего компонента, выполненного в виде

макроса с относительным размещением. Функции исполнительного модуля реализу-

ет компонент KCPSM (Constant (k) Coded Programmable State Machine). Описание

этого модуля на языке VHDL содержится в файле kcpsm.vhd. Для применения ком-

понента KCPSM в качестве элемента проектируемой системы необходимо прежде

всего включить в состав ее описания выражения декларации, которые выглядят сле-

дующим образом:

component kcpsm

Port (

address: out std_logic_vector(7 downto 0);

instruction: in stdjogic_vector(15 downto 0);

portJd : out stdjogic_vector(7 downto 0);

write_strobe: out stdjogic;

out_port: out std_logic_vector(7 downto 0);

read_strobe: out stdjogic;

in_port: in stdjogic_vector(7 downto 0);

interrupt: in stdjogic;

reset: in stdjogic;

elk: in stdjogic

);

end component;

В приведенных выражениях декларации используется следующая система обо-

значений интерфейсных цепей компонента. Идентификаторы elk, reset и interrupt,

описывают соответственно входы тактового сигнала, сброса и прерывания,

a read_strobe и writestrobe соответствуют выходам сигналов, сопровождающих опе-

рации чтения и записи данных в порты ввода/вывода. Векторы in_port и out_port

представляют соответственно входную и выходную шины данных. Вектор address

соответствует выходной шине адресов команд, instruction - входной шине команд,

port_id соответствует выходной шине адресов портов ввода/вывода.

Для создания одного экземпляра компонента kcpsm, представляющего модуль

ЦПУ, необходимо в состав структурного описания архитектуры проектируемой сис-

темы включить следующий оператор:

ГЛАВА 2

21

inst_name_processor: kcpsm

port map(

address => address_signal,

instruction => instruction_signal,

portjd => port_id_signal,

write-Strobe => writG-Strobe„signal,

ouLport => out-port-Signal,

read-Strobe => read_strobe_signal,

in_port => in_port_signal,

interrupt => interrupt_signal,

reset => reset-signal,

elk => clk_signal

);

Вместо идентификатора inst_name-processor следует задать метку, определяю-

щую позиционное обозначение экземпляра компонента. Кроме того, названия сигна-

лов, указанные в операторе, должны соответствовать именам сигналов, которые ис-

пользуются в описании проектируемого устройства.

Таким же способом, в виде компонента с названием prog_rom, описывается мо-

дуль программной памяти в составе разрабатываемой системы. Вначале выполняется

декларация этого компонента, которая выглядит следующим образом:

component prog_rom

Port (

address: in stdjogic_vector(7 downto 0);

instruction : out std_logic_vector(15 downto 0);

elk: in stdjogic

end component;

В описании интерфейса компонента prog_rom идентификатор elk соответствует

входу тактового сигнала, address - входной шине адресов команд, instruction - вы-

ходной шине команд. Создание экземпляра компонента, представляющего про-

граммную память, выполняется следующим оператором:

inst_name_program: prog_rom

port map(

address => address_signal,

instruction => instruction_signal,

elk => cik_signal

);

При практическом использовании этого компонента следует учитывать, что его

название должно совпадать с идентификатором файла, имеющего расширение PSM,

в котором записан исходный текст микропроцессорной программы.

Помимо отдельных компонентов, рассмотренных выше, пользователю также

доступно VHDL-описание объекта EMBEDDEDKCPSM, который представляет

встраиваемое микропроцессорное ядро PicoBlaze в целом, в виде подсистемы, со-

стоящей из модуля ЦПУ и подключенной к нему программной памяти. Описание

этого объекта является наглядной иллюстрацией практического применения компо-

нентов микропроцессорного ядра, и поэтому далее полностью приводится его текст.

22

Зотов В. Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС

- EMBEDDED_KCPSM.VHD

-- Standard IEEE libraries

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity embedded_kcpsm is

Port ( portjd: out std_logic_vector(7 downto 0);

write_strobe: out stdjogic;

read_strobe: out stdjogic;

out_port: out std_logic_vector(7 downto 0);

in_port: in std_logic_vector(7 downto 0);

interrupt: in stdjogic;

reset: in stdjogic;

elk: in stdjogic);

end embedded_kcpsm;

-- Start of test achitecture

architecture connectivity of embedded_kcpsm is

-- declaration of KCPSM

component kepsm

Port ( address: out std_logic_vector(7 downto 0);

instruction: in std_logic_vector(15 downto 0);

portjd: out std_logic_vector(7 downto 0);

write_strobe: out stdjogic;

out_port: out std_logic_vector(7 downto 0);

read_strobe: out stdjogic;

in_port: in std_logic_vector(7 downto 0);

interrupt: in stdjogic;

reset: in stdjogic;

elk: in stdjogic);

end component:

-- declaration of program ROM

component prog_rom

Port ( address: in std_logic_vector(7 downto 0);

instruction : out std_logic_vector(15 downto 0);

ГЛАВА 2

23

elk: in stdjogic);

end component;

-- Signals used to connect KCPSM to program ROM

signal address: stdjogic_vector(7 downto 0);

signal instruction : stdjogic_vector(15 downto 0);

~ Start of test circuit description

begin

processor: kepsm

port map( address => address,

instruction => instruction,

portjd => portjd,

write_strobe => write_st robe,

ouLport -> ouLport,

read_strobe => read_strobe,

in_port => in_port,

interrupt => interrupt,

reset => reset,

elk => elk);

program: prog_rom

port map( address => address,

instruction => instruction,

elk => elk);

end connectivity;

- END OF FILE EMBEDDEDJ<CPSM.VHD

Приведенное описание объекта EMBEDDED_KCPSM имеет стандартную струк-

туру исходного модуля, выполненного с применением языка VHDL [19, 20]. В начале

описания указаны ссылки на используемые стандартные библиотеки и пакеты. Затем

следуют операторы, описывающие интерфейс объекта. Далее приводится структур-

ное описание архитектуры объекта.

Объект EMBEDDED KCPSM, описывающий микропроцессорное ядро PicoBlaze,

может применяться как автономно, так и в виде модуля, входящего в состав разраба-

тываемой системы. В последнем случае это встраиваемое ядро используется в форме

одноименного компонента embedded_kcpsm. Для декларации компонента embedded

_kcpsm в составе VHDL-описания проектируемой системы используется следующая

конструкция:

component embeddedJccpsm

Port (

portjd: out stdjogic_vector(7 downto 0);

write_strobe: out stdjogic;

24

Зотов В. Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС

read_strobe: out stdjogtc;

out_port: out std_logic_vector(7 downto 0);

in_port: in std_logic_vector(7 downto 0);

interrupt: in stdjogic;

reset: in stdjogic;

elk: in stdjogic

);

end embeddedJccpsm;

В описании интерфейса компонента embeddedJkcpsm используется та же система

обозначений, что и для компонента kepsm. Конкретный экземпляр компонента, пред-

ставляющего микропроцессорное ядро PicoBlaze, создается в структурном описании

проектируемой системы с помощью оператора, текст которого представлен ниже.

При практическом использовании этого оператора следует заменить метку

inst_name_embedded-processor идентификатором, который, как правило, соответству-

ет позиционному обозначению экземпляра компонента в составе описания проекта.

При описании внешних связей компонента embeddedJkopsm должны быть указаны

названия соответствующих сигналов, используемых в проекте.

inst_name_embedded_processor: embedded_kcpsm

port map(

port Jd => portJd_signal,

write_strobe => write_strobe_signal,

read_strobe => read_strobe_signal,

ouLport => out_port_signal,

in_port => in_port_signal,

interrupt => interrupt- signal,

reset => reseLsignal,

elk => clk_signal

);

Полный текст VHDL-описания исполнительного устройства kepsm приведен

в прил. 1. Наличие исходного описания компонентов микропроцессорного ядра Pi-

coBlaze открывает широкие возможности для его модификации в соответствии с тре-

бованиями разработчика. Проанализировав текст исходных VHDL-описаний, пользо-

ватель может достаточно легко добавить поддержку дополнительных команд.

2.4. Общая характеристика системы команд, поддерживаемых

микропроцессорным ядром PicoBlaze (семейства Spartan-II,

Spartan-IIE, Virtex, Virtex-E)

Совокупность команд, поддерживаемых микропроцессорным ядром PicoBlaze,

можно разбить по функциональному признаку на 6 групп. К первой группе относятся

команды, управляющие последовательностью выполнения операций в программе,

и команды обработки подпрограмм. В эту группу входят команды переходов JUMP,

вызова подпрограмм CALL и возврата из подпрограмм RETURN. Каждая из перечис-

ленных команд представлена как в безусловной форме, так и в условном формате

(т. е. может исполняться только при выполнении определенного условия).

Вторую группу образуют логические команды. Эти команды выполняют пораз-

рядные операции «Логическое И» (поразрядное умножение) - AND, «Логическое

ИЛИ» (поразрядное сложение) - OR, «Исключающее ИЛИ» - XOR. В качестве one-

ГЛАВА 2

25

рандов могут выступать содержимое любого регистра общего назначения и констан-

та, указанная непосредственно в тексте инструкции, а также содержимое двух реги-

стров блока РОН. К этой же группе относится команда загрузки значения в регистр

общего назначения LOAD. С помощью этой команды в выбранный регистр может за-

писываться константа, указанная в тексте команды, или содержимое другого регист-

ра блока РОН.

В третью группу входят арифметические команды. Команды ADD и ADDCY

предназначены для получения суммы двух операндов без учета и с учетом входного

переноса соответственно. Операция вычитания также может выполняться без учета и

с учетом заема с помощью команд SUB и SUBCY соответственно. Значение одного из

операндов, участвующих в арифметических операциях, содержится в регистре обще-

го назначения, номер которого указан в виде параметра команды. В качестве второго

операнда может употребляться значение, заданное непосредственно в коде команды,

или содержимое другого регистра блока РОН.

Четвертую группу составляют команды сдвига. Они позволяют реализовать опе-

рации логического (арифметического) или циклического сдвига данных, записанных

в регистре общего назначения, номер которого указан в тексте команды. В процессе

выполнения одной команды сдвиг производится на один разряд. Сдвиг может осуще-

ствляться как влево (в сторону младшего разряда), так и вправо (в сторону старшего

разряда). Операции циклического сдвига могут выполняться с участием разряда пе-

реноса регистра статуса.

Пятая группа включает в себя команды ввода/вывода. Эти команды предназначе-

ны для организации обмена данными между регистрами, входящими в блок РОН,

и портами ввода/вывода. Выполнение операций чтения данных из входного порта в

регистр общего назначения (INPUT) и записи информации из регистра в выходной

порт (OUTPUT) рассмотрено выше, в разделе описания архитектуры микропроцес-

сорного ядра PicoBlaze.

Последняя группа объединяет команды, используемые для обслуживания преры-

ваний. В нее входят команды разрешения ENABLE INTERRUPT и запрета прерыва-

ний DISABLE INTERRUPT.

Более подробно синтаксис и выполнение команд микропроцессорного ядра

PicoBlaze, предназначенного для применения в проектах, реализуемых на основе

ПЛИС семейств Spartan-II, Spartan-IIE, Virtex, Virtex-E, будут рассмотрены в гл. 3.

3. СИСТЕМА КОМАНД МИКРОПРОЦЕССОРНОГО ЯДРА

PICOBLAZE, РЕАЛИЗУЕМОГО НА ОСНОВЕ ПЛИС СЕМЕЙСТВ

SPARTAN-II, SPARTAN-IIE, VIRTEX, VIRTEX-E

Команды, рассматриваемые в данной главе, поддерживаются всеми вариантами

микропроцессорных ядер семейства PicoBlaze. Процесс их исполнения инвариантен

по отношению к версии микропроцессорного ядра. Различия в формате инструкций

будут указаны в соответствующих главах при описании характеристик и архитекту-

ры каждой конкретной модификации ядра PicoBlaze.

3.1. Команды управления последовательностью выполнения

операций в программе

Команды переходов JUMP позволяют осуществить передачу управления в про-

грамме по указанному адресу. Эти команды обычно используются для организации

ветвления и формирования циклов в ходе выполнения алгоритма программы. Мик-

ропроцессорное ядро PicoBlaze поддерживает 5 модификаций инструкции переходов

JUMP: Qjspy безусловную и 4 условных. Форматы различных вариантов команд пере-

ходов JUMP представлены в табл. 3.1. Единственным параметром команд переходов

является 1-байтовая константа, значение которой определяет адрес перехода. При

мнемонической форме записи команд этот параметр задается в виде двух шестнадца-

теричных символов.

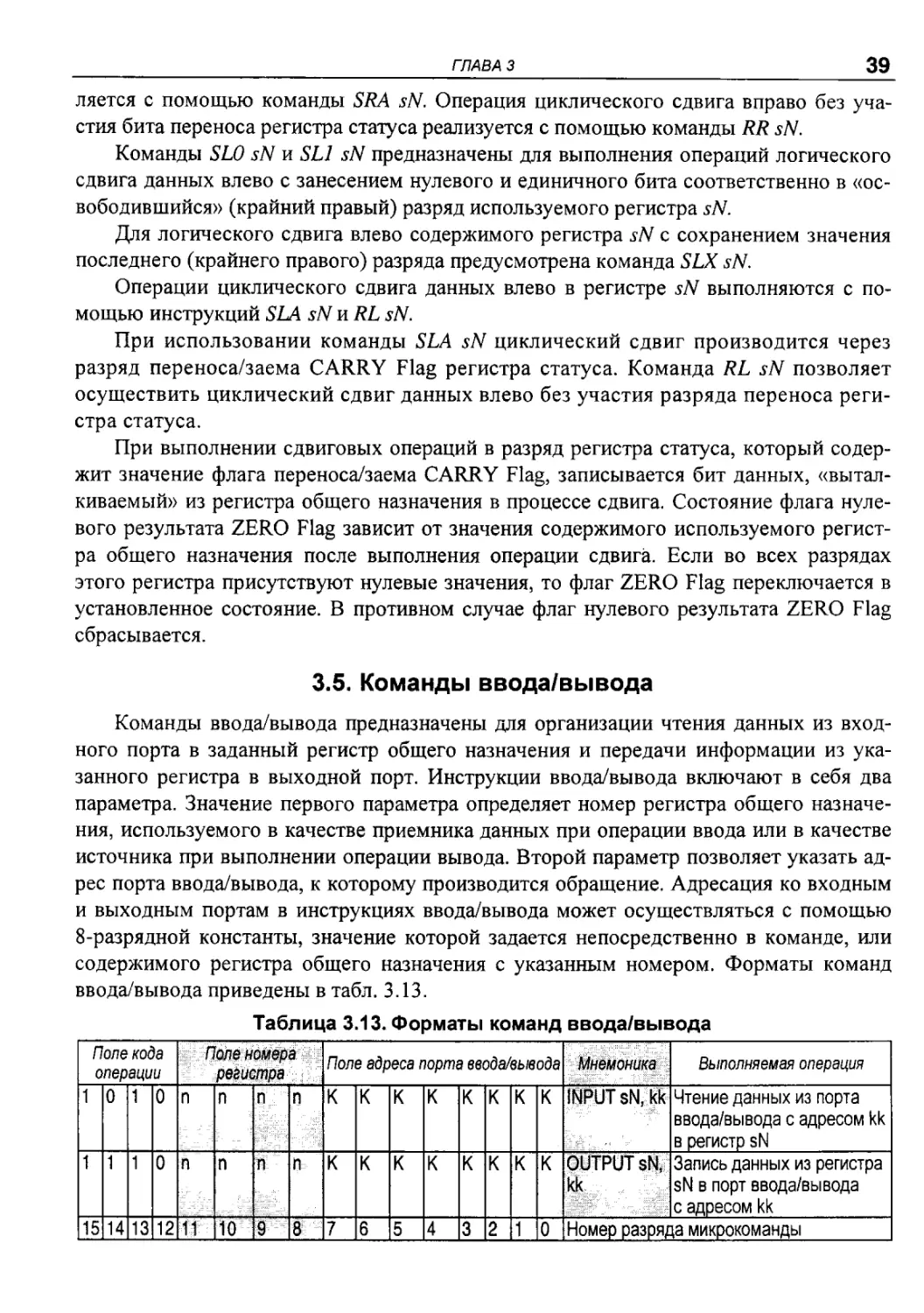

Таблица 3.1. Форматы команд переходов

Поле кода операции Поле адреса перехода Мнемоника Выполняемая операция

1 0 0 0 X X 0 1 А А А А А А А А JUMPaa Безусловный переходII

1 0 0 1 0 0 0 1 А: А А А < А А А || JUMP Z,aa Переход при условии, что флаг ’ lag 'на^рдитря^ .в уйайрв- ленном состоянии |

1 0 0 1 0 1 0 1 А А А А А А || || JUMP NZ,aa Переход при условии, что флаг. • ZERO Flag находится в сброшен- ном состоянии

1 0 0 1 1 0 0 1 А А А А А А А А JUMP C,aa Переход при услози/, что срлаг ' CARRY Flag находится в установ- ленном состоянии

1 0 0 1 1 1 0 1 А: А А< А = А f| А || JUMP NC.aa Переход при условии, что флаг CABBY. Flag находится в сброшен- ном состоянии

15 14 13 12 11 10 9 8 7 6 ii 4: || и II III Номер разряда микрокоманды

Процесс выполнения команд переходов иллюстрирует рис. 3.1. При исполнении

операции безусловной передачи управления JUMP аа в программный счетчик запи-

сывается значение адреса перехода аа. При условных переходах загрузка в про-

граммный счетчик нового адреса, указанного в команде, производится только при

выполнении соответствующего условия. Если заданное условие не выполнено, то

программный счетчик продолжает работу в инкрементном режиме, т. е. его прежнее

содержимое увеличивается на единицу. В процессе реализации команд безусловного

и условных переходов состояние флагов регистра статуса не изменяется.

ГЛАВА 3

27

Старое значение

Условие программного счетчика

не выполнено

Новое значение

программного счетчика

JUMP Z,aa

JUMP NZ,aa

JUMP C,aa

JUMP NC,aa ,

--------- Адрес перехода

|JUMPaa|

Условие выполнено

или

безусловный переход

Рис. 3.1. Выполнение команд безусловного и условных переходов

Команда JUMP Z,aa инициирует переход к выполнению инструкции, располо-

женной по указанному адресу, при условии, что флаг нулевого результата ZERO Flag

находится в состоянии логической единицы. При исполнении команды JUMP NZ,aa

управление передается инструкции с указанным адресом только в случае, если флаг

нулевого результата ZERO Flag установлен в состояние логического нуля. Команда

JUMP C,aa загружает новое значение адреса в программный счетчик при условии,

что состояние флага переноса/заема CARRY Flag соответствует значению логиче-

ской единицы. С помощью команды JUMP NC,aa осуществляется переход к выпол-

нению инструкции с указанным адресом, если флаг переноса/заема CARRY Flag на-

ходится в сброшенном состоянии (логического нуля).

Команды вызова подпрограмм CALL позволяют передать управление по адресу,

который соответствует первой инструкции вызываемой процедуры. Обращение к

подпрограмме может происходить как в безусловном порядке, так и при выполнении

заданного условия. Форматы безусловного и условных вариантов команд вызова

подпрограмм CALL приведены в табл. 3.2. Адрес вызываемой процедуры задается в

том же виде, в котором задается и адрес в командах перехода JUMP, Команды безус-

ловного и условных обращений к подпрограммам не влияют на состояние флагов ре-

гистра статуса.

Таблица 3.2. Форматы команд вызова подпрограмм

Лоле кода операции под ipo гран Мнемоника Выполняемая операция

1 0 0 0 X X 1 1 А< ж А/ is: А ЙУ At At CALL аа Безусловный вызов подпрограммы

1 0 0 1 0 0 1 1 А/ А/ II II А А‘ А CALLZ.aa Вызов подпрограммы при условии, Flag находится в ШЙШЙННЖсжоянии

1 0 0 1 0 1 1 1 1/ i й is А| А CALL NZ,aa Вызов подпрограммы при условии, что флаг ZERO Flag находится в сброшенном состоянии

1 0 0 1 1 0 1 1 А .11 А А А А А А CALLC.aa Вызов подпрограммы при условии, находится в установленном состояв и и

1 0 0 1 1 1 1 1 А| AS Й; й чи W CALL NC.aa Вызов подпрограммы при условии, :CARRY Flag находится в сброшенном состоянии

15 14 13 12 11 10 9 8 IS Й!! г 2 1 0 Номер разряда микрокоманды

28 Зотов В. Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС

На рис. 3.2 в наглядной форме отображена последовательность действий, кото-

рые производятся при различных вызовах подпрограмм. Выполнение команды без-

условного обращения к подпрограмме CALL aa начинается с записи в стек текущего

содержимого программного счетчика (т. е. адреса исполняемой инструкции вызова

процедуры). Сохраненное значение используется впоследствии при завершении под-

программы и возврате в основную программу или подпрограмму, из которых вызы-

валась текущая процедура. Затем в программный счетчик заносится значение адреса,

указанное в команде. Это значение определяет начальный адрес блока памяти,

в котором хранится вызываемая подпрограмма.

Стек

Условие

не выполнено

Старое значение

программного счетчика

CALLZ.aa

CALL NZ,aa

CALL C,aa

CALL NC,aa

Адрес подпрограммы

Условие выполнено

или

безусловный вызов

подпрограммы

Рис. 3.2. Выполнение команд безусловного и условных вызовов подпрограмм

Микропроцессорным ядром PicoBlaze поддерживается 4 варианта команд услов-

ного обращения к подпрограмме. Исполнение команды условного вызова подпро-

граммы начинается с проверки выполнения соответствующего условия. Если это ус-

ловие выполнено, то далее производится последовательность операций, рассмотрен-

ная выше для команды безусловного обращения к подпрограмме (рис. 3.2). В случае

невыполнения заданного условия содержимое программного счетчика увеличивается

на единицу, указывая тем самым адрес следующей команды основной программы.

Команда CALL Z,aa передает управление подпрограмме, расположенной по указан-

ному адресу, если флаг нулевого результата ZERO Flag установлен в состояние логи-

ческой единицы. С помощью команды CALL NZ,aa осуществляется вызов подпро-

граммы при условии, что флаг нулевого результата ZERO Flag находится в состоянии

логического нуля. Команда CALL C,aa загружает в программный счетчик указанный

адрес подпрограммы, если состояние флага переноса/заема CARRY Flag соответст-

вует значению логической единицы. При исполнении команды CALL NC,aa обраще-

ние к подпрограмме производится только при условии, что флаг переноса/заема

CARRY Flag находится в сброшенном состоянии.

Команды возврата из подпрограммы RETURN предназначены для передачи

управления основной программе или подпрограмме, из которых вызывалась текущая

процедура. Эта операция может осуществляться как в безусловной форме, так и в за-

висимости от выполнения заданного условия.

Табл. 3.3 представляет форматы безусловного и условных вариантов команд воз-

врата из подпрограммы RETURN.

ГЛАВА 3

29

Таблица 3.3. Форматы команд безусловного и условных возвратов

из подпрограммы

Поле кода операции Поле адреса Мнемоника Выполняемая операция

1 0 0 0 X X 0 0 0 0 0 0 О' 0 0 0 RETURN Безусловный возврат из подпрограммы

1 0 0 1 0 0 0 0 о 0 0 0 0 0 0 0 RETURNZ Возврат из подпрограммы при ус- ловии, что флаг ZERO Flag нахо- дится в установленном состоянии

1 0 0 1 0 1 0 0 0 0 0 0 0 0 0 0 RETURN NZ Возврат из подпрограммы при ус- ловии, что флаг ZERO Flag нахо- дится в сброшенном состоянии

1 0 0 1 1 0 0 0 0 0 0 0 0 0 0 ; 0 RETURN C Возврат из подпрограммы при ус- ловии, что флаг CARRY Flag нахо- дится в установленном состоянии

1 0 0 1 1 1 0 0 0 0 0 0 0 0 0 0 RETURN NC Возврат из подпрограммы при ус- ловии, что флаг CARRY Flag нахо- дится в сброшенном состоянии

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 Номер разряда микрокоманды

Процесс выполнения команд возврата из подпрограмм в условной и безусловной

форме показан на рис. 3.3. Безусловное завершение выполняемой подпрограммы и

передача управления основной программе или подпрограмме, из которых производи-

лось обращение к этой процедуре, осуществляется с помощью команды RETURN.

При этом из стека извлекается последнее записанное значение, увеличивается на

единицу и загружается в программный счетчик. Таким образом, в программный

счетчик заносится адрес очередной команды основной программы (или подпрограм-

мы при вложенном вызове процедуры), следующей после инструкции обращения

к подпрограмме.

Рис. 3.3. Выполнение команд безусловного и условного возвратов из подпрограммы

При реализации команды условного возврата из подпрограммы прежде всего

осуществляется контроль выполнения соответствующего условия. При получении

положительного результата проверки далее выполняется та же последовательность

действий, что и при безусловном возврате. Если условие не выполнено, то текущее

содержимое программного счетчика увеличивается на единицу. Таким образом, но-

30

Зотов В. Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС

вое значение программного счетчика в этом случае соответствует адресу следующей

команды текущей исполняемой подпрограммы.

Команда RETURN Z возвращает управление вызывающей программе или под-

программе в случае, если флаг нулевого результата ZERO Flag принимает значение

логической единицы. С помощью команды RETURN NZ осуществляется возврат из

подпрограммы при условии, что флаг нулевого результата ZERO Flag сброшен в со-

стояние логического нуля. Команда RETURN С выполняет операцию возврата из

подпрограммы, если состояние флага переноса/заема CARRY Flag соответствует зна-

чению логической единицы. При исполнении команды RETURN NC управление пе-

редается вызывающей программе или подпрограмме только при условии, что флаг

переноса/заема CARRY Flag находится в сброшенном состоянии. При выполнении

команд возврата из подпрограммы состояние флагов регистра статуса не изменяется.

3.2. Группа логических команд

В командах, входящих в эту группу, используются два параметра, которые опре-

деляют значения операндов. Первым операндом всегда является содержимое регист-

ра общего назначения, номер которого N указан в тексте инструкции. В качестве но-

мера регистра N может использоваться любое число в диапазоне от 0 до 15, которое

при мнемонической записи команд задается в шестнадцатеричном формате (0 - F).

В этот же регистр записывается результат выполненной операции. В качестве второ-

го операнда используется либо константа, значение которой указывается непосредст-

венно в коде команды, либо содержимое другого регистра общего назначения. При

мнемонической форме записи команд значение константы задается в виде двух ше-

стнадцатеричных символов.

При выполнении поразрядных логических операций флаг переноса/заема

CARRY Flag всегда сбрасывается в состояние логического нуля. Значение флага

ZERO Flag определяется полученным результатом. Если все разряды результирую-

щего слова принимают значение логического нуля, то флаг нулевого результата

ZERO Flag устанавливается в состояние, соответствующее логической единице.

В противном случае, если хотя бы в одном разряде результата присутствует единич-

ное значение, флаг нулевого результата ZERO Flag переключается в сброшенное со-

стояние.

Форматы команд поразрядных операций «Логическое И» (поразрядное умноже-

ние) AND представлены в табл. 3.4.

Таблица 3.4. Форматы команд поразрядных операций «Логическое И»

Поле кода операции Поле номера регистра Поле константы Мнемоника Выполняемая операция

0 0 0 1 П п п л К К К К К К К к AND sN, kk Поразрядное «Логическое И» содержимого регистра sN и константы kk

Поле префикса ко- да операции Поле номера первого -i регистра Поле номера второго регистра Поле кода операции Мнемоника Выполняемая операция

1 1 0 0 п п п п m m m m 0 0 0 1 AND sN.sM Поразрядное «Логическое И» содержимого регистров sN и sM

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 Номер разряда микрокоманды

ГЛАВА 3

31

Команда AND sN,kk выполняет операцию «Логическое И» над соответствующи-

ми разрядами содержимого регистра с номером N и константы кк. Для поразрядного

умножения содержимого двух регистров общего назначения с номерами N и М пред-

назначена команда AND sN,sM. Выполнение этих команд иллюстрирует рис. 3.4.

Исходное содержимое

регистра sN

Константа, указанная

в команде

Регистр sN

|AND sN,kk]

I I I I I + I I

.Ill

CARRY ГТД

Flag “i

ZERO И

Flag

Результат^

L-----------1

Результат = О

Исходное содержимое

регистра sN

Содержимое

регистра sM

Регистр sN

|AND sN,sm]

CARRY

Flag

ZERO pZTl

Flag bi

Результат^ 0^

L-----------1

Результат = 0

0

Рис. 3.4. Выполнение поразрядных операций «Логическое И»

Операции поразрядного сложения двух операндов осуществляются с помощью

инструкций OR, форматы которых определены в табл. 3.5.

Таблица 3.5. Форматы команд поразрядных операций «Логическое ИЛИ»

Поле кода операции Поле номера регистра Поле константы Мнемоника Выполняемая операция

0 0 1 0 п п - -п- п К К К К К К К К OR sN, kk Поразрядное «Логическое ИЛИ» содержимого регистра sN и константы kk

Поле префик- са кода операции Поле номера первого регистра Поле номера второго регистра Поле кода операции Мнемоника Выполняемая операция

1 1 0 0 п п п п m m m m 0 0 1 0 ORsN.sM Поразрядное «Логическое ИЛИ» содержимого регистров sN nsM

15 14 13 12 11 10 9 ву 7 6 5 4 3 2 1 0 Номер разряда микрокоманды

Команда OR sN,kk выполняет поразрядную операцию «Логическое ИЛИ» содер-

жимого регистра с номером N и константы кк. Поразрядное сложение содержимого

двух регистров общего назначения с номерами N и М реализует команда OR sN,sM.

Последовательность выполнения операций «Логическое ИЛИ» показана на рис. 3.5

32 Зотов В. Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС

Исходное содержимое

регистра sN

Константа, указанная

в команде

Регистр sN

|OR sN,kk|

|к|к|к|к|к|к|к|к|

4 + I + 4 i 4 +

Г"1 Tl. rt г~п

CARRY Щ

Flag 1И

ZERO

Flag В™

Результат И О

u-----------1

Результат » О

Исходное содержимое

регистра sN

Содержимое

регистра sM

Регистр sN

CARRY

Flag

Результат # О

U-----------1

Результат О

Рис. 3.5. Выполнение поразрядных операций «Логическое ИЛИ»