Author: Басманов А.С. Широков Ю.Ф.

Tags: компьютерные технологии вычислительная техника микропроцессоры электротехника эвм микро эвм микропроцессорные средства и системы

ISBN: 5-283-01485-1

Year: 1988

МИКРОПРОЦЕССОРНЫЕ

БИС

И ИХ ПРИМЕНЕНИЕ

А.С. БАСМАНОВ

Ю.Ф. ШИРОКОВ

Микропроцессоры

и однокристальные

микроЭВМ:

Номенклатура

и функциональные

возможности

ЭНЕРГО АТОМ ИЗД АТ

„МИКРОПРОЦЕССОРНЫЕ

БИС

И ИХ ПРИМЕНЕНИЕ”

А.С. БАСМАНОВ

Ю.Ф. ШИРОКОВ

М и препроцессоры

и однокристальные

микроЭВМ:

Номенклатура

и функциональные

возможности

Под редакцией доктора

технических наук В.Г. ДОМРАЧЕВА

МОСКВА ЭНЕРГАТОМИЗДАТ 1988

ББК 32.97

Б 27 AlVaKo 28/04/2011

УДК 681.322-181.48

Серия основа в 1988 году

Рецензент О. П. Глудкин

Басманов А. С., Широков Ю. Ф

Б 27 Микропроцессоры и однокристальные микроЭВМ: Номенк-

латура и функциональные возможности / Под ред. В.Г. Домра-

чева - М.: Энергоатомиздат, 1988. — 128 с: ил. — (Микропро-

цессорные БИС и их применение)

ISBN-5-283-01485-1

Приведены номенклатура, сравнительные характеристики, струк-

тура и функциональные возможности микропроцессоров и однокрис-

тальных микроЭВМ широкого применения: К1801/09, К1810,К1813,

К1815, К1816, К1820, К1821. Приведены примеры программирования

однокристальных микроЭВМ.

Для инженеров, занимающихся разработкой и применением микро-

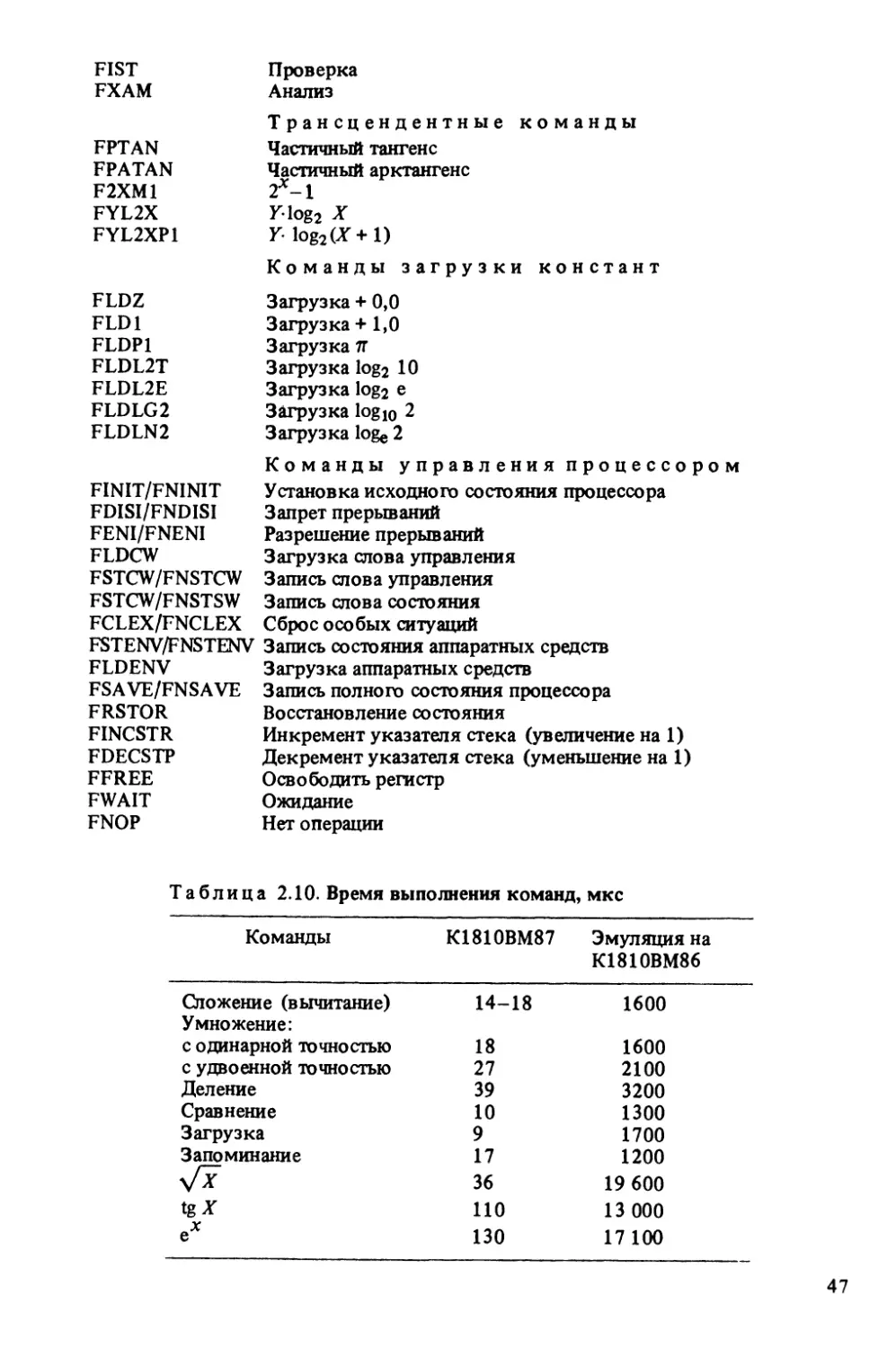

процессорной техники.

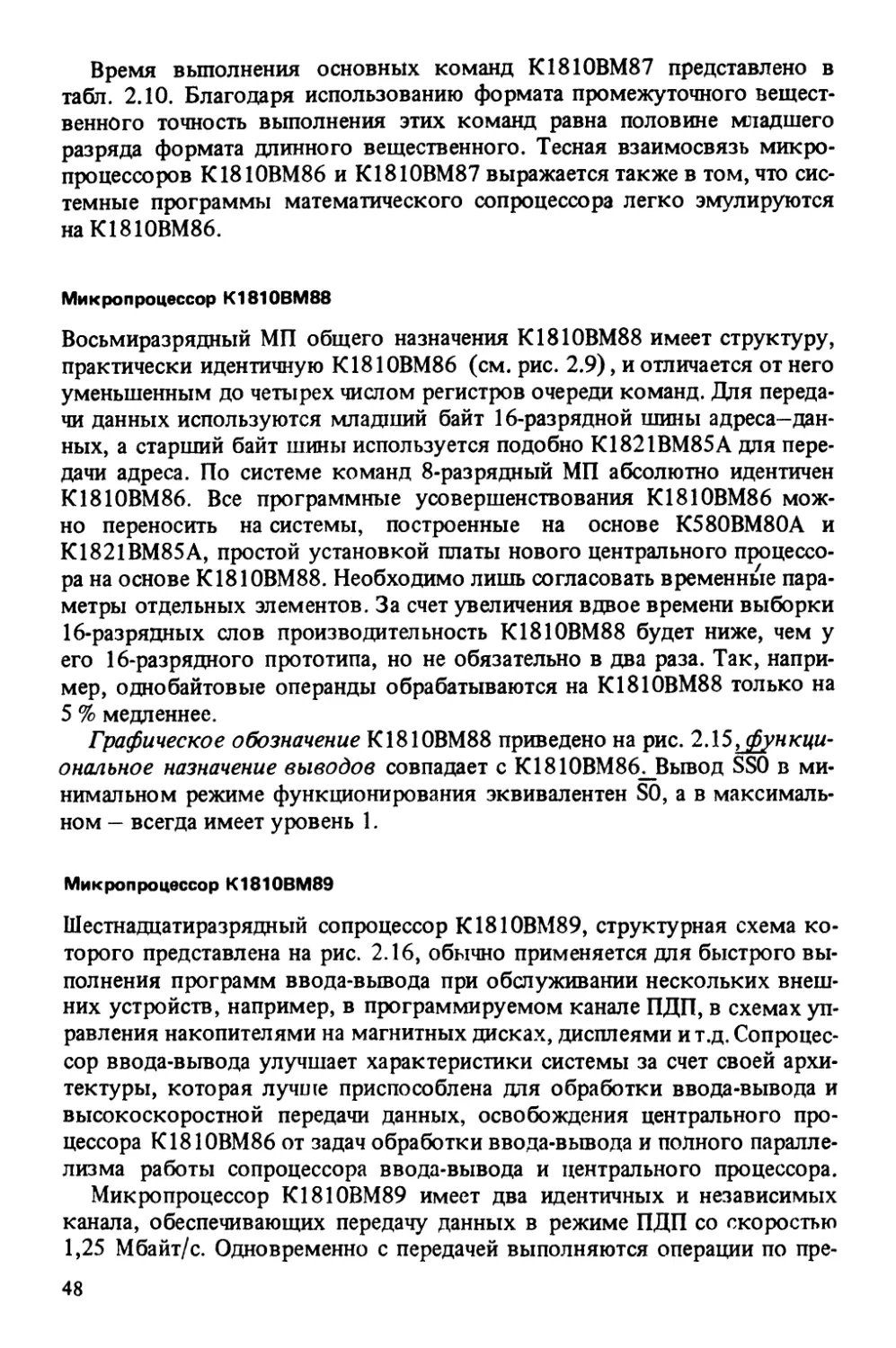

Б2405000000-439 кб.34.39.87

051(00-88

ББК 32.97

ISBN5-283-01485-1

© Энергоатомиздат, 1988

ПРЕДИСЛОВИЕ

Эффективная автоматизация машин, приборов и технологического обо-

рудования, которая является обязательным условием ускорения науч-

но-технического прогресса, основана на широком применении средств

микропроцессорной техники. Автоматизация с использованием микро-

процессоров быстро распространяется в самых разнообразных отрас-

лях народного хозяйства, охватывает новые сферы.

Характерно, что создание микропроцессорных систем управления

все в большей степени становится функцией специалистов в конкретной

предметной области, а не профессиональных программистов и специа-

листов по электронике. Это вызывает во всех отраслях быстрый коли-

чественный рост инженерных кадров, имеющих непосредственное отно-

шение к применению и эксплуатации микропроцессорной техники. С

другой стороны, электронная промышленность осваивает в производст-

ве все новые микропроцессорные БИС с целью улучшения технико-эко-

номических характеристик систем управления и расширения сфер их

применения. Эти два фактора обусловливают актуальность книг, несу-

щих новую информацию по микропроцессорам.

Предлагаемая книга позволяет широкому кругу специалистов, в том

числе начинающих свою деятельность в области применения микропро-

цессоров, получить общую ориентацию в существующей номенклатуре

микропроцессорных БИС и выбрать из нее те изделия, которые обеспе-

чили бы наиболее рациональное решение поставленой задачи.

Достоинством книги является то, что здесь впервые представлена

обобщенная информация по наиболее перспективным в настоящее время

отечественным 8- и 16-разрядным микропроцессорам и 4- и 8-разрядным

однокристальным микроЭВМ; уделено внимание однокристальным мик-

роЭВМ как наиболее массовым микропроцессорным БИС, обеспечиваю-

щим значительные технико-экономические преимущества в большинстве

потенциальных областей применения, а также специализированным мик-

ропроцессорам и однокристальным микроЭВМ для цифровой обработки

аналоговых сигналов, привлекающим в последние годы все большее вни-

мание специалистов.

В обобщенном виде в книге даны сведения о номенклатуре и характе-

ристиках отечественных микропроцессорных БИС. При этом выделены

наиболее перспективные микропроцессоры и однокристальные микро-

ЭВМ широкого применения, а по узкоспециализированным и устарев-

3

шим БИС приведена лишь краткая информация либо о них вообще не

упоминается.

В книге подробно рассмотрены состав перспективных серий микро-

процессорных комплектов и однокристальных микроЭВМ, структура и

функциональные возможности входящих в них БИС, даны примеры про-

граммирования однокристальных микроЭВМ, что будет во многом спо-

собствовать правильному выбору номенклатуры этих изделий в процес-

се проектирования аппаратуры.

Книга рассчитана на инженерно-технических работников различных

отраслей народного хозяйства, занимающихся разработкой и применени-

ем микропроцессорных устройств и систем.

В. Г. Домрачев

ВВЕДЕНИЕ

Общепризнано, что электроника является катализатором научно-техни-

ческого прогресса во всех областях народного хозяйства, основой авто-

матизации машин, приборов, оборудования, технологических процессов

Однако широкомасштабное ее использование во всех сферах человече-

ской деятельности предполагает наличие объективных условий, главное

из которых - общедоступность электронных изделий различного назна-

чения. Это значит, что электроника должна быть дешевой в широком по-

нимании - с учетом затрат материальных и трудовых ресурсов на ее про-

ектирование, производство и эксплуатацию.

Развитие микроэлектронной технологии, обеспечившее появление

больших (БИС) и сверхбольших интегральных схем (СБИС), создало

предпосылки для резкого снижения стоимости систем управления. Но

практическая реализация достижений технологии БИС и СБИС в широ-

ких масштабах стала возможной только с изобретением микропроцессора

(МП) — универсального компонента, который стал связующим звеном

для нового поколения изделий микроэлектроники (БИС и СБИС) и обес-

печил его функциональную полноту. Выдающееся значение микропроцес-

сора заключается не столько в его собственной универсальности, сколь-

ко в том, что он придает свойство универсальности всей совокупно-

сти современного поколения БИС и СБИС, обеспечивающих низкую

стоимость систем управления. Благодаря этому МП стал провод-

ником электроники во все сферы народного хозяйства. В этом отноше-

нии ни одно другое изделие не может конкурировать с МП ни сейчас, ни

в ближайшей перспективе.

Установилась четкая тенденция обеспечения совместимости основных

классов электронных компонентов с микропроцессорами — не только

микроэлектронных, но и дискретных, в том числе пассивных компонен-

тов. Совместимость обеспечивается в самых различных аспектах - элек-

трическая, энергетическая, архитектурная, программная, конструктив-

ная, экономическая. Эта тенденция также направлена на снижение стоимо-

сти микропроцессорных систем управления, обеспечение их компактности

и высокой надежности и лишний раз подтверждает центральное место МП

в системе электронных компонентов и дальнейшее укрепление его веду-

щей роли.

Сегодня универсальный МП может использоваться как стандартный

элемент не только на печатной плате, но и в составе все более сложных

5

полупроводниковых кристаллов. Ранее созданные и завоевавшие попу-

лярность у потребителей МП используются как стандартные элементы

при проектировании БИС и СБИС, занимая в них обычно центральное

место. Таким образом, прогресс технологии, позволяющий создавать на

кристалле более сложные изделия, чем универсальный МП, не снижает

роль последнего как центрального звена электронных компонентов, так

как другие ’’претенденты” на эту роль пока неизвестны. Одним из таких

компонентов, завоевавших огромную популярность, стали однокристаль-

ные микроЭВМ (ОЭВМ), объединяющие на одном полупроводниковом

кристалле как сам микропроцессор, так и целый ряд дополнительных

устройств, обеспечивающих его функционирование в системе управле-

ния: оперативную и программную память, генератор синхроимпульсов,

разнообразные устройства ввода-вывода информации и др. Благодаря

низкой стоимости систем управления, основанных на ОЭВМ (в простей-

ших случаях для создания системы достаточно одной БИС), более двух

третей мирового рынка МП составили ОЭВхМ.

Масштабы применения МП (а следовательно, и электроники в целом)

в народном хозяйстве в решающей мере определяются степенью разви-

тия номенклатуры микропроцессорных и процессорно-ориентированных

БИС. В настоящее время это развитие достигло такого уровня, что сфе-

ры применения МП можно считать практически неограниченными, по-

скольку в любой из них могут быть реализованы потенциальные возмож-

ности микропроцессорных систем управления. Это относится как к

простейшим объектам управления - датчикам, исполнительным устрой-

ствам, регистраторам информации, так и к самым сложным станкам или

приборам.

Прямым следствием универсальности МП-систем является замеча-

тельное их свойство — высокая гибкость, возможность быстрой перена-

стройки при необходимости даже значительных изменений алгоритмов

управления. Как правило, перенастройка осуществляется программным

путем без существенных производственных затрат. Более того, МП позво-

ляют легко реализовать принципы открытых систем, функциональные

возможности которых могут наращиваться по мере необходимости или

по мере появления новых технических средств. Тем самым обеспечива-

ется соответствие технического уровня микропроцессорных систем уп-

равления самым современным требованиям в течение длительного

времени.

Универсальность МП-систем обеспечивает их доступность широкому

кругу потребителей. Наряду с потенциально низкой стоимостью это опре-

деляется и возможностью централизации производства универсальных

МП-систем, специализация которых под конкретные задачи (т.е. програм-

мирование) осуществляется самим потребителем. Следовательно, органи-

зация электронного приборостроения в каждой отрасли народного хо-

зяйства не является необходимым условием для широкого примене-

ния МП.

6

Микропроцессорная техника существенно влияет на техническое пе-

ревооружение народного хозяйства и в первую очередь машинострои-

тельных и приборостроительных отраслей. Ни одна перспективная систе-

ма управления, какой бы уровень сложности она ни имела, не может

обойтись без МП или ОЭВМ. Развитие техники управления производст-

вом характеризуется в настоящее время широким применением нового

поколения средств управления на основе МП и ОЭВМ. Техническая база

большинства отраслей достигла такого уровня, на котором эффектив-

ность производственного процесса зависит, прежде всего, от качества уп-

равления технологией и производством в целом.

Следовательно, решение задачи оптимального управления промышлен-

ными объектами (технологическим оборудованием, устройствами и про-

цессами, а также параметрами и данными, характеризующими их) имеет

первостепенное значение. Успешно решить ее можно лишь на основе ши-

рокого внедрения в различные отрасли промышленности микропроцес-

сорных контроллеров и систем управления. Управление технологическим

оборудованием, устройствами и процессами относится к нижнему уров-

ню управления производством. Наибольший выигрыш от применения

МП и ОЭВМ достигается именно на этом уровне, от эффективности его

работы прежде всего зависит производительность труда и качество про-

дукции.

Процесс применения МП и ОЭВМ развивается очень стремительно, так

как практически нет ограничений на области применения контроллеров и

систем, построенных на их основе. Вопросы применения МП и ОЭВМ

обычно рассматриваются в литературе применительно к различным отрас-

лям (энергетике, химии, металлургии, машиностроению и др.) и подот-

раслям промышленности, направлениям развития техники и технологии

и т.д. Естественно, провести классификацию этих многочисленных об-

ластей применения не представляется возможным, да и не имеет смысла.

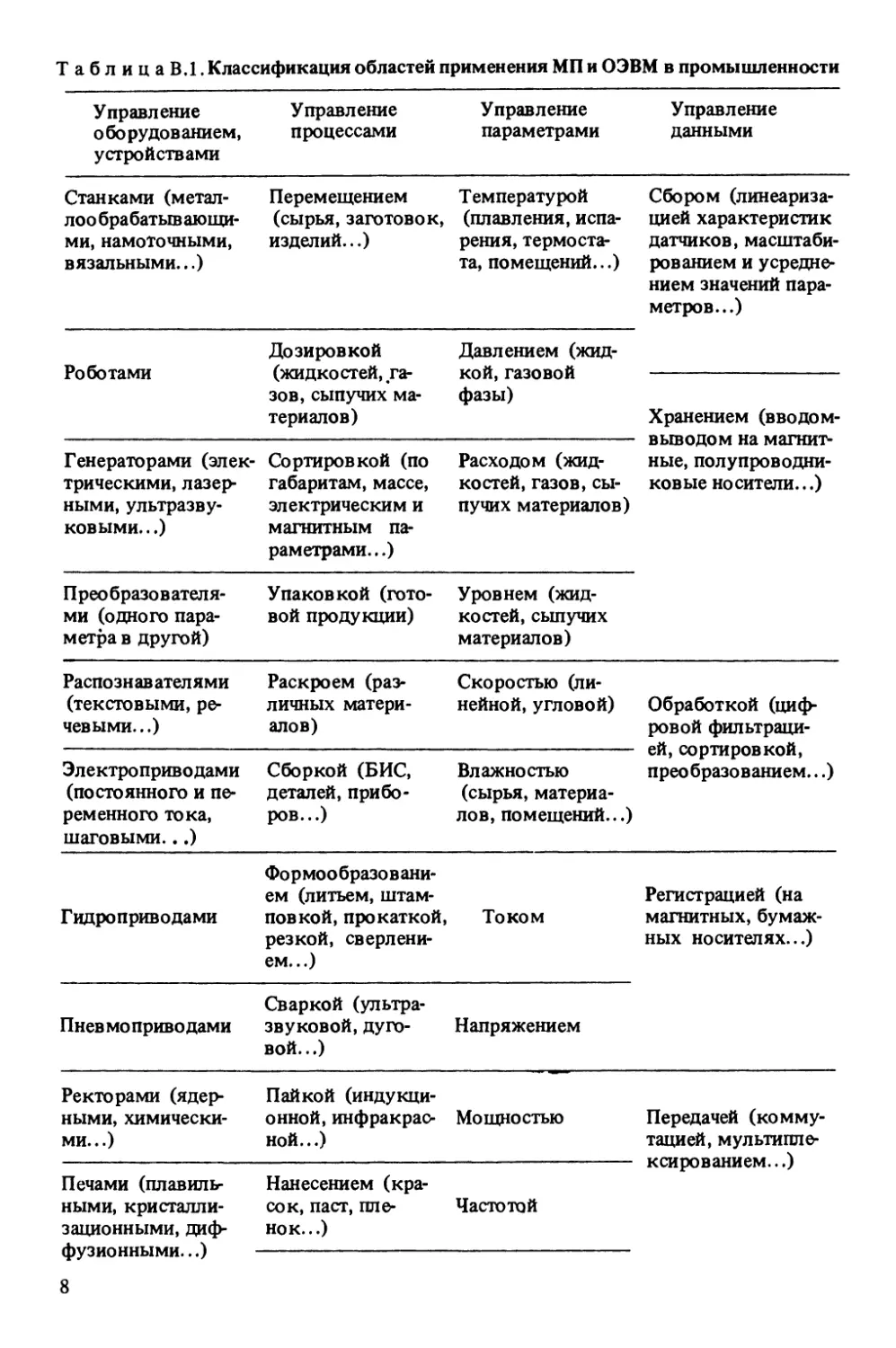

Области применения МП и ОЭВМ целесообразнее классифицировать по

функциональному признаку (табл. В1), т.е. по составу функций, выпол-

няемых МП и ОЭВМ по управлению технологическими процессами, обо-

рудованием, устройствами а также параметрами и данными, характери-

зующими их (вне зависимости от отраслей промышленности).

Принятие такого подхода (а также дальнейшее его развитие и конкре-

тизация) может явиться одним из путей повышения эффективности при-

менения МП и ОЭВМ и привести к определенной унификации аппаратур-

ных и программных средств МП-контроллеров и систем управления од-

нотипными технологическими процессами и оборудованием в различных

отраслях промышленности.

Необходимо отметить, что преимущества МП-контроллеров и систем

не обеспечиваются сами собой, автоматически, а являются результатом

глубокого анализа, грамотной постановки и решения задачи на основе

разумных компромиссов, оптимального выбора типа МП или ОЭВМ и

элементной базы в целом [1 ]. Обязательным условием эффективного при-

7

ТаблицаВ.1. Классификация областей применения МП и ОЭВМ в промышленности

Управление оборудованием, устройствами Управление процессами Управление параметрами Управление данными

Станками (метал- лов брабатываю щи- ми, намоточными, вязальными...) Перемещением (сырья, заготовок, изделий...) Температурой (плавления, испа- рения, термоста- та, помещений...) Сбором (линеариза- цией характеристик датчиков, масштаби- рованием и усредне- нием значений пара- метров...)

Роботами Дозировкой (жидкостей, га- зов, сыпучих ма- териалов) Давлением (жид- кой, газовой фазы)

Хранением (вводом- выводом на магнит- ные, полупроводни- ковые носители...)

Генераторами (элек- трическими, лазер- ными, ультразву- ковыми...) Сортировкой (по габаритам, массе, электрическим и магнитным па- раметрами...) Расходом (жид- костей, газов, сы- пучих материалов)

Преобразователя- ми (одного пара- метра в другой) Упаковкой (гото- вой продукции) Уровнем (жид- костей, сыпучих материалов)

Распознавателями (текстовыми, ре- чевыми...) Раскроем (раз- личных матери- алов) Скоростью (ли- нейной, угловой) Обработкой (циф- ровой фильтраци- ей, сортировкой, преобразованием...)

Электроприводами (постоянного и пе- ременного тока, шаговыми...) Сборкой (БИС, деталей, прибо- ров...) Влажностью (сырья, материа- лов, помещений...)

Гидроприводами Формообразовани- ем (литьем, штам- повкой, прокаткой, резкой, сверлени- ем...) Током Регистрацией (на магнитных, бумаж- ных носителях...)

Пневмоприводами Сваркой (ультра- звуковой, дуго- вой...) Напряжением

Ректорами (ядер- ными, химически- ми...) Пайкой (индукци- онной, инфракрас- ной...) Мощностью Передачей (комму- тацией, мультипле- ксированием...)

Печами (плавиль- ными, кристалли- зационными, диф- фузионными...) Нанесением (кра- сок, паст, пле- нок...) Частотой

8

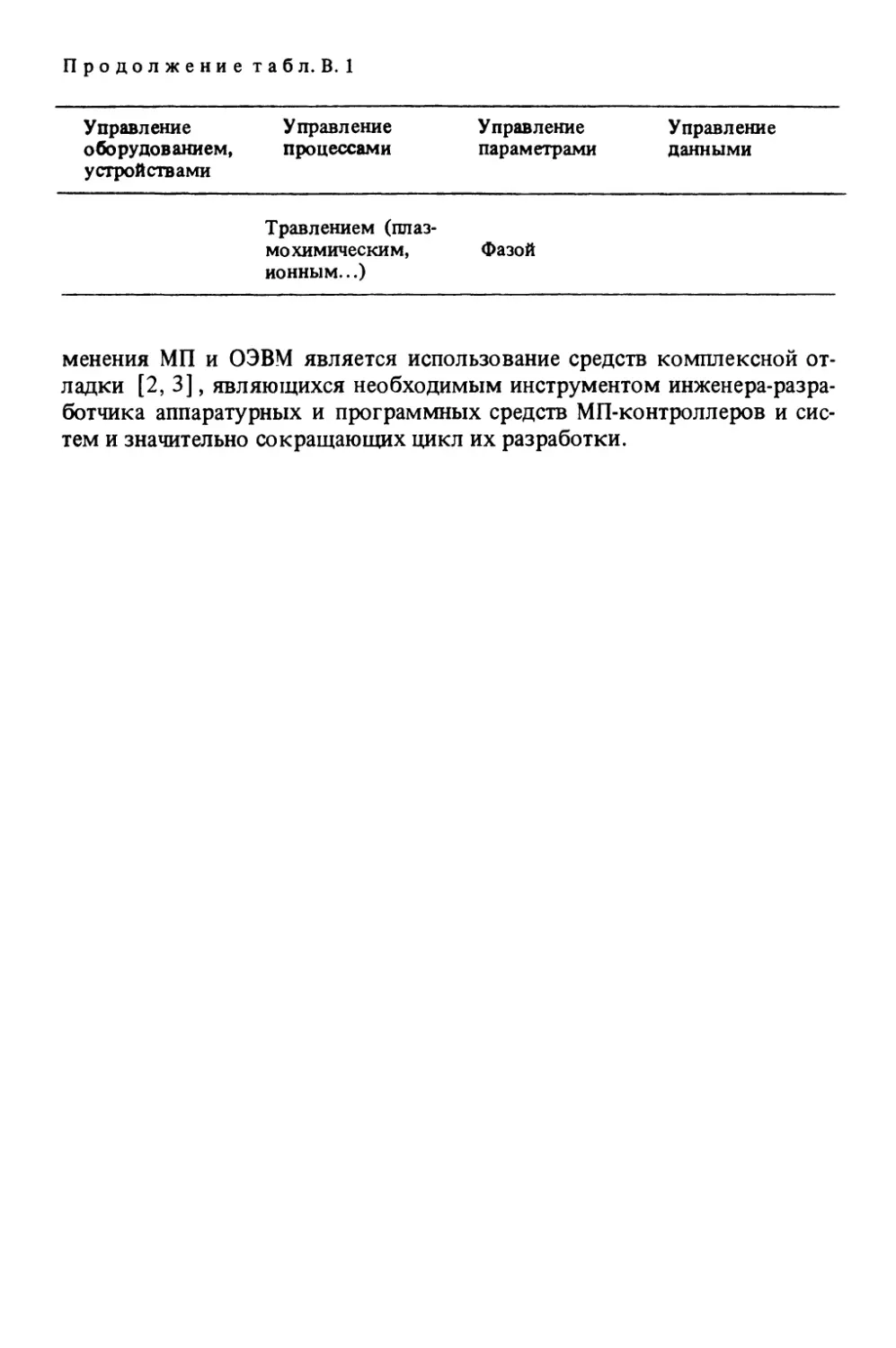

Продолжение табл. В. 1

Управление Управление Управление Управление

оборудованием, устройствами процессами параметрами данными

Травлением (плаз-

мохимическим, Фазой

ионным...)

менения МП и ОЭВМ является использование средств комплексной от-

ладки [2, 3], являющихся необходимым инструментом инженера-разра-

ботчика аппаратурных и программных средств МП-контроллеров и сис-

тем и значительно сокращающих цикл их разработки.

ГЛАВА 1

НОМЕНКЛАТУРА И СРАВНИТЕЛЬНЫЕ ХАРАКТЕРИСТИКИ

ОТЕЧЕСТВЕННЫХ МИКРОПРОЦЕССОРОВ И ОДНОКРИСТАЛЬНЫХ

МИКРОЭВМ

Развитие отечественной номенклатуры БИС характеризуется наличием

трех классов микропроцессорных БИС, отличающихся по структуре, тех-

ническим характеристикам и функциональным возможностям: секцио-

нированных МП с наращиванием разрядности и микропрограммным уп-

равлением, однокристальных МП и однокристальных микроЭВМ с фик-

сированной разрядностью и системой команд. Вместе с периферийными

БИС, выполняющими функции хранения и ввода-вывода данных, управ-

ления и синхронизации, сопряжения интерфейсов и т.д., микропроцессо-

ры составляют функционально законченные комплекты БИС. Секциони-

рованные МП-комплекты (МПК) обладают возможностью наращивания

параметров (прежде всего разрядности обрабатываемых данных) и функ-

циональных возможностей. Структура и система команд проектиру-

емых на их основе устройств и систем определяются разработчиком в со-

ответствии с конкретным назначением. Секционированные МПК ориен-

тированы в основном на применение в универсальных и специализиро-

ванных ЭВМ, контроллерах и других средствах вычислительной техники

высокой производительности. Микропроцессорные комплекты на основе

однокристальных МП и однокристальные микроЭВМ, обладающие мень-

шей производительностью, но гибкой системой команд и большими функ-

циональными возможностями, ориентированы на широкое применение

в различных отраслях народного хозяйства.

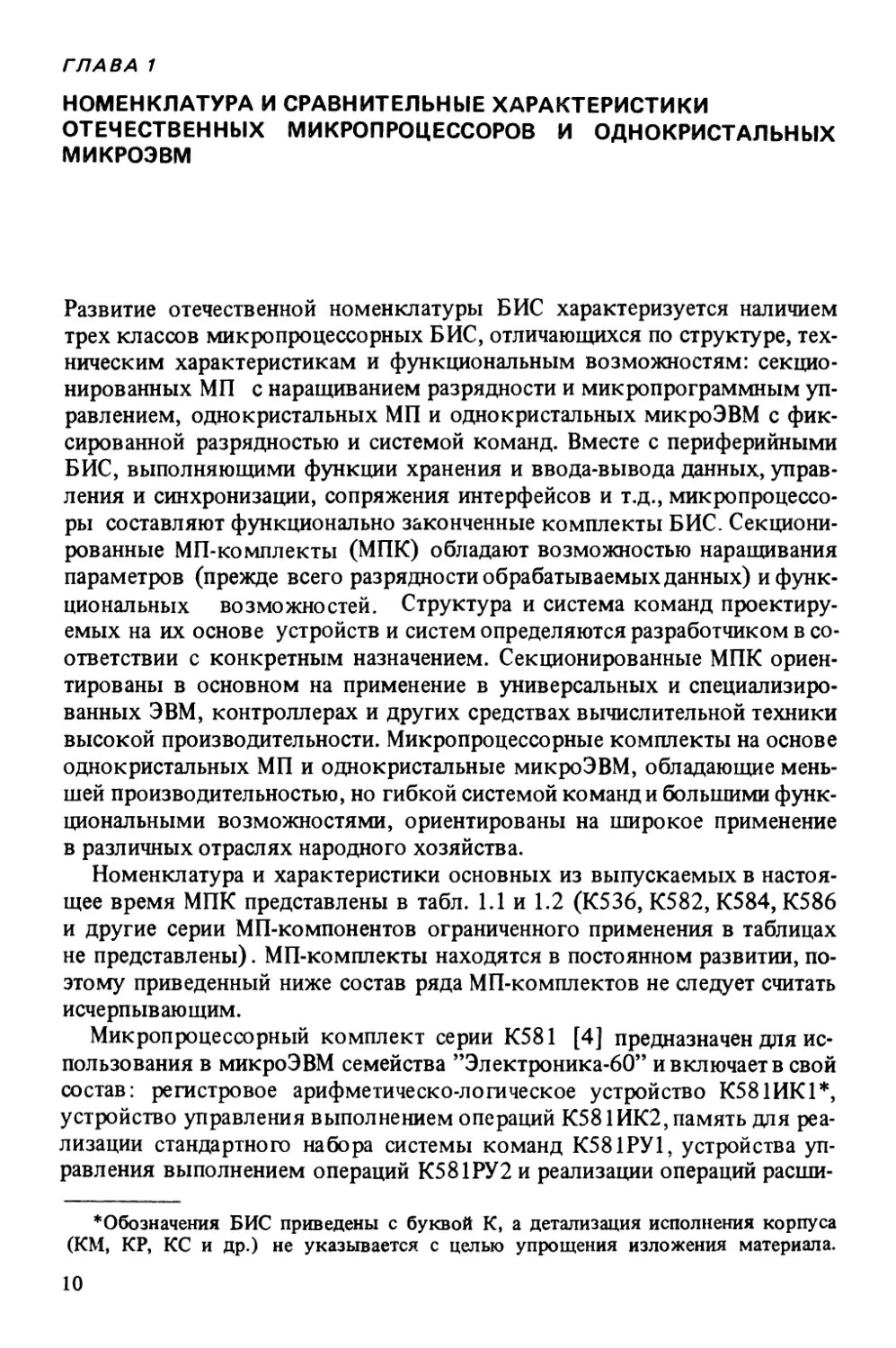

Номенклатура и характеристики основных из выпускаемых в настоя-

щее время МПК представлены в табл. 1.1 и 1.2 (К536, К582, К584, К586

и другие серии МП-компонентов ограниченного применения в таблицах

не представлены). МП-комплекты находятся в постоянном развитии, по-

этому приведенный ниже состав ряда МП-комплектов не следует считать

исчерпывающим.

Микропроцессорный комплект серии К581 [4] предназначен для ис-

пользования в микроЭВМ семейства ”Электроника-60” и включает в свой

состав: регистровое арифметическо-логическое устройство К581ИК1*,

устройство управления выполнением операций К581ИК2, память для реа-

лизации стандартного набора системы команд К581РУ1, устройства уп-

равления выполнением операций К581РУ2 и реализации операций расши-

*Обозначения БИС приведены с буквой К, а детализация исполнения корпуса

(КМ, КР, КС и др.) не указывается с целью упрощения изложения материала.

10

Таблица!.1. Сравнительные характеристики отечественных МПК

с системой команд пользователя

Обоз- наче- ние се- рии Число БИС в МПК Обозна- чение МП Раз- ряд- ность, бит Время цикла, мкс Число микро- команд Число РОН Техно- логия Потреб- ляемая мощ- ность, Вт Напряже- ние пита- ния, В

о ВЕ1 16 0,4 84 26 и-МОП 0,5 ±5; ±12

К5о1 О ИК1 8,16 0,4 84 8 и-МОП 0,5 - 5; + 12

ВС1 8п 0,3 112 16 И2Л 0,2 + 5

К583 14 ВС4 8п 0,22 112 16 И2Л 0,2 + 5

К587 4 ИК2 4п 2,0 168 8 КМОП 0,01 + 9

К588 9 ВС2 16п 2,0 420 16 КМОП 0,005 + 5

К589 10 ИКО2 2п 0,1 40 11 ттлш 0,95 + 5

К1800 11 ВС1 4п 0,1 70 32x9 эсл 1,65 - 2; - 5,2

К1802 15 ВС1 8п 0,15 256 16x4 ттлш 1,2 + 5

ту 1 ОЛЛ 1 а ВС1 4п 0,12 512 16 ттлш 1,5 + 5

К1804 1У ВС2 4п 0,12 512 16 ттлш 1,75 + 5

К1811 5 ВМ1 8п 0,3 74 8 л-МОП 0,5 + 5; +12

ренной арифметики и операций с плавающей запятой К581РУЗ, динами-

ческое ОЗУ К581РУ4, универсальный асинхронный приемопередатчик

К581ВА1, однокристальный МП К581ВЕ1. В функциональном отноше-

нии К581ВЕ1 представляет собой микропроцессор, объединяющий функ-

ции четырех БИС: К581ИК1, К581ИК2, К581РУ1 и К581РУ2. МП-комп-

лект может быть использован при разработке специализированных вы-

числительных устройств.

МПК серии К583 [5] предназначен для построения магистрально-мо-

дульных систем обработки данных с возможностью широкого распарал-

леливания процессов. В состав МПК входят следующие БИС: микропро-

цессорные секции К583ВС1 и К583ВС4, инкрементный МП К583ИК1,

коммутационный МП К583КП1, логический МП К583ВМ1, адресный

МП K583BC3, контроллер-синхронизатор К583ВГ1, умножитель

К583ВС2, магистральные приемопередатчики К583ВА1 (с памятью) и

К583ВА2, универсальные магистральные коммутаторы K583BA3 и

К583ВА4, ассоциативная память К583РА1, ПЛМ К583РЕ1, контроллер

предварительной обработки информации К583ВГ2.

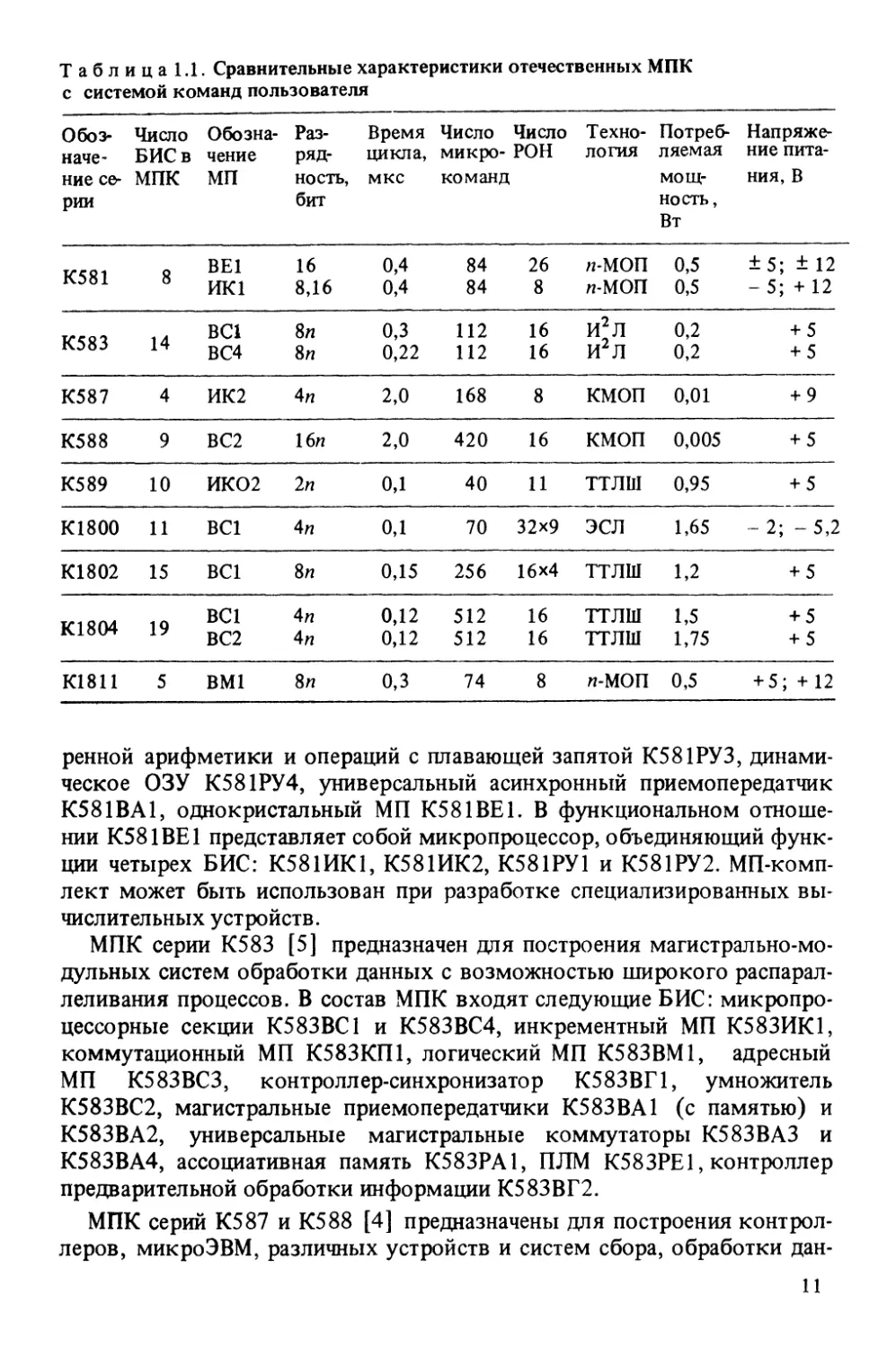

МПК серий К587 и К588 [4] предназначены для построения контрол-

леров, микроЭВМ, различных устройств и систем сбора, обработки дан-

11

Таблица 1.2. Сравнительные характеристики отечественных МПК с фиксирован-

Обозначе- ние серии Число БИС в МПК Обозначение МП Разрядность, бит Быстродейст- вие, операций/i (мкс) Число г команд

К580 19 ВМ80А 8 (2,0) 78

ВМ1 16 5 10s 66

К1801/09 14 ВМ2 16 1 • 106 74

ВМЗ 16 2 -106 74

К1806 3 ВМ2 16 5 - 10s 77

К1808 9 ВМ1 8 ?т.и. ”20 - -

100 кГц

ВМ86 16 (0,4) 135

К1810 12 ВМ87 ВМ88 16 8 (0,5) (0,45) 68 135

ВМ89 16; 16 (2,4) 46

К1821 3 ВМ85А 8 (0,8) 80

ных и управления объектами в тех областях применения, где требуется

малое потребление энергии и высокая помехоустойчивость. МП-комп-

лект серии К587 состоит из арифметического устройства К587ИК2,

арифметического расширителя К587ИКЗ, устройства обмена информаци-

ей К587ИК1 и управляющей памяти К587РП1.

МПК серии К588 включает в свой состав: арифметические устройства

К588ВС1 и К588ВС2, устройство микропрограммного управления

К588ВУ1, управляющую память К588ВУ2, арифметический расширитель

К588ВР1, арифметический умножитель К588ВР2, магистральный приемо-

передатчик К588ВА1, приемопередатчик трансформаторной линии

К588ВА2, усилитель-ограничитель сигналов К588ВАЗ, системный конт-

роллер К588ВГ1, контроллер памяти К588ВГ2, кодек мультиплексного

канала К588ВГЗ, контроллер АЦП К588ВГ4, контроллер ЦАП К588ВГ5,

адаптер мультиплексного канала К588ВГ6, двухканальный таймер

К588ВИ1, контроллер прерываний К588ВН1, многофункциональный бу-

ферный регистр К588ИР1, селектор адреса К588ВТ1, контроллер прямо-

го доступа к памяти К588ВТ2, ПЗУ с унифицированным интерфейсом

К588РЕ1.

МПК серии К589 [3, 6] предназначен для построения быстродействую-

щих вычислительных устройств, контроллеров, микроЭВМ. В состав

К589 входят следующие БИС: центральный процессорный элемент

К589ИК02, устройство микропрограммного управления К589ИК01, уст-

ройство ускоренного переноса К589ИК03, устройство приоритетного

прерывания К589ИК14, многофункциональный буферный регистр

12

ной системой команд

Емкость адресуемой памяти. Кбайт Число РОН Число уровней пре- рывания Техноло- гия Потребля- емая мощ- ность, Вт Напряжение питания, В

64 6 1 л-МОП 1,25 ±5; + 12

64 8 4 л-МОП 1,0 + 5

64 8 2 л-МОП 1.75 + 5

4Ю3 8 4 л-МОП 2,0 + 5

64 8 2 КМОП 0,025 + 5

- - - и2 л 0,1 + 5

1 • 103 8 2 л-МОП 1,75 + 5

1-Ю3 8 л-МОП 2,5 + 5

1Ю 8 2 л-МОП 1,75 + 5

1.103 4 л-МОП 1,75 + 5

64 6 2 КМОП 0,2 + 5

К589ИР12, многофункциональное синхронизирующее устройство

К589ХЛ4, шинные формирователи К589АП16 и К589АП26 (инвертирую-

щий) , ассоциативная память К589РА04, ОЗУ К589РУ01.

МПК серии К1800 [7] предназначен для построения высокопроизво-

дительных ЭВМ, процессоров, контроллеров и систем. Этот МП-комп-

лект включает в свой состав: арифметическо-логическое устройство

К1800ВС1, устройство микропрограммного управления К1800ВУ1, уст-

ройство синхронизации К1800ВБ2, контроллер памяти К1800ВТЗ, двух-

адресную буферную память К1800РП6 и К1800РП16, устройство обнару-

жения и исправления ошибок К1800ВЖ5, умножитель К1800ВР1,

программируемый сдвигатель К1800ВР8, двунаправленный пре-

образователь уровней К1800ВА4, двунаправленный приемопередатчик

К1800ВА7.

МПК серий К1802 [6] предназначен для построения широкого класса

микро- и миниЭВМ, работающих в составе различных систем, и других

устройств. В состав К1802 входят следующие БИС: микропроцессорная

секция К1802ВС1, арифметический расширитель К1802ВР1, последова-

тельный умножитель К1802ВР2, параллельные умножители К1802ВРЗ,

К1802ВР4 и К1802ВР5, сумматор К1802ИМ1, регистр общего назначения

К1802ИР1, устройство обмена информацией К1802ВВ1, интерфейс

К1802ВВ2, программируемый адаптер последовательного интерфейса

К1802ВВЗ, многофункциональный коммутатор магистралей К1802КП1,

многофункциональная матрица ассоциативных регистров К1802ИП1.

13

МПК серии К1804 [8] предназначен для построения контроллеров,

высокопроизводительных ЭВМ и других средств вычислительной техни-

ки и включает в свой состав: микропроцессорные секции К1804ВС 1 и

К1804ВС2, устройства управления адресом микрокоманды К1804ВУ1 и

К1804ВУ2, устройство управления следующим адресом К1804ВУЗ, уст-

ройство управления последовательностью микрокоманд К1804ВУ4, уст-

ройство управления адресом программной памяти К1804ВУ5, устройст-

во ускоренного переноса К1804ВР1, устройство управления состоянием

и сдвигами К1804ВР2, расширитель приоритетного прерывания

К1804ВРЗ, устройство векторного приоритетного прерывания К1804ВН1,

параллельные регистры К1804ИР1, К1804ИР2 и К1804ИРЗ, системный

тактовый генератор К1804ГГ1, магистральные приемопередатчики

К1804ВА1, К1804ВА2 (с инверсией) и KI804ВАЗ (с интерфейсной логи-

кой), устройство обнаружения и коррекции ошибок К1804ВЖ1.

МПК серии К1811 предназначен для построения микроЭВМ семейства

”Электроника-60” и включает в свой состав: арифметическо-логическое

устройство К181 IBM 1, управляющую микропрограммную память для

реализации базового набора системы команд К1811ВУ1, системы команд

с расширенной арифметикой К1811ВУЗ и плавающей запятой К1811ВУ2,

диспетчер памяти К1811 ВТ 1.

Из МПК с фиксированной разрядностью и системой команд наиболь-

шее применение в различных отраслях народного хозяйства получила

серия К580 [9, 10], которая имеет в своем составе: микропроцессор

К580ВМ80А, параллельный интерфейс К580ВВ55А, последовательный

интерфейс К580ВВ51А, контроллер прямого доступа к памяти

К580ВТ57, контроллер прерываний К580ВН59, контроллер клавиатуры

и индикации К580ВВ79, таймер интервалов К580ВИ53, контроллер ал-

фавитно-цифровых дисплеев К580ВГ75, генератор тактовых сигналов

К580ГФ24, системные контроллеры К580ВК28 и К580ВК38, буферные

регистры К580ИР82 и К580ИР83 (с инверсией), шинные формировате-

ли К580ВА86 и К580ВА87 (с инверсией), контроллер шины К580ВГ18,

интерфейс системы микропроцессор — канал общего пользования

К580ВК91А, контроллер интерфейса системы микропроцессор - канал

общего пользования К580ВГ92, приемопередатчик системы микропро-

цессор - канал общего пользования К580ВА93.

МПК серии К1806 предназначен для использования в контроллерах и

системах управления технологическими процессами, в системах связи,

в контрольно-измерительной аппаратуре и других областях применения.

МПК включает в свой состав: микропроцессор К1806ВМ2, контроллер

устройств индикации К1806ВП1-092, контроллер клавиатуры и програм-

мируемый таймер К1806ВП1-093.

МПК серии К1808 [11] предназначен для построения бытовой радио-

электронной аппаратуры, в том числе устройств управления зеркальны-

ми фотокамерами. В состав серии входят следующие БИС: микропро-

цессор К1808ВМ1, устройство задания режимов экспонирования

14

К1808ВВ1, схема интерфейса для фотоаппаратов К1808ВВ2, схема авто-

матической фокусировки К1808ВВЗ, аналого-цифровой преобразователь

К1808ИР1, устройства автоматического управления экспозицией

К1808ХК1 и К1808ХК2, устройство управления семисегментным инди-

катором К1808ВУ1, устройство управления светодиодными матрицами

К1808ВУ2.

Получившая в последние годы развитие новая номенклатура микро-

процессорных БИС — однокристальных микроЭВМ и специализирован-

ных МПК цифровой обработки сигналов имеет большую перспективу

применения в силу своих функциональных возможностей и характери-

стик. К числу перспективных можно отнести ОЭВМ серий К1816, К1820

и К1829, а также ОЭВМК1813ВЕ1 и МПК серии К1815 для цифровой об-

работки сигналов. Разработанные на основе p-МОП технологии серии

К145 и К1814 находят ограниченное применение.

Серия К145 [12] представляет собой достаточно обширную номенкла-

туру БИС, предназначенных для построения программируемых микро-

калькуляторов, устройств и систем управления различного назначения.

В их число входит ряд однокристальных микроконтроллеров последова-

тельного действия, которые разработаны на основе базовых БИС

К145ИК18 и К145ИК19, имеющих соответственно: емкость внутреннего

ПЗУ 5,5 и 4,0 Кбит, емкость внутреннего ОЗУ 76x4 и 34x4 бит, набор из

40 и 32 команд, частоту тактовых импульсов 70-200 и 30-40 кГц.

Функциональное назначение вариантов исполнения микроконтроллеров

следующее: сопряжение с датчиками (К145ИК1801), управление элек-

тромеханическим печатающим устройством (К145ИК1802), управление

устройством ввода-вывода на перфоленту, сопряжение с ЗУ и микроЭВМ

типа ”Электроника-60” (К145ИК1803), управление термопечатающим

устройством (К145ИК1805), управление электробытовыми приборами,

технологическим оборудованием и процессами (К145ИК1807), преобра-

зование, обработка и контроль аналого-цифровой информации

(К145ИК1808), процессор с портами ввода-вывода для микроЭВМ

(К145ИК1809 и К145ИК1810), процессор для устройств сбора ина-

копления данных (К145ИК1811), управление дисплеем и клавиатурой

(К145ИК1814), часы-таймер (К145ИК1901), вычисление и контроль

скорости движения автомобиля и расхода горючего (К145ИК1903),

контроль и управление режимами работы лентопротяжного механизма

бытового магнитофона (К145ИК1906), многофункциональный таймер-

программатор (К145ИК1907 и К145ИК1908), одновременное управ-

ление двумя независимыми процессами (К145ИК1909), управление

параметром (температурой, влажностью, давлением и др.) в заданных

пределах (К145ИК1910), сопряжение с телефонной линией связи

(К145ИК1905 и К145ИК1912), управление роботами (К145ИК1916).

Серия К1814 [13] представляет собой совокупность 4-разрядных

ОЭВМ, предназначенных для применения в системах управления, в конт-

рольно-измерительной, медицинской и бытовой аппаратуре. Серия К1814

15

включает с свой состав идентичные по структуре ОЭВМ: К1814ВЕ1 с

внутренним масочным ПЗУ емкостью 1 Кбайт, внутренним ОЗУ емко-

стью 64х4 бит, набором из 43 команд, тактовой частотой 100—300 кГц и

К1814ВЕЗ, отличием которой является отсутствие внутреннего ПЗУ и на-

личие дополнительных выводов, обеспечивающих подключение внешнего

ПЗУ аналогичного объема и организации. На базе К1814ВЕ1 разработаны

ОЭВМ, выполняющие функции специализированных микроконтролле-

ров: цветомузыкального устройства (К1814ВЕ2), кассетного магнито-

фона (К1814ВЕ4) и телевизионной техники (К1814ВЕ5). МикроЭВМ

К1814ВЕЗ может быть использована для отладки программ разрабатыва-

емых микроконтроллеров или для самостоятельного применения в изде-

лиях, требующих периодической модернизации (переналадки) или изго-

тавляемых в небольших количествах, когда разработка масочного ва-

рианта экономически нецелесообразна.

Серия К1829, разрабатываемая на основе КМОП-технологии, обеспечи-

вающей малое энергопотребление, предназначена для применения в быто-

вой, медицинской и измерительной аппаратуре, контроллерах автомо-

бильных устройств, калькуляторах, многофункциональных часовых и

таймерных устройствах. К1829 имеет в своем составе пока только 4-раз-

рядную ОЭВМ К1829ВМ1 с внутренним масочным ПЗУ емкостью 2 Кбайт,

внутренним ОЗУ емкостью 128х4 бит, набором из 92 команд, минималь-

ным циклом выполнения команды 10 мкс и возможностью управления

ЖК-индикатором. Возможности применения серии К1829 значительно

расширятся после разработки отладочной ОЭВМ.

ГЛ А В А 2

СОСТАВ, СТРУКТУРА И ФУНКЦИОНАЛЬНЫЕ ВОЗМОЖНОСТИ

МИКРОПРОЦЕССОРНЫХ КОМПЛЕКТОВ ШИРОКОГО ПРИМЕНЕНИЯ

2.1. Восьмиразрядный микропроцессорный комплект серии К1821

Состав. Микропроцессорный комплект серии К1821 включает:

К1821ВМ85А — однокристальный 8-разрядный МП с емкостью адресуе-

мой памяти 64 Кбайт и тактовой частотой 3 мГц, К1821РУ55 — стати-

ческое ОЗУ емкостью 2 Кбит (256х8 бит) с портами ввода-вывода и тай-

мером, К1821РЕ55 - ПЗУ емкостью 16 Кбит (2048х8 бит) с портами

ввода-вывода.

Совместно с БИС серии К1821 может быть использована широкая но-

менклатура БИС серии К580. Микропроцессор К1821ВМ85 А имеет по

сравнению сК580ВМ80А более высокое быстродействие, возможность

последовательного ввода-вывода данных, одно напряжение питания, объе-

диняете себе функции тактового генератора К580ГФ24 и системного кон-

троллера-шинного формирователя К580ВК28 и полностью совместим с

К580ВМ80А по системе команд.

16

TRAP

RST 7.5

RST 6.5

RST 5.5

INTA

INTR

Блок управления

прерываниями

Блок управления SID

последовательным

вводом—выводом —SOD

Регистр

временного

хранения

Регистр

признаков

Регистр

команд

Регистр В

Регистр D

Регистр С

Регистр Е

SRI

SRO

HLDA

HOLD

Ю/М

SO

S1

ЕА

WR

RD

RA

SYNC

АЛУ

Дешифратор

команд и

шифратор

машинных

циклов

Регистр Н

Регистр L

Указатель стека

СК

Регистр адреса со схемой

инкремента - декремента

Синхронизация команд |

Блок синхронизации

и управления

Буфер адреса

А8-А15

Буфер адреса

— данных

AD0-AD7

CR1

CR2

Рис. 2.1. Структурная схема микропроцессора К1821ВМ85А

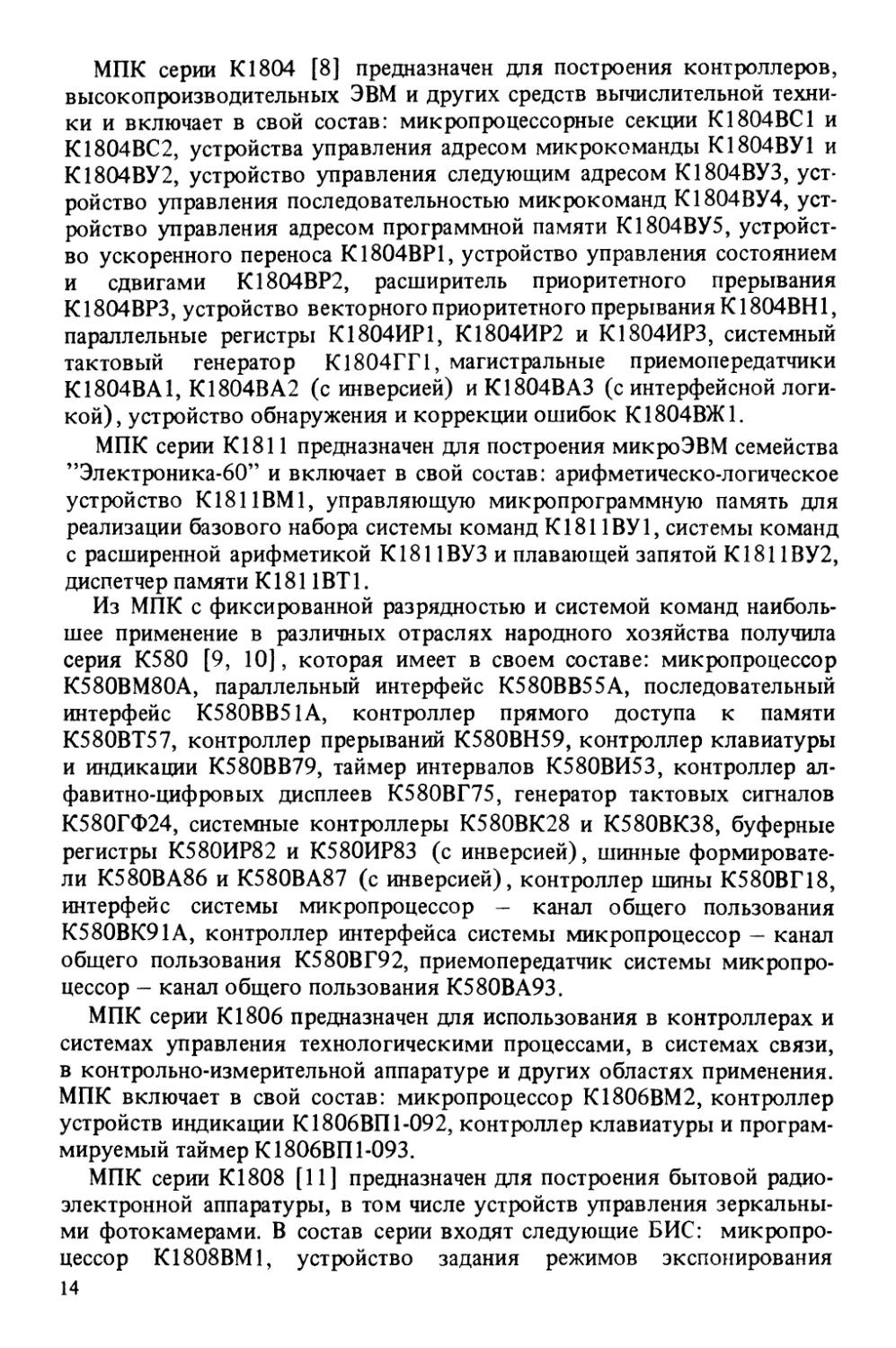

Структурная схема К1821ВМ85А (рис. 2.1) показывает состав его ос-

новных функциональных блоков и связи между ними, а также внешние

информационно-управляющие сигналы.

Микропроцессор имеет следующие функциональные блоки: арифме-

тическо-логическое устройство (АЛУ), аккумулятор (А), регистр вре-

менного хранения, регистр признаков (флагов), регистр команд, блок

регистров (шесть регистров общего назначения, указатель стека, счетчик

команд и регистр адреса со схемой инкремента-декремента), дешифра-

тор команд и шифратор машинных циклов, буфер старших разрядов ад-

реса А8-А15, буфер адреса данных AD0-AD7, блок синхронизации и

управления, блок управления прерываниями, блок управления после-

довательным вводом-выводом.

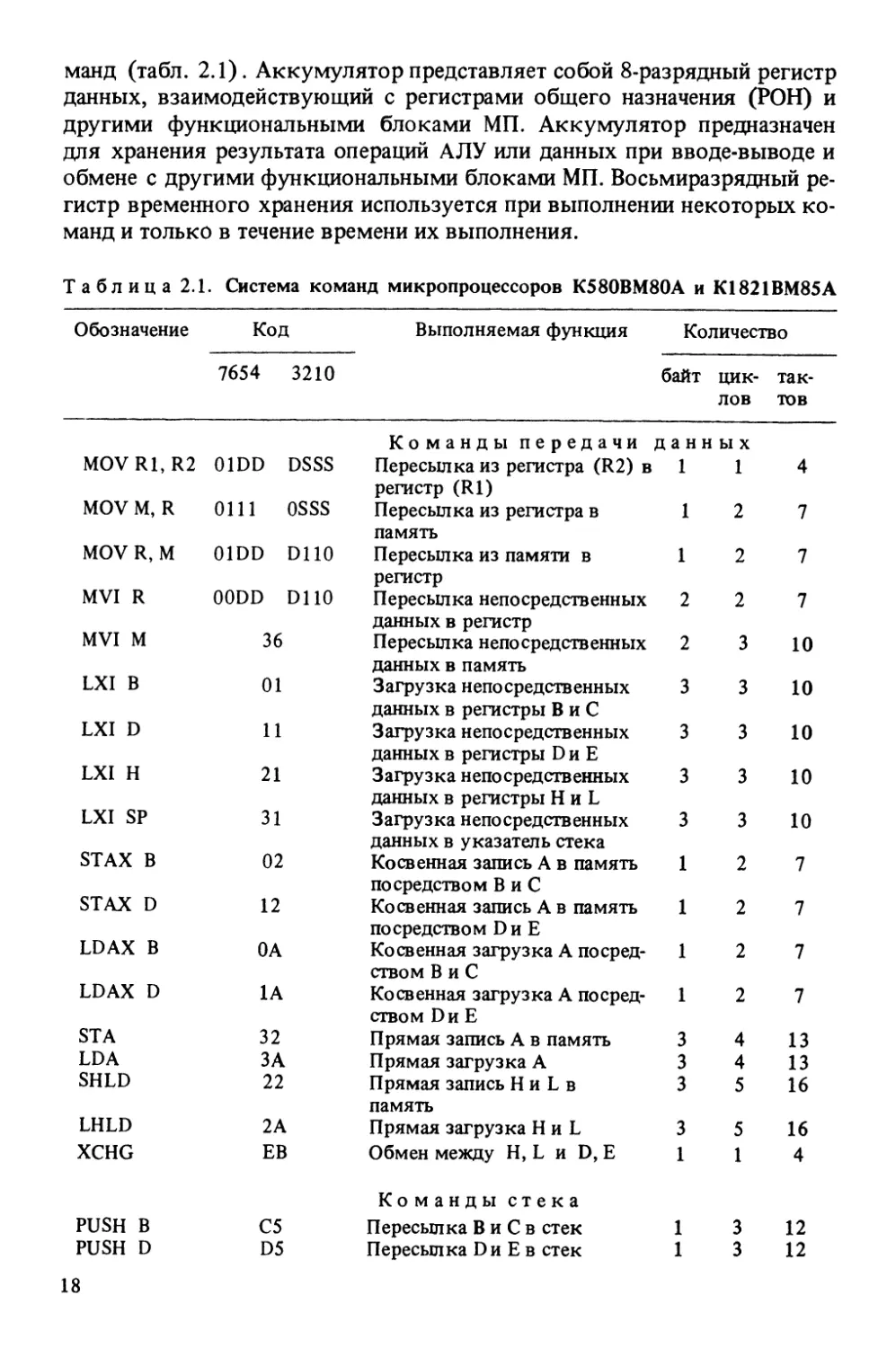

Восьмиразрядное АЛУ выполняет арифметические и логические опе-

рации, операции сдвига и управления, предусмотренные системой ко-

17

манд (табл. 2.1). Аккумулятор представляет собой 8-разрядный регистр

данных, взаимодействующий с регистрами общего назначения (РОН) и

другими функциональными блоками МП. Аккумулятор предназначен

для хранения результата операций АЛУ или данных при вводе-выводе и

обмене с другими функциональными блоками МП. Восьмиразрядный ре-

гистр временного хранения используется при выполнении некоторых ко-

манд и только в течение времени их выполнения.

Таблица 2.1. Система команд микропроцессоров К580ВМ80А и К1821ВМ85А

Обозначение Код Выполняемая функция Количество

7654 3210 байт цик- лов так- тов

MOV Rl, R2 01DD DSSS Команды передачи Пересылка из регистра (R2) в д а н н 1 ы X 1 4

MOV М, R 0111 OSSS регистр (R1) Пересылка из регистра в 1 2 7

MOV R, М 01DD D110 память Пересылка из памяти в 1 2 7

MVI R 00DD DUO регистр Пересылка непосредственных 2 2 7

MVI M 36 данных в регистр Пересылка непосредственных 2 3 10

LXI В 01 данных в память Загрузка непосредственных 3 3 10

LXI D 11 данных в регистры В и С Загрузка непосредственных 3 3 10

LXI H 21 данных в регистры D и Е Загрузка непосредственных 3 3 10

LXI SP 31 данных в регистры Н и L Загрузка непосредственных 3 3 10

STAX В 02 данных в указатель стека Косвенная запись А в память 1 2 7

STAX D 12 посредством В и С Косвенная запись А в память 1 2 7

LDAX В 0A посредством Dh Е Косвенная загрузка А посред- 1 2 7

LDAX D 1A ством В и С Косвенная загрузка А посред- 1 2 7

STA 32 ством Dh Е Прямая запись А в память 3 4 13

LDA ЗА Прямая загрузка А 3 4 13

SHLD 22 Прямая запись Н и L в 3 5 16

LHLD 2A память Прямая загрузка Н и L 3 5 16

XCHG ЕВ Обмен между Н, L и D, Е 1 1 4

PUSH В C5 Команды стека Пересылка В и С в стек 1 3 12

PUSH D D5 Пересылка Dh Е в стек 1 3 12

18

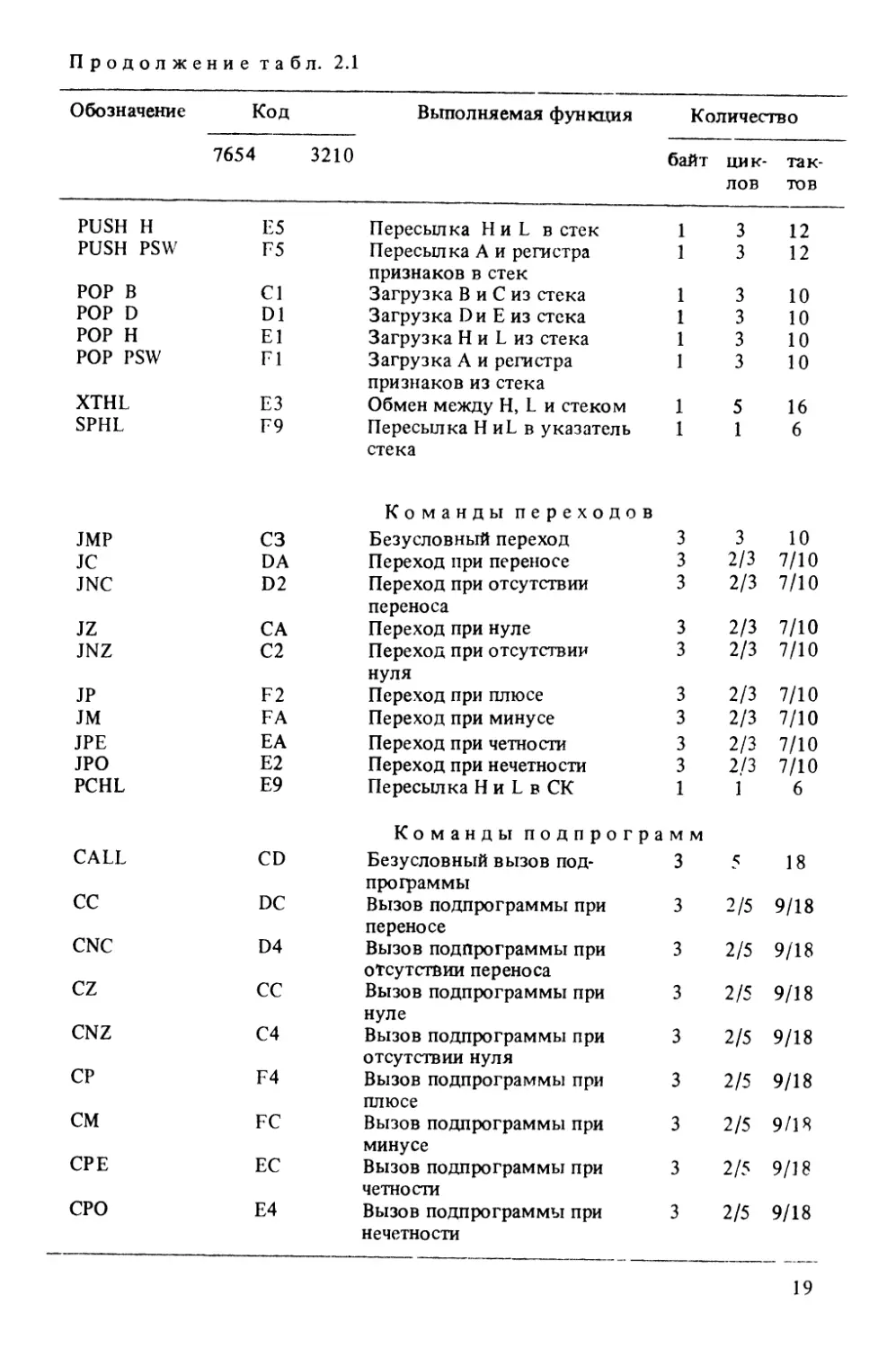

Продолжение табл. 2.1

Обозначение Код Выполняемая функция 3210 Количество

7654 байт цик- лов так- тов

PUSH н E5 Пересылка HhL в стек 1 3 12

PUSH PSW F5 Пересылка А и регистра признаков в стек 1 3 12

POP в Cl Загрузка В и С из стека 1 3 10

POP D DI Загрузка Dh Е из стека 1 3 10

POP н El Загрузка Н и L из стека 1 3 10

POP PSW Fl Загрузка А и регистра признаков из стека 1 3 10

XTHL E3 Обмен между Н, L и стеком 1 5 16

SPHL F9 Пересылка Н иЕ в указатель 1 1 6

стека

Команды переходов

JMP C3 Безусловный переход 3 3 10

JC DA Переход при переносе 3 2/3 7/10

JNC D2 Переход при отсутствии переноса 3 2/3 7/10 7/10

JZ CA Переход при нуле 3 2/3

JNZ C2 Переход при отсутствии нуля 3 2/3 7/10 7/10

JP F2 Переход при плюсе 3 2/3

JM FA Переход при минусе 3 2/3 7/10

JPE EA Переход при четности 3 2/3 7/10

JPO E2 Переход при нечетности 3 2/3 7/10

PCHL E9 Пересылка Н и L в СК 1 1 6

Команды подпрограмм

CALL CD Безусловный вызов под- программы 3 5 18

CC DC Вызов подпрограммы при переносе 3 2/5 9/18

CNC D4 Вызов подпрограммы при отсутствии переноса 3 2/5 9/18

CZ CC Вызов подпрограммы при нуле 3 2/5 9/18

CNZ C4 Вызов подпрограммы при отсутствии нуля 3 2/5 9/18

CP F4 Вызов подпрограммы при 3 2/5 9/18

плюсе

CM FC Вызов подпрограммы при минусе 3 2/5 9/18

CPE EC Вызов подпрограммы при 3 2/5 9/18

четности

CPO E4 Вызов подпрограммы при нечетности 3 2/5 9/18

19

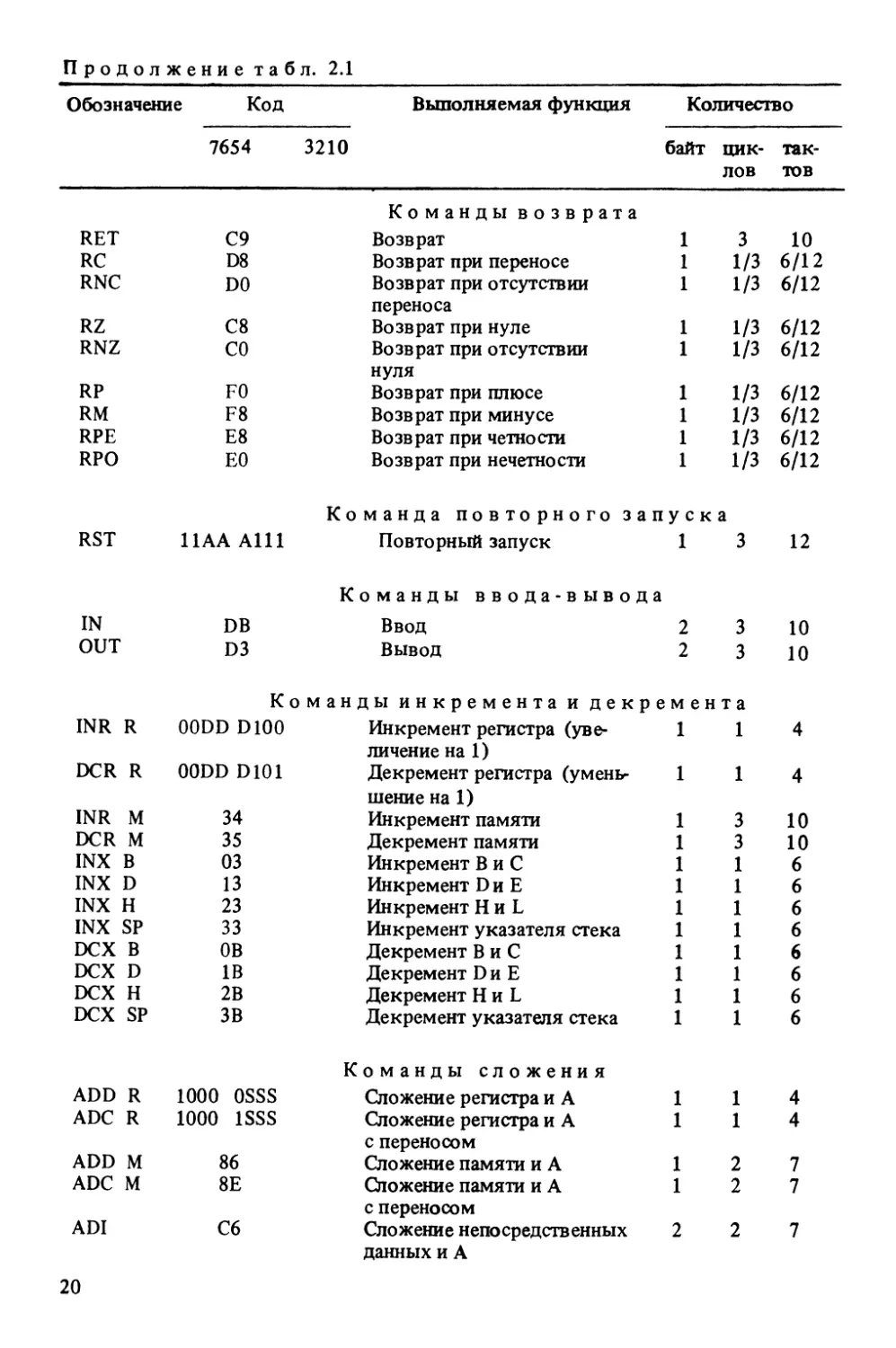

Продолжение табл. 2.1

Обозначение Код Выполняемая функция Количество

7654 3210 байт цик- лов так- тов

RET C9 Команды возврата Возврат 1 3 10

RC D8 Возврат при переносе 1 1/3 6/12

RNC DO Возврат при отсутствии 1 1/3 6/12

RZ C8 переноса Возврат при нуле 1 1/3 6/12

RNZ CO Возврат при отсутствии 1 1/3 6/12

RP F0 нуля Возврат при плюсе 1 1/3 6/12

RM F8 Возврат при минусе 1 1/3 6/12

RPE E8 Возврат при четности 1 1/3 6/12

RPO E0 Возврат при нечетности 1 1/3 6/12

Команда повторного запуска

RST 11АА А111 Повторный запуск 1 3 12

IN DB Команды ввода-вывода Ввод 2 3 10

OUT D3 Вывод 2 3 10

Команды инкремента и декремента

INR R 00DD D100 Инкремент регистра (уве- личение на 1) 1 1 4

DCR R 00DD D101 Декремент регистра (умень- шение на 1) 1 1 4

INR M 34 Инкремент памяти 1 3 10

DCR M 35 Декремент памяти 1 3 10

INX В 03 Инкремент В и С 1 1 6

INX D 13 Инкремент D и Е 1 1 6

INX H 23 Инкремент Н и L 1 1 6

INX SP 33 Инкремент указателя стека 1 1 6

DCX В 0B Декремент В и С 1 1 6

DCX D IB Декремент D и Е 1 1 6

DCX H 2B Декремент Н и L 1 1 6

DCX SP 3B Декремент указателя стека 1 1 6

Команды сложения

ADD R 1000 OSSS Сложение регистра и А 1 1 4

ADC R 1000 1SSS Сложение регистра и А с переносом 1 1 4

ADD M 86 Сложение памяти и А 1 2 7

ADC M 8E Сложение памяти и А с переносом 1 2 7

ADI C6 Сложение непосредственных 2 2 7

данных и А

20

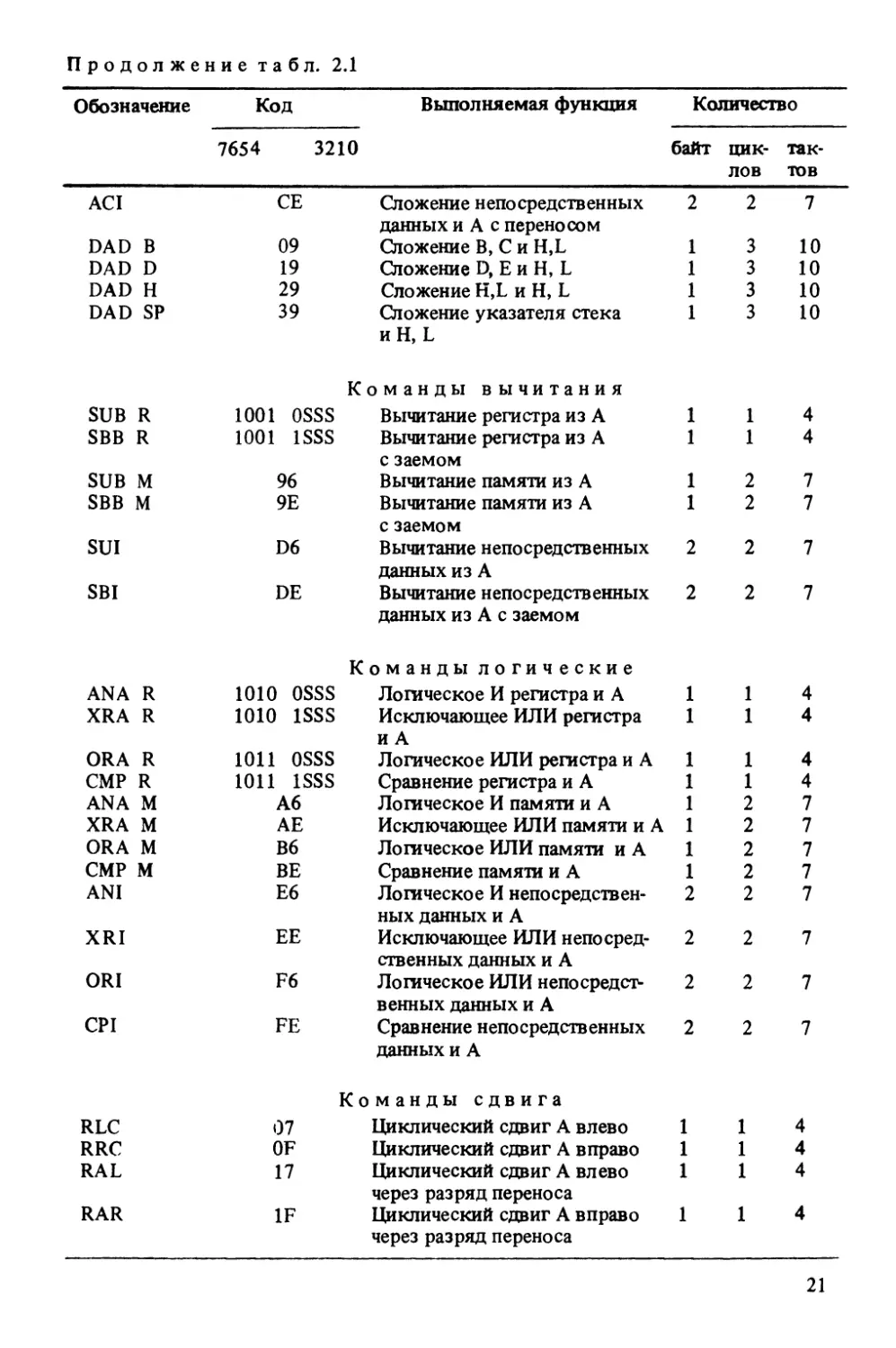

Продолжение табл. 2.1

Обозначение Код Выполняемая функция Количество

7654 3210 байт цик- так-

лов тов

ACI CE Сложение непосредственных данных и А с переносом 2 2 7

DAD В 09 Сложение В, С и H,L 1 3 10

DAD D 19 Сложение D, Е и Н, L 1 3 10

DAD Н 29 Сложение H,L и Н, L 1 3 10

DAD SP 39 Сложение указателя стека иН, L 1 3 10

Команды вычитания

SUB R 1001 OSSS Вычитание регистра из А 1 1 4

SBB R 1001 1SSS Вычитание регистра из А 1 1 4

с заемом

SUB M 96 Вычитание памяти из А 1 2 7

SBB M 9E Вычитание памяти из А с заемом 1 2 7

SUI D6 Вычитание непосредственных данных из А 2 2 7

SBI DE Вычитание непосредственных данных из А с заемом 2 2 7

Команды логические

ANA R 1010 OSSS Логическое И регистра и А 1 1 4

XRA R 1010 1SSS Исключающее ИЛИ регистра и А 1 1 4

ORA R 1011 OSSS Логическое ИЛИ регистра и А 1 1 4

CMP R 1011 1SSS Сравнение регистра и А 1 1 4

ANA M A6 Логическое И памяти и А 1 2 7

XRA M AE Исключающее ИЛИ памяти и А 1 2 7

ORA M B6 Логическое ИЛИ памяти и А 1 2 7

CMP M BE Сравнение памяти и А 1 2 7

ANI E6 Логическое И непосредствен- ных данных и А 2 2 7

XRI EE Исключающее ИЛИ непосред- ственных данных и А 2 2 7

ORI F6 Логическое ИЛИ непосредст- венных данных и А 2 2 7

CPI FE Сравнение непосредственных данных и А 2 2 7

Команды сдвига

RLC 07 Циклический сдвиг А влево 1 1 4

RRC OF Циклический сдвиг А вправо 1 1 4

RAL 17 Циклический сдвиг А влево через разряд переноса 1 1 4

RAR IF Циклический сдвиг А вправо 1 1 4

через разряд переноса

21

Продолжение табл. 2.1

Обозначение Код Выполняемая функция Количество

7654 3210 байт цик- лов так- тов

Команды специальные

СМА 2F Инвертирование А 1 1 4

STC 37 Установка признака переноса в единицу 1 1 4

СМС 3F Инвертирование признака переноса 1 1 4

DAA 27 Преобразование А в двоично- десятичный код 1 1 4

Команды управления

EI FB Разрешение прерывания 114

DI F3 Запрещение прерывания 114

NOP 00 Нет операции 114

HLT 76 Останов 115

Команды дополнительные (для К1821ВМ85А)

RIM 20 Чтение маски прерывания 114

SIM 30 Установка маски прерывания 114

Примечание.

1. DDD - код регистра-приемника данных; SSS - код регистра-источника дан-

ных. Коды регистров: В - ООО; С-001; D-010; Е-011; Н- 100; L-101; памя-

ти - 110; аккумулятора (А) - 111.

2. Значения циклов и тактов приведены для К1821ВМ85А; два возможных их

значения приведены для команд, зависящих от состояния признаков (флагов).

Шестнадцатиразрядный указатель стека предназначен для хранения ад-

реса ячейки стека, к которой было произведено последнее обращение.

Шестнадцатиразрядный счетчик команд СК предназначен для хранения

адреса следующей выполняемой команды. Восьмиразрядные РОН (В, С,

D, Е, Н, L) могут быть использованы для хранения данных независимо

друг от друга или соединены в регистровые пары - 16-разрядные регист-

ры данных или адреса памяти. Шестнадцатиразрядный регистр адреса со

схемой инкремента-декремента позволяет увеличивать или уменьшать

на единицу содержимое 16-разрядных регистров. Восьмиразрядный ре-

гистр команд используется для хранения выбранной команды. Регистр

признаков предназначен для определения дополнительных характери-

стик результата и состояния АЛУ. В состав регистра входят пять тригге-

ров признаков: триггер знака 5, триггер переноса С, триггер вспомога-

тельного переноса АС, триггер нуля L, триггер четности Р.

Блок управления прерываниями переключает МП с выполнения одной

программы на другую с помощью внешних сигналов прерывания и по-

22

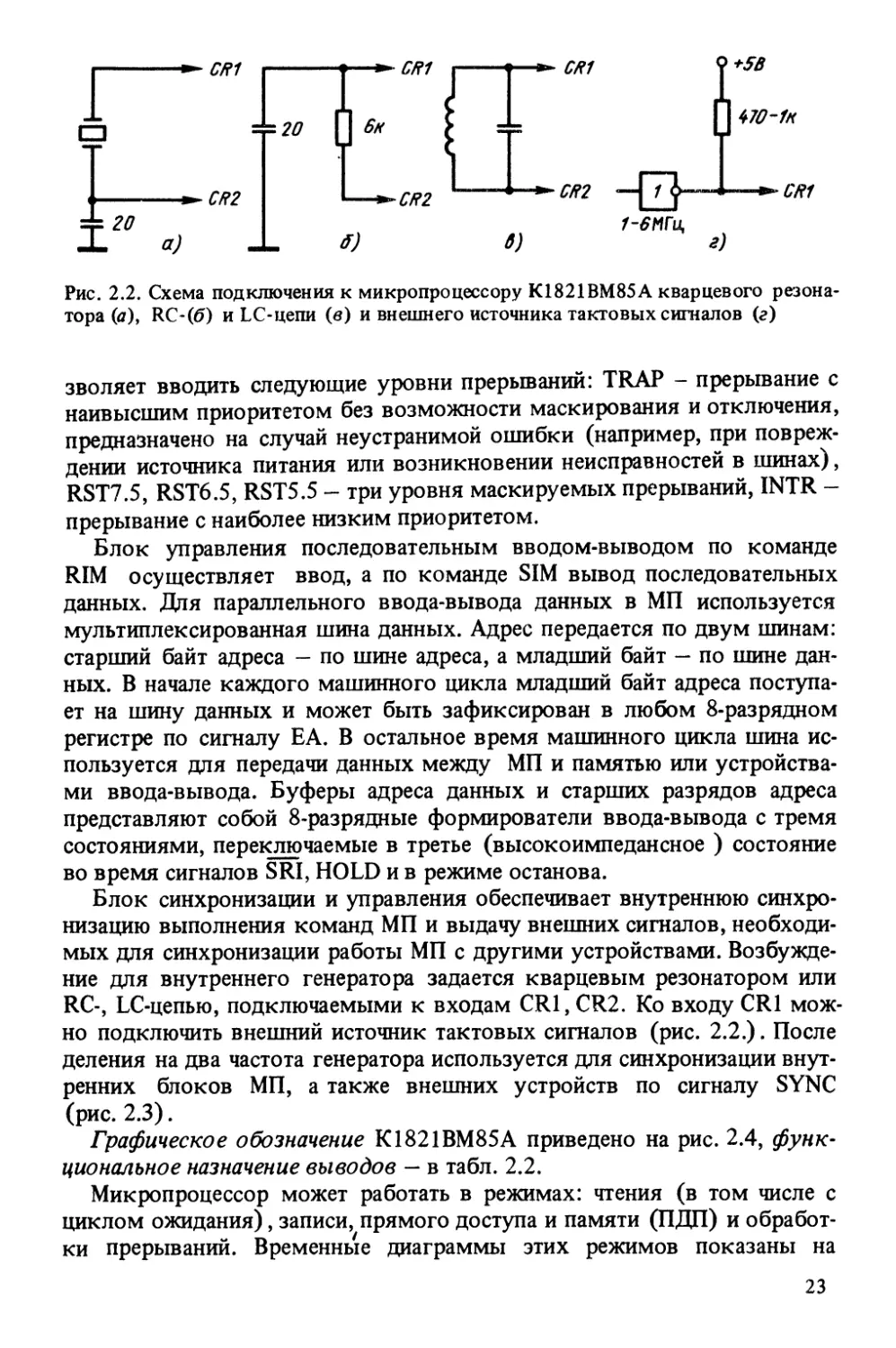

Рис. 2.2. Схема подключения к микропроцессору К1821ВМ85А кварцевого резона-

тора (я), RC-(6) и LC-цепи (в) и внешнего источника тактовых сигналов (г)

зволяет вводить следующие уровни прерываний: TRAP - прерывание с

наивысшим приоритетом без возможности маскирования и отключения,

предназначено на случай неустранимой ошибки (например, при повреж-

дении источника питания или возникновении неисправностей в шинах),

RST7.5, RST6.5, RST5.5 - три уровня маскируемых прерываний, INTR -

прерывание с наиболее низким приоритетом.

Блок управления последовательным вводом-выводом по команде

RIM осуществляет ввод, а по команде SIM вывод последовательных

данных. Для параллельного ввода-вывода данных в МП используется

мультиплексированная шина данных. Адрес передается по двум шинам:

старший байт адреса — по шине адреса, а младший байт — по шине дан-

ных. В начале каждого машинного цикла младший байт адреса поступа-

ет на шину данных и может быть зафиксирован в любом 8-разрядном

регистре по сигналу ЕА. В остальное время машинного цикла шина ис-

пользуется для передачи данных между МП и памятью или устройства-

ми ввода-вывода. Буферы адреса данных и старших разрядов адреса

представляют собой 8-разрядные формирователи ввода-вывода с тремя

состояниями, переключаемые в третье (высокоимпедансное ) состояние

во время сигналов SRI, HOLD и в режиме останова.

Блок синхронизации и управления обеспечивает внутреннюю синхро-

низацию выполнения команд МП и выдачу внешних сигналов, необходи-

мых для синхронизации работы МП с другими устройствами. Возбужде-

ние для внутреннего генератора задается кварцевым резонатором или

RC-, LC-цепью, подключаемыми к входам CR1, CR2. Ко входу CR1 мож-

но подключить внешний источник тактовых сигналов (рис. 2.2.). После

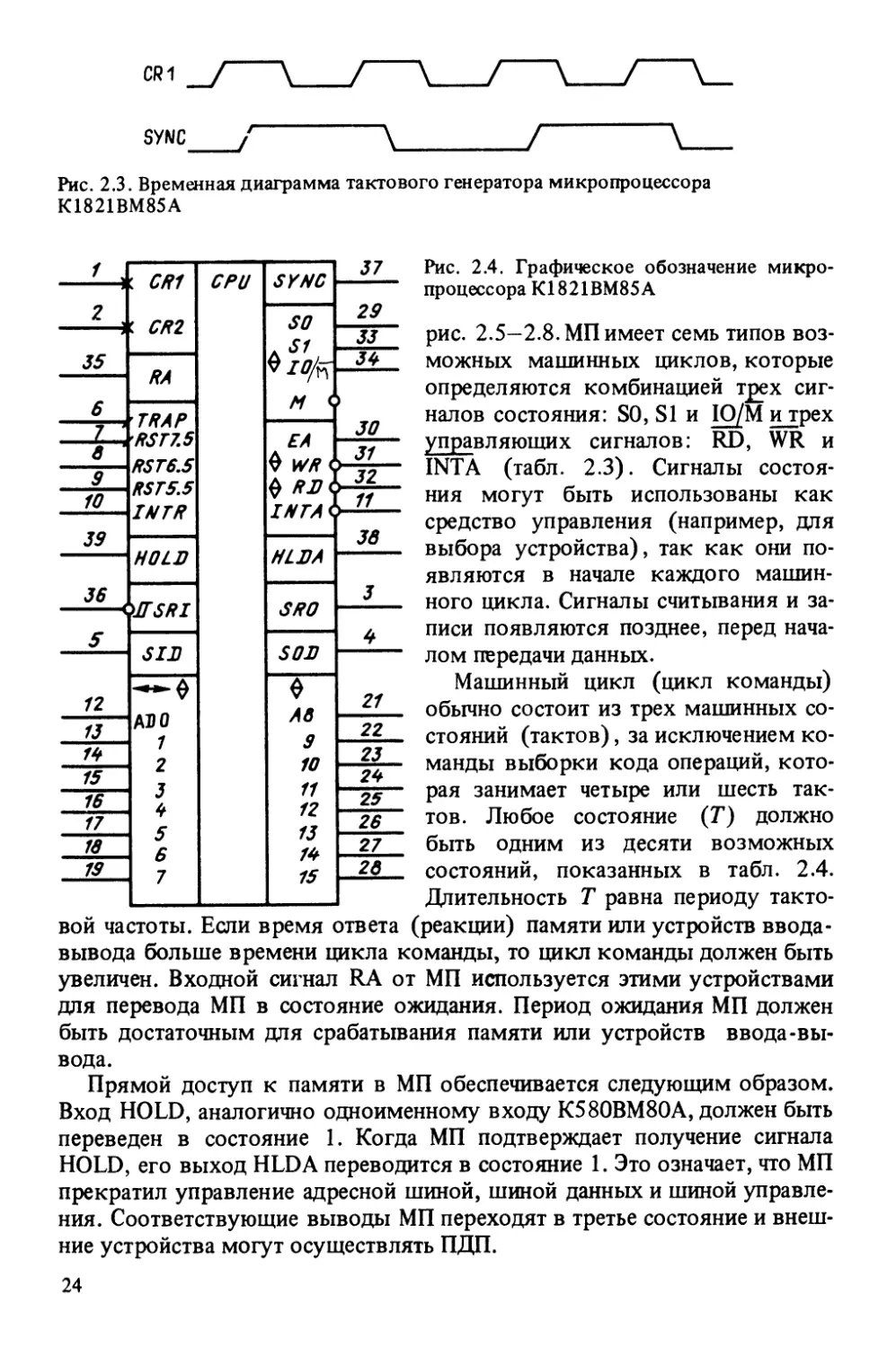

деления на два частота генератора используется для синхронизации внут-

ренних блоков МП, а также внешних устройств по сигналу SYNC

(рис. 2.3).

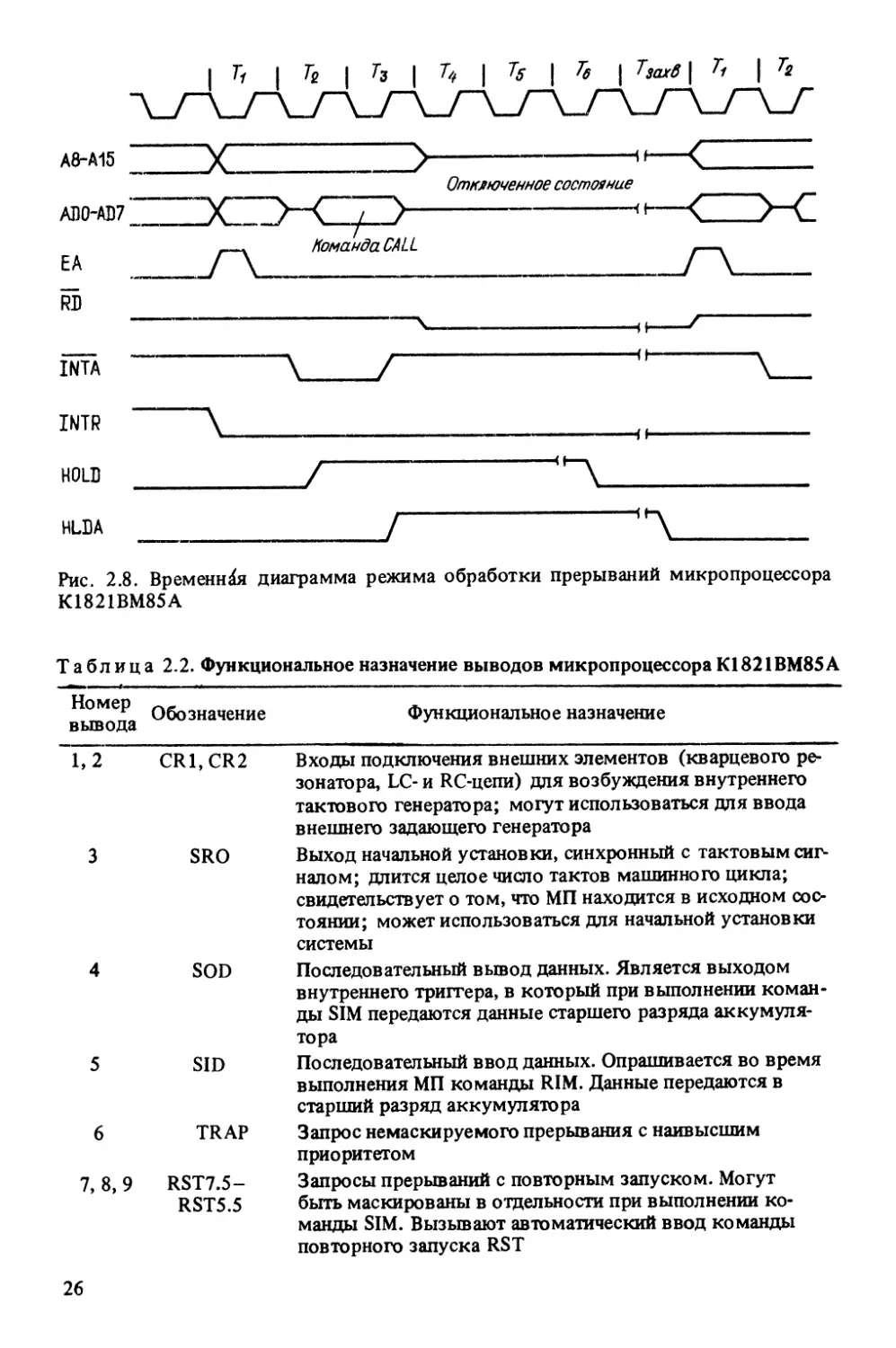

Графическое обозначение К1821ВМ85А приведено на рис. 2.4, функ-

циональное назначение выводов — в табл. 2.2.

Микропроцессор может работать в режимах: чтения (в том числе с

циклом ожидания), записи, прямого доступа и памяти (ПДП) и обработ-

ки прерываний. Временные диаграммы этих режимов показаны на

23

Рис. 2.3. Временная диаграмма тактового генератора микропроцессора

К1821ВМ85А

1 , : CR1 С CR2 CPU SYNC 37

2 29

SO К S1 $ I Ofc M <

35 33 34 30

RA

6

TRAP RST7.5 RSTS.5 RST5.5 INTR

EA 0 WR < INTM

а ' [ 31

9 [ 32

10 L 11

39 36

HOLD HLDA

36 5 3

WSRI SRO

4

SID SOD

12 21

ADO 1 2 3 4 5 6 7 $ A6 9 10 11 12 13 14 15

13 22

14 23

15 24

16 25

17 26

16 27

19 26

Рис. 2.4. Графическое обозначение микро-

процессора К1821ВМ85А

рис. 2.5—2.8. МП имеет семь типов воз-

можных машинных циклов, которые

определяются комбинацией трех сиг-

налов состояния: SO, S1 и Ю/М и трех

управляющих сигналов: RD, WR и

INTA (табл. 2.3). Сигналы состоя-

ния могут быть использованы как

средство управления (например, для

выбора устройства), так как они по-

являются в начале каждого машин-

ного цикла. Сигналы считывания и за-

писи появляются позднее, перед нача-

лом передачи данных.

Машинный цикл (цикл команды)

обычно состоит из трех машинных со-

стояний (тактов), за исключением ко-

манды выборки кода операций, кото-

рая занимает четыре или шесть так-

тов. Любое состояние (Т) должно

быть одним из десяти возможных

состояний, показанных в табл. 2.4.

Длительность Т равна периоду такто-

вой частоты. Если время ответа (реакции) памяти или устройств ввода-

вывода больше времени цикла команды, то цикл команды должен быть

увеличен. Входной сигнал RA от МП используется этими устройствами

для перевода МП в состояние ожидания. Период ожидания МП должен

быть достаточным для срабатывания памяти или устройств ввода-вы-

вода.

Прямой доступ к памяти в МП обеспечивается следующим образом.

Вход HOLD, аналогично одноименному входу К580ВМ80А, должен быть

переведен в состояние 1. Когда МП подтверждает получение сигнала

HOLD, его выход HLDA переводится в состояние 1. Это означает, что МП

прекратил управление адресной шиной, шиной данных и шиной управле-

ния. Соответствующие выводы МП переходят в третье состояние и внеш-

ние устройства могут осуществлять ПДП.

24

| Tt | тг I To* I T3 I 7/

SYNC ---------/ \------/ \------/ \------1 \—

A8-A15 ~X Адрес '' X~

AB0-AB7~\ Адрес

yillllllllllllllt.

Ввод данных

RD/INTA.

RA

Рис. 2.5. Временная диаграмма цикла чтения (с ожиданием) микропроцессора

К1821ВМ85А

А8-А15~^Х" мРес

ADO-APT^ Адрес Х~

Вывод данных

Рис. 2.6. Временная диаграмма цикла записи микропроцессора К1821ВМ85А

HLDA / ” \

АВО-АБ^ Отключенное состояние

А8-А15__________ У~^'----------------------------------------

Рис. 2.7. Временная диаграмма режима ПДП микропроцессора К1821ВМ85А

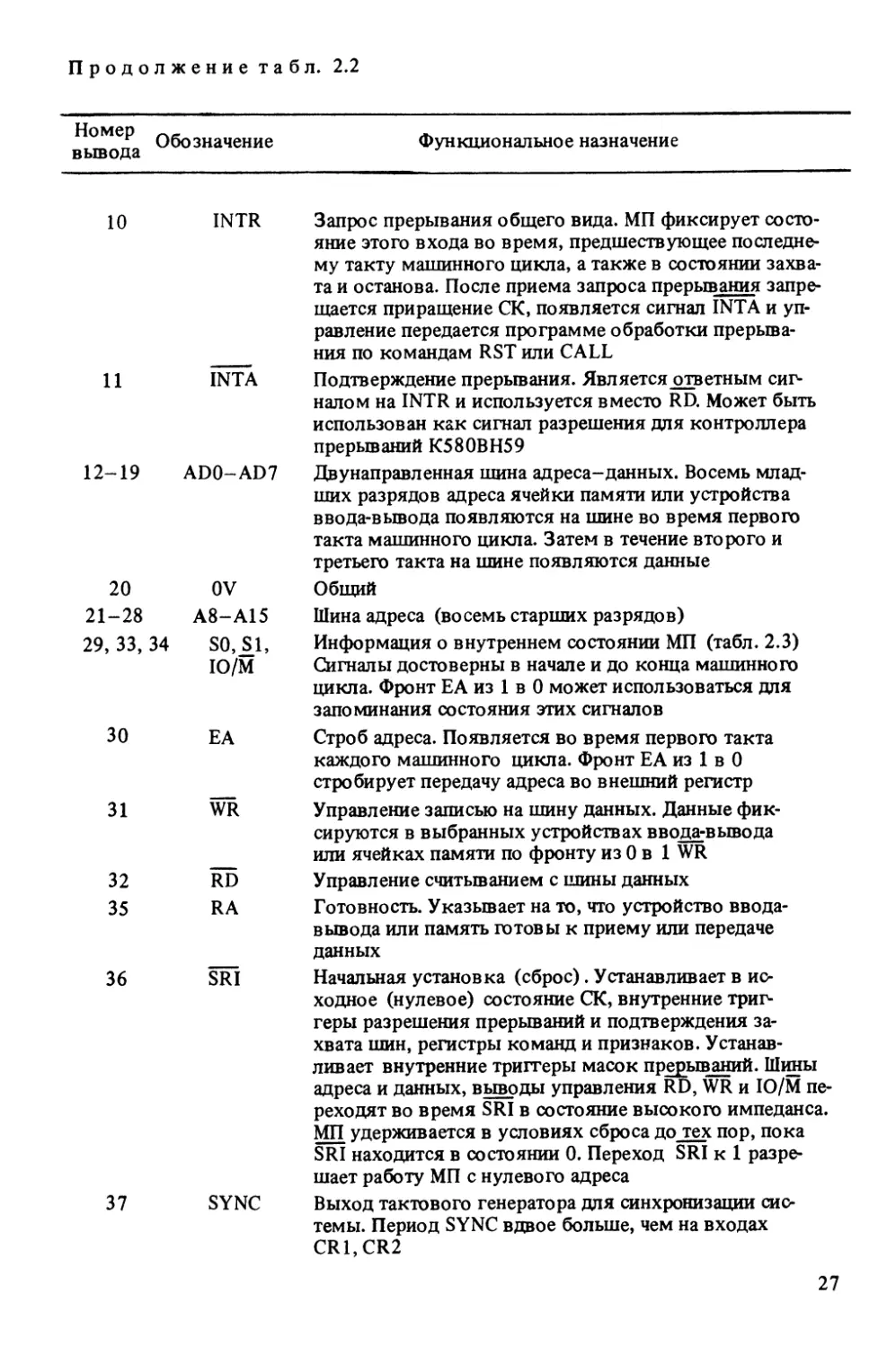

I Г/ I TS | T3 | T/f I TS | Tg | Tgarf | T1 | T2

Рис. 2.8. Временная диаграмма режима обработки прерываний микропроцессора

К1821ВМ85А

Таблица 2.2. Функциональное назначение выводов микропроцессора К1821ВМ85А

Обозначение вывода Функциональное назначение

1,2 CR1.CR2 Входы подключения внешних элементов (кварцевого ре- зонатора, LC- и RC-цепи) для возбуждения внутреннего тактового генератора; могут использоваться для ввода внешнего задающего генератора

3 SRO Выход начальной установки, синхронный с тактовым сиг- налом; длится целое число тактов машинного цикла; свидетельствует о том, что МП находится в исходном сос- тоянии; может использоваться для начальной установки системы

4 SOD Последовательный вывод данных. Является выходом внутреннего триггера, в который при выполнении коман- ды SIM передаются данные старшего разряда аккумуля- тора

5 SID Последовательный ввод данных. Опрашивается во время выполнения МП команды RIM. Данные передаются в старший разряд аккумулятора

6 TRAP Запрос немаскируемого прерывания с наивысшим приоритетом

7, 8, 9 RST7.5- RST5.5 Запросы прерываний с повторным запуском. Могут быть маскированы в отдельности при выполнении ко- манды SIM. Вызывают автоматический ввод команды повторного запуска RST

26

Продолжение табл. 2.2

Номер

вывода

Обозначение

Функциональное назначение

10 INTR Запрос прерывания общего вида. МП фиксирует состо- яние этого входа во время, предшествующее последне- му такту машинного цикла, а также в состоянии захва- та и останова. После приема запроса прерывания запре- щается приращение СК, появляется сигнал INTA и уп- равление передается программе обработки прерыва- ния по командам RST или CALL

11 INTA Подтверждение прерывания. Является ответным сиг- налом на INTR и используется вместо RD. Может быть использован как сигнал разрешения для контроллера прерываний К580ВН59

12-19 AD0-AD7 Двунаправленная шина адреса-данных. Восемь млад- ших разрядов адреса ячейки памяти или устройства ввода-вывода появляются на шине во время первого такта машинного цикла. Затем в течение второго и третьего такта на шине появляются данные

20 OV Общий

21-28 А8-А15 Шина адреса (восемь старших разрядов)

29, 33, 34 SO, SI, IO/M Информация о внутреннем состоянии МП (табл. 2.3) Сигналы достоверны в начале и до конца машинного цикла. Фронт ЕА из 1 в 0 может использоваться для запоминания состояния этих сигналов

30 ЕА

31 WR

32 RD

35 RA

36 SRI

37 SYNC

Строб адреса. Появляется во время первого такта

каждого машинного цикла. Фронт ЕА из 1 в 0

стробирует передачу адреса во внешний регистр

Управление записью на шину данных. Данные фик-

сируются в выбранных устройствах ввода-вывода

или ячейках памяти по фронту из 0 в 1 WR

Управление считыванием с шины данных

Готовность. Указывает на то, что устройство ввода-

вывода или память готовы к приему или передаче

данных

Начальная установка (сброс). Устанавливает в ис-

ходное (нулевое) состояние СК, внутренние триг-

геры разрешения прерываний и подтверждения за-

хвата шин, регистры команд и признаков. Устанав-

ливает внутренние триггеры масок прерываний. Шины

адреса и данных, выводы управления RD, WR и IO/M пе-

реходят во время SRI в состояние высокого импеданса.

МП удерживается в условиях сброса до тех пор, пока

SRI находится в состоянии 0. Переход SRI к 1 разре-

шает работу МП с нулевого адреса

Выход тактового генератора для синхронизации сис-

темы. Период SYNC вдвое больше, чем на входах

CR1,CR2

27

Продолжение табл. 2.2

Номер

вывода

Обозначение

Функциональное назначение

38 HLDA Разрешение прямого доступа. Является ответным сиг-

39 HOLD налом да HOLD. Шины адреса, данных и выводы управ- ления RD, WR и IO/M переходят в состояние высокого импеданса Запрос прямого доступа (захвата шины). МП после по-

40 +5 V лучения запроса на захват завершает текущую передачу по шине, внутренняя обработка может продолжаться. МП вновь получит в свое распоряжение шины адреса и данных лишь тогда, когда HOLD будет снят Напряжение питания

Таблица 2.3. Машинные циклы микропроцессора К1821ВМ85А

Тип машинного цикла Сигналы состояния Сигналы управления

Ю/М S1 so RD WR INTA

Выборка кода операции 0 1 1 0 1 1

Чтение из памяти 0 1 0 0 1 1

Запись в память 0 0 1 1 0 1

Чтение из устройства ввода-вывода 1 1 0 0 1 1

Запись в устройство ввода-вывода 1 0 1 1 0 1

Подтверждение прерывания 1 1 1 1 1 0

Шина свободна:

команда DAD 0 1 0 1 1 1

подтверждение RST, TRAP 1 1 1 1 1 1

останов Z 0 0 Z Z 1

Примечание.

Z - состояние высокого импеданса.

Таблица 2.4.Состояния (такты) машинных циклов микропроцессора К1821ВМ85А

Тип состояния (такта) Сигналы состояния Сигналы адреса-данных Сигналы управления

SI, S 0 Ю/М А8-А15 AD0-AD7 RD, WR INTA ЕА

Л X X X X 1 1 1*

X X X X X X 0

^ож X X X X X X 0

т3 X X X X X X 0

т4 1 Q** X Z 1 1 0

TS 1 0** X Z 1 1 0

28

Продолжение табл. 2.4

Тип состояния (такта) Сигналы состояния Сигналы адреса-данн ых Сигналы управления

si, so Ю/М А8-А15 AD0-AD7 RD, WR INTA ЕА

Т6 1 0** X Z 110 ^сброса X Z Z Z Z 1 0 ^останова 0 Z Z Z Z 1 0 Тзахв X Z Z Z Z 1 0 Примечание. X - состояние не определено. * Сигнал ЕА не вырабатывается в течение второго и третьего машинных цик- лов команда DAD. * * Сигнал Ю/М = 1 в течение Т4-Т6 машинного цикла "Подтверждение пре- рывания (по INTR)".

Микропроцессор имеет пять входов для приема сигналов запроса пре-

рывания: TRAP, RST7.5, RST6.5, RST5.5 и INTR (расположены в поряд-

ке снижения их приоритета). Векторы прерываний по этим входам рас-

положены в памяти соответственно по адресам: 24Н, ЗСН, 34Н, 2СН (ад-

рес по INTR зависит от источника прерывания). При поступлении запросов

прерывания на входы RST7.5—RST5.5 нет необходимости обеспечивать

подачу адресов рестарта (команды повторного запуска RST) на шину

данных - МП определяет их автоматически. Векторы рестарта по входам

RST7.5—RST5.5 расположены в памяти соответственно по адресам 38Н,

ЗОН, 28Н.

Сигнал INTR имеет такое же назначение, как и сигнал INT у

К580ВМ80А. Каждый из трех RST может программно маскироваться.

Прерывание по входу TRAP не может быть маскировано, т.е. запросы на

прерывание, подаваемые на вход TRAP, никогда не могут быть запреще-

ны программно. Среди маскируемых прерываний есть прерывания двух

различных типов. Входы сигналов прерываний RST5.5 и RST6.5 являют-

ся, подобно входам INTR К1821ВМ85А и входу INT К580ВМ80А, чувст-

вительными к уровню сигнала. Вход RST7.5 является чувствительным к

фронту (из 0 в 1) сигнала. Чтобы установить триггер, генерирующий

внутренний запрос на прерывание, достаточно подать импульс на вход

RST7.5. Триггер остается установленным до тех пор, пока прерывание

не будет обработано. После завершения обработки прерывания, а также

по команде SIM или сигналу начальной установки SRI этот триггер сбра-

сывается. Внутренний триггер запроса прерывания RST7.5 может быть

установлен подачей импульса даже тогда, когда прерывание RST7.5Mac-

кировано. Состояние масок прерываний типа RST может быть изменено

только командой SIM, которой нет в системе команд К580ВМ80А, и сиг-

налом SRI. Вход TRAP является чувствительным и по фронту сигнала, и

по его уровню. Сигнал TRAP должен вырасти до определенного уровня и

оставаться на этом высоком уровне вплоть до выработки сигнала под-

29

тверждения прерывания. Следующее прерывание на входе TRAP может

быть зарегистрировано только тогда, когда уровень сигнала на нем изме-

нится от 0 до 1. Таким образом, устраняются ложные срабатывания, ко-

торые могли бы возникнуть из-за различных помех.

Во время обработки прерываний TRAP, RST, INTR до тех пор, пока не

будет выполнена команда EL запрещены все прерывания, кроме TRAP.

Прерывание TRAP носит особый характер в том смысле, что блокирует

прерывания, но сохраняет состояние разрешения поступившего уже сиг-

нала прерывания. Выполнение первой после TRAP команды RIM позво-

ляет определить состояние маски прерываний независимо от того, были

ли разрешены или запрещены прерывания до TRAP. Все последующие

команды RIM дают текущее состояние маски прерываний. Выполнение

RIM после прерываний по входам RST и INTR также будет информиро-

вать о текущем состоянии маски прерываний, обнаруживая, что преры-

вания заблокированы.

Система команд К1821ВМ85А, приведенная в табл. 2.1, идентична сис-

теме команд К580ВМ80А и имеет две дополнительные команды: уста-

новки маски прерывания SIM и чтения маски прерывания RIM.

2.2. Восьми-шестнадцатиразрядный микропроцессорный

комплект серии К1810

Состав МП-комплекта

Микропроцессорный комплект серии К1810 [14-16] включает в свой

состав следующие БИС:

К1810ВМ86 — однокристальный 16-разрядный микропроцессор с

быстродействием до 2,5 млн. операций/с, емкостью адресуемой памяти

1 Мбайт и системой команд, совместимой с К580ВМ80А на ассемблере;

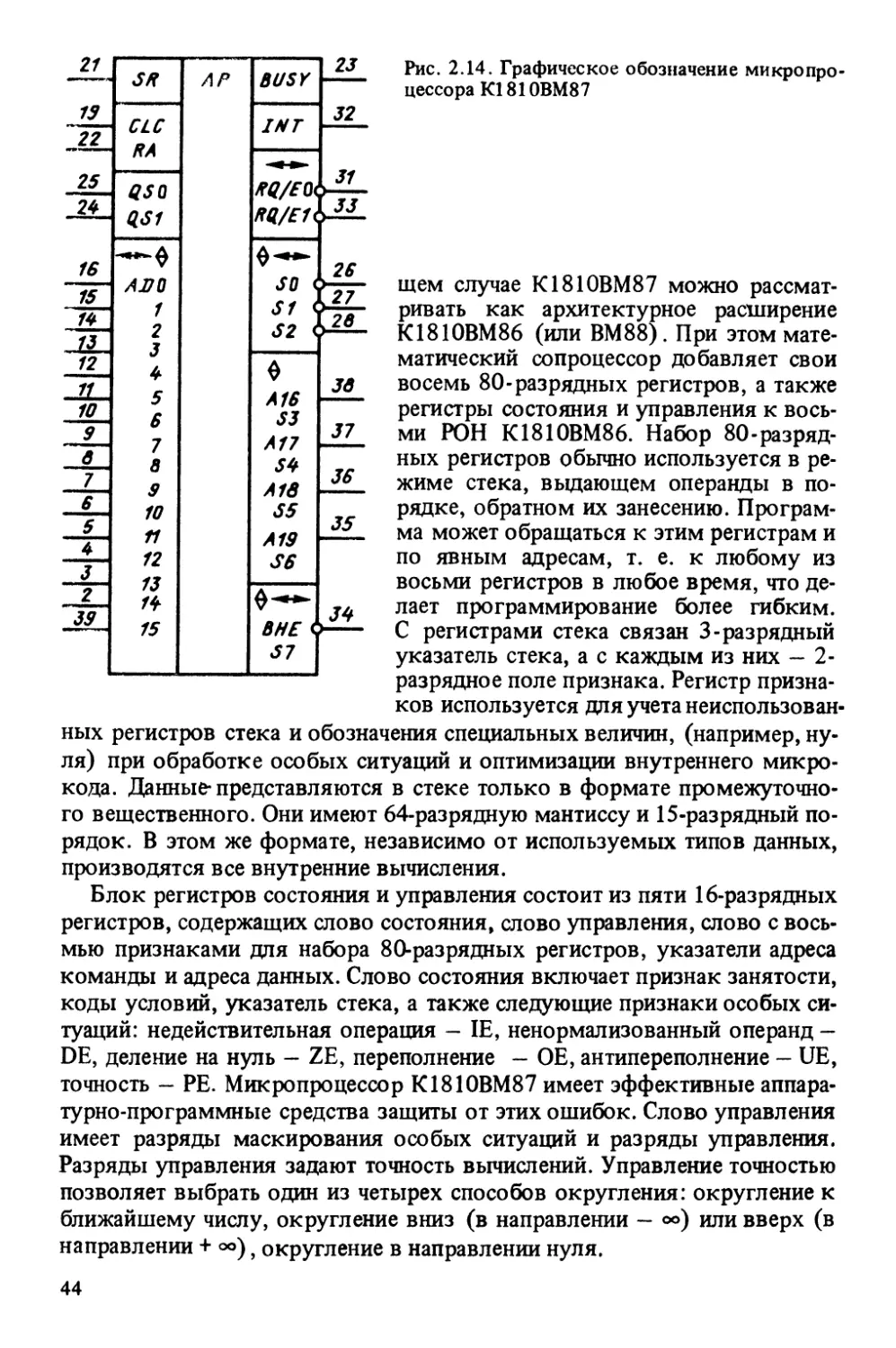

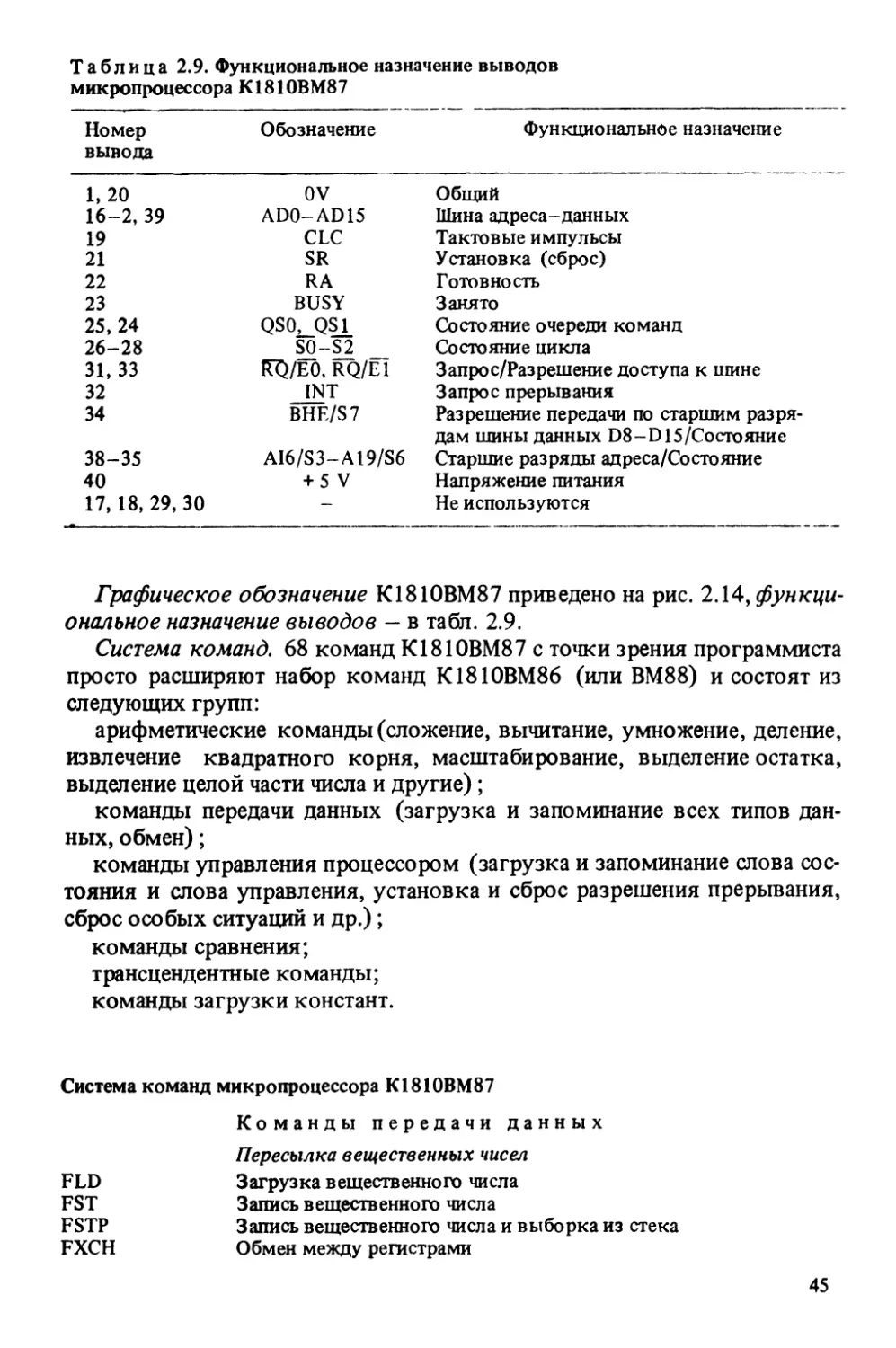

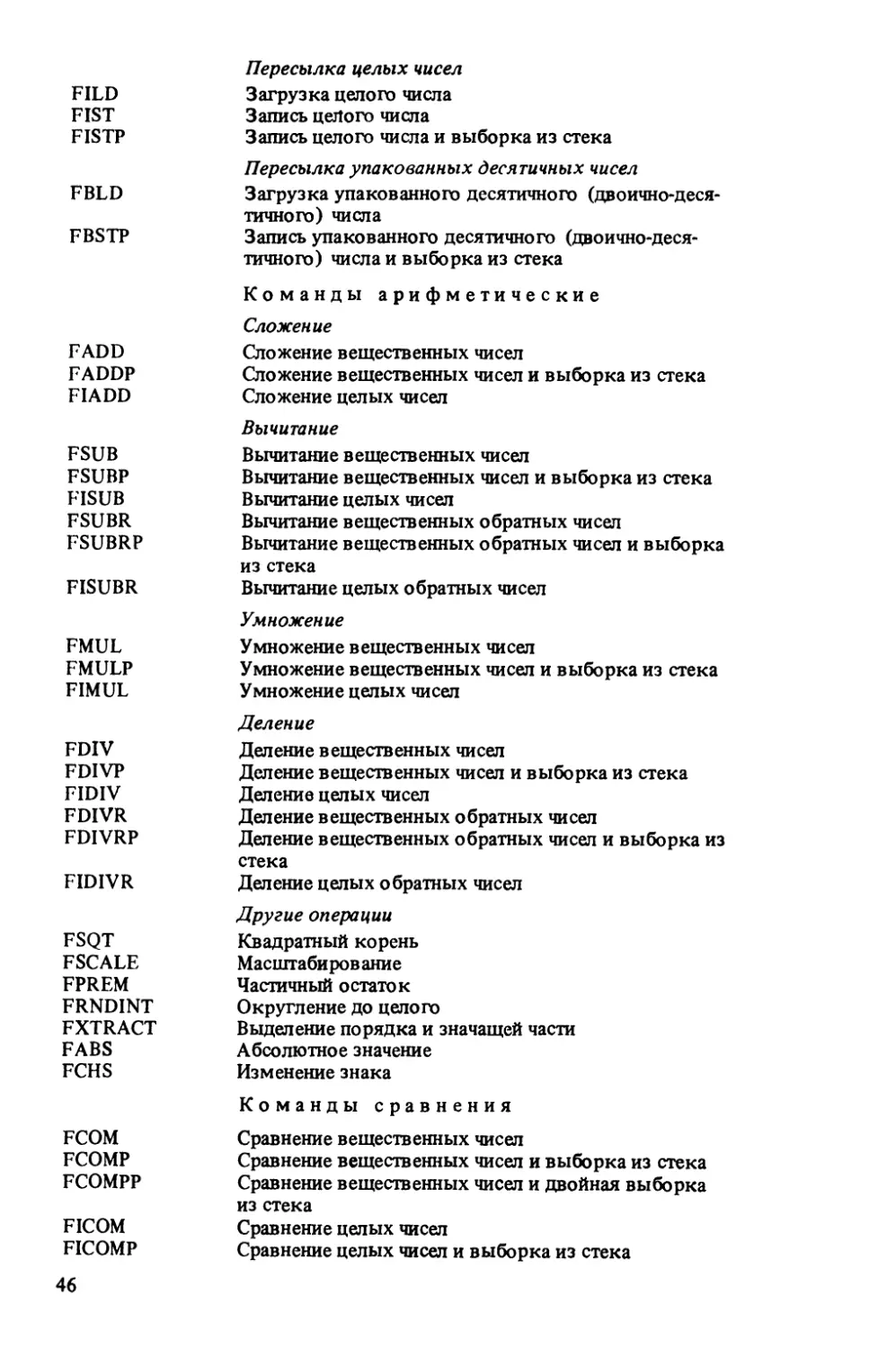

К1810ВМ87 - однокристальный 16-разрядный сопроцессор арифмети-

ки с плавающей запятой;

К1810ВМ88 - однокристальный 8-разрядный микропроцессор с быст-

родействием примерно в 2 раза большим, чем у К1821ВМ85А, и в пять

раз, чем у К580ВМ80А; емкостью адресуемой памяти 1 Мбайт и систе-

мой команд, идентичной К1810ВМ86;

К1810ВМ89 - однокристальный 16-разрядный сопроцессор ввода-вы-

вода;

К1810ГФ84 - генератор тактовых сигналов;

К1810ВН59А - программируемый контроллер прерываний;

К1810ВГ88 - системный контроллер;

К1810ВБ89 - арбитр шины;

К1810ВА86 - шинные формирователи;

К1810ВА87 — шинные формирователи (выходы с инверсией) ;

К1810ИР82 - буферные регистры;

К1810ИР83 - буферные регистры (выходы с инверсией).

30

БИС МП комплекта серии К1810 могут использоваться совместно с

контроллером клавиатуры и индикации К580ВВ79, интерфейсными БИС

системы микропроцессор — канал общего пользования К580ВК91Аи

К580ВГ92, а также другими БИС МП-комплекта серии К580.

Микропроцессор К1810ВМ86

16-разрядный МП, наряду с аппаратурной и программной совместимо-

стью с БИС серии К580, обеспечивает возможность эффективной работы

с языками высокого уровня, имеет гибкую и мощную систему команд.

Микропроцессор К1810ВМ86 может быть использован как 16- или 8-раз-

рядный. МП выполняет операции над битами, байтами, двухбайтовыми

словами, действия знаковой и беззнаковой двоичной или десятичной

арифметики, в том числе умножение и деление, имеет гибкую структуру

аппаратурных и программных прерываний (до 256 типов).

К наиболее важным аппаратурным особенностям К1810ВМ86 отно-

сятся: развитая регистровая структура, существенно уменьшающая чис-

ло обращений к памяти; конвейерный принцип выполнения команд с

предварительной выборкой, обеспечивающий максимальную пропуск-

ную способность системной магистрали; распределенное микропрограм-

мное устройство управления; мультиплексированная шина адреса—дан-

ных; многофункциональное использование выводов, позволяющее адап-

тировать МП к уровню сложности разрабатываемой системы; способ-

ность координировать взаимодействие нескольких процессоров, упро-

щающая построение на его базе мультипроцессорных систем. В этих сис-

темах возможно применение процессоров двух типов: независимых, т.е.

выполняющих собственный поток команд (К1810ВМ86), и вспомога-

тельных - сопроцессоров (например, К1810ВМ87, К1810ВМ89). Сопро-

цессор анализирует команды, выбираемые главным (независимым) про-

цессором и выполняет те, на которые распространяется его специа-

лизация.

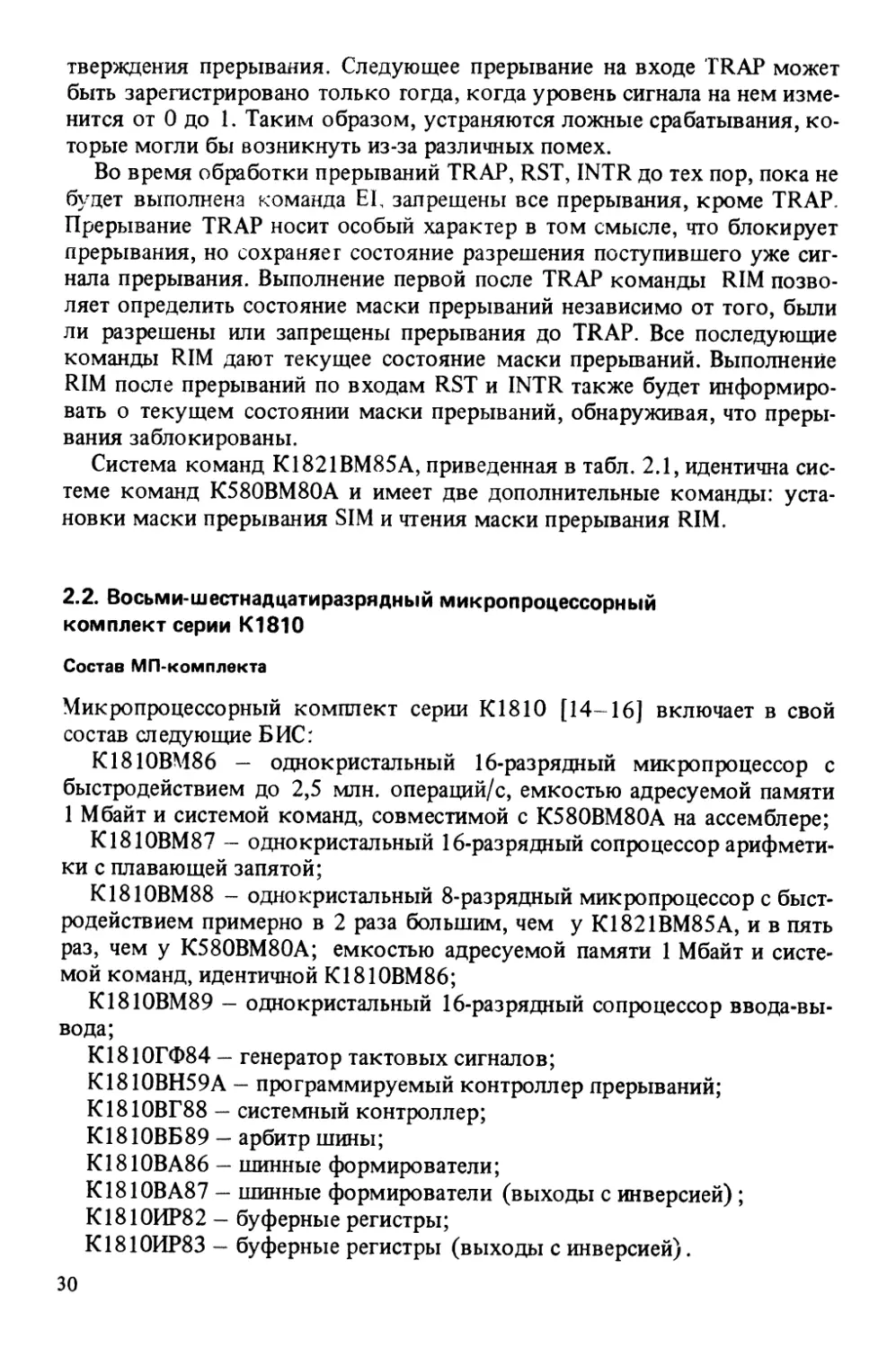

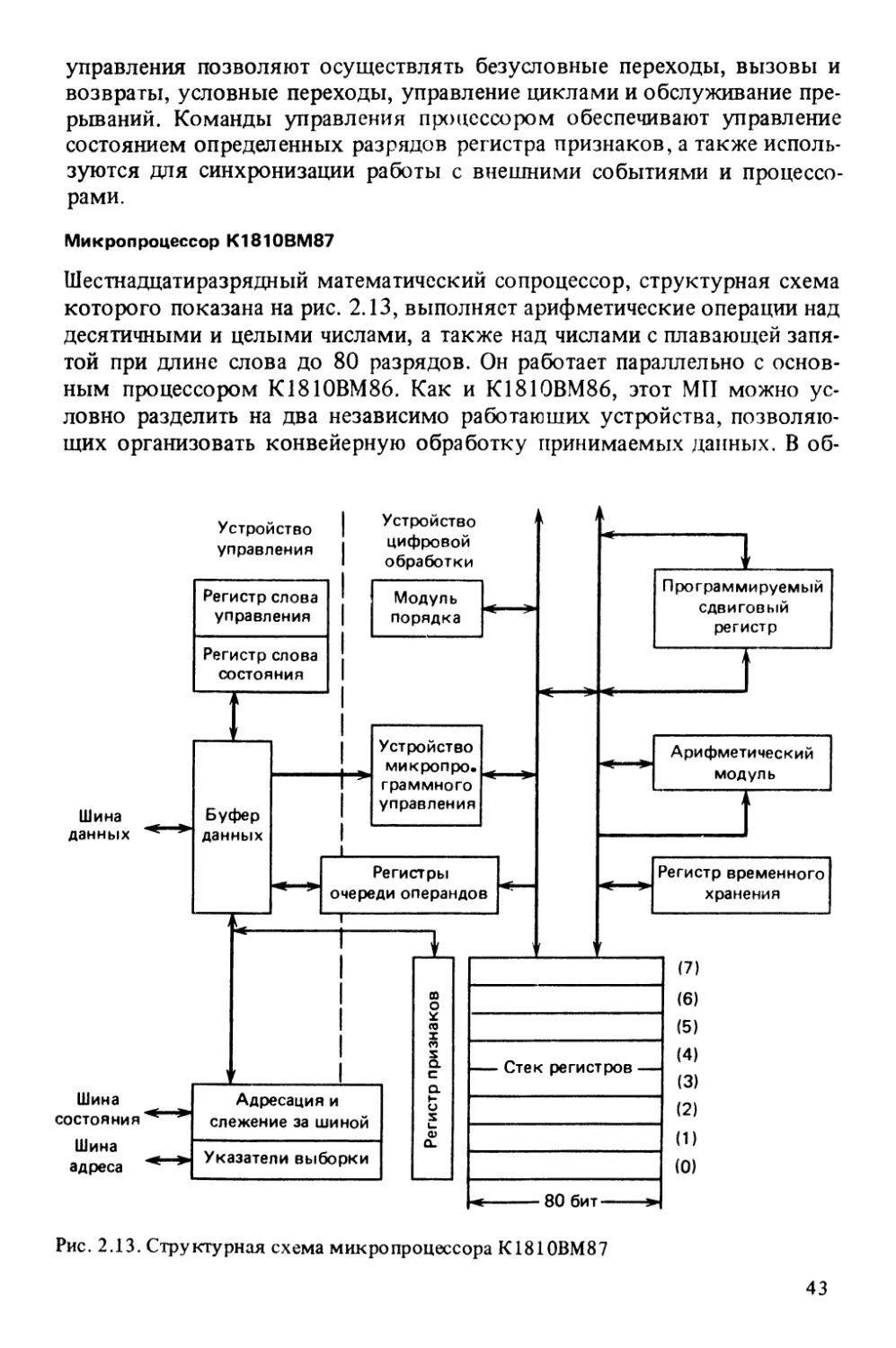

Структура К1810ВМ86 (рис. 2.9), ориентированная на параллельное

выполнение функций выборки и выполнения команд, может быть услов-

но разделена на две части, работающие асинхронно: устройство сопряже-

ния с магистралью (УС) и устройство обработки (УО).

Устройство сопряжения с магистралью обеспечивает возможность

формирования 20-разрядного физического адреса памяти, выборки ко-

манд и операндов из памяти, организации очередности команд и запоми-

нания результатов выполнения команд в памяти. В состав УС входит

шесть 8-разрядных регистров очереди команд, четыре 16-разрядных сег-

ментных регистра, 16-разрядный регистр адреса команд, 16-разряд-

ный регистр обмена и 16-разрядный сумматор адреса.

Устройство сопряжения готово выполнить цикл выборки слова из па-

мяти всякий раз, когда в очереди освобождаются, по меньшей мере, два

байта, УО извлекает из нее коды команд по мере необходимости. Оче-

31

Рис. 2.9. Структурная схема микропроцессора К1810ВМ86

редь организована по принципу ’’первым пришел - первого обслужили”,

а шесть ее уровней позволяют удовлетворять запросы У О в кодах ко-

манд достаточно эффективно, сокращая тем самым до минимума затра-

ты времени МП на ожидание выборки команд из памяти. Выполнение ко-

манд происходит в логической последовательности, предписанной прог-

раммой, поскольку в очереди находятся те команды, которые хранились

в ячейках памяти, непосредственно следующих за текущей командой.

При передаче управления в другую ячейку памяти ход выполнения прог-

раммы нарушается. Устройство сопряжения очищает регистры очереди,

выбирает команду по адресу перехода, передает ее УО и начинает новое

заполнение этих регистров. При возврате из подпрограммы или из пре-

рывания происходит восстановление очереди команд, адреса которых ав-

томатически вычисляются в сумматоре адреса. Если МП необходимо вы-

32

полнить цикл чтения или записи, то выборка команд приостанавливает-

ся на время цикла.

Сегментные регистры соответствуют четырем сегментам памяти: дан-

ных — DS, стека - SS, кода - CS и промежуточных данных - ES. В каж-

дом из этих регистров хранятся 16 старших разрядов кода адреса соот-

ветствующего сегмента памяти. 20-разрядный физический адрес, позво-

ляющий работать с памятью емкостью до 1 Мбайт, образуется в сумма-

торе адреса путем сдвига базового адреса сегмента на четыре разряда

влево и сложения его с 16-разрядным адресом смещения. Адрес смеще-

ния находится в одном из регистров указателей или индексов УО и по-

зволяет адресовать байты или слова в пределах 64 Кбайт выбранного

сегмента. Если полученное в сумматоре адреса значение превышает зна-

чение самого старшего адреса сегмента, то физический адрес вновь отсчи-

тывается от начала сегмента до значения превышения. При вычисле-

нии физического адреса операнда в качестве базового адреса исполь-

зуется содержимое регистров сегмента данных и сегмента проме-

жуточных данных, а при вычислении физического адреса команды-со-

держимое регистра сегмента кода. Регистр адреса команд (указатель ко-

манд) IP соответствует счетчику команд микропроцессора К580ВМ80А

и указывает следующую команду, которая будет выполняться после те-

кущей команды. Устройство сопряжения записывает в него из УО смеще-

ние следующей команды от начала текущего сегмента кода. Если содер-

жимое регистра адреса команд засылается в стек, то происходит автома-

тическая настройка его на адрес следующей команды.

Устройство обработки предназначено для выполнения операций по

обработке данных и состоит из устройства микропрограммного управле-

ния (УМУ), 16-разрядного арифметическо-логического устройства

(АЛУ), восьми 16-разрядных регистров общего назначения (РОН) и ре-

гистра признаков. Команды, выбранные УС из памяти и записанные в ре-

гистры очереди команд, по запросам от У О поступают в УМУ. Это устрой-

ство, содержащее память микрокоманд, декодирует команды и выраба-

тывает последовательность микрокоманд, управляющую процессом об-

работки. В АЛУ выполняются арифметические и логические операции

над 8- и 16-разрядными числами с фиксированной запятой. Для ускоре-

ния внутренних пересылок данных все регистры и магистрали данных в

УО имеют 16 разрядов, УО не имеет прямой связи с внешней системной

магистралью и обменивается данными с УС через регистр обмена.

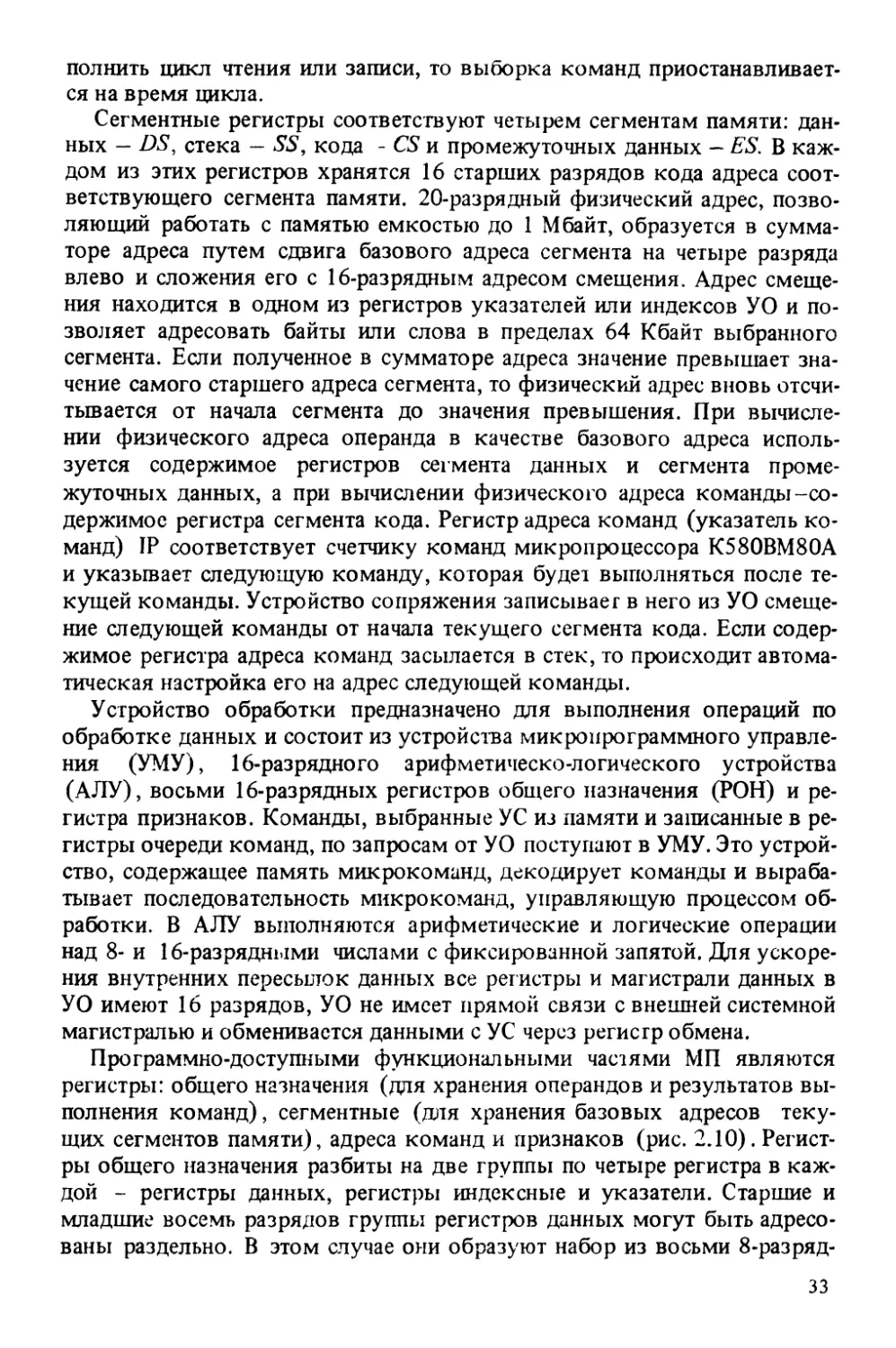

Программно-доступными функциональными час1ями МП являются

регистры: общего назначения (для хранения операндов и результатов вы-

полнения команд), сегментные (для хранения базовых адресов теку-

щих сегментов памяти), адреса команд и признаков (рис. 2.10). Регист-

ры общего назначения разбиты на две группы по четыре регистра в каж-

дой - регистры данных, регистры индексные и указатели. Старшие и

младшие восемь разрядов группы регистров данных могут быть адресо-

ваны раздельно. В этом случае они образуют набор из восьми 8-разряд-

33

Регистры

данных

Регистры

индексные

и

указатели

Сегментные

регистры

Регистры

общего \

назначения

Регистр признаков

Признаки:

Переноса

Четности

Вспомогательного переноса

Нуля

Знака

Пошагового режима

Разрешения прерывания

Направления

Переполнения

Рис. 2.10 Программно-доступные регистры микропроцессора К1810ВМ86

ных регистров. Регистры данных можно использовать без ограничения в

большинстве арифметических и логических операций. Другая группа ре-

гистров, включающая в себя два указателя (базы и стека) и два индекс-

ных регистра (источника и прйемника), также может участвовать в боль-

шинстве арифметических и логических операций. Кроме того, в некото-

рых командах предполагается неявное использование РОН по следующе-

34

му назначению: умножение, деление и ввод-вывод слов (АХ); умноже-

ние, деление и ввод-вывод байтов, перекодировка, десятичная арифмети-

ка (A L); умножение и деление байтов (АН); перекодировка (ВХ) ; опе-

рации со строками, циклы (СХ); сдвиги и циклические сдвиги на раз-

личное число разрядов (CL); умножение и деление слов, неявный

ввод-вывод (DX); операции со стеком (SP); операции со строками (SI,

DI).

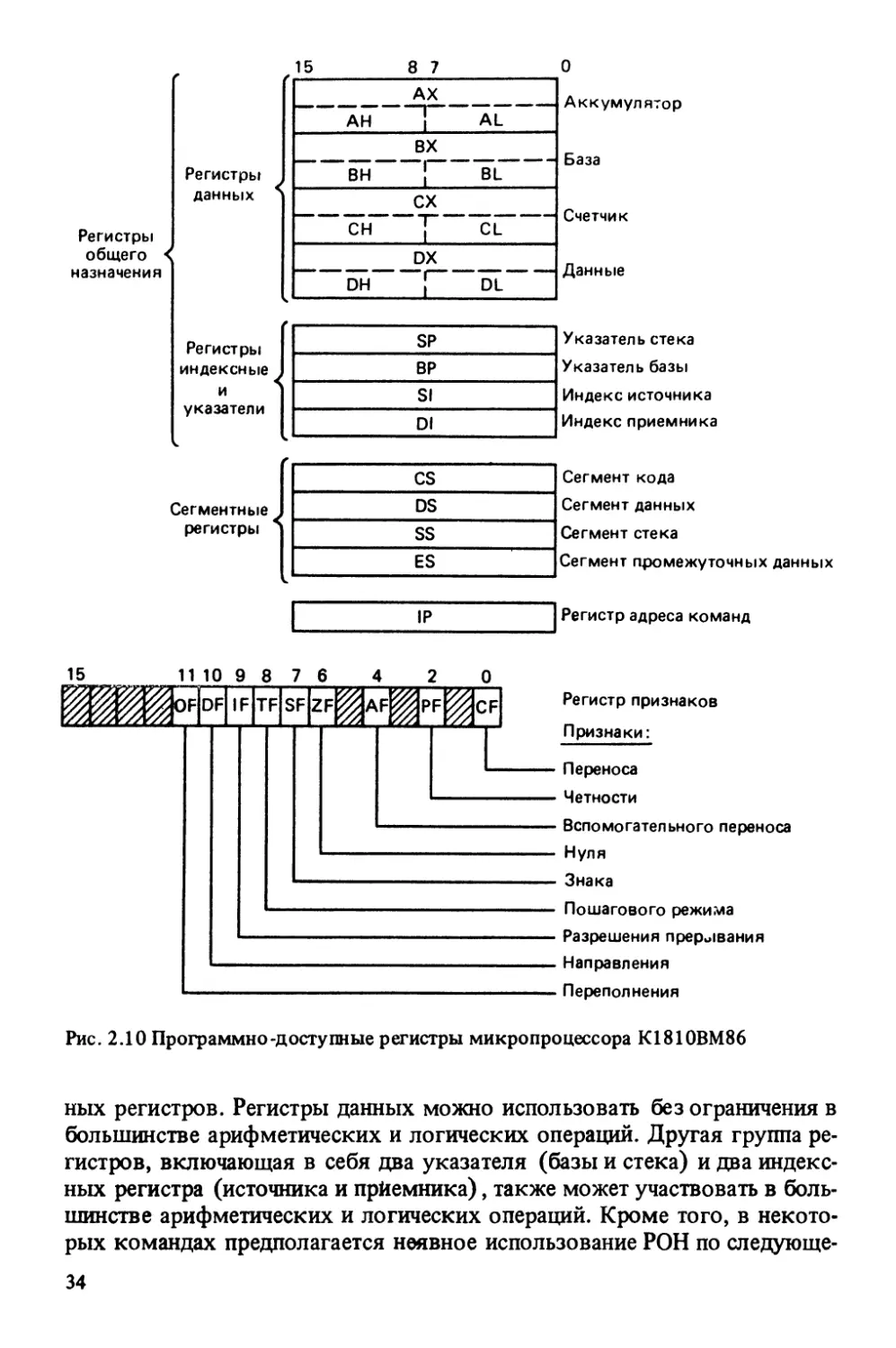

В регистре признаков используются только девять разрядов. Шесть из

них служат для регистрации особенностей результата арифметических и

логических операций. Микропроцессор имеет группу команд, которые

позволяют изменить порядок выполнения программы в зависимости от

состояния этих шести разрядов, т.е. от результата предыдущей операции.

Признак вспомогательного переноса AF, используется командами деся-

тичной арифметики. При переносе из третьего разряда в четвертый либо

заеме из четвертого разряда в третий младшего байта 16-разрядного чис-

ла AF устанавливается в 1. Признак переноса CF используется команда-

ми сложения и вычитания многобайтовых чисел. При переносе или заеме

из старшего разряда результата CF устанавливается в 1. Команды цикли-

ческого сдвига могут изолировать сдвигаемый разряд в памяти или ре-

гистре путем размещения его в разряде признака переноса.

Команда INTO вырабатывает программное прерывание при наличии

признака переполнения OF. Если OF равен 1, значит, произошло арифме-

тическое переполнение (т.е. утеряна значащая цифра) и разрядность ре-

зультата превышает разрядность приемника результата. В МП двоичные

отрицательные числа представляются в дополнительном коде. Состояние

О или 1 признака знака SF говорит о том, что результат соответственно

положительный или отрицательный. Признак четности PF используется

для обнаружения сбоев при передаче данных (1 говорит о четности ре-

зультата). Если признак нуля ZF равен 1, значит, результат опрации ра-

вен нулю.

В регистре признаков имеется еще три разряда, которые можно ис-

пользовать для управления действиями МП путем записи в них 0 или 1.

Запись 1 в разряд приз’нака направления DF вызывает автодекремент

при выполнении операций со строками данных. Это значит, что строки

обрабатываются от старших адресов к младшим (справа налево). Запись

О в DF вызывает автоинкремент, т.е. обработку строк слева направо.

Если признак разрешения прерывания IF равен 1, то МП реагирует на

внешние маскируемые запросы прерывания. Запись 0 в IF запрещает эти

прерывания. При этом IF не влияет на внутренние и немаскируемые пре-

рывания. Для перевода МП в пошаговый режим выполнения программы

необходимо записать 1 в разряд признака пошагового режима TF. В

этом режиме после выполнения каждой команды МП автоматически ге-

нерирует прерывание.

Графическое обозначение микропроцессора К1810ВМ86 приведено на

рис. 2.11, функциональное назначение выводов - в табл. 2.5.

35

33

21

19

23

UJn 22

(RO/EQ) ~

17

16

16

15

14

13

12

11

10

9

6

7

6

5

4

3

2

39

MN > MX SR CLC > Т RA HOLD NMI INTR AEO 1 2 3 4 5 6 7 6 9 10 11 12 13 14 15 CPU

0

WR

RE

EA

INTA

$

EE

IV

OD

10

M

T“

A16

S3

A17

64

A16

65

A19

66

$BHE'

67

30

25

24

26

27

26

36

37

36

35

34

(LOCH)

(R0/E1)

(060)

(061)

(60)

(SI)

(52)

Рис. 2.11. Графическое обо-

значение микропроцессора

К1810ВМ86

Функционирование

K1810BM86. Для запус-

ка или установки МП в

исходное состояние ис-

пользуют вход SR, сигна-

лы на который поступа-

ют от К1810ГФ84. При

запуске МП сигнал на

входе SR должен остава-

ться в состоянии 1 еще

50 мкс после достиже-

ния напряжением пита-

ния номинального зна-

чения. При установке

МП в исходное состоя-

ние в процессе работы

(перезапуск) длитель-

ность сигнала SR должна

быть не менее четырех

периодов тактовой час-

тоты. Микропроцессор

прекращает выполнение

внутренних операций, пе-

HL UA

реводит шины адреса - данных и управления в высокоимпедансное со-

стояние. После перехода в 0 сигнала SR микропроцессор в течение вось-

ми тактов выполняет установку в исходное состояние внутренних реги-

стров. Поскольку содержимое регистра сегмента кода CS становится рав-

ным FFFFH, а регистра адреса команд 0000Н, первую команду МП выби-

рает из ячейки памяти с адресом FFFF0H. Обычно эта ячейка содержит ко-

манду безусловного перехода JMP на действительное начало системной

программы.

Выбор режима функционирования предлагает пользователю возмож-

ность выбора состава выходных управляющих сигналов в соответствии

со степенью сложности проектируемой МП-системы. Функциональное на-

значение выводов МП для минимального и максимального режимов дано

в табл. 2.5. В минимальном режиме (вывод MN/MX подключен к шине пи-

тания), ориентированном на малые вычислительные системы (одно- и

двухплатные), МП выдает сигналы управления обменом с памятью и

внешними устройствами, а также обеспечивает доступ к системной ма-

гистрали по запросу прямого доступа к памяти, используя сигналы

HOLD и HLDA. Если вывод MN/MX подключен к шине ’’Корпус”, то МП

36

Таблица 2.5. Функциональное назначение выводов микропроцессора К1810ВМ86

Номер вывода Обозначение Функциональное назначение

1, 20 0V Общий

16-2, 39 AD0-AD15 Шина адреса-данных

17 NMI Немаскируемый запрос прерывания

18 INTR Маскируемый запрос прерывания

19 CLC Тактовые импульсы

21 SR Установка (сброс)

22 RA Готовность

23 Т Проверка. Состояние входного сигнала опрашиваем ся по команде WAIT

32 RD Чтение

33 MN/MX Минимальный/Максимальный режим

34 BHE/S7 Разрешение передачи по старшим разрядам шины данных О8-О15/Состояние

38-35 A16/S3-A19/S6 Старшие разряды адреса/Состояние

40 + 5V Напряжение питания Минимальный режим

24 INTA Подтверждение прерывания

25 ЕА Строб адреса

26 _ ED Разрешение обмена данными

27 ID/OD Ввод данных/Вывод данных

28 Ю/М Внешнее устройство/Память

29 WR Запись

30 HLDA Разрешение прямого доступа

31 HOLD Запрос прямого доступа (захвата шины) Максимальный режим

25,24 QSO, QS1 Состояние очереди команд

26-28 S0-S2 Тип цикла обмена

29 _ LOCK Канал занят. Выдается по команде LOCK

31,30 RQ/EO,RQ/E1 Запрос/Разрешение доступа к шине

находится в максимальном режиме и может работать в сложных одно- и

многопроцессорных системах. При работе в этом режиме изменяются

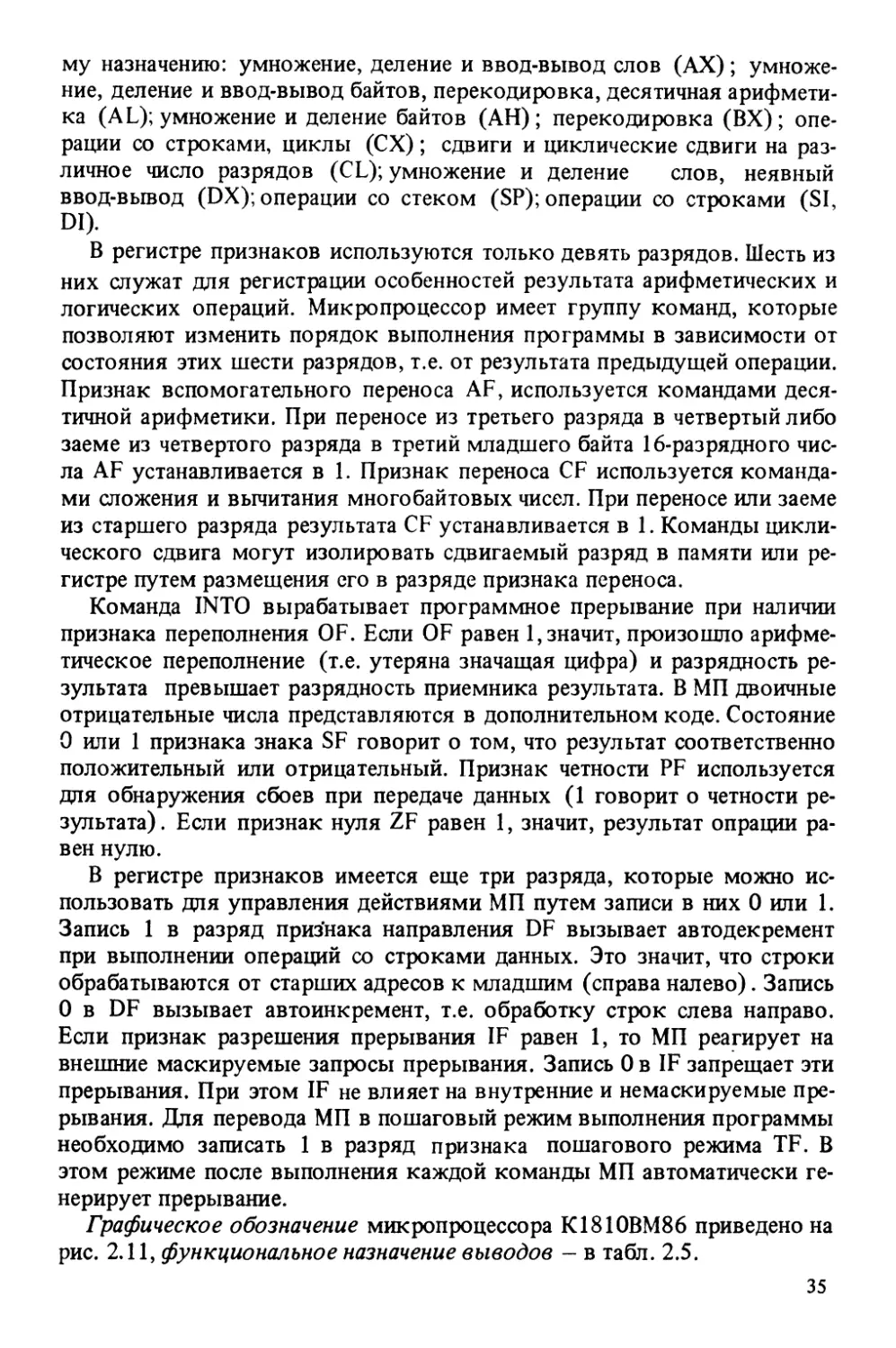

функции ряда выводов МП. Восемь сигналов состояния, которые выдает

МП, могут быть использованы внешними устройствами. Сигналы SO-S2

определяют тип цикла обмена по шине адреса—данных (табл.2.6). Эти

сигналы состояния МП декодируются системным контроллером

К1810ВГ88, и он выдает расширенный набор сигналов управления обме-

ном. Сигналы S3, S4 определяют, какой сегментный регистр использует-

ся в текущем цикле обмена для вычисления физического адреса ячейки

памяти (табл. 2.7). Сигнал S5 определяет состояние триггера разрешения

прерывания регистра признаков, S6 всегда находится в состоянии 0, a S7

является вспомогательным сигналом и его состояние в процессе работы

МП не определено. В максимальном режиме МП выдает также сигналы QSO

и QS1 состояния очереди команд (табл. 2.8.), предназначенные для того,

37

Таблица 2.6. Функциональное назна-

чение выводов ЗЮ-S2 микропроцессора

К1810ВМ86

Сигналы Тип цикла

состояния обмена Таблица 2.7. Функциональное назна-

-----— — — чение выводов S3, S4 микропроцессора

S2 SI-------------------------------SO К1810ВМ86

0 0 0 0 0 1 Подтверждение прерывания Чтение из устройст- ва ввода-вывода Сигналы состояния Используемый сегментный регистр

S4 S3

0 1 0 Запись в устройст-

0 0 ES

во ввода-вывода

0 1 1 Останов 0 1 SS

1 0 0 Выборка команды 1 0 CS или никакой

1 0 1 Чтение из памяти (при вводе-выводе

1 1 0 Запись в память или прерывании)

1 1 1 Пассивный 1 1 DS

чтобы внешние процессоры могли принимать от МП команды и операнды

с помощью команды ESC. Сигналы, полученные в текущем такте, описы-

вают состояние очереди в предыдущем такте. Отслеживание состояния

очереди команд позволяет обрабатывать расширение системы команд с

помощью сопроцессора.

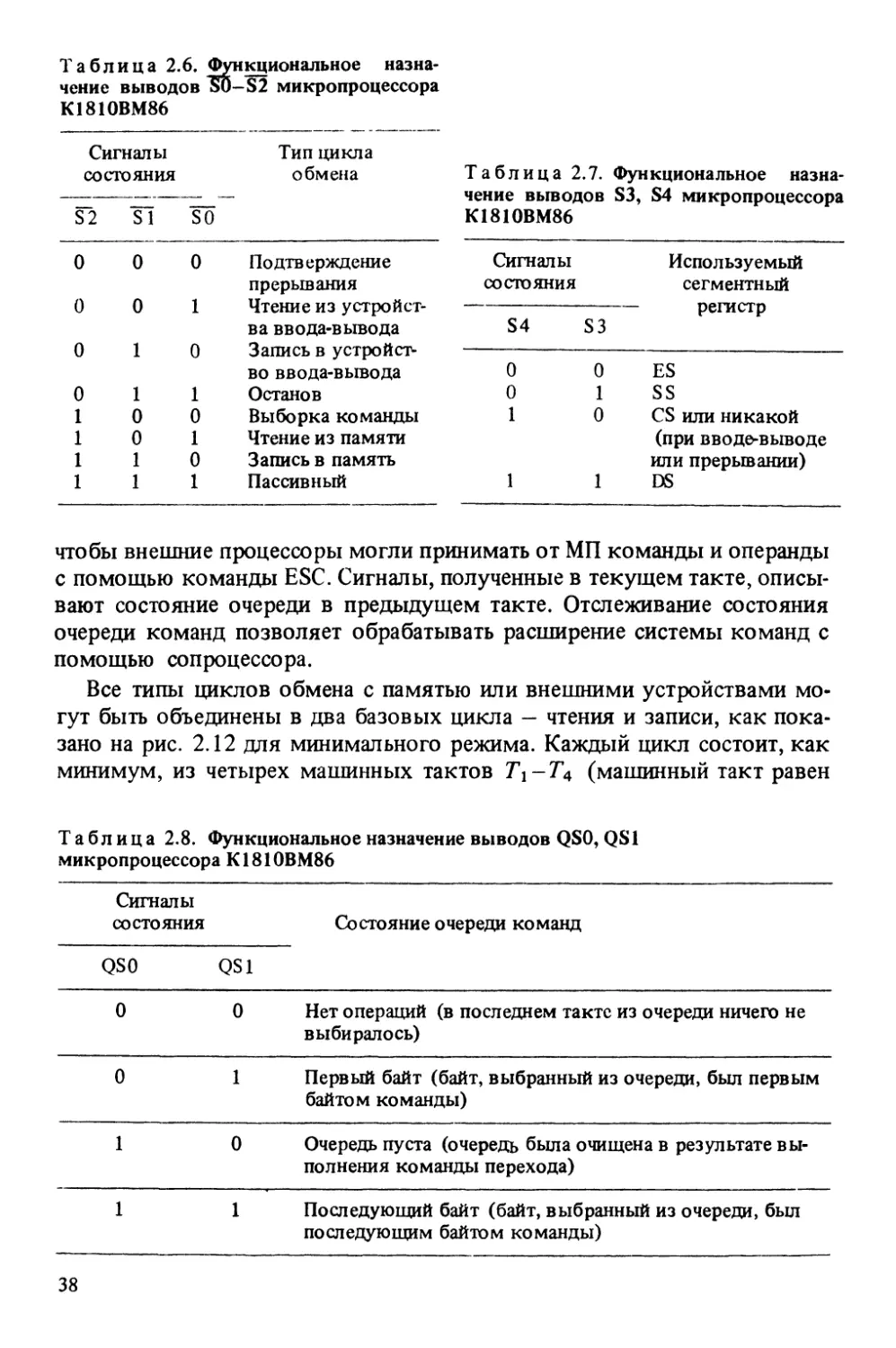

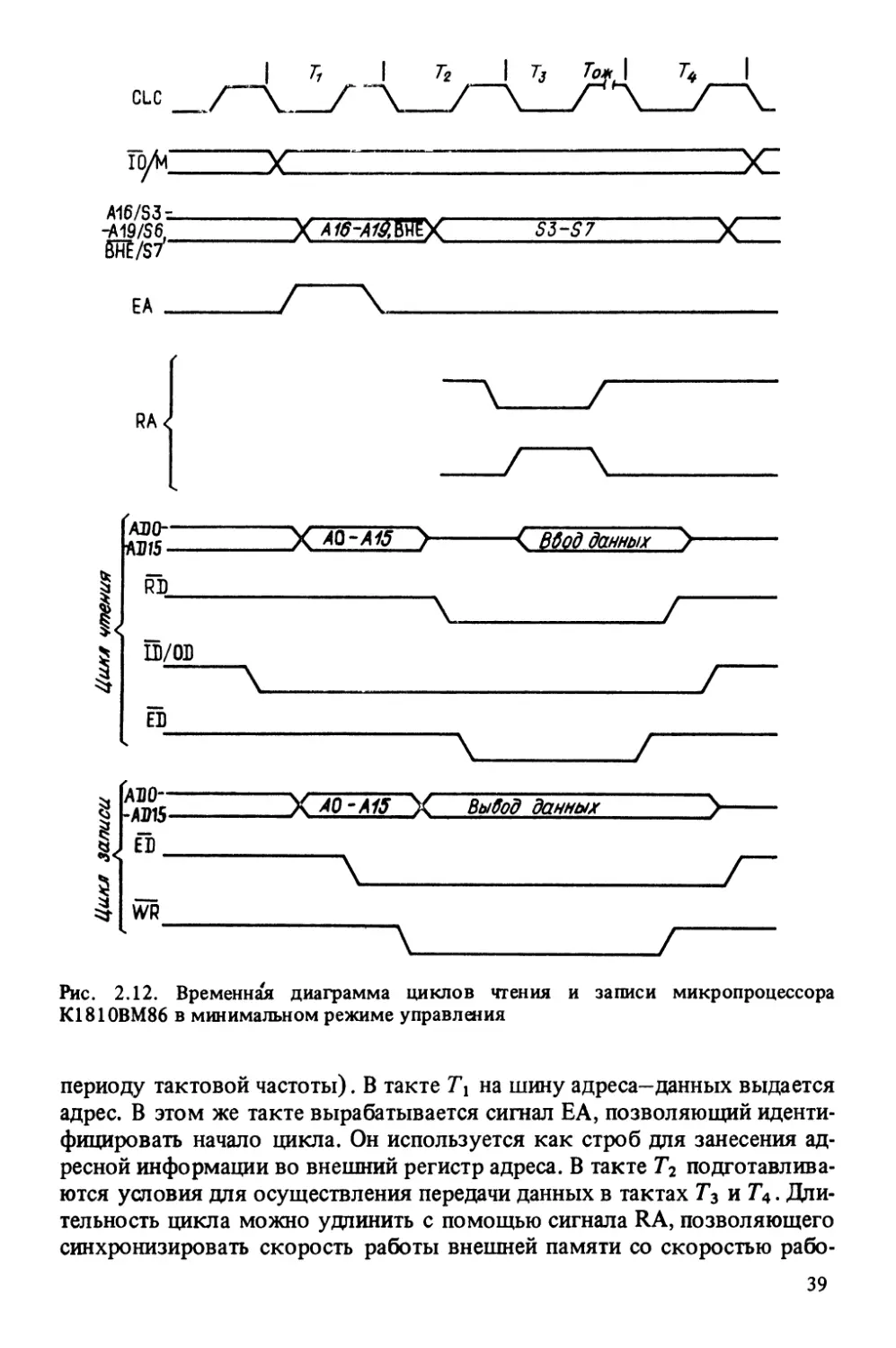

Все типы циклов обмена с памятью или внешними устройствами мо-

гут быть объединены в два базовых цикла - чтения и записи, как пока-

зано на рис. 2.12 для минимального режима. Каждый цикл состоит, как

минимум, из четырех машинных тактов Тх-Тл (машинный такт равен

Таблица 2.8. Функциональное назначение выводов QSO, QS1

микропроцессора K1810BM86

Сигналы состояния QS0 QS1 Состояние очереди команд

0 0 Нет операций (в последнем такте из очереди ничего не выбиралось)

0 1 Первый байт (байт, выбранный из очереди, был первым байтом команды)

1 0 Очередь пуста (очередь была очищена в результате вы- полнения команды перехода)

1 1 Последующий байт (байт, выбранный из очереди, был последующим байтом команды)

38

УСА0-А15 >

Вбод данных >

RD

ID/ОБ

ED

$ _

§<{ED

i _

WR

X ЛО-Л/5 У Выбод данных

Рис. 2.12. Временная диаграмма циклов чтения и записи микропроцессора

К1810ВМ86 в минимальном режиме управления

периоду тактовой частоты). В такте Т! на шину адреса—данных выдается

адрес. В этом же такте вырабатывается сигнал ЕА, позволяющий иденти-

фицировать начало цикла. Он используется как строб для занесения ад-

ресной информации во внешний регистр адреса. В такте Г2 подготавлива-

ются условия для осуществления передачи данных в тактах Т3 и Г4. Дли-

тельность цикла можно удлинить с помощью сигнала RA, позволяющего

синхронизировать скорость работы внешней памяти со скоростью рабо-

39

ты МП. По низкому уровню этого сигнала между тактами Т3 и Г4 вво-

дятся дополнительные та^сты ожидания. В течение тактов ожидания дан-

ные остаются неизменными. Между тактом Г4 текущего цикла и тактом

7\ следующего цикла МП может вводить дополнительные (’’холостые”)

такты, предназначенные для выполнения внутренних действий. Момен-

ты введения этих тактов и их число зависят от состояния очереди ко-

манд и выполняемой команды.

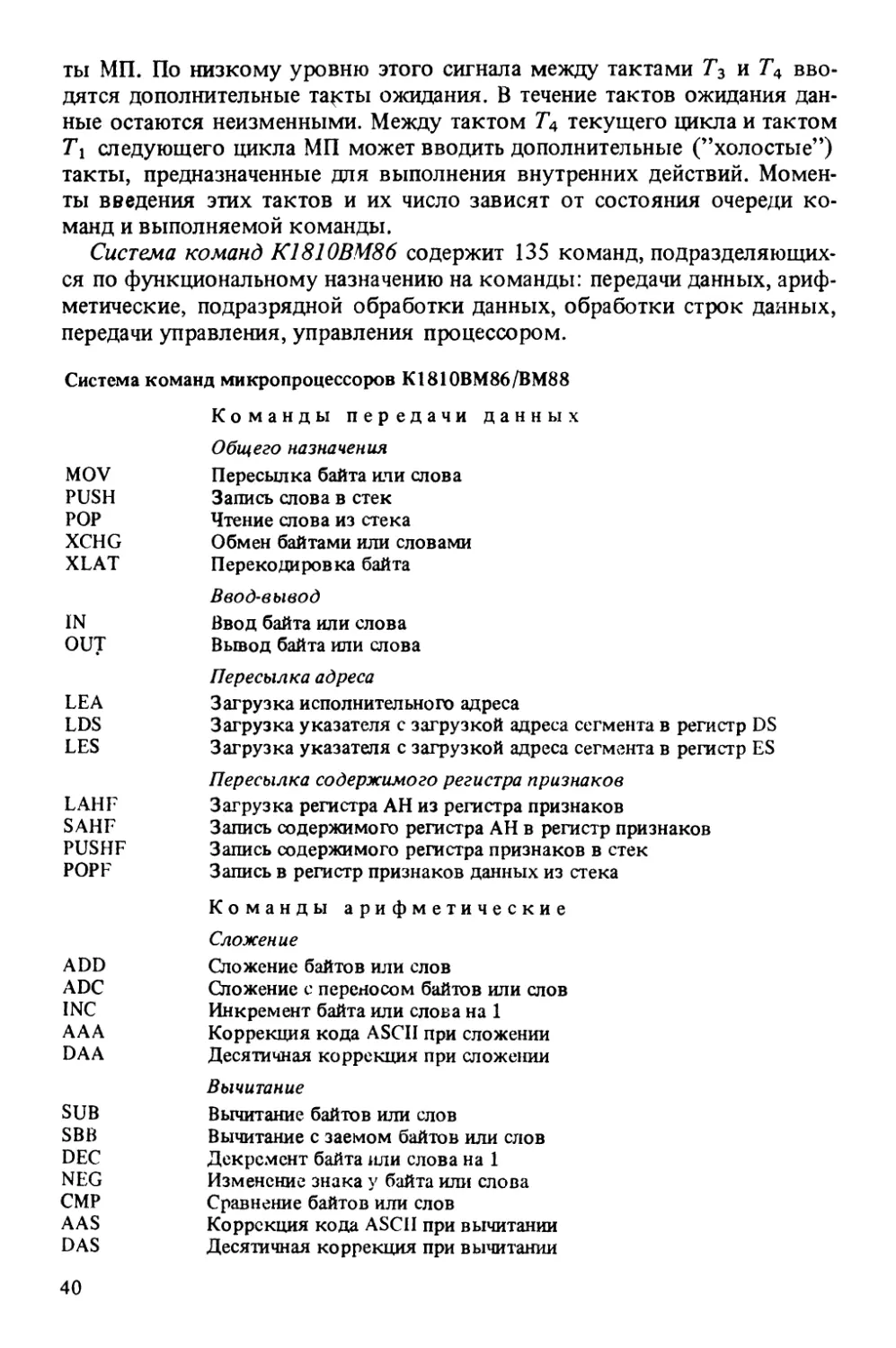

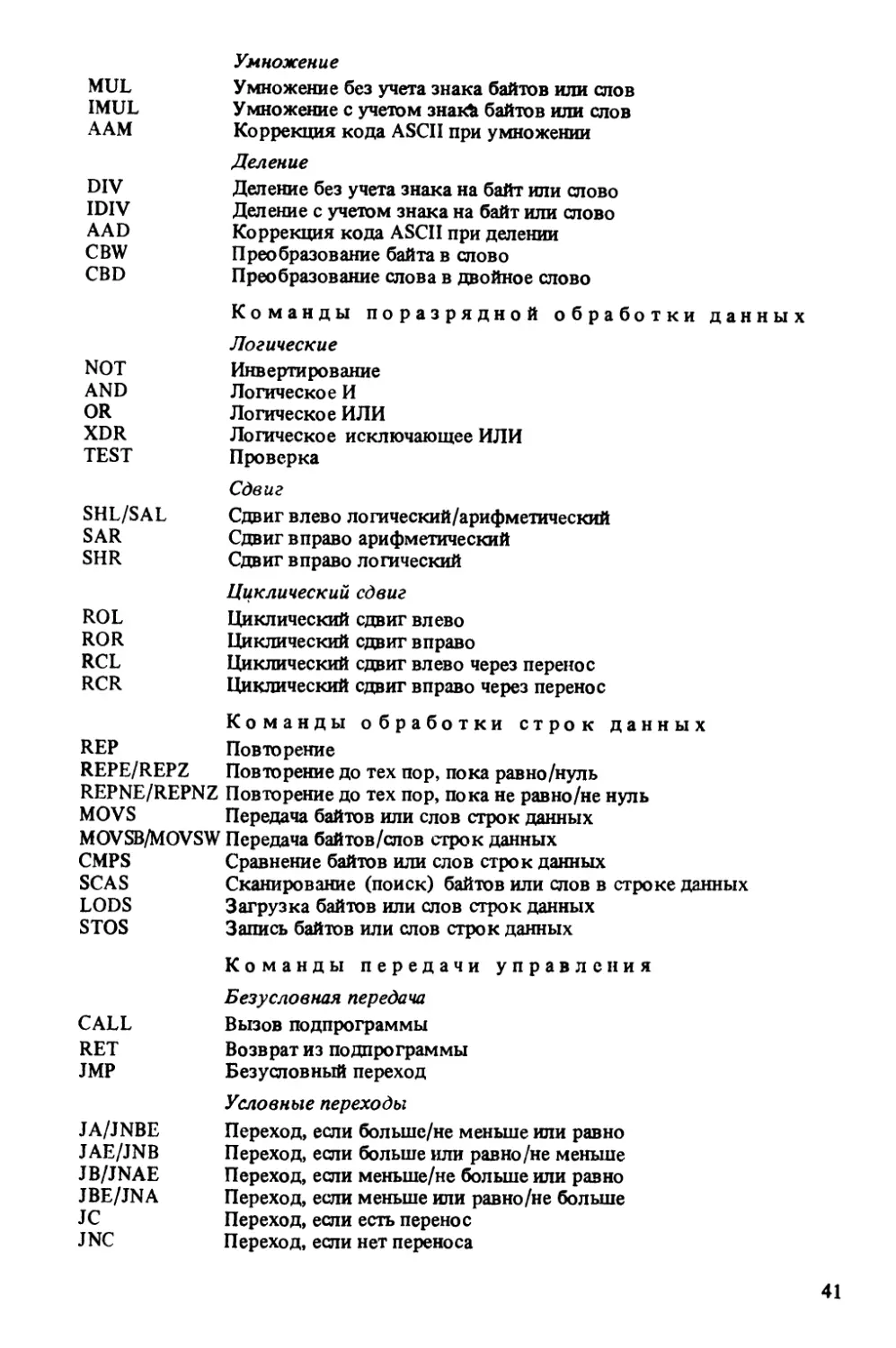

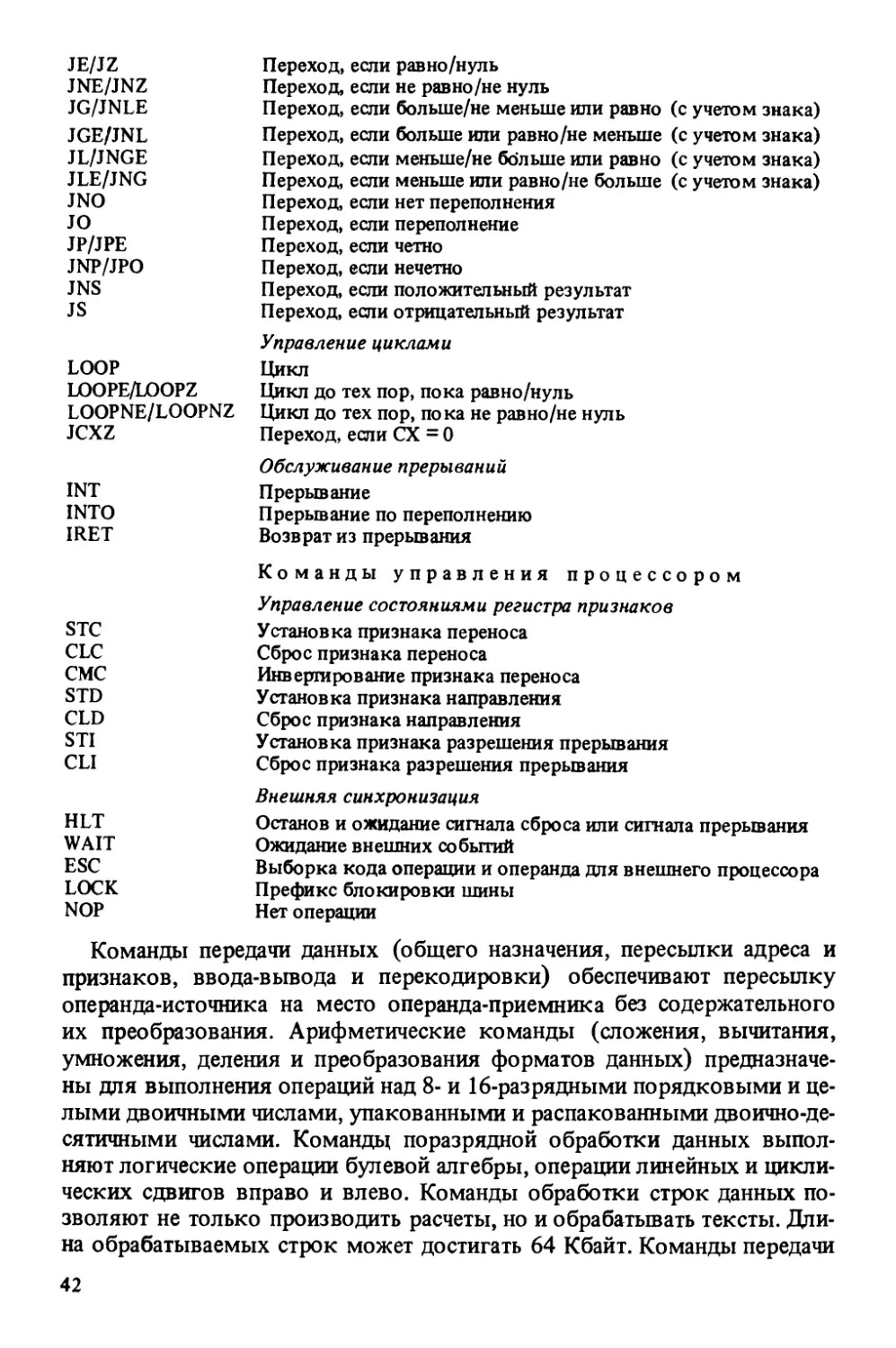

Система команд К1810ВМ86 содержит 135 команд, подразделяющих-

ся по функциональному назначению на команды: передачи данных, ариф-

метические, подразрядной обработки данных, обработки строк данных,

передачи управления, управления процессором.

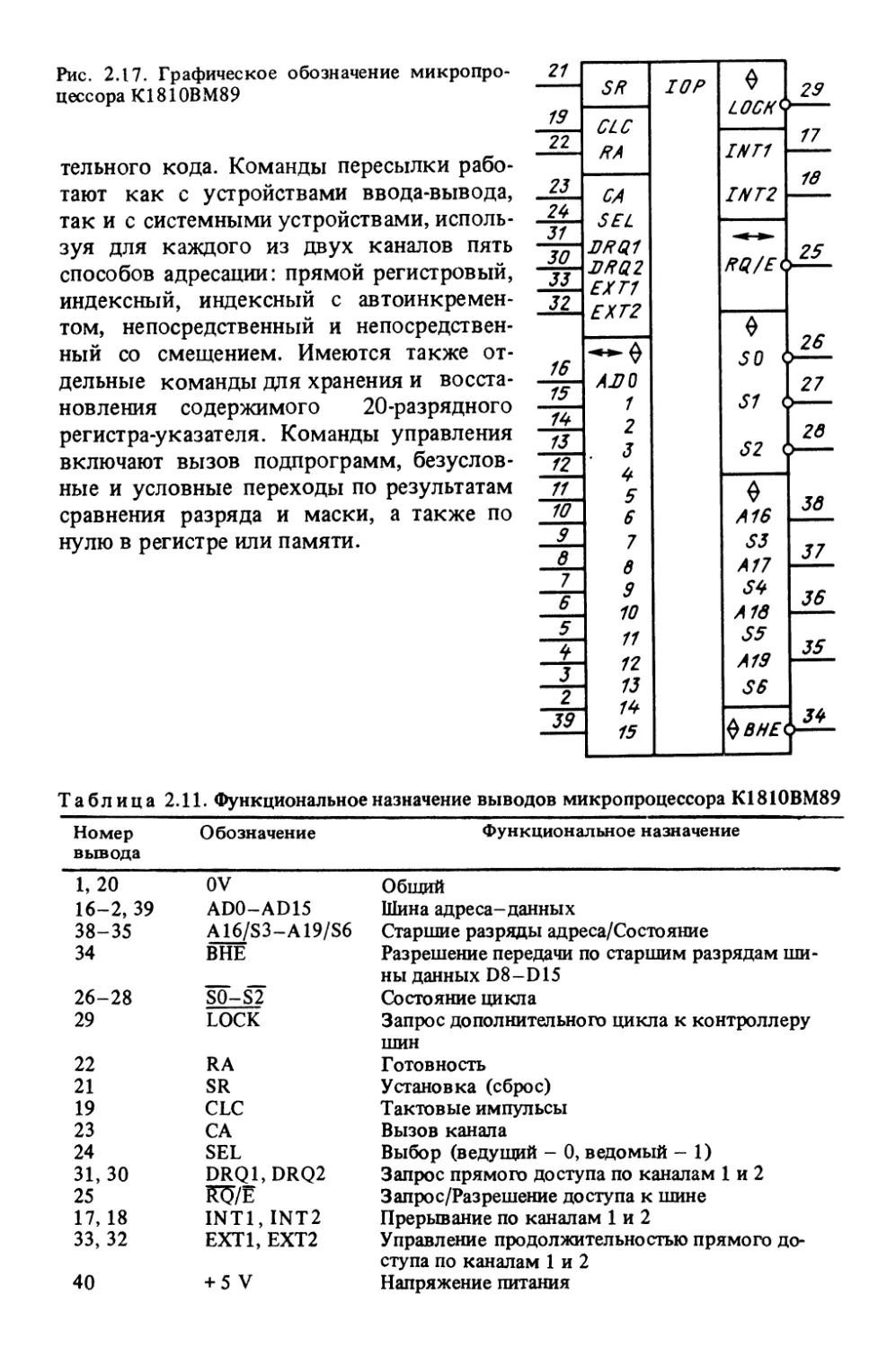

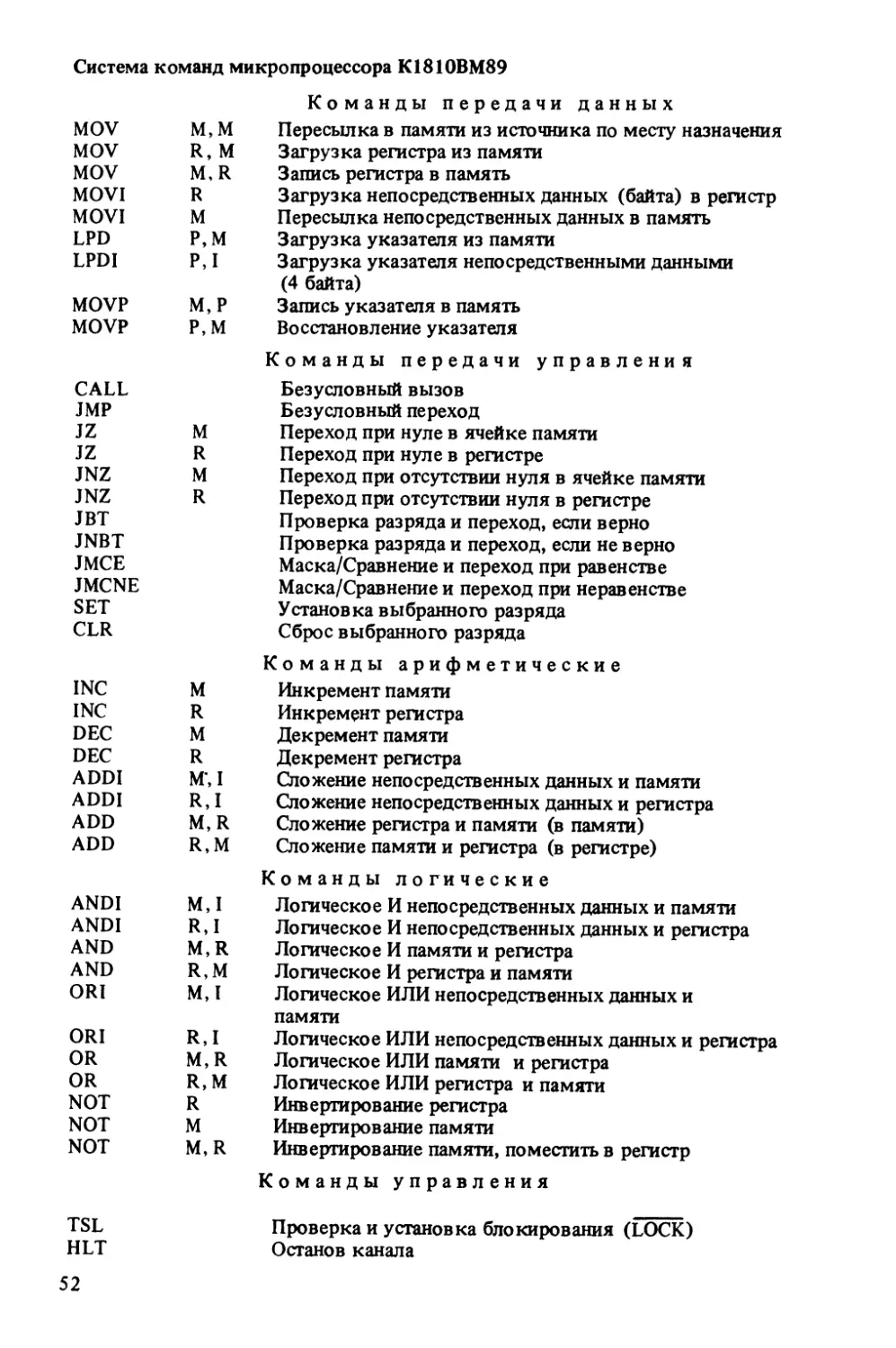

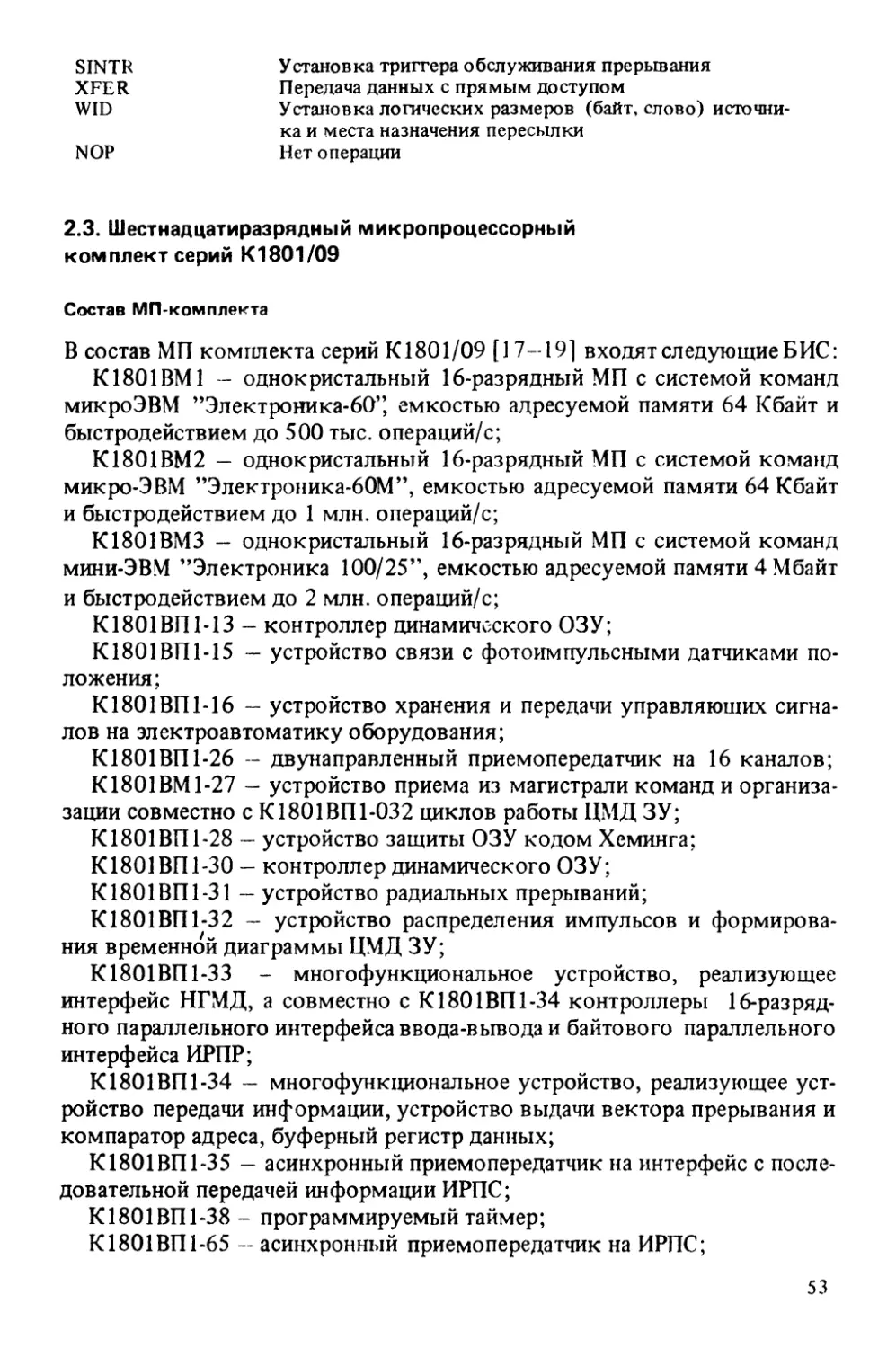

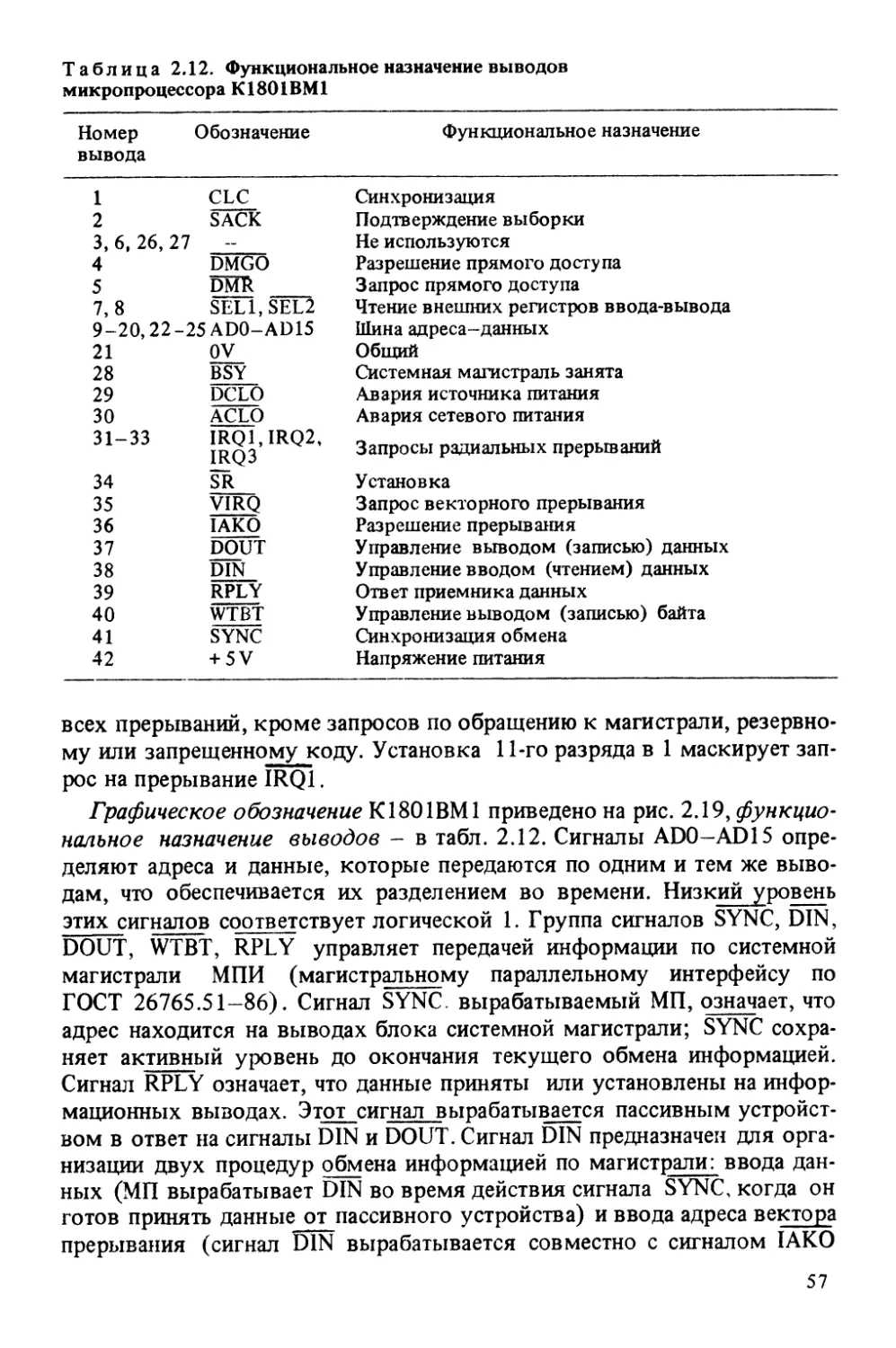

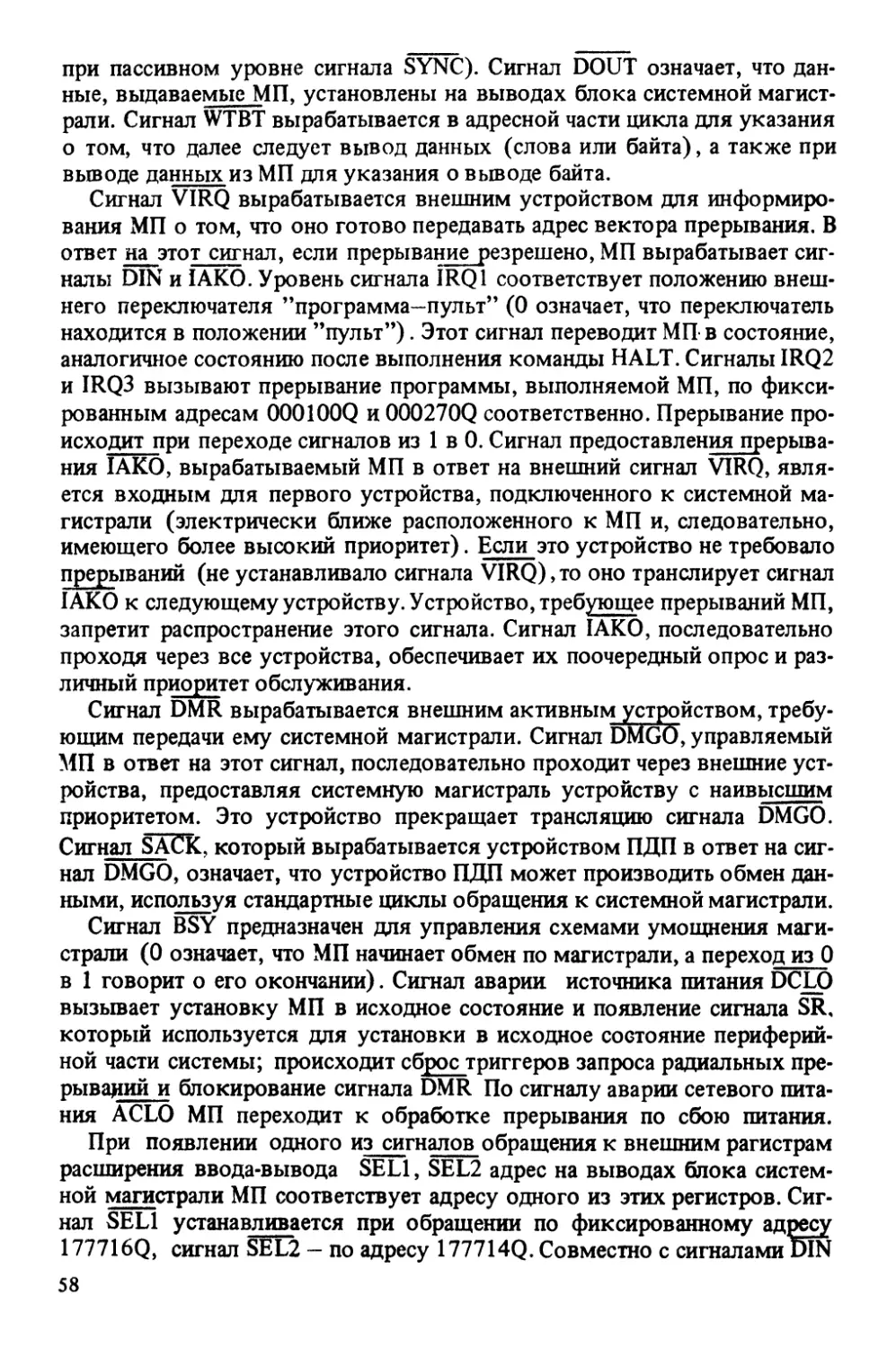

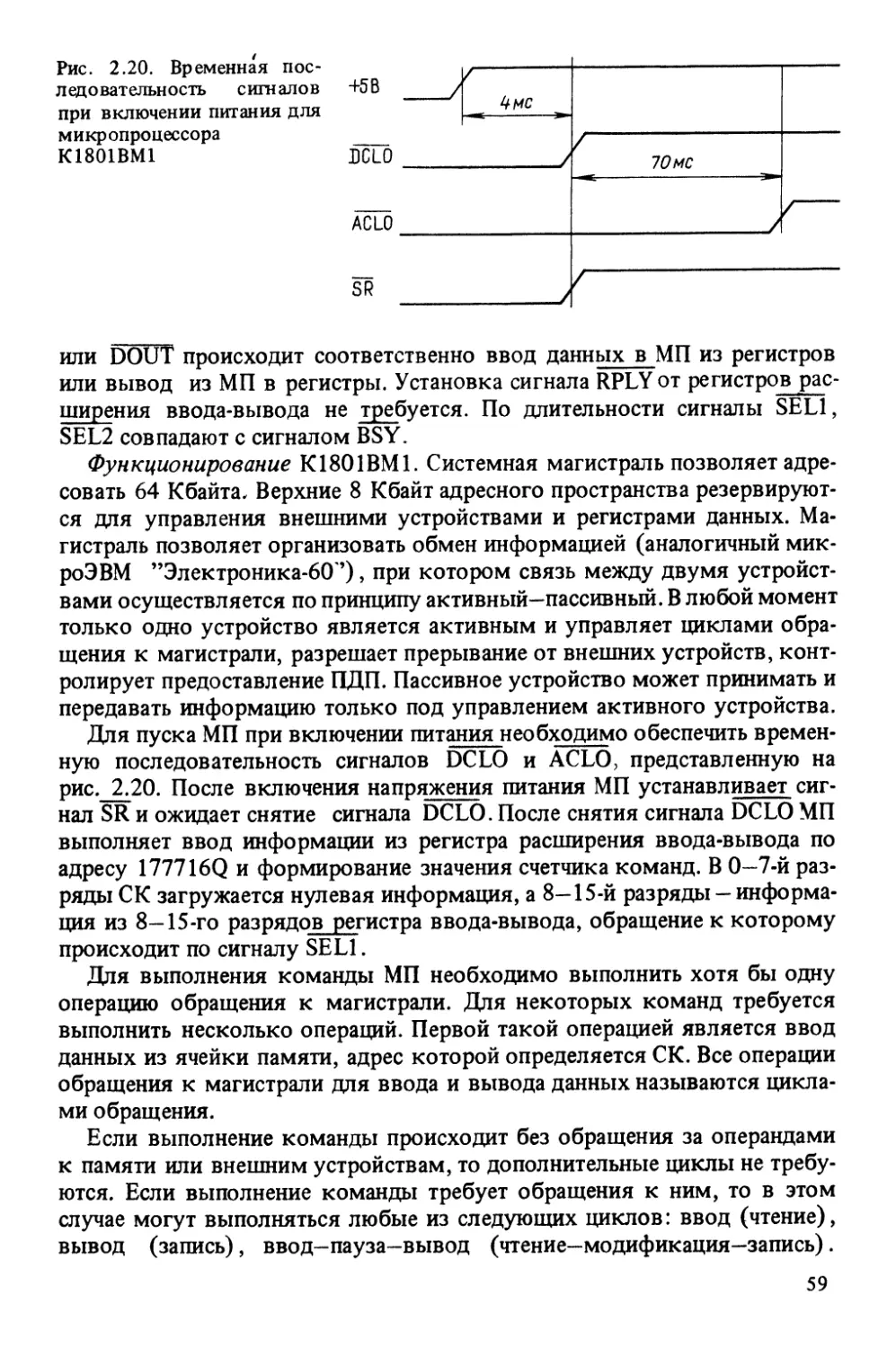

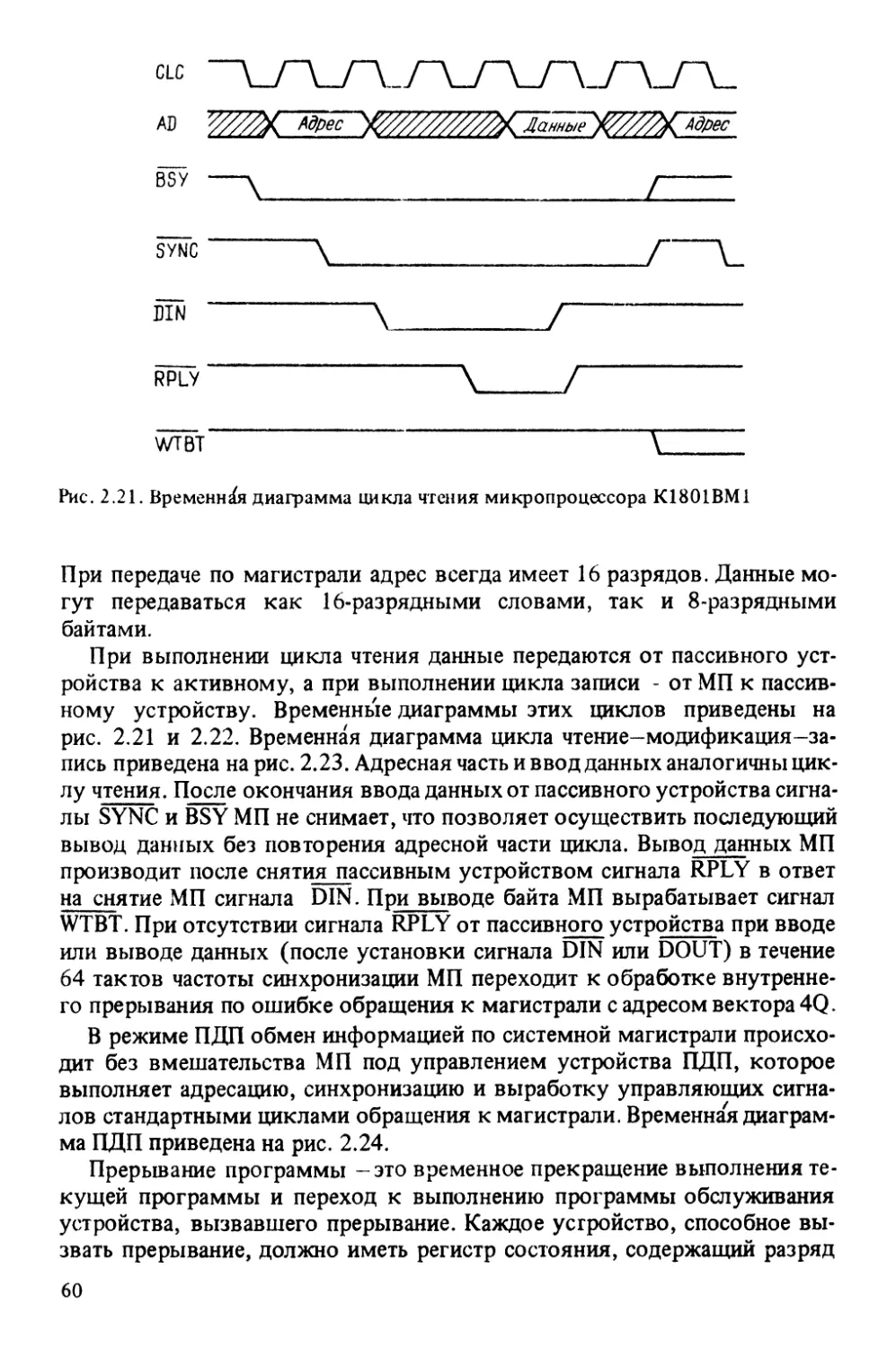

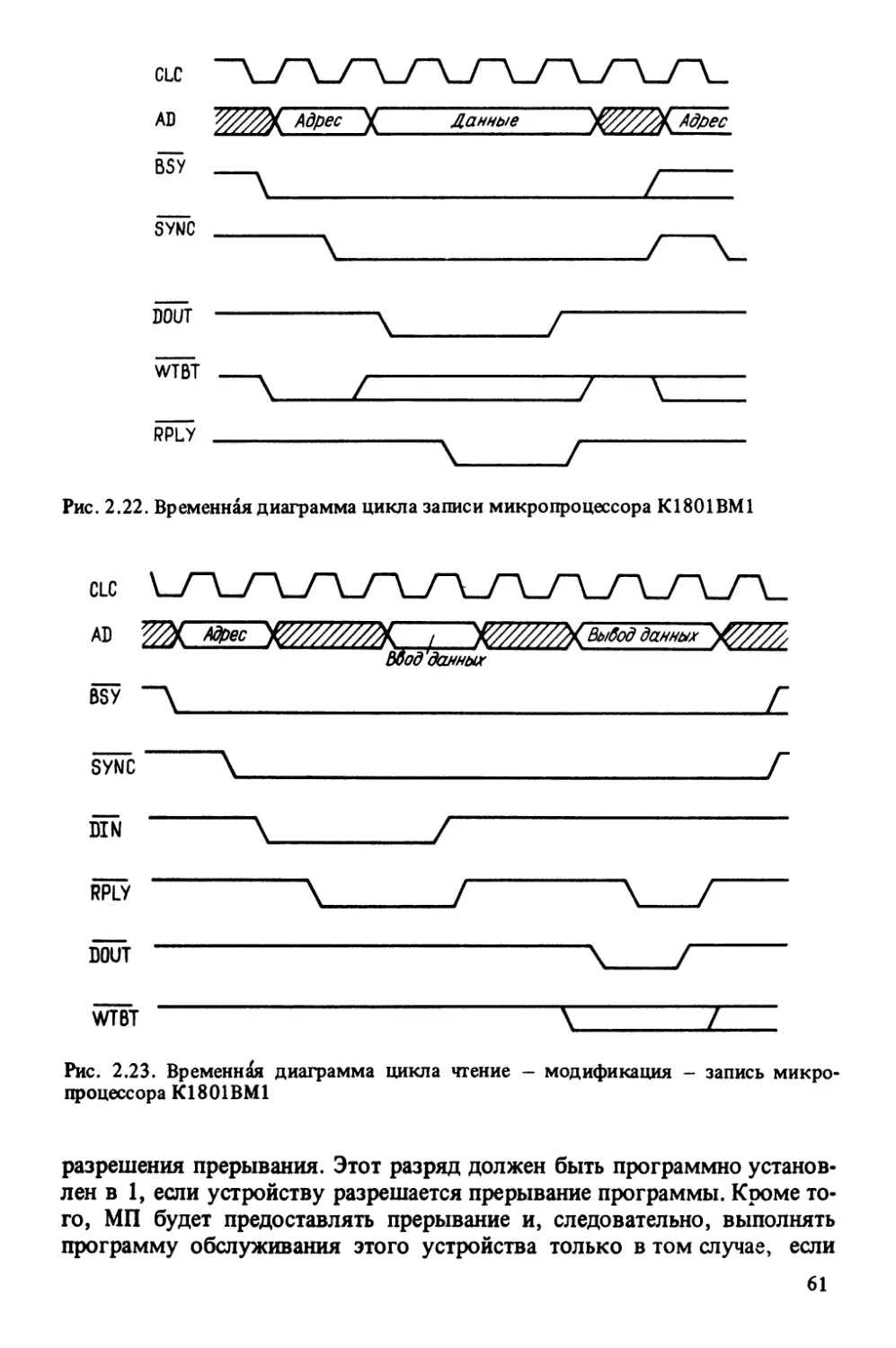

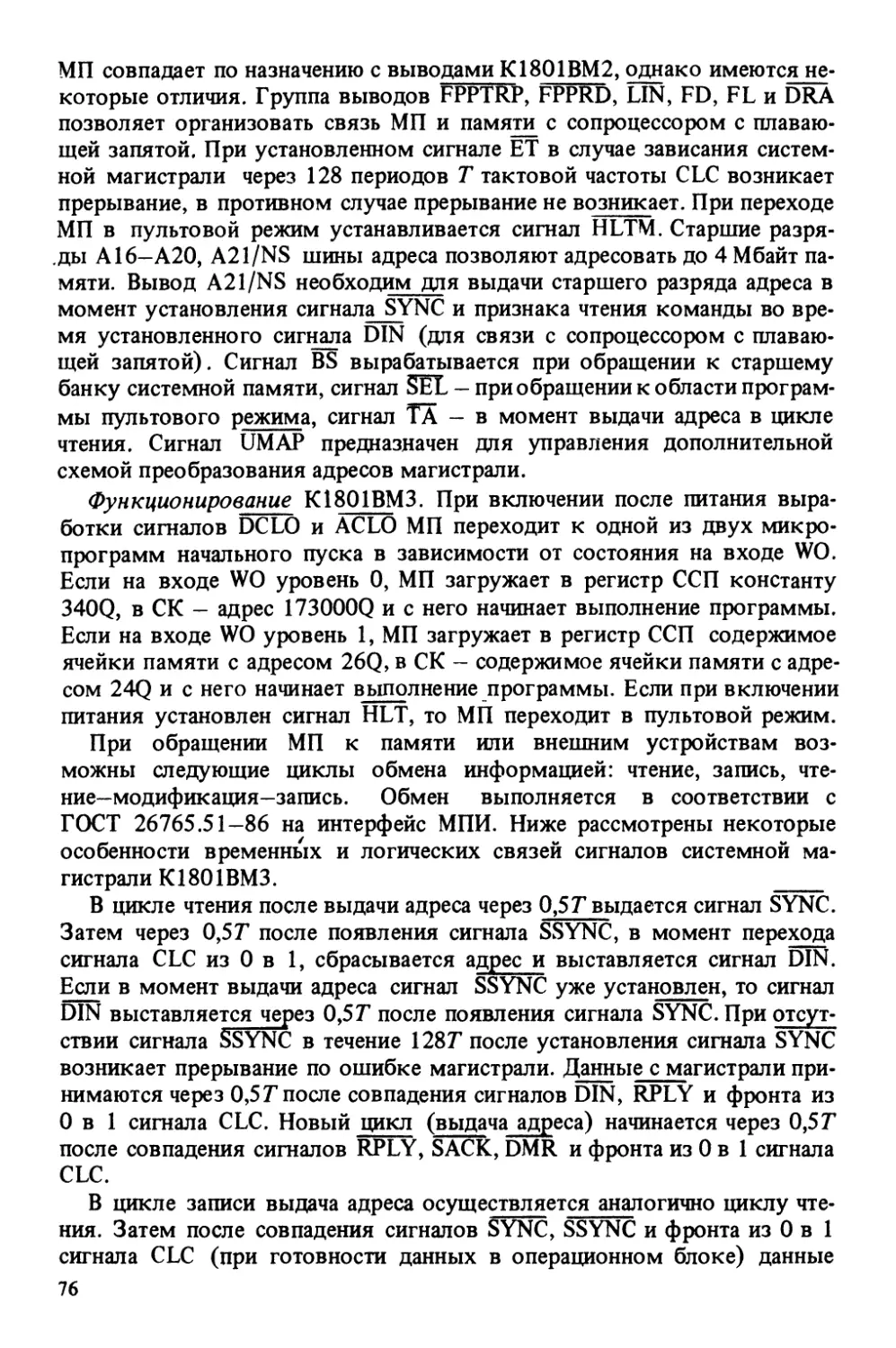

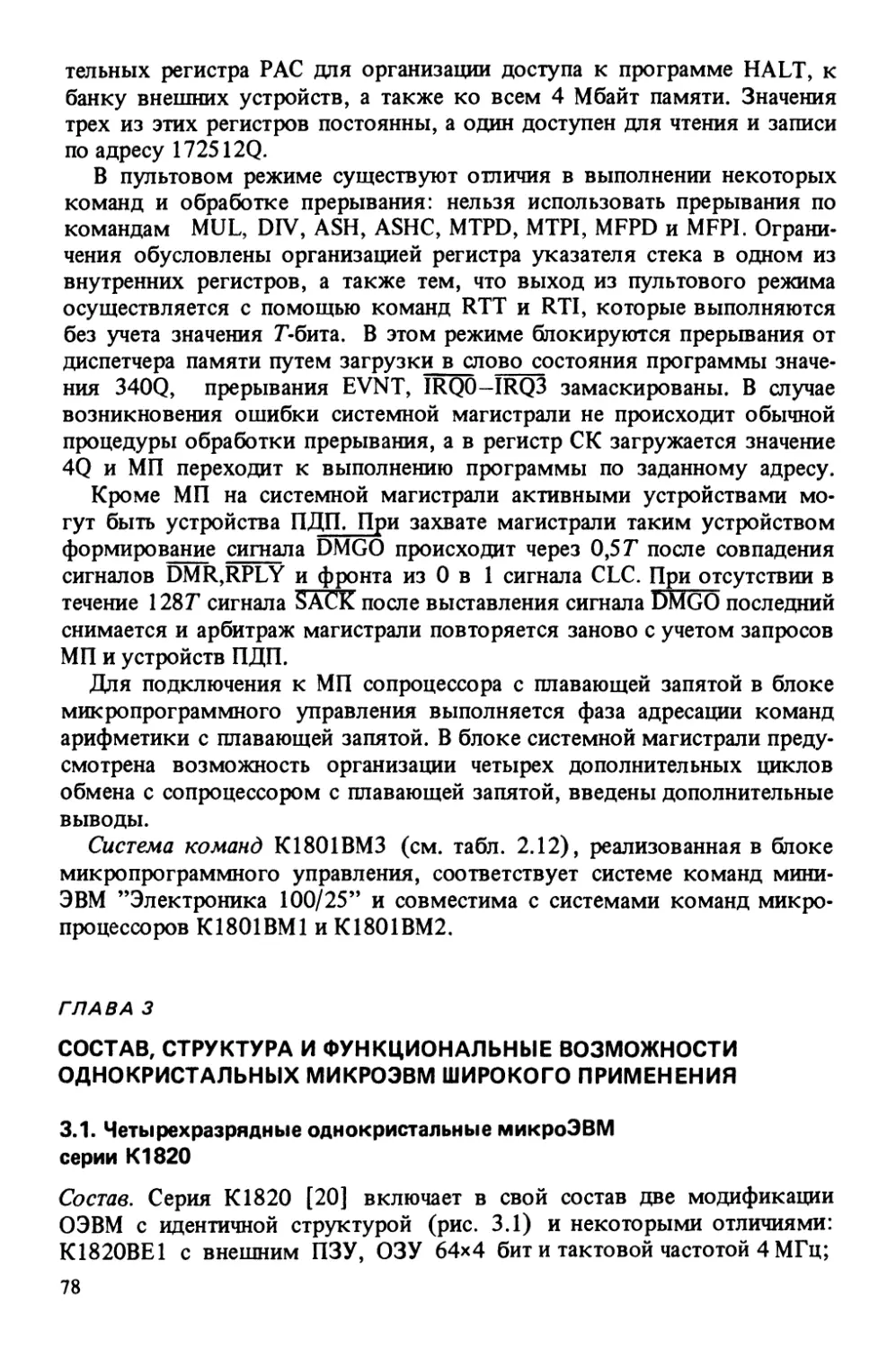

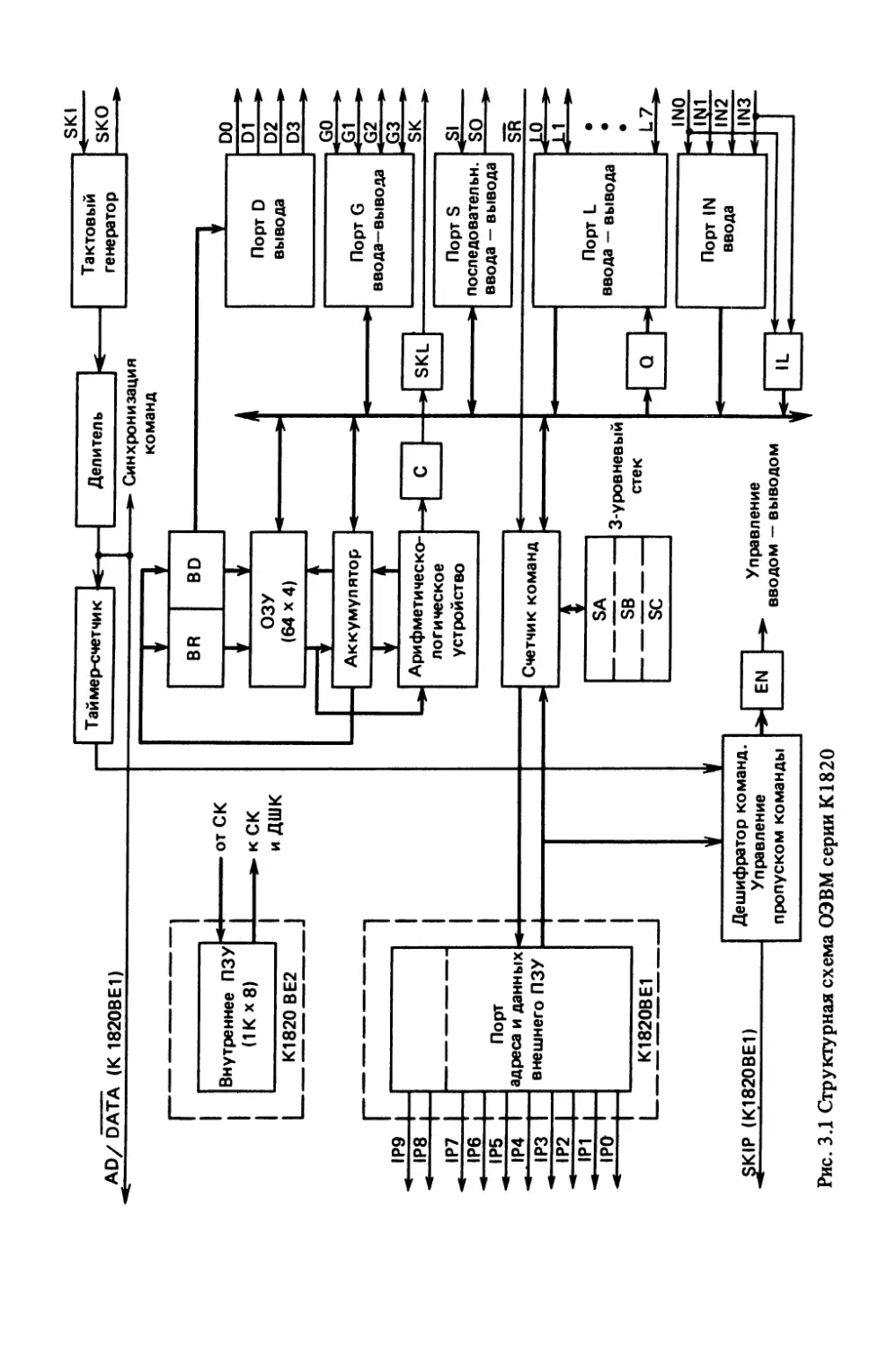

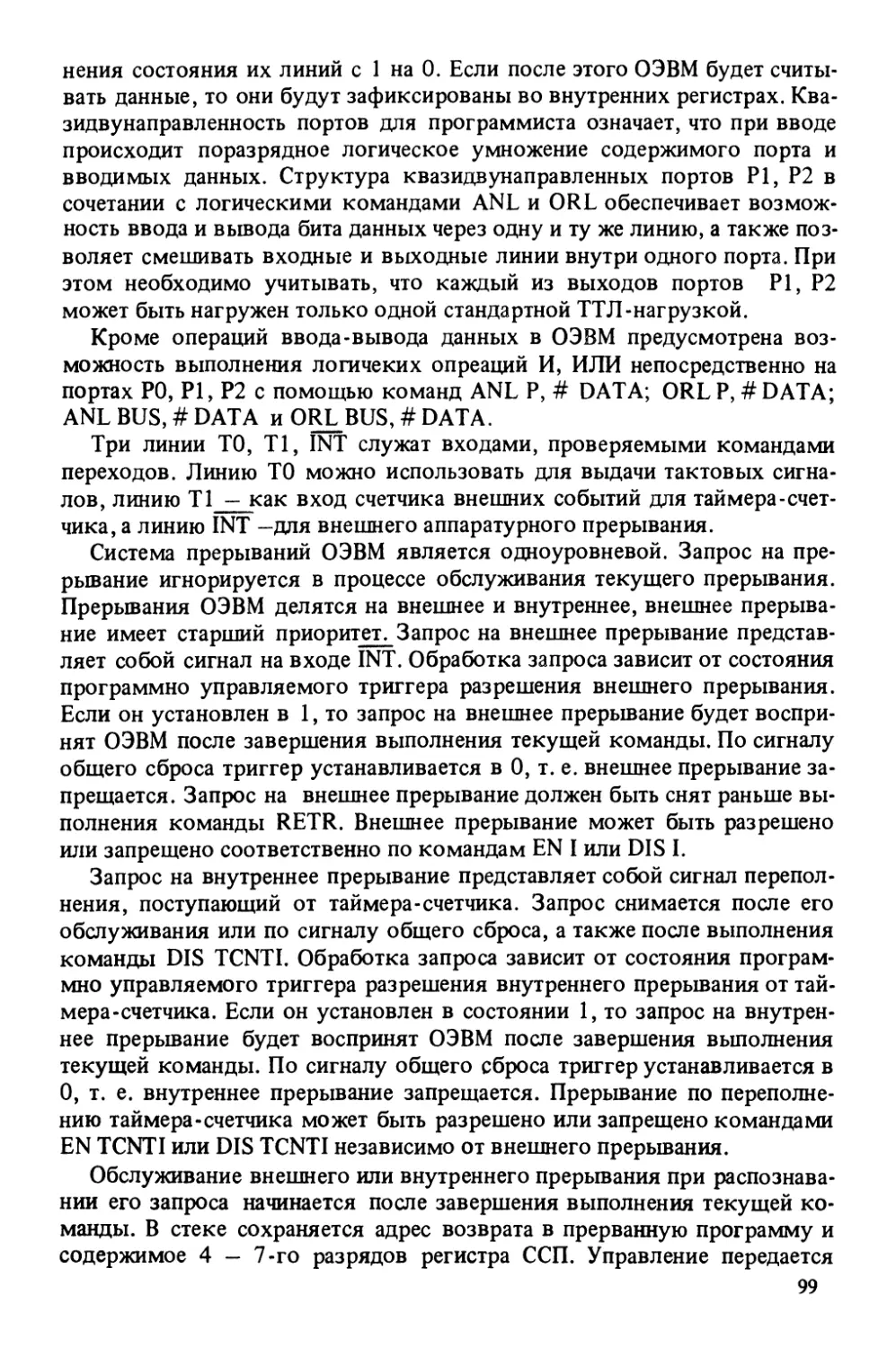

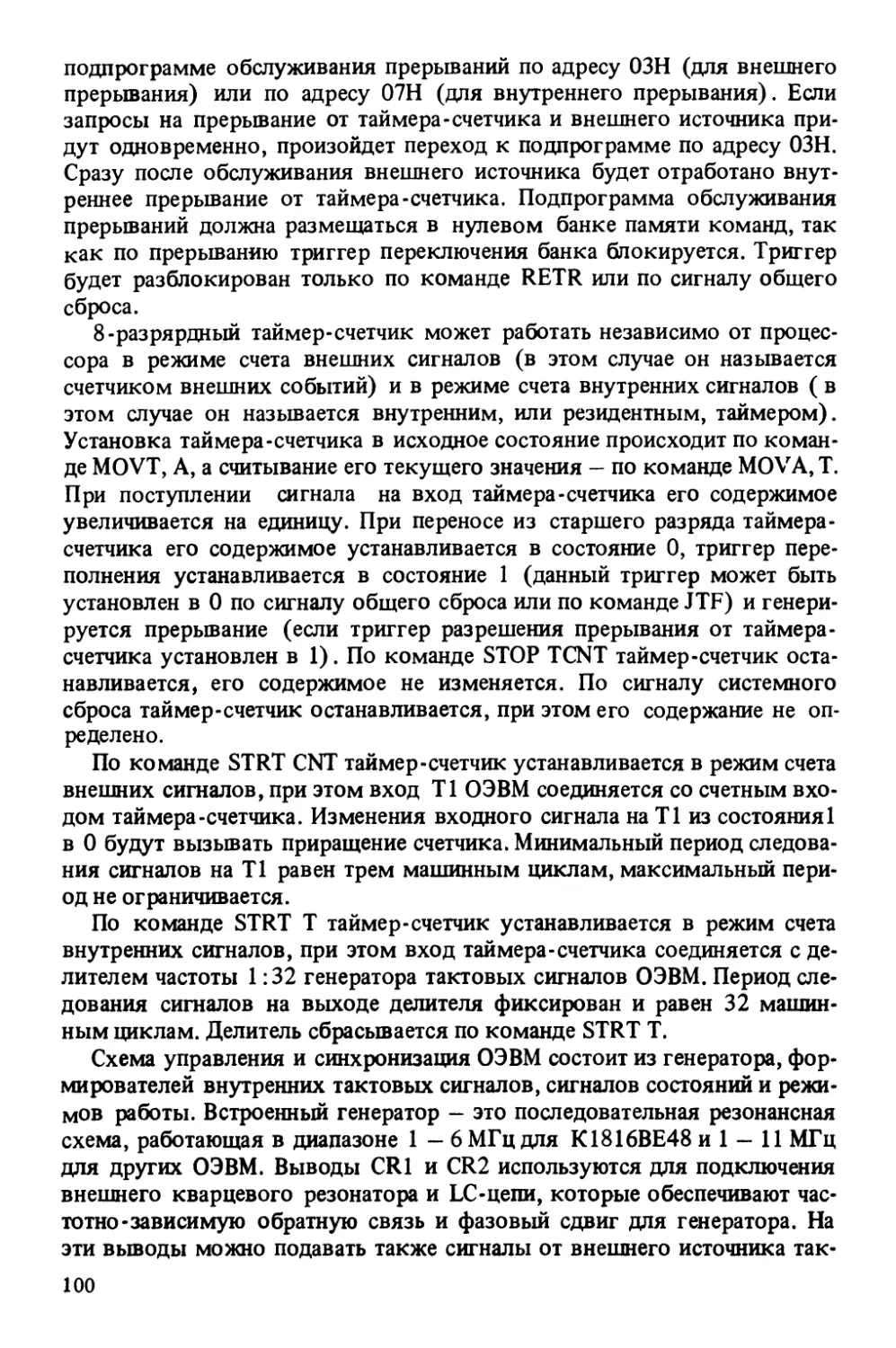

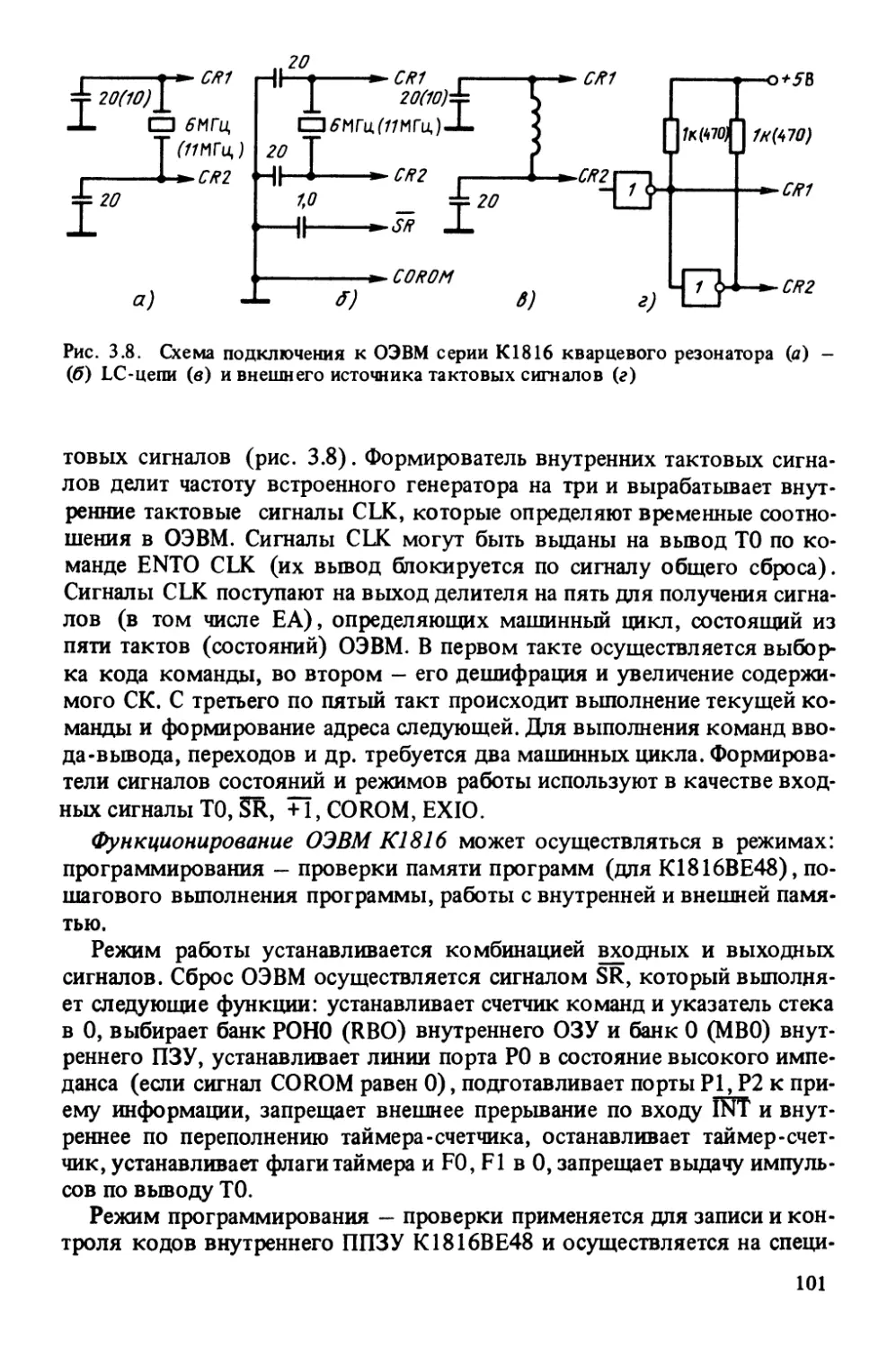

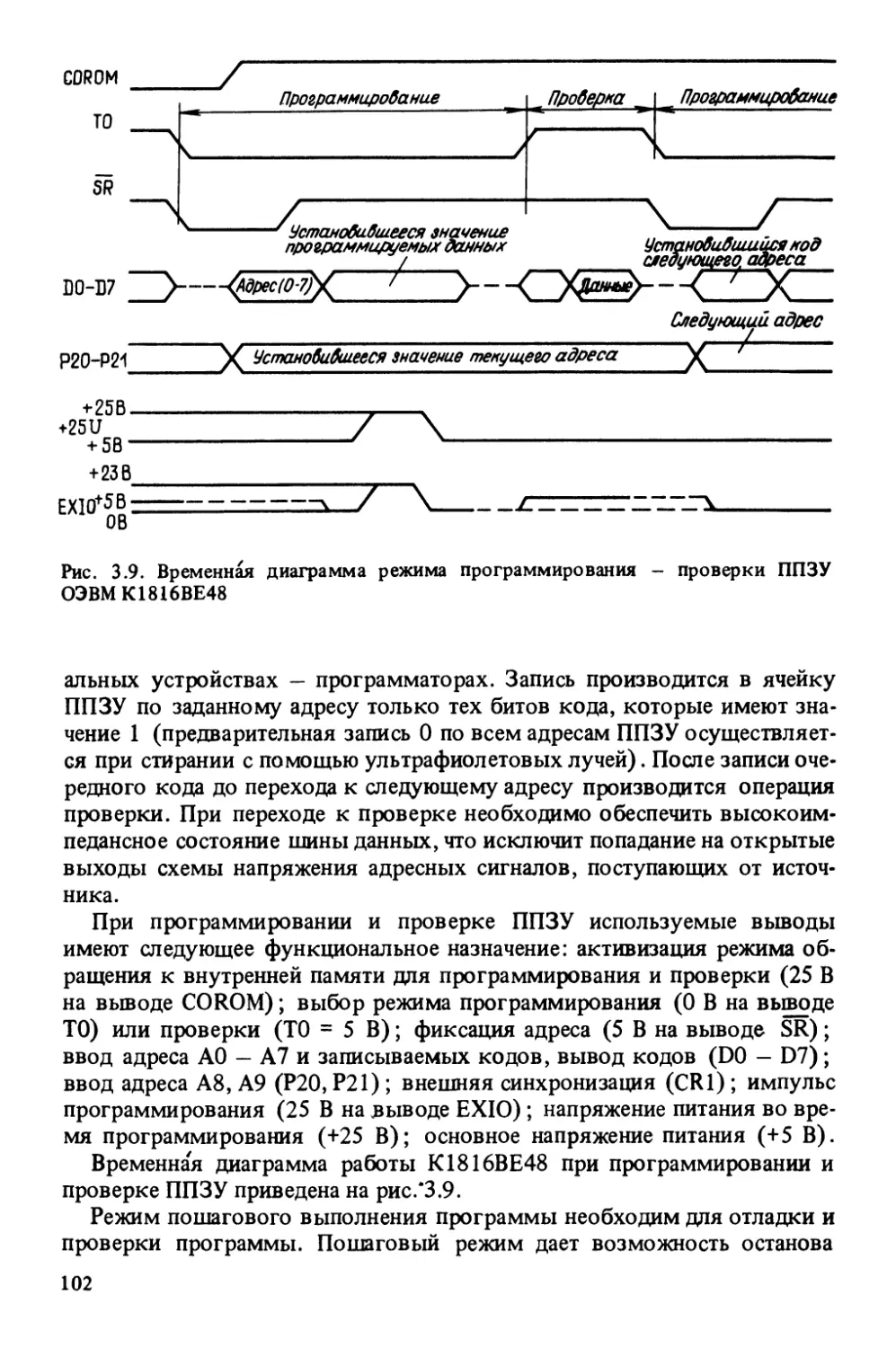

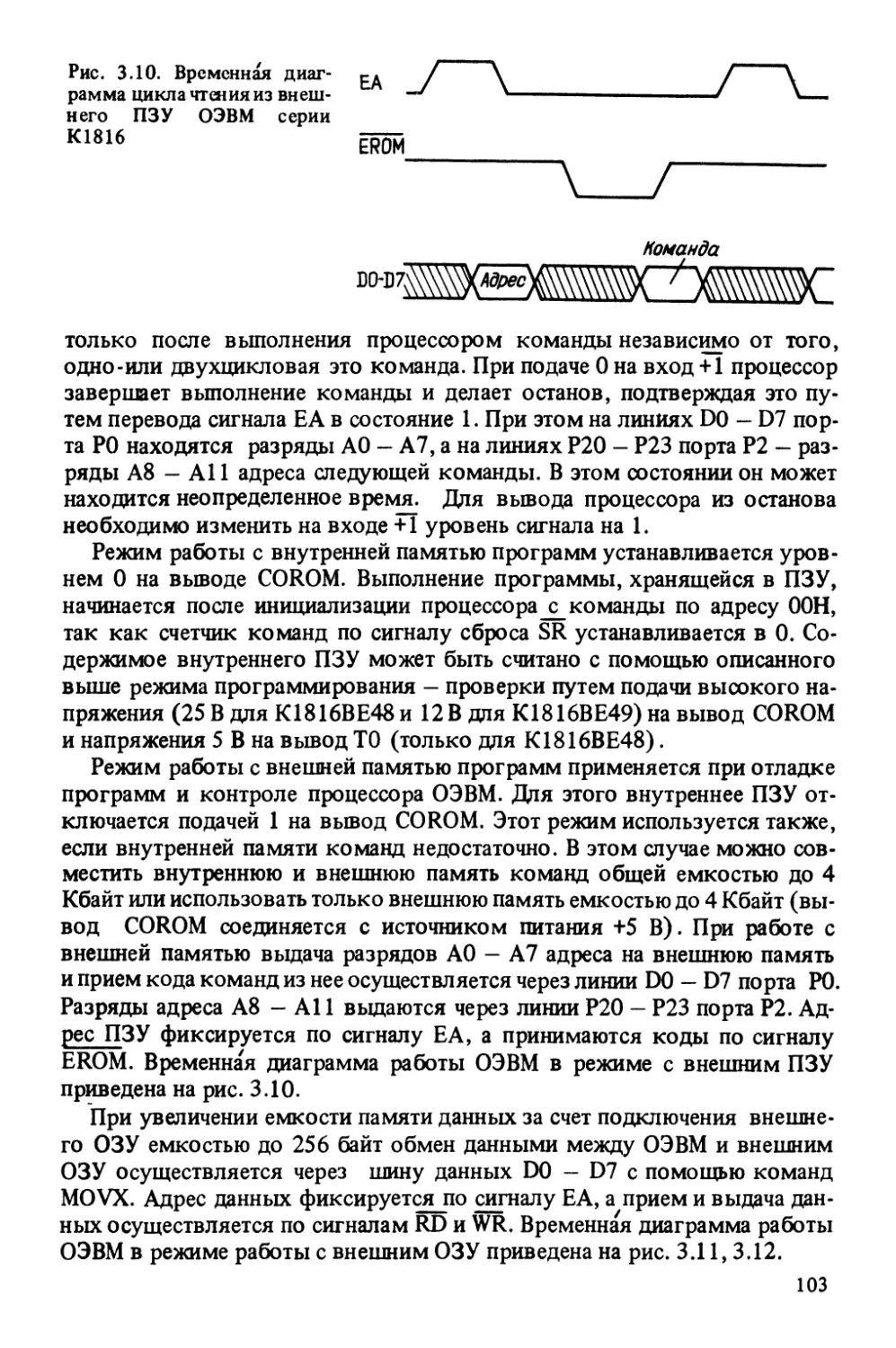

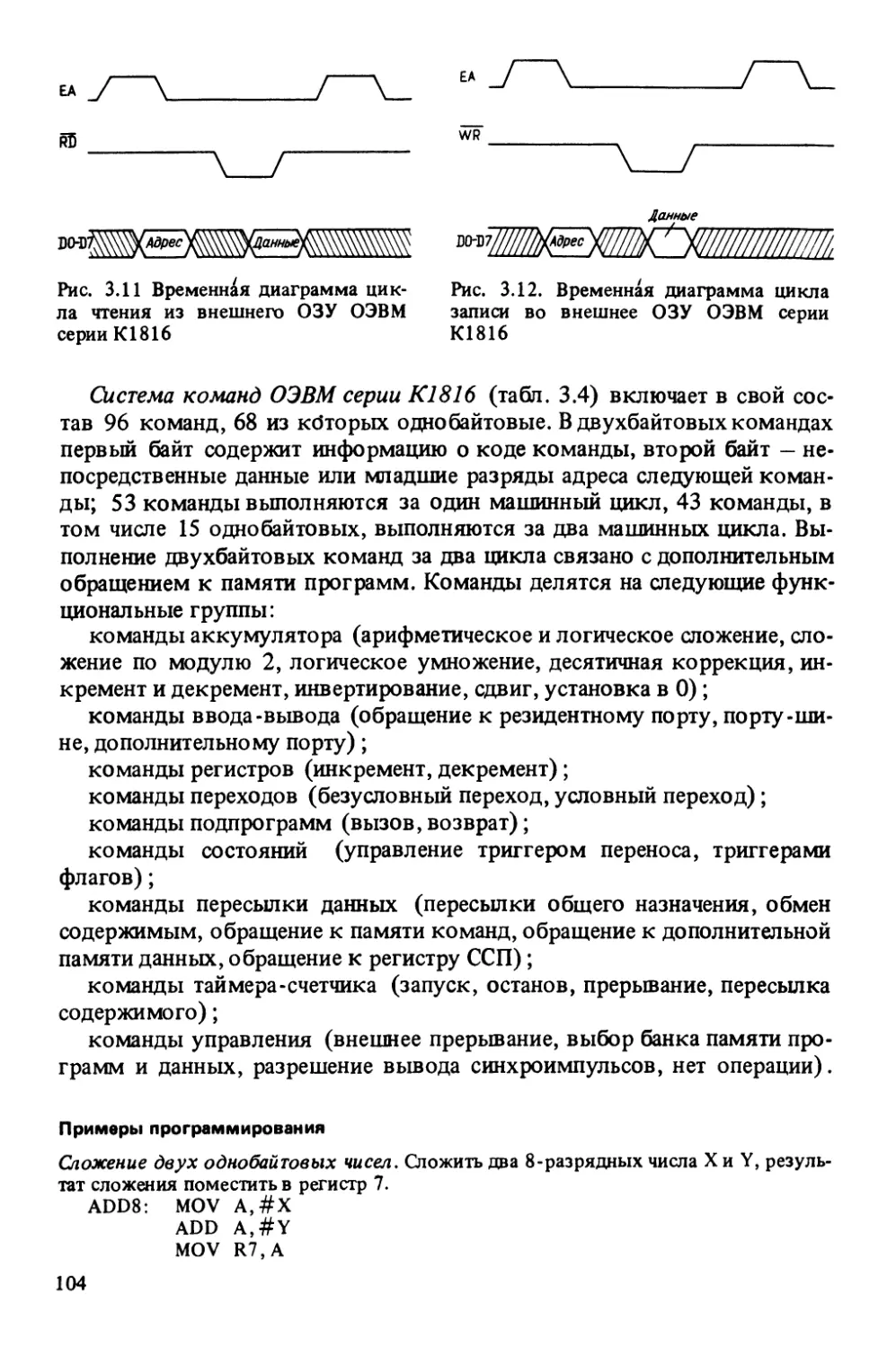

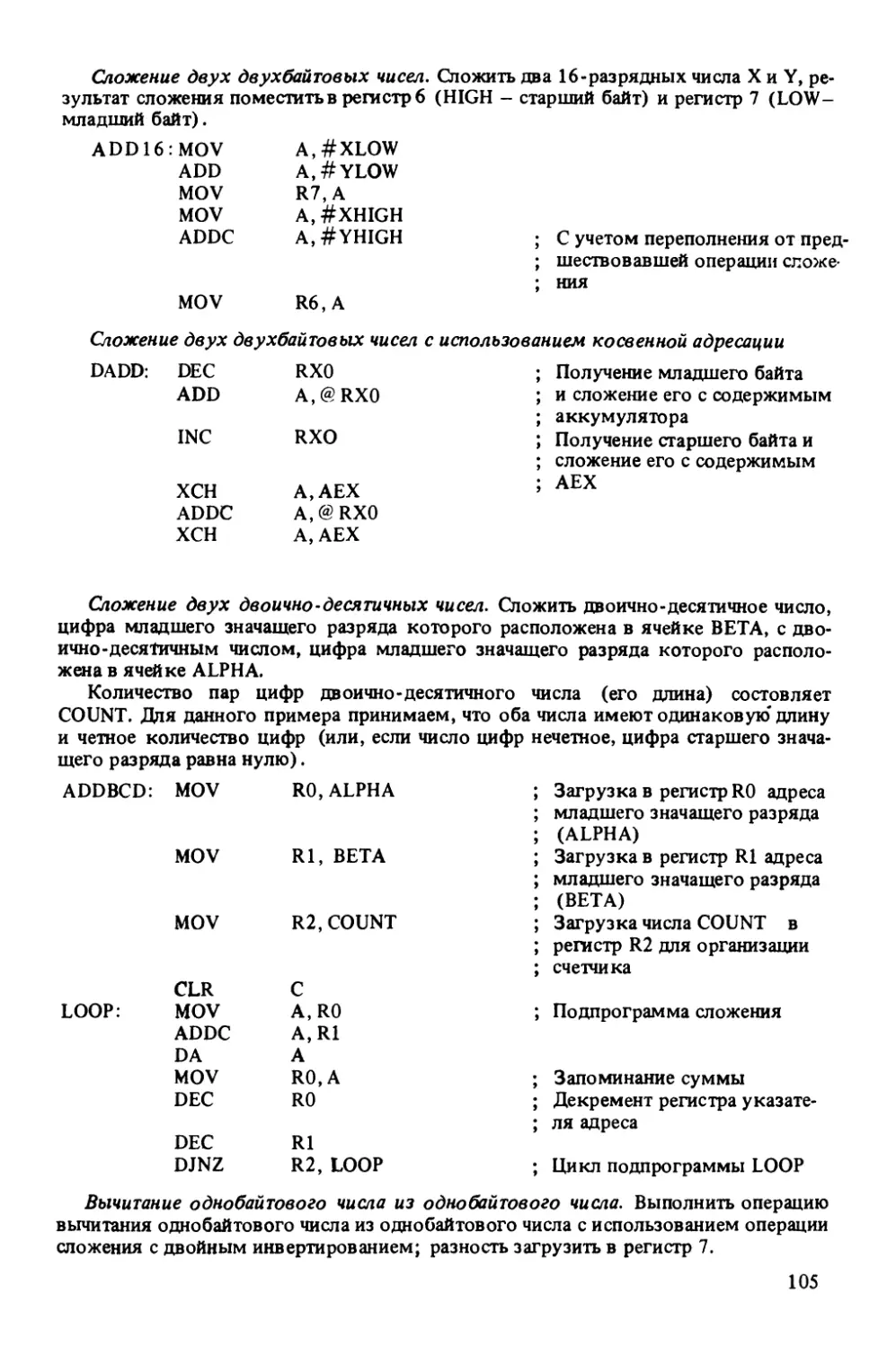

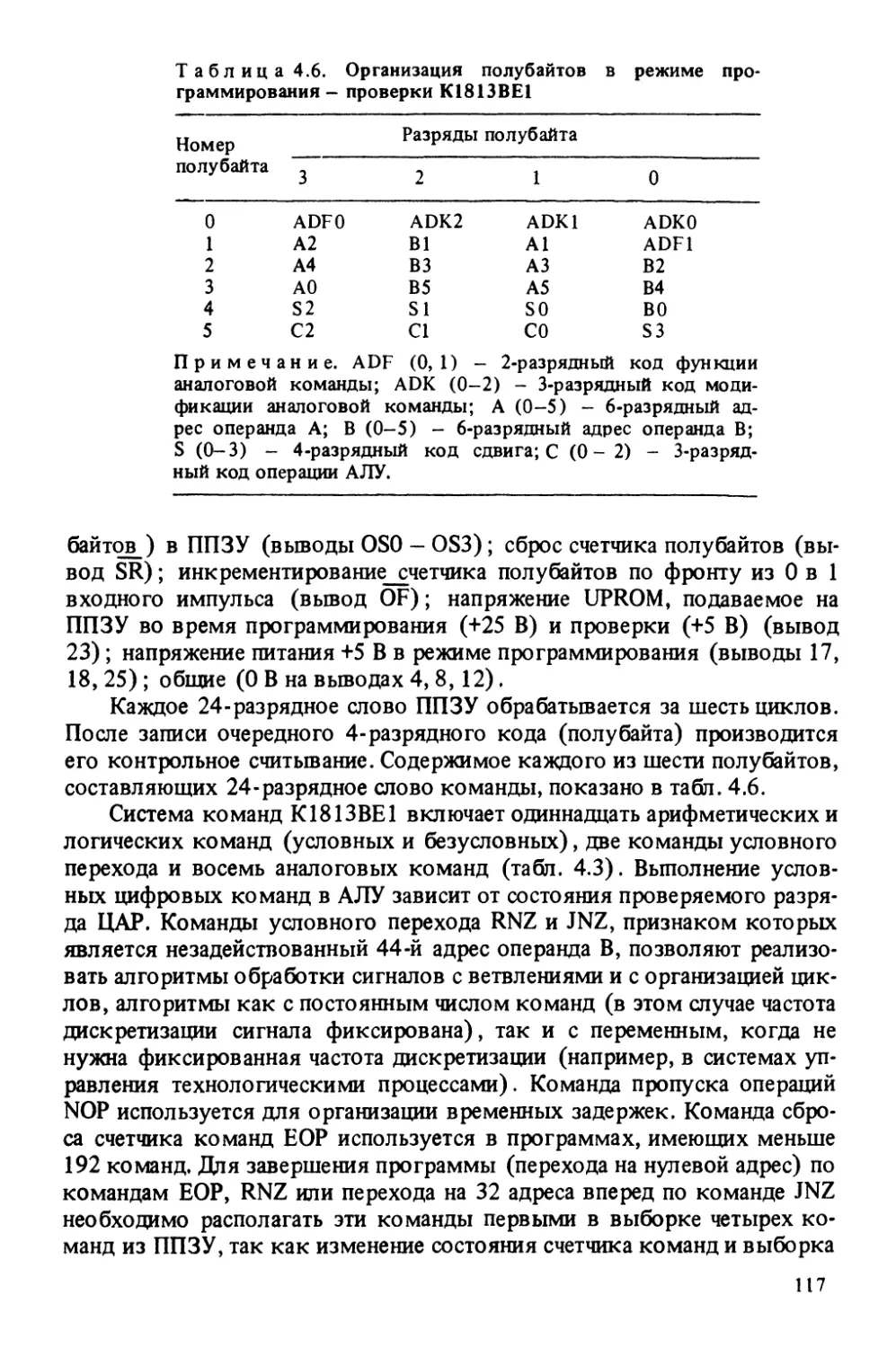

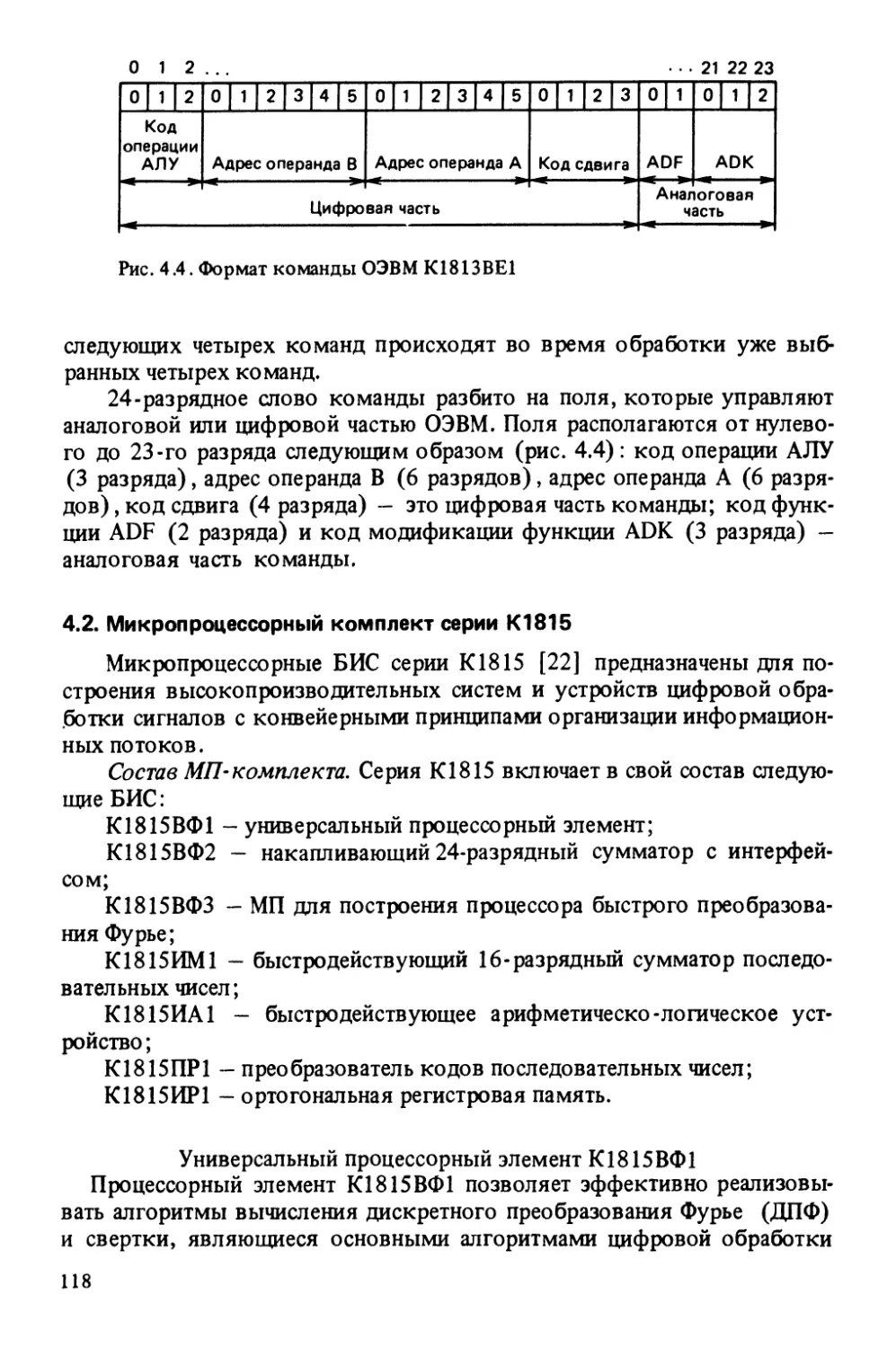

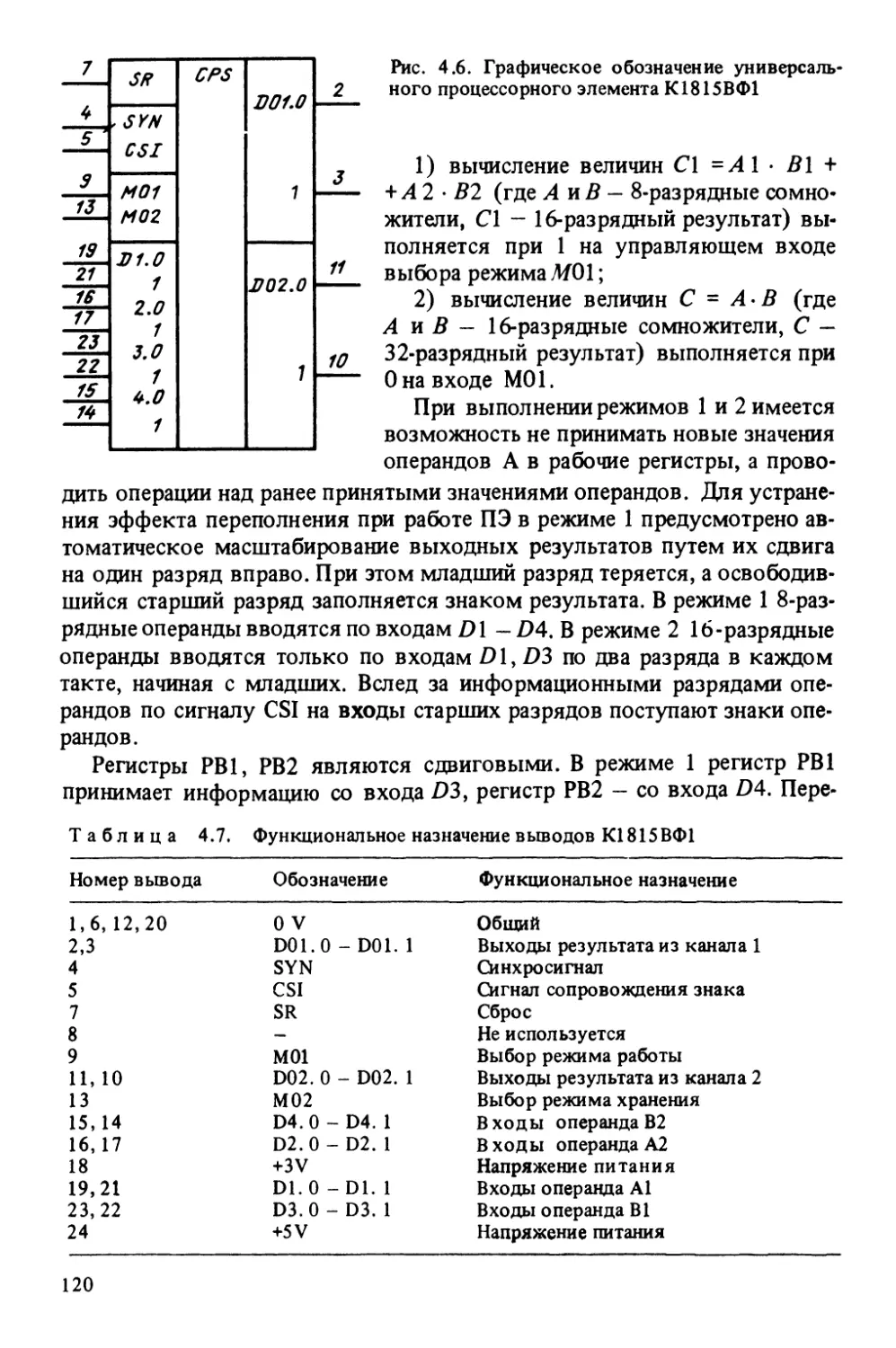

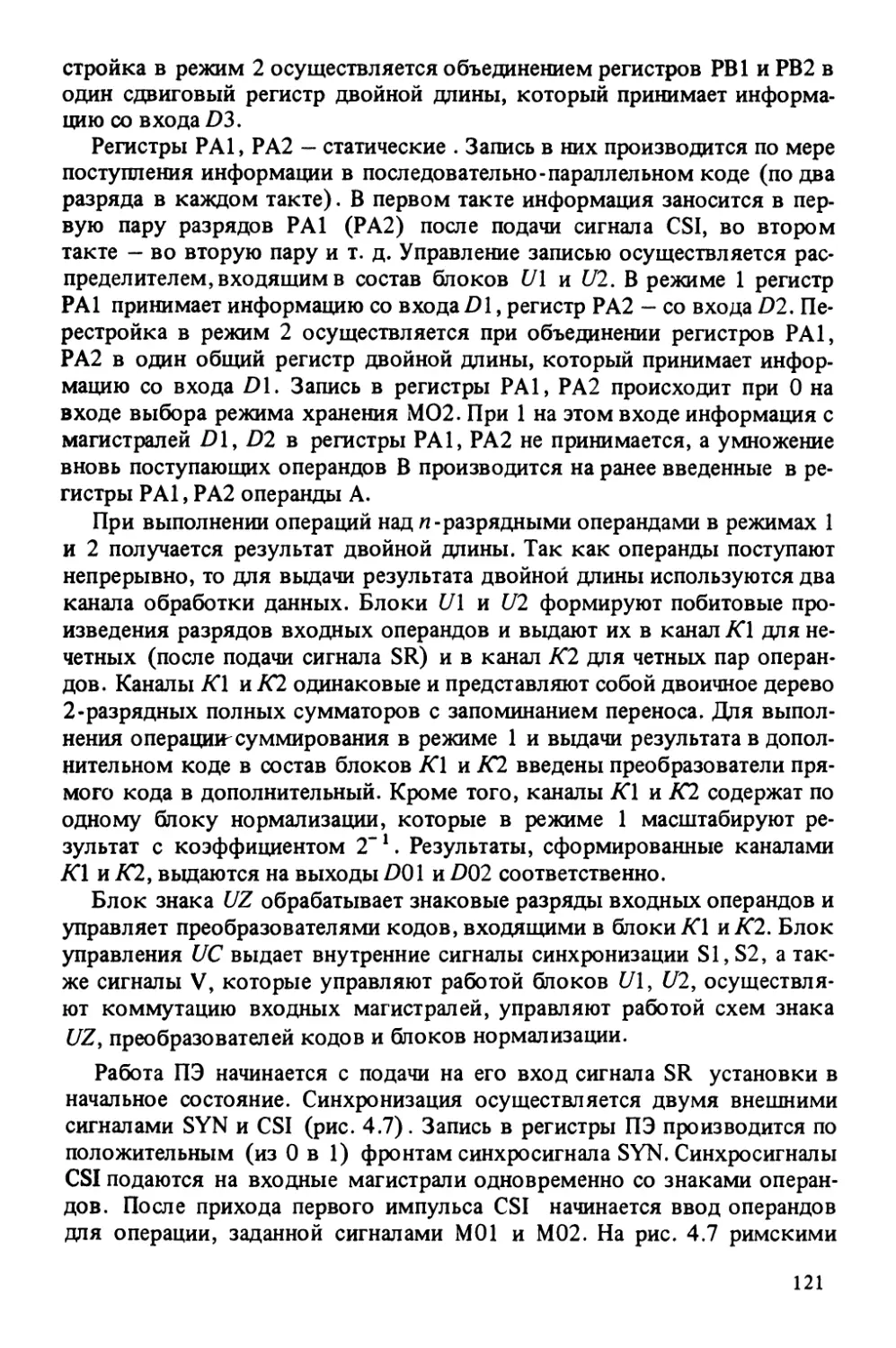

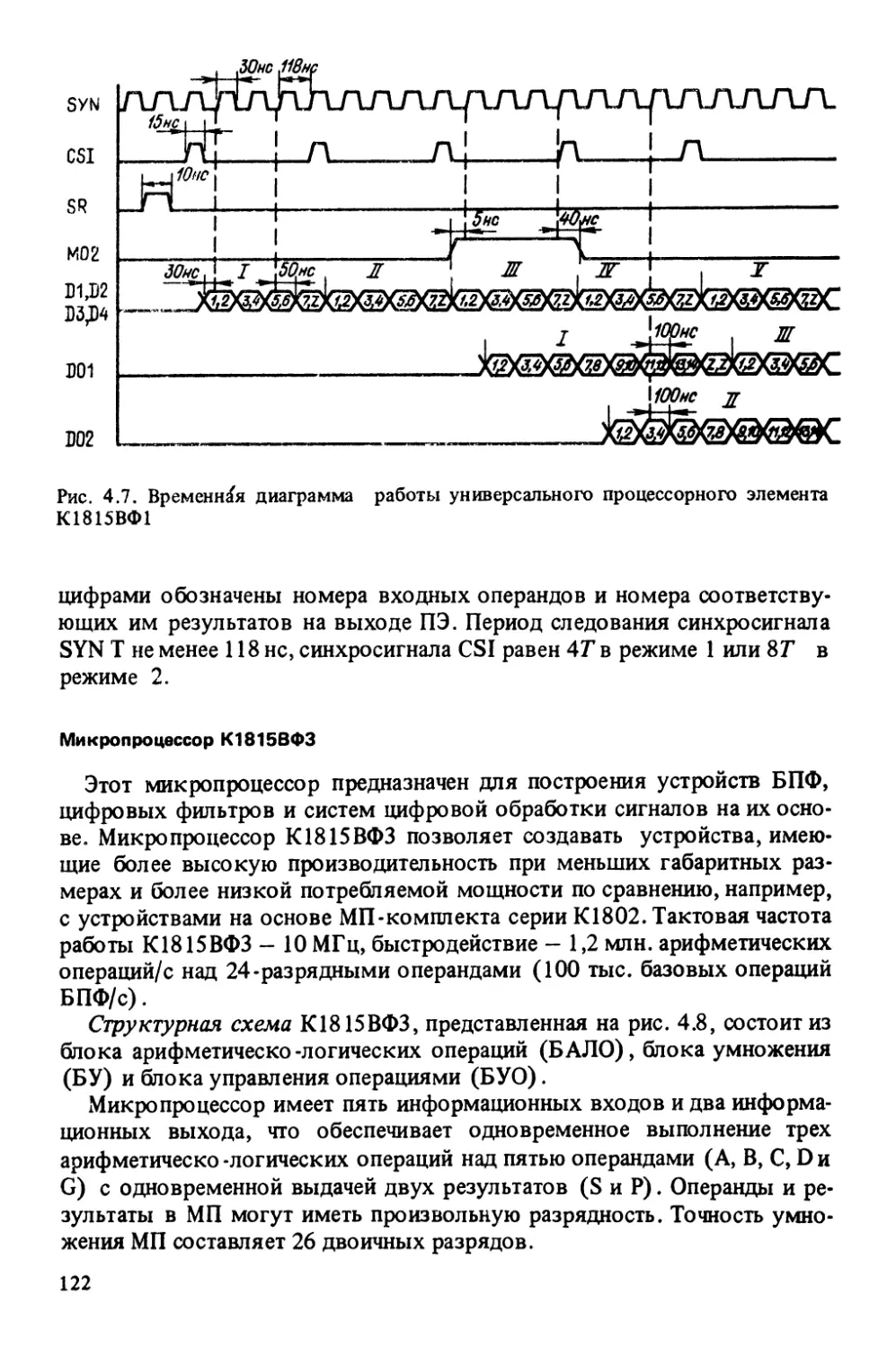

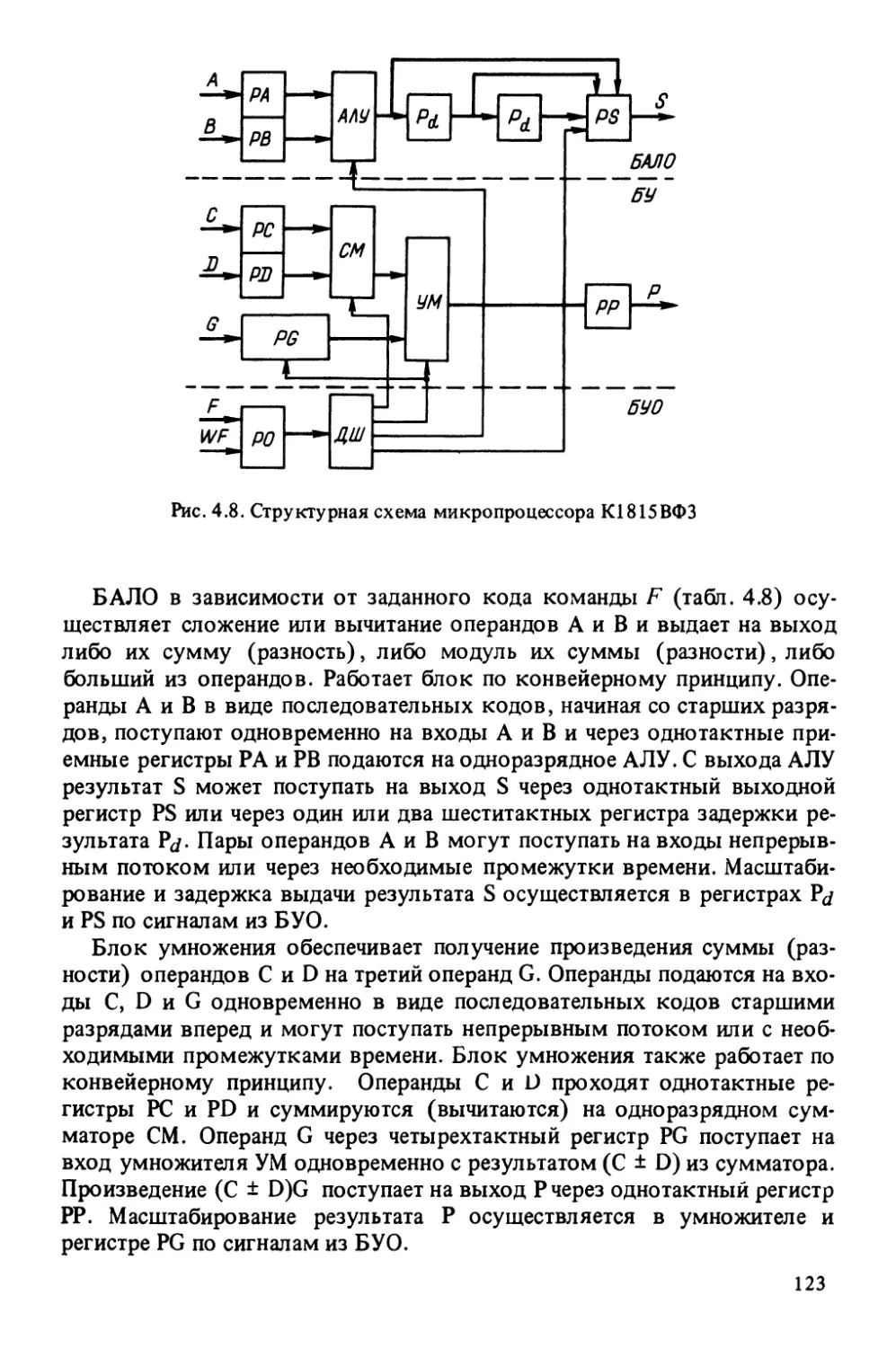

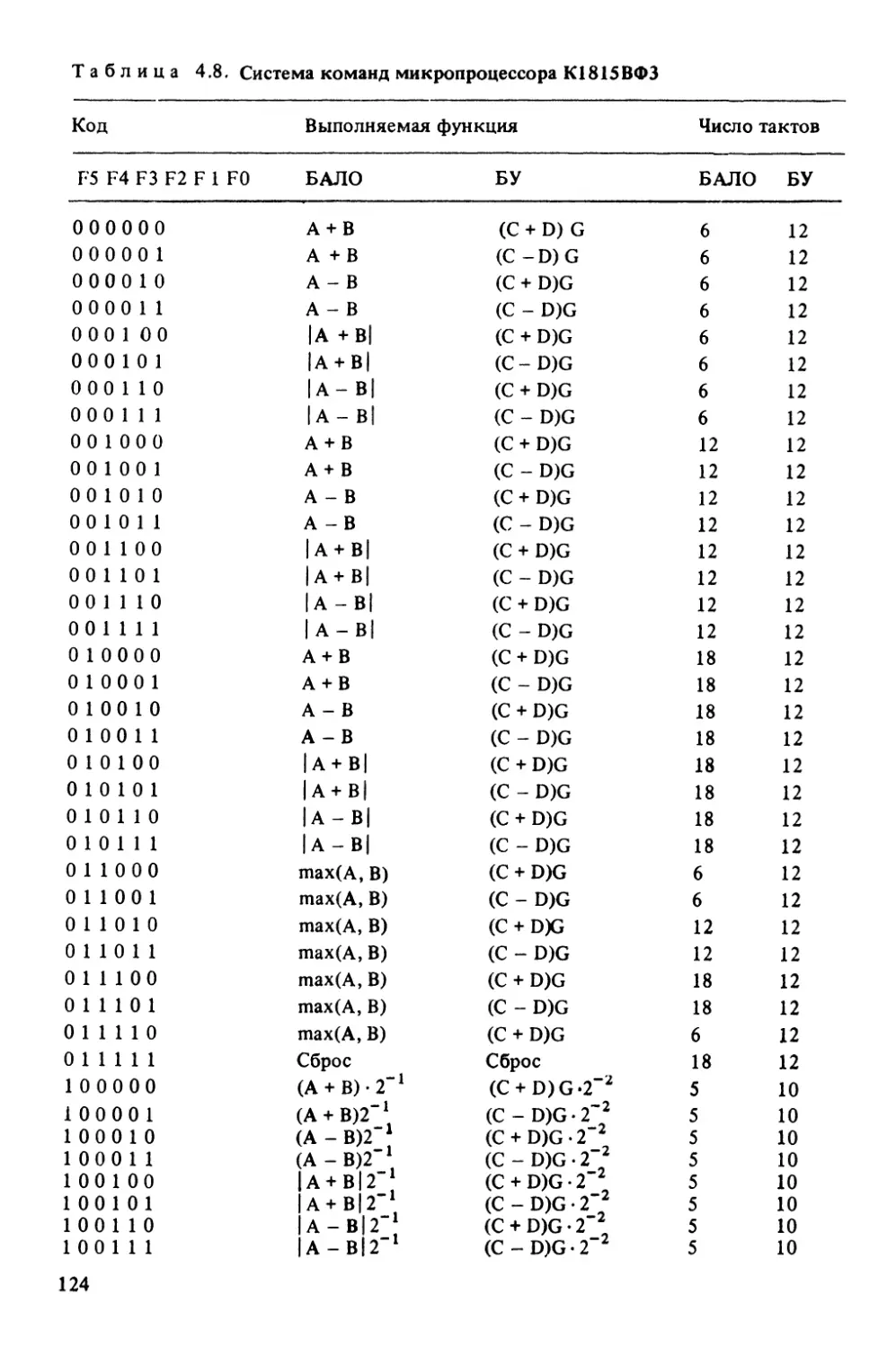

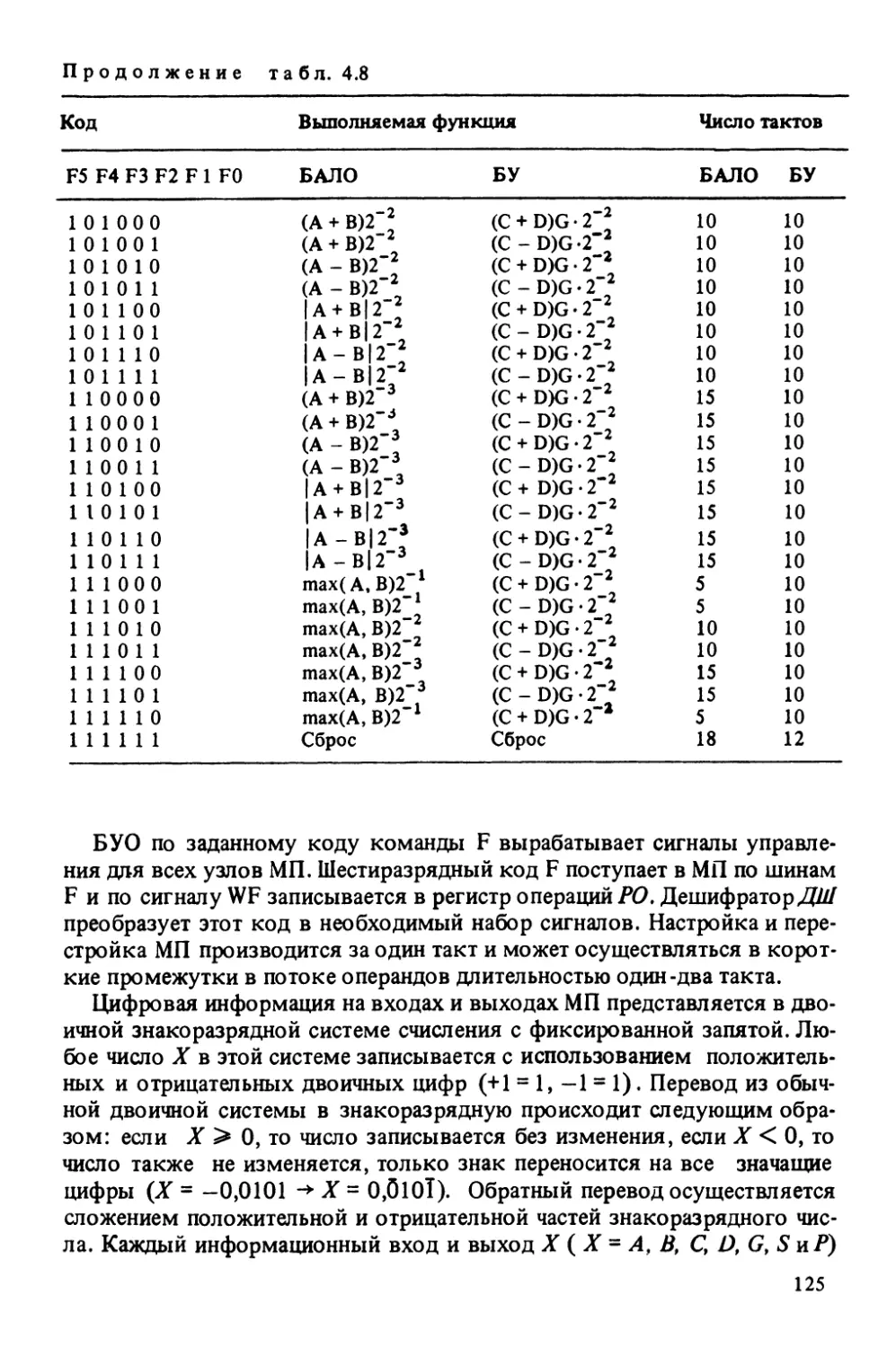

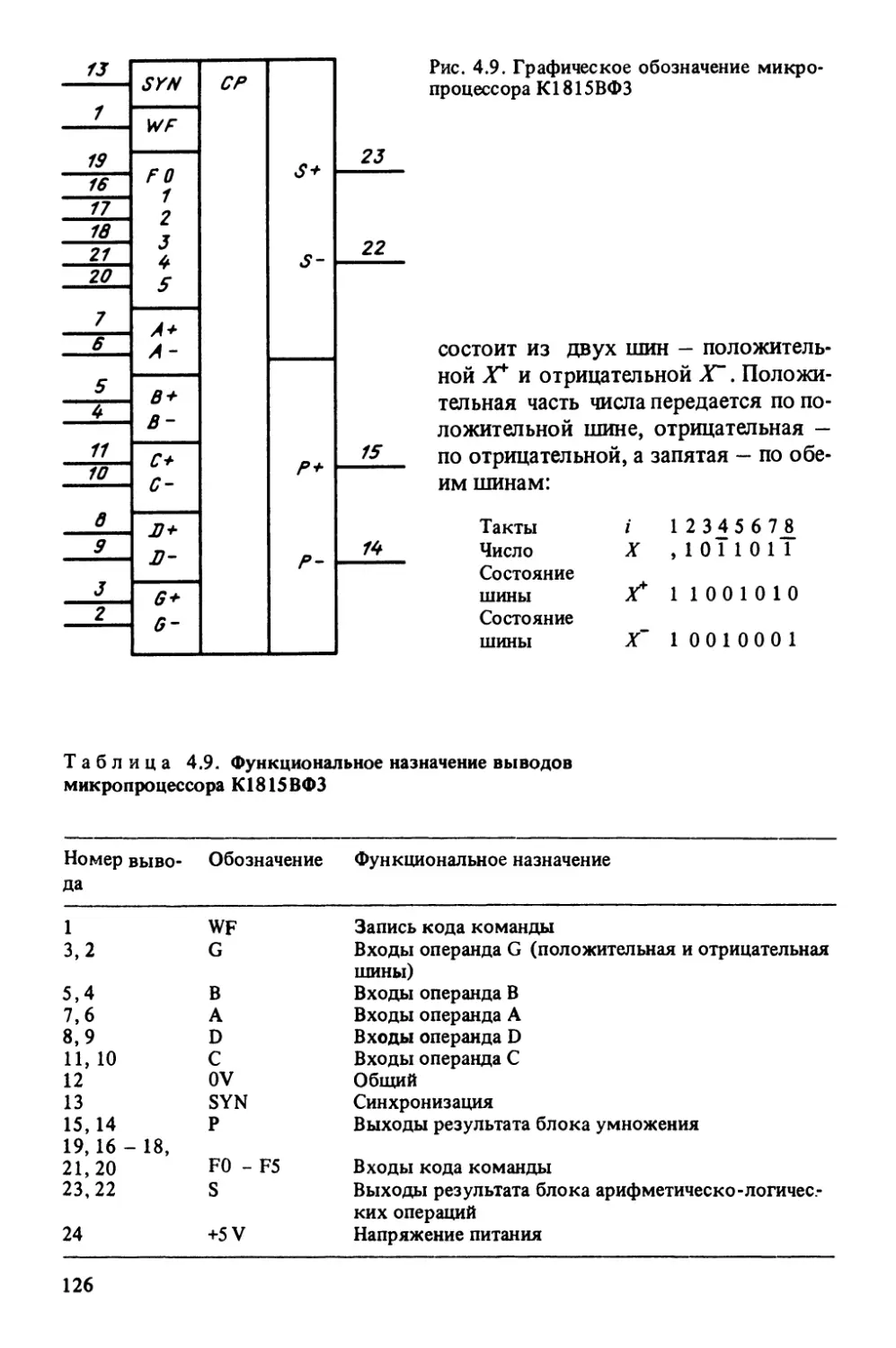

Система команд микропроцессоров К1810ВМ86/ВМ88