Text

итм-вт

АН СССР

ВЫЧИСЛИТЕЛЬНАЯ

ТЕХНИКА ЗА РУБЕЖОМ

В 1985 ГОДУ

ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ

ИНСТИТУТ

ТОЧНОЙ МЕХАНИКИ И ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ

им. С. А. ЛЕБЕДЕВА АН СССР

ВЫЧИСЛИТЕЛЬНАЯ

ТЕХНИКА ЗА РУБЕЖОМ

В 1985 ГОДУ

Под общей редакцией

члена-корр. АН СССР Г. Г. Рябова

Москва-1986

УДК 681.322 (047.1 )

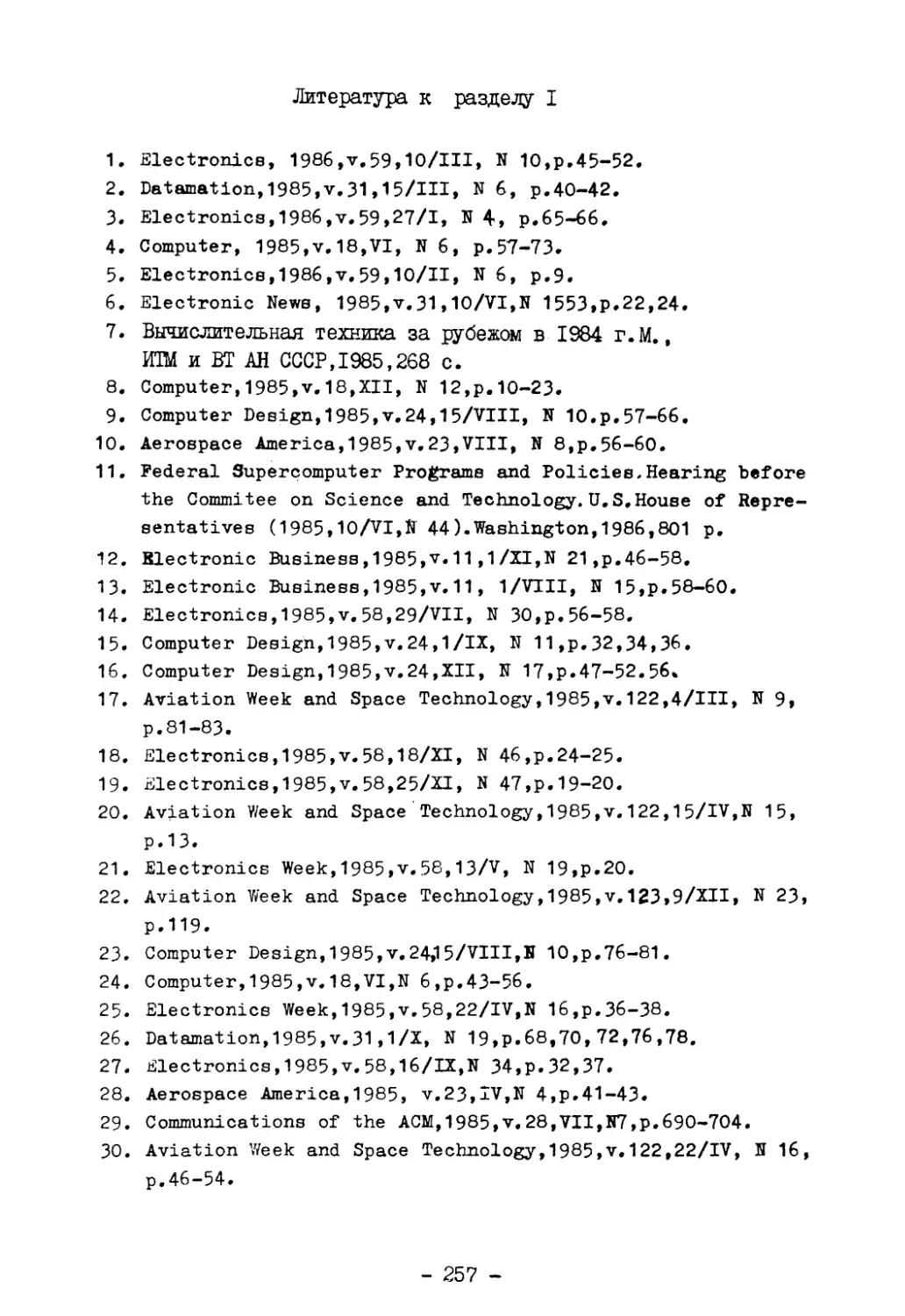

В данном 25-м выпуске ежегодного сборника от¬

ражены состояние и. тенденции развития зарубежной

высокопроизводительной вычислительной техники по

материалам 1985 и начала 1986 г.

055(02) 2

©ИТМ и ВТ АН СССР, 1986

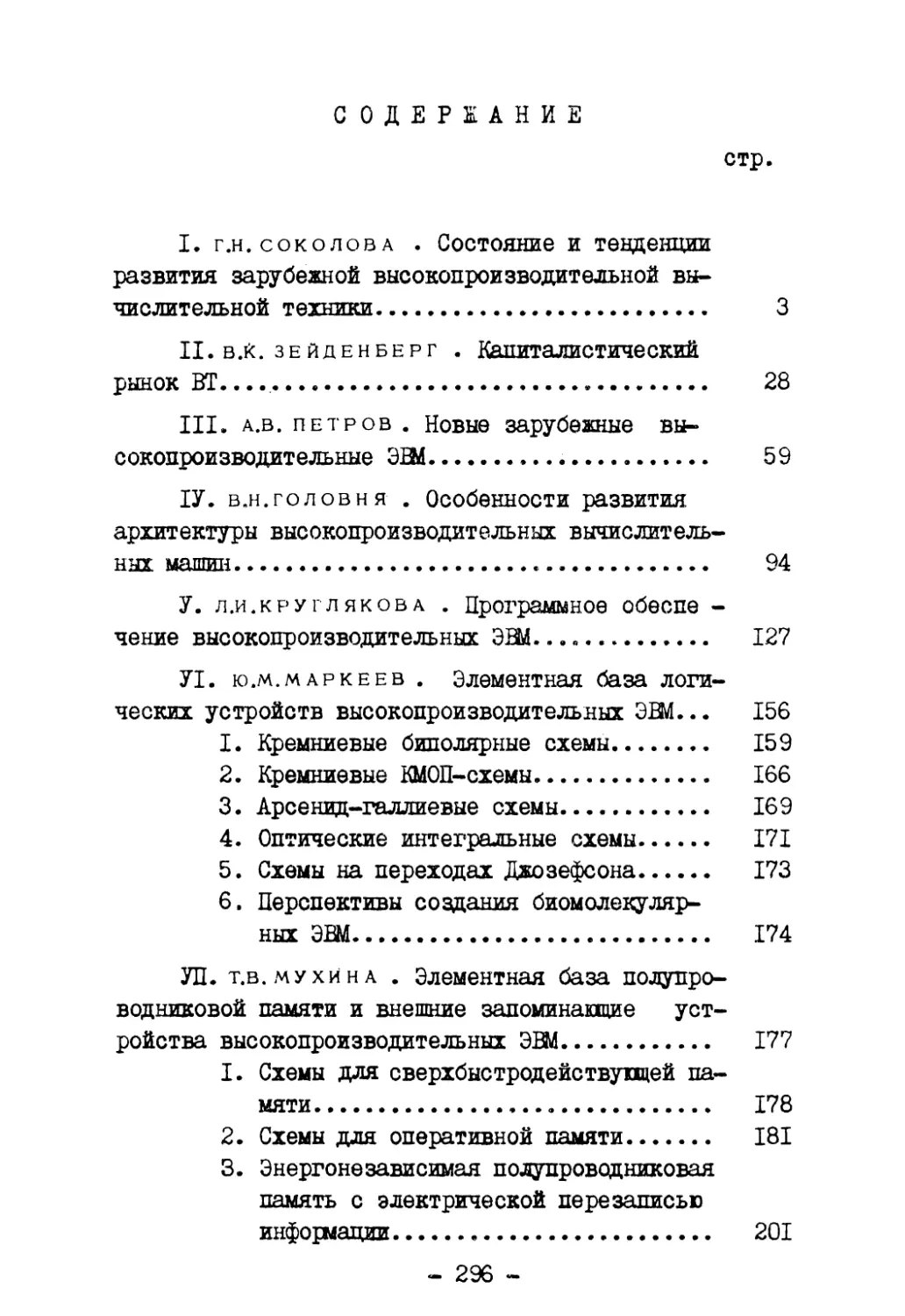

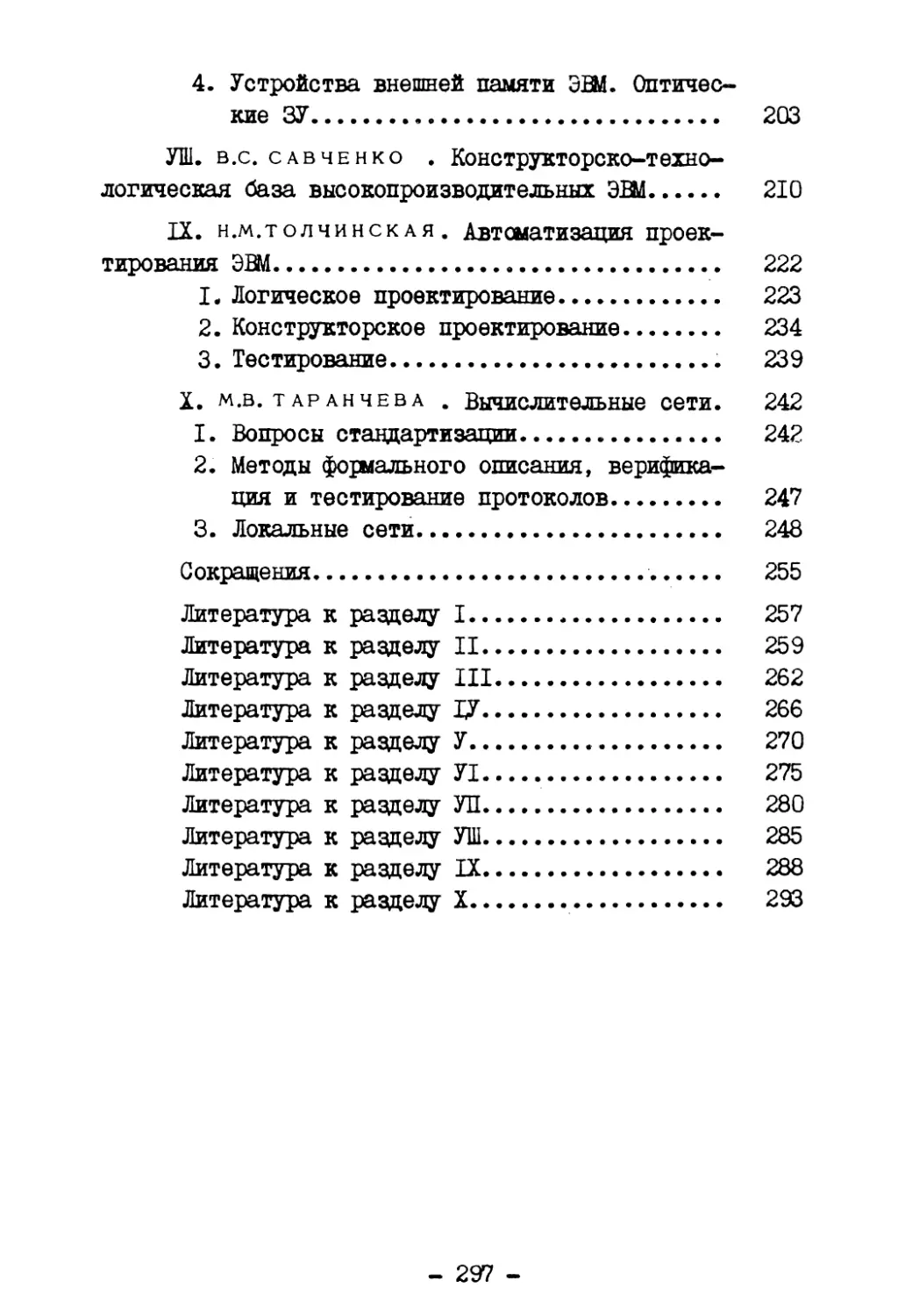

I

Г. H. Соколова

СОСТОЯНИЕ И ТЕНДЕНЦИИ РАЗБИТИЯ

заиъекной шсокопроизводатишюй ВЫЧИСЛИТЕЛЬНОЙ

ТЕХНИКИ

Мировой парк установленных к концу 1985 г. супер¬

ЭВМ насчитывал примерю 165 штук. Он представлен век¬

торными ЭВМ с конвейерной организацией Cray 1, Cray 2,

Cray Х-ИР фирмы Cray Эе search (116 ШТ.), супер—ЭВЫ Cy¬

ber 205 ФЦМ CDC-ETA Systems (ОКОЛО 40 ШТ.), единичными

векторными супер-ЭВМ фирм Fujitsu, Hitachi и BSC, не-

сколькими скалярными суперсистемами НЕР-1 фирмы Denel-

сог и специализированными суперсистемами типа мрр фир¬

мы Goodyear Aerospace. В настоящее врюмя фирме Cray Be¬

se ar ch принадлежит около 70% ряшка супер-ЭЕЫ, эти маши¬

ны проще других супер-ЭВМ в эксплуатации и имеют значи¬

тельное количество разработанных средств системного и

прикладного ПО. В 1985 г. свыше 30 тыс. пользователей

применяли супер»-ЭВМ Cray в режиме разделения вр»емени.

Предполагается дальнейшее быстрое увеличение парка су¬

пер-ЭВМ до 258 шт. в 1986 г. и 1675 (135О’‘)шт. к 1990 г.

/1-3/.

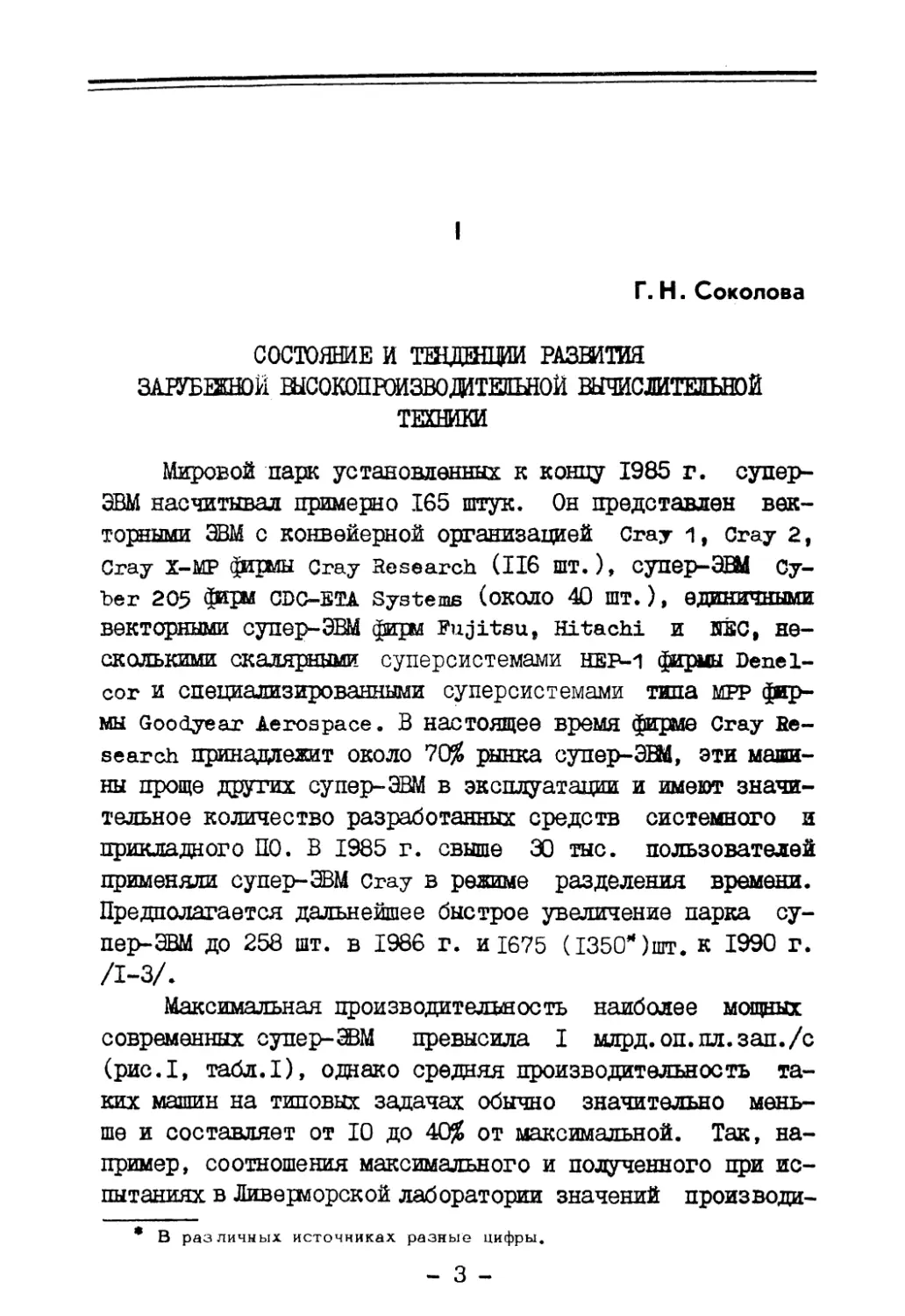

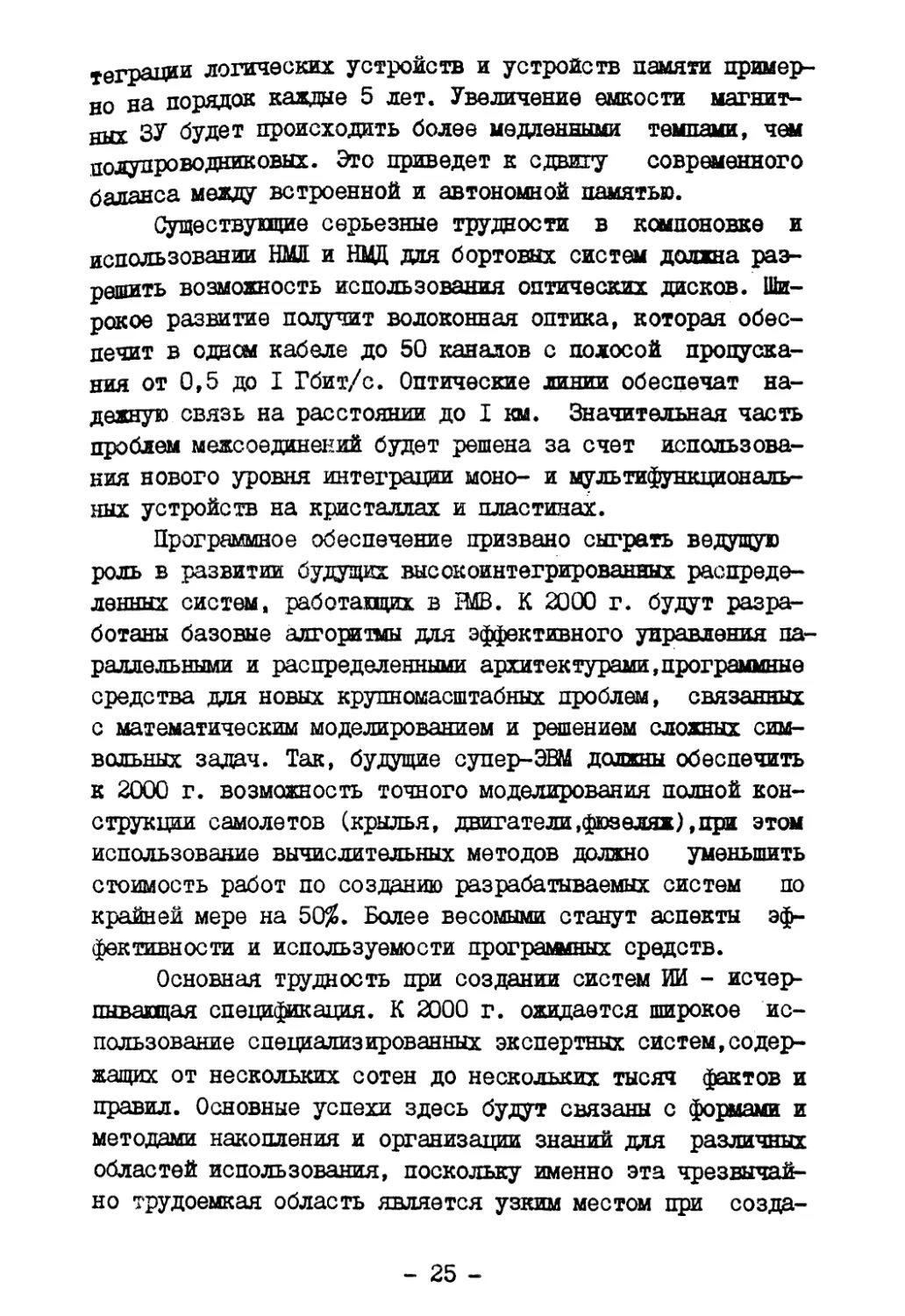

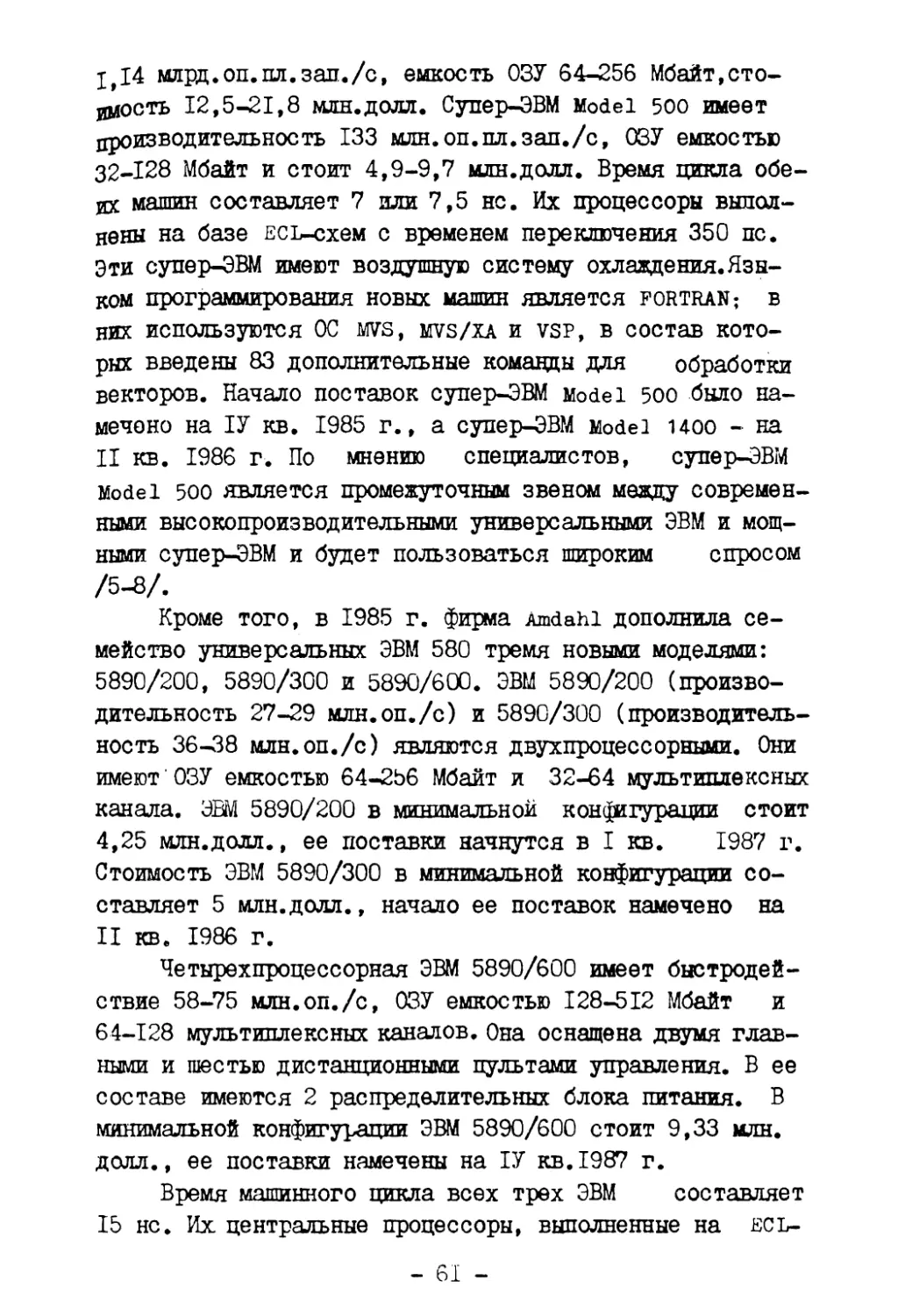

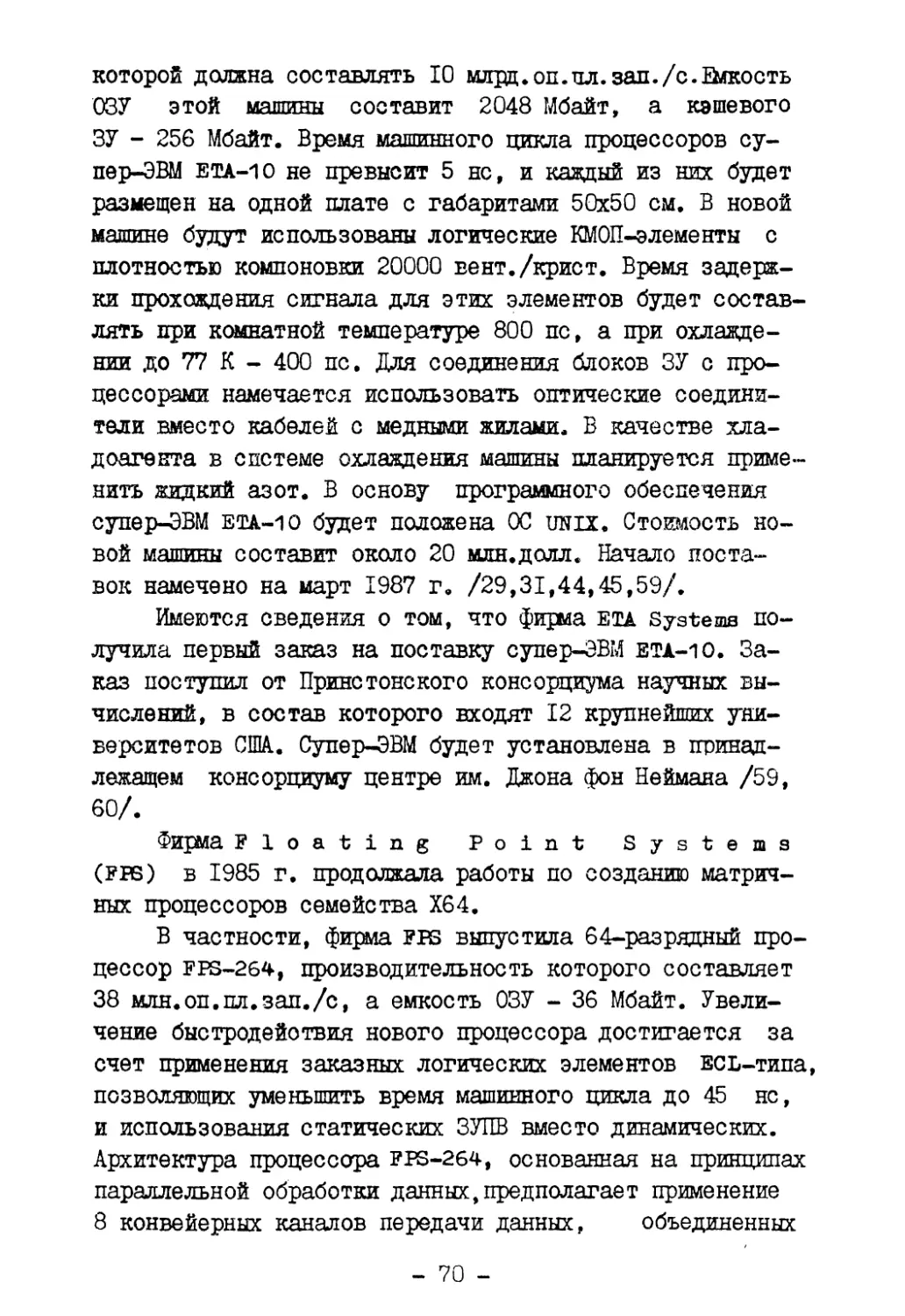

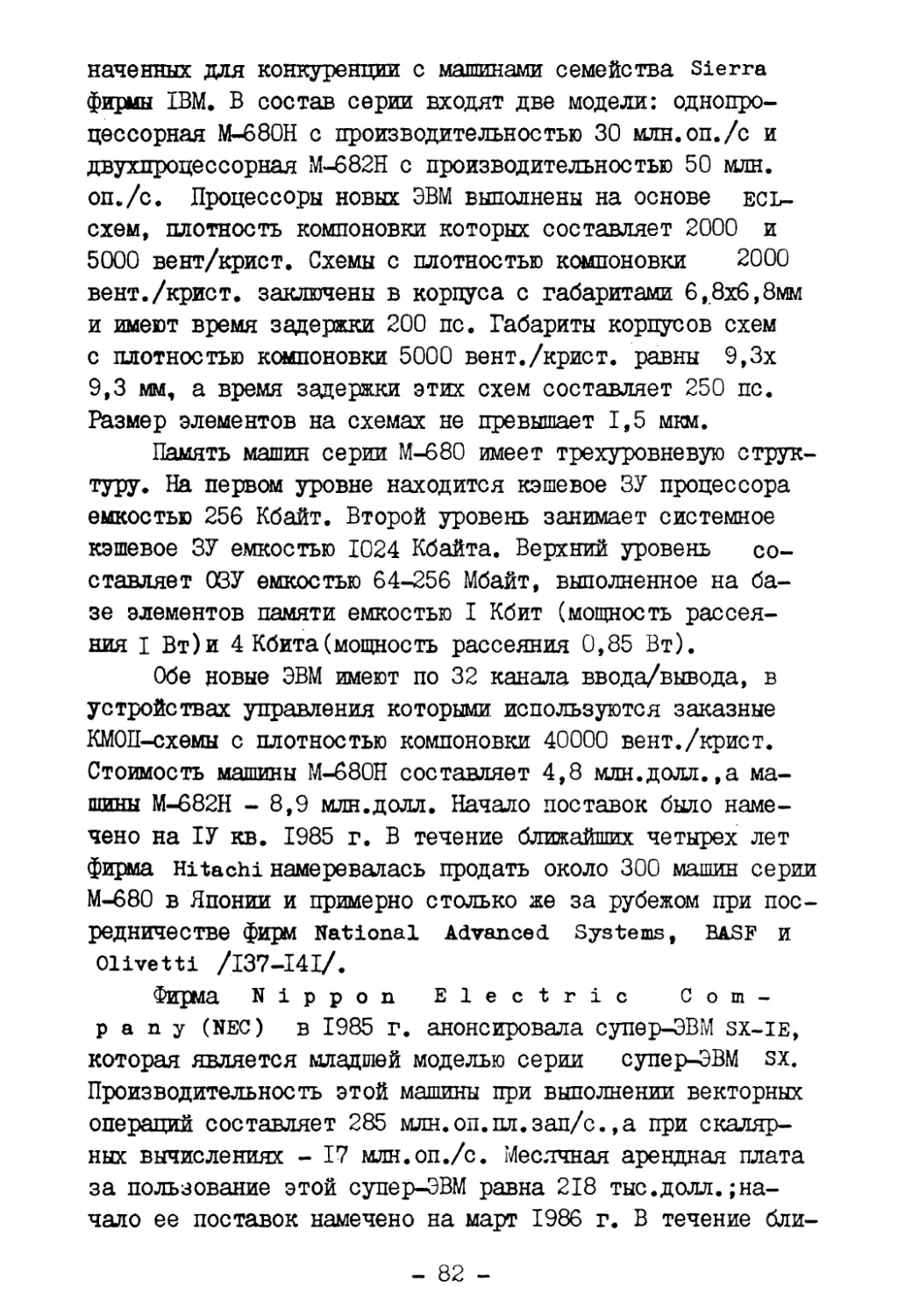

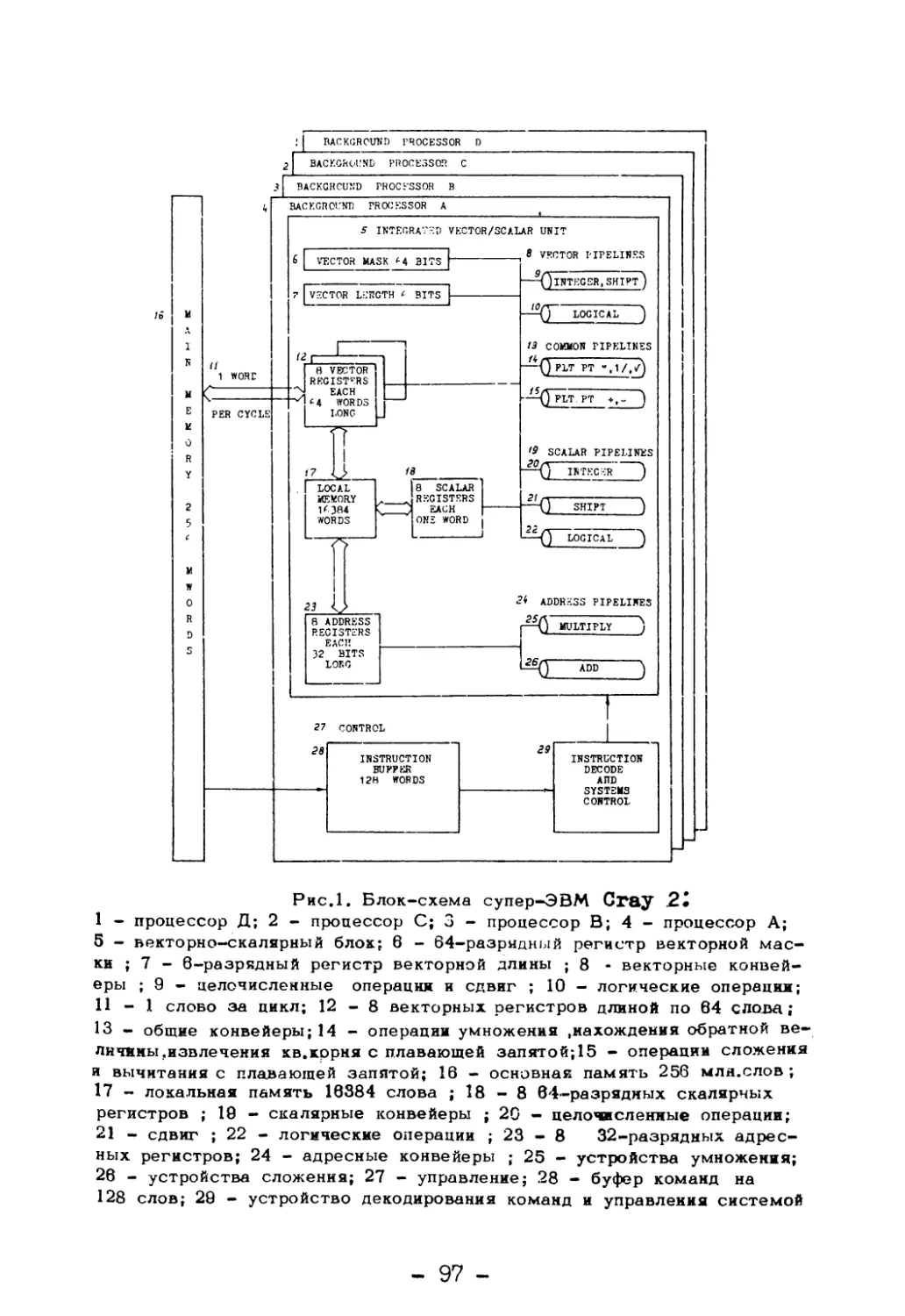

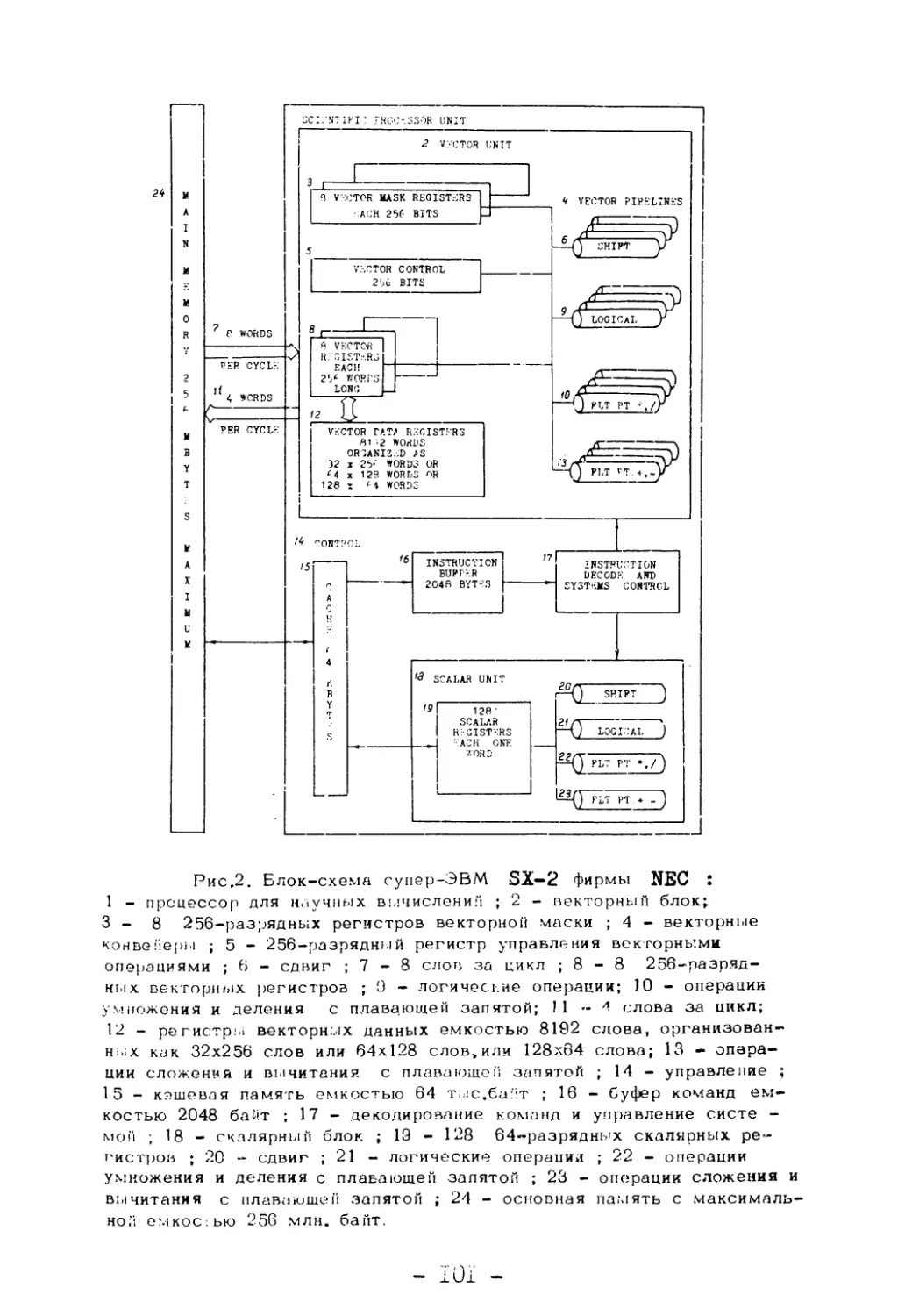

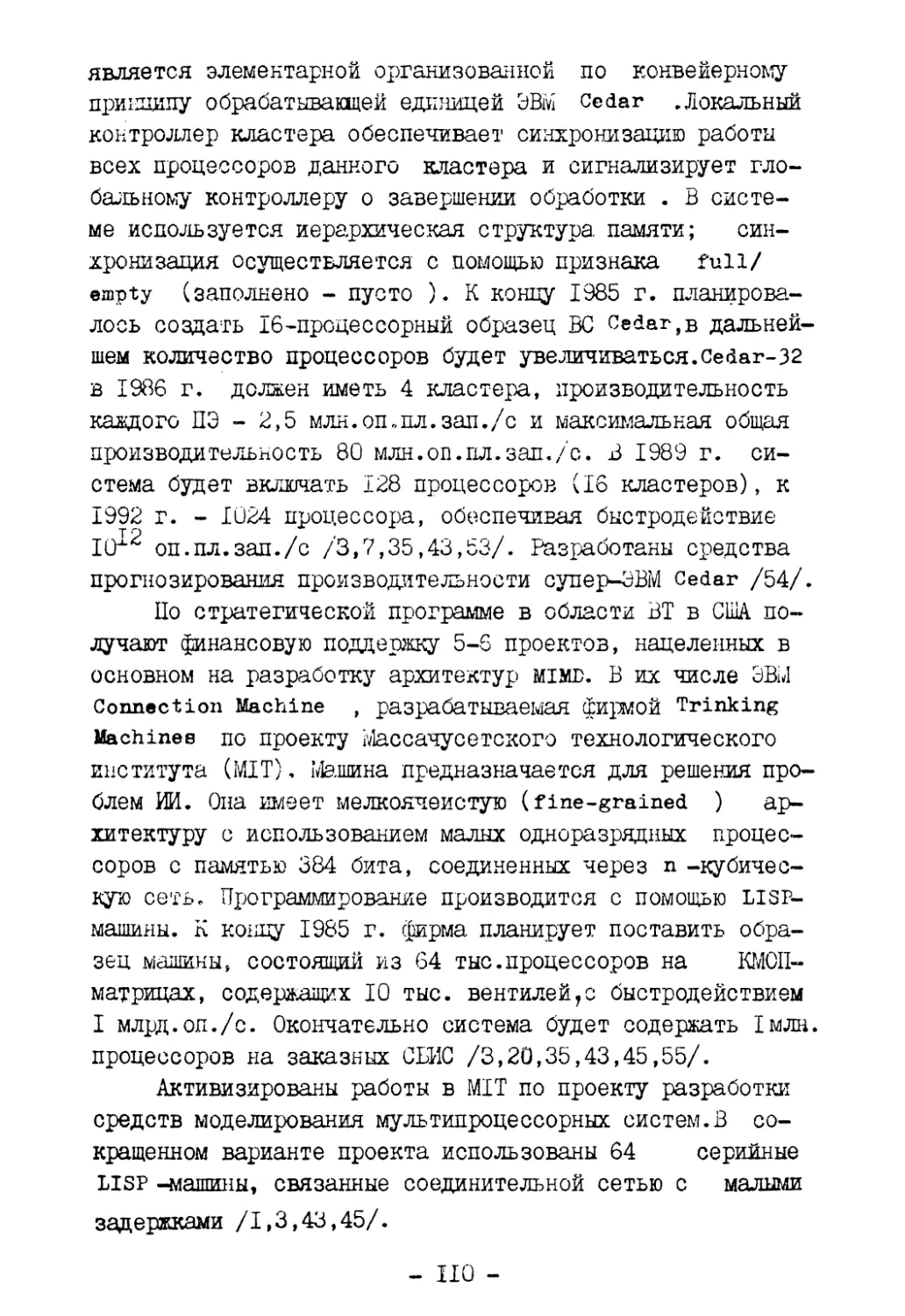

Максимальная производительность наиболее мощных

современных супер-ЭВМ превысила I млрд.оп.пл.зап./с

(рис.1, табл.1), однако средняя производительность та¬

ких машин на типовых задачах обычно значительно мень¬

ше и составляет от 10 до 40% от максимальной. Так, на¬

пример, соотношения максимального и полученного при ис¬

пытаниях в Ливерморской лаборатории значений производи-

* В различных источниках разные цифры.

- 3 -

тельности (в млн.оп.пл.зап./с) составили 1300 и 286 для

SX-2, 630 И 100 ДЛЯ 810/20 и 1000 И 161 ДЛЯ VP-400 /I,

4-7/.

CJr

ст

СЕ

m

•с

1 9 7 С

i 9 80

19 8 5 Дата

ПЕРВОЙ ПОСТАВКИ

Рис,, i . Динамик.'! разработок супер-ЭВМ

По-прежнему оольшой интерес в мире вызывают япон¬

ские супер-ЭВМ. В мае 1985 г. в Лос-Аламосской лабора¬

тории (США) были проведены очередные сравнительные ис¬

пытания японских супер-ЭВМ VP-200 (ддомы Fujitsu) и

8-810/20 ‘.фирмы Hitachi), совместимых по ПО с ЭВМ фир¬

мы IBM, с супер-ЭВМ Cray х-мр. Был использован типовой

- 4 -

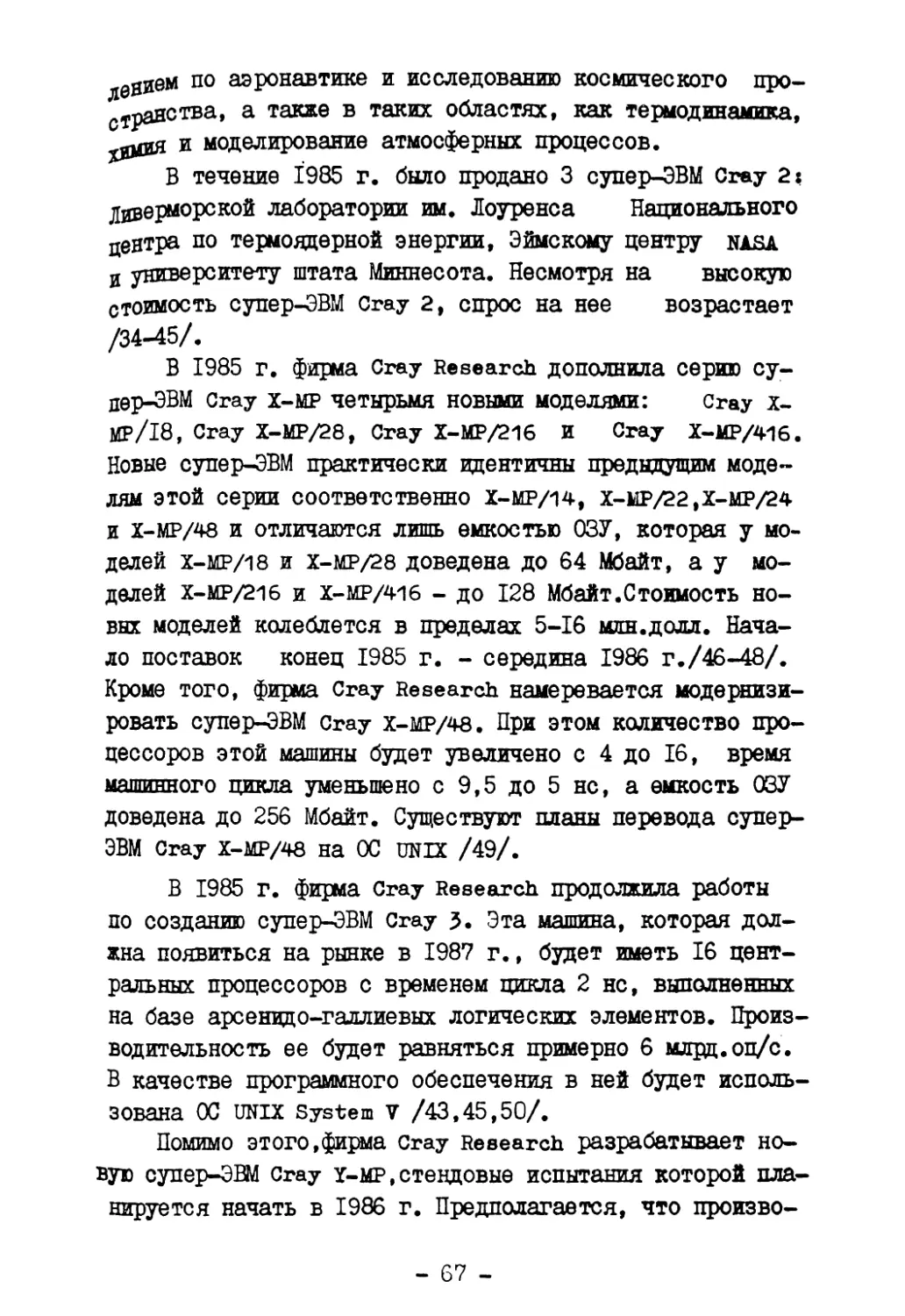

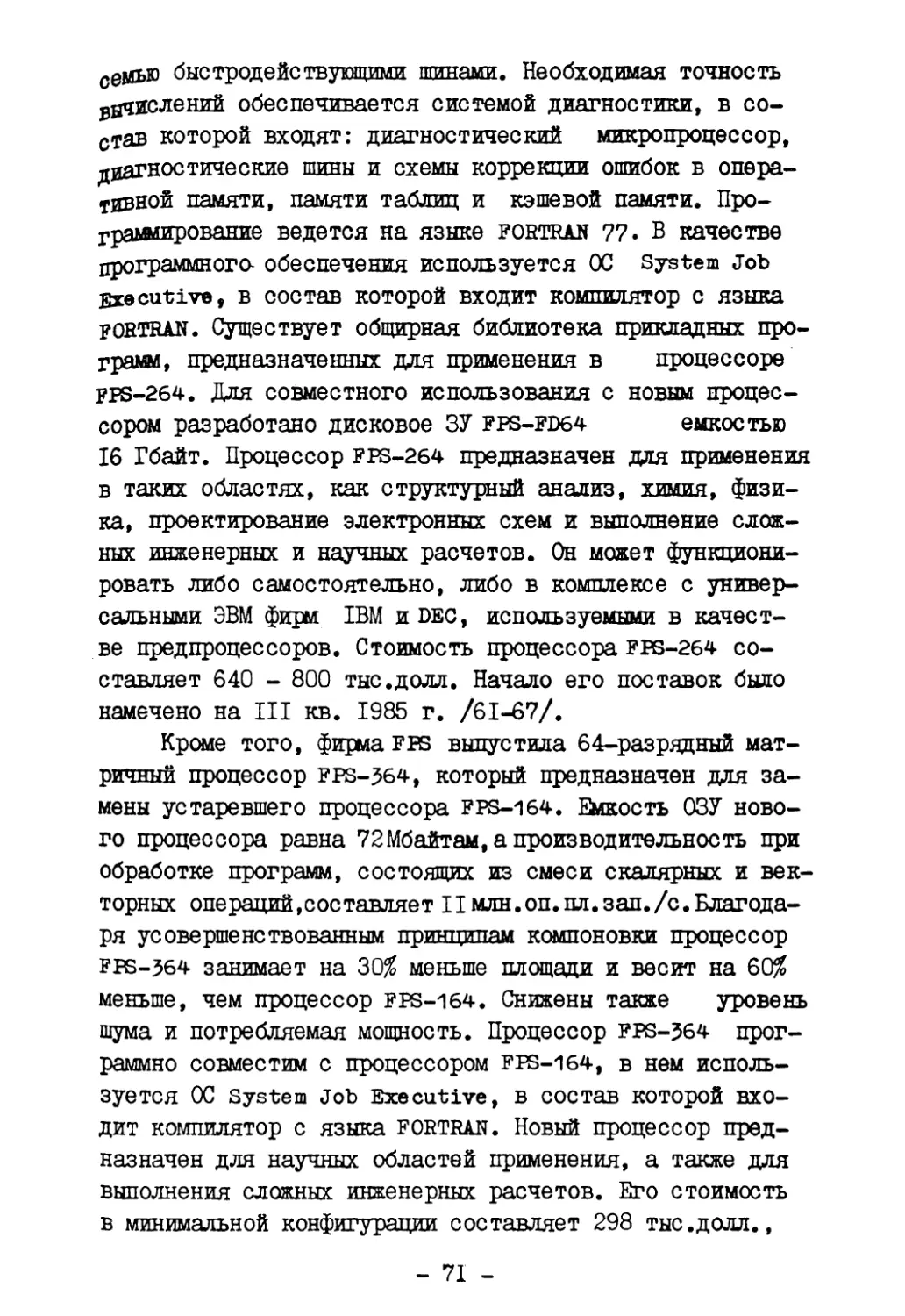

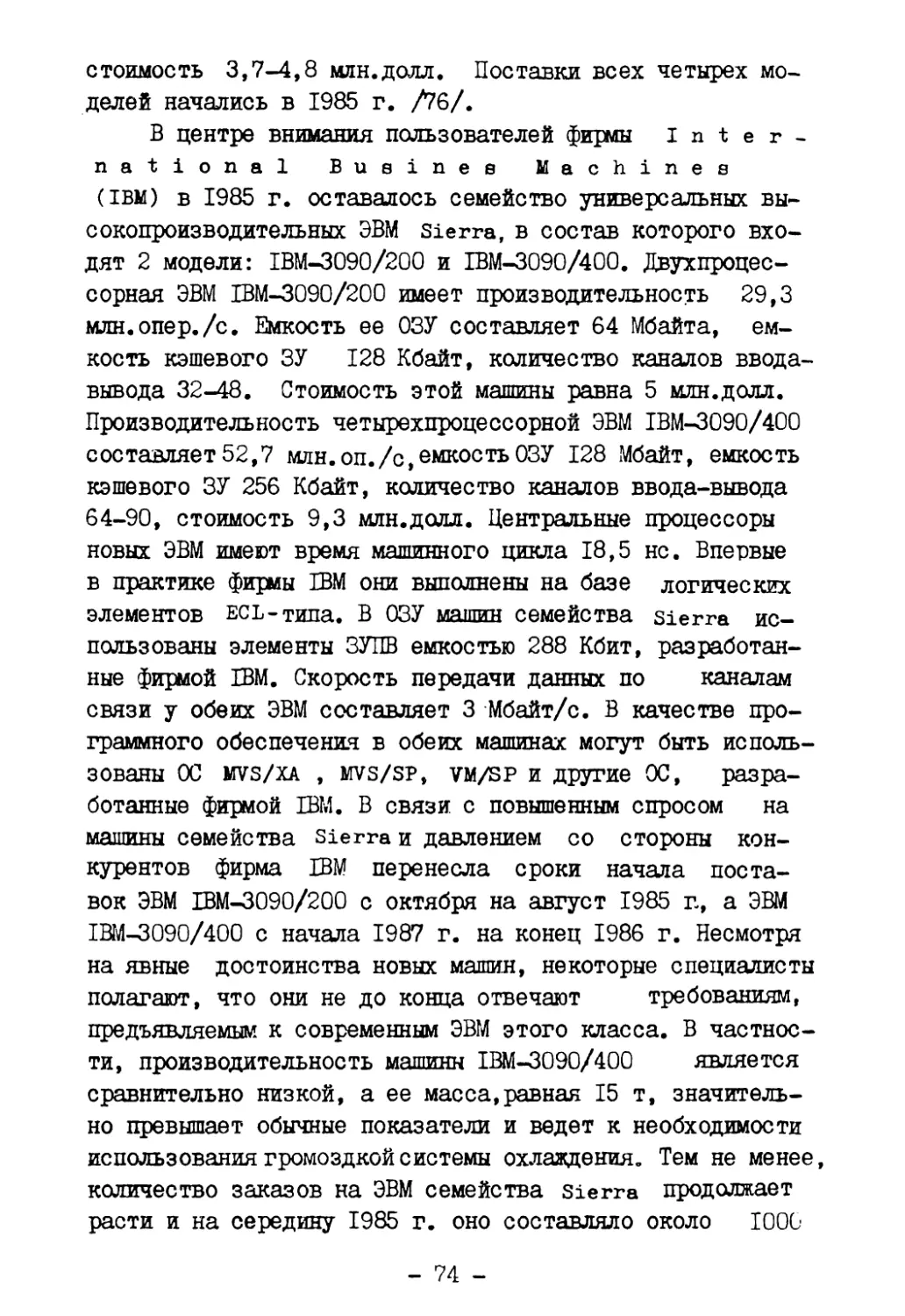

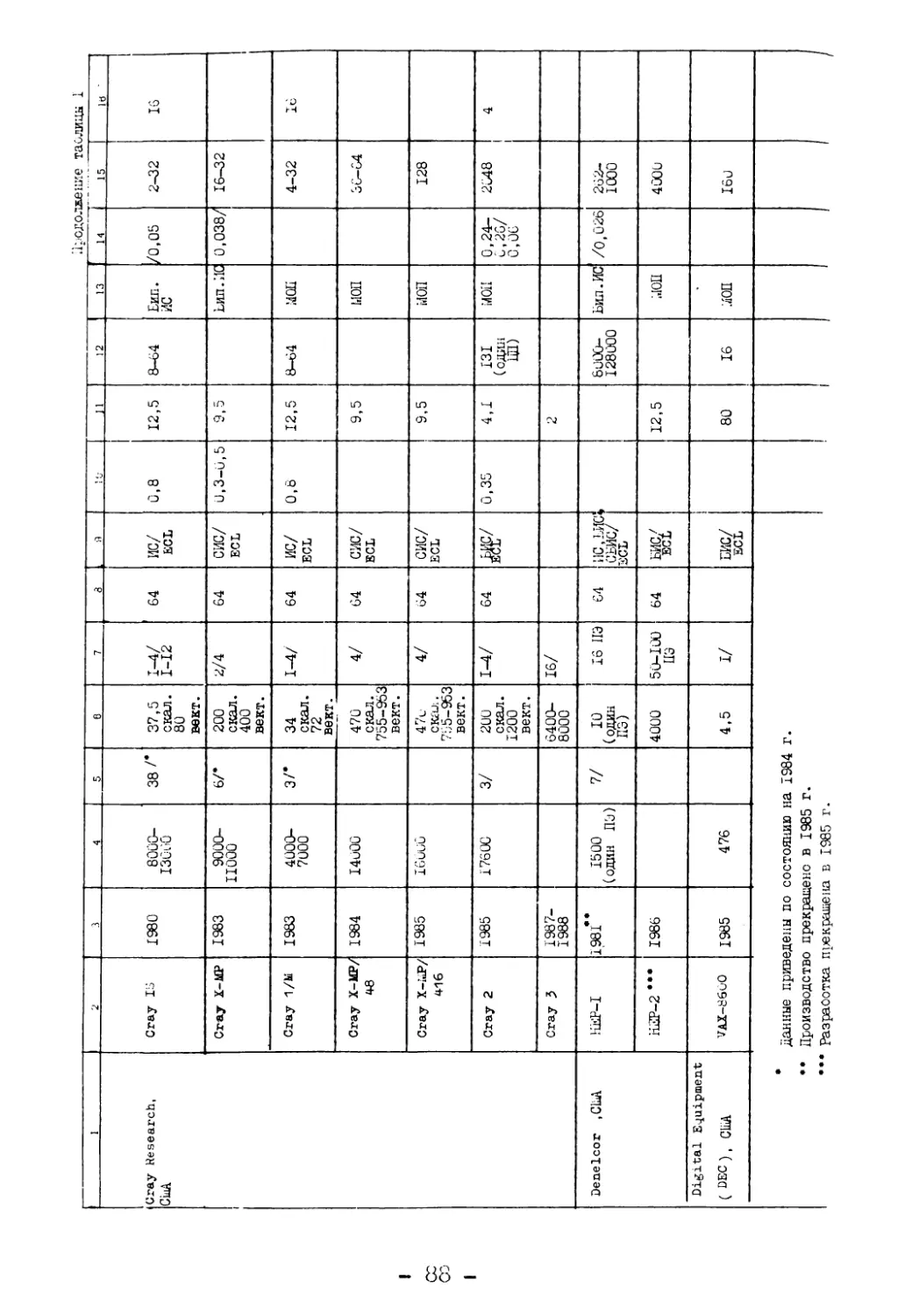

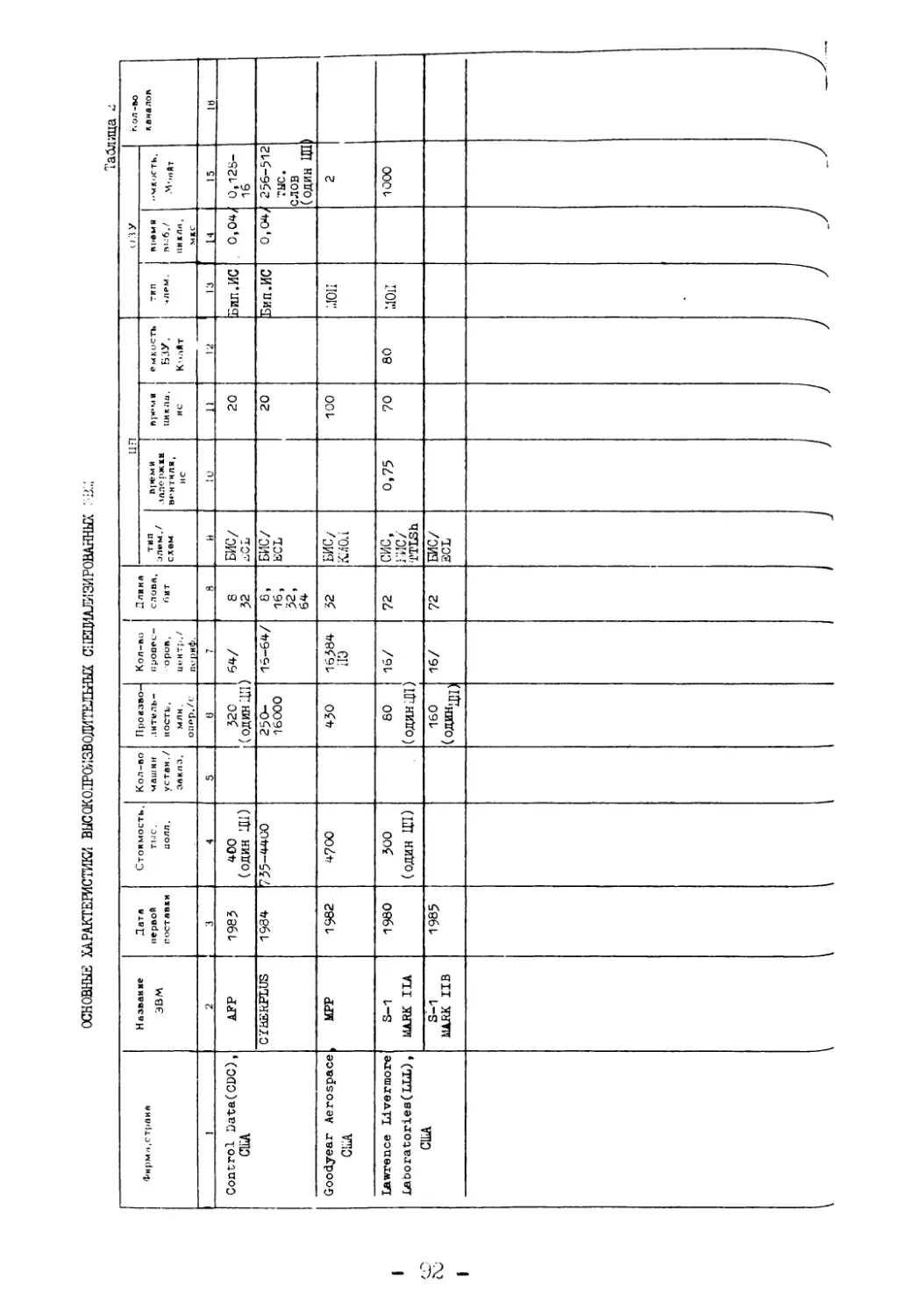

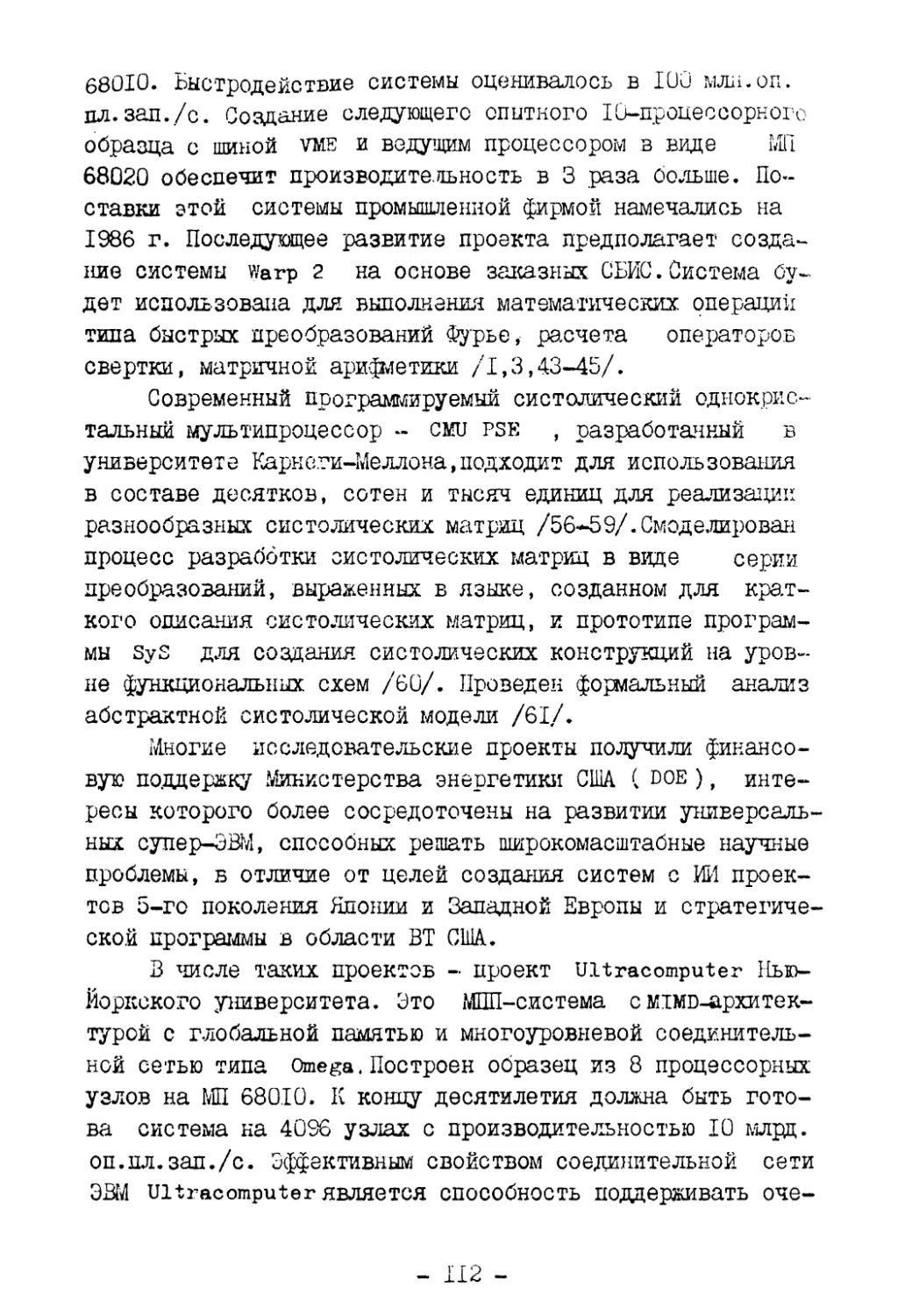

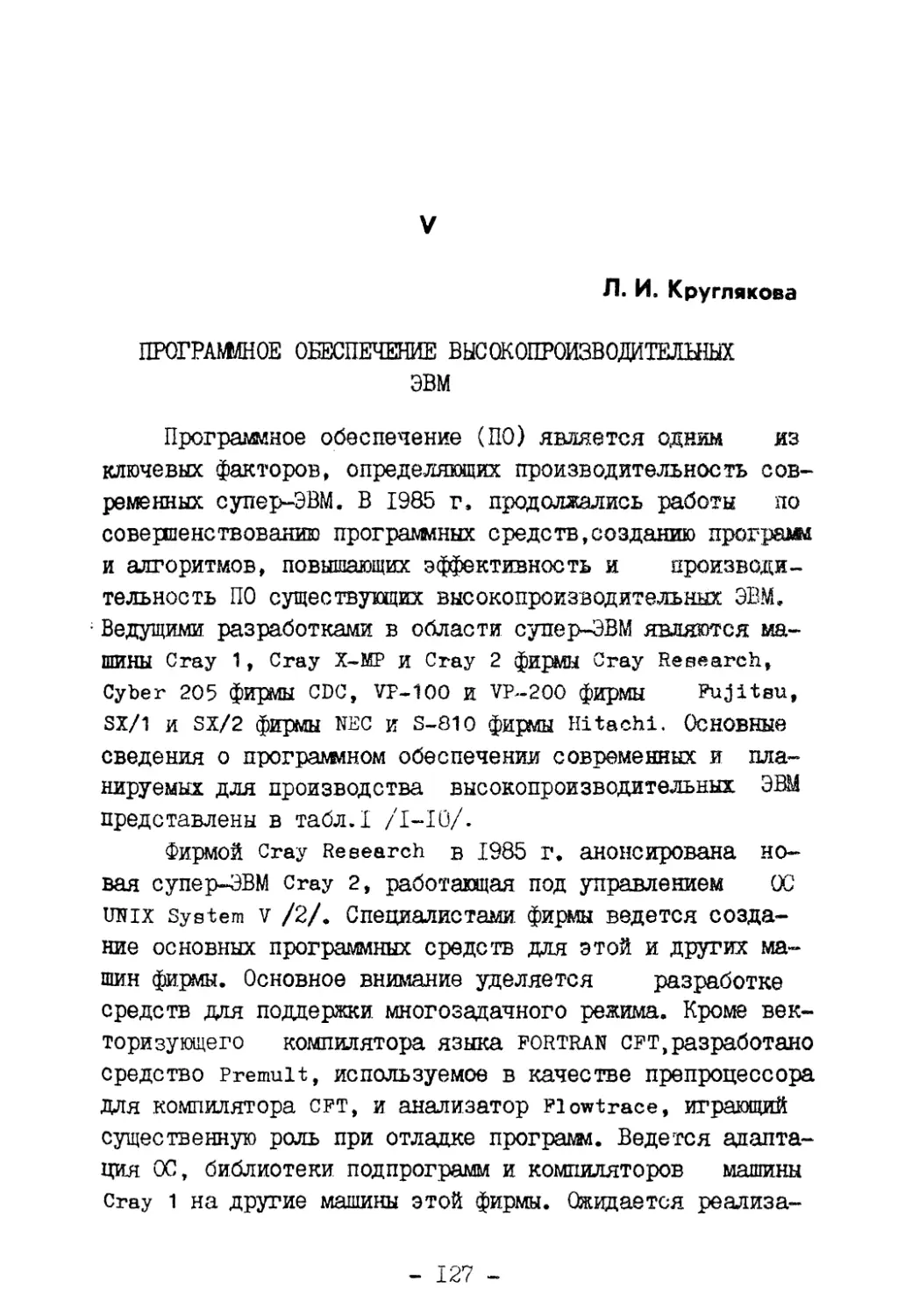

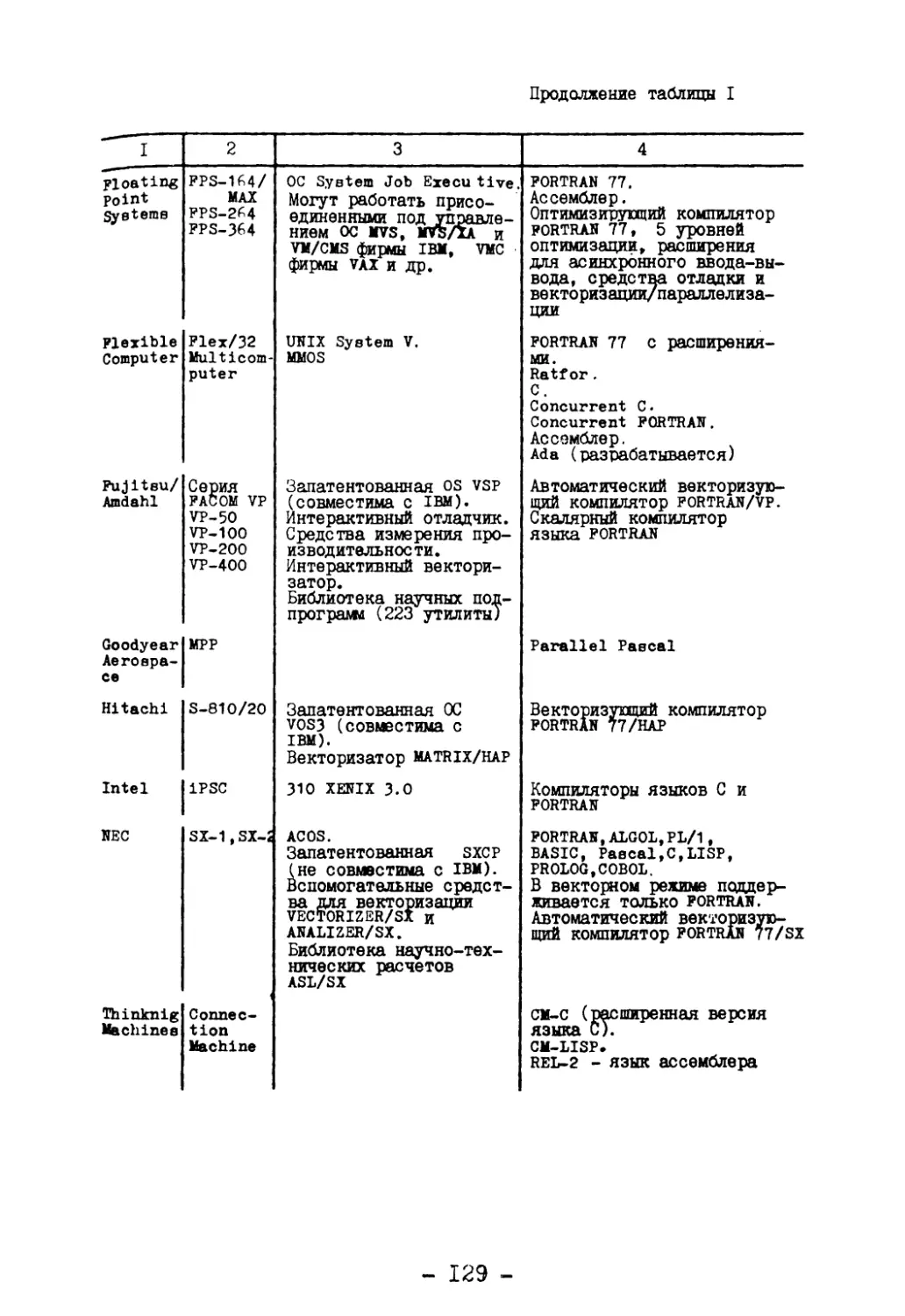

Таблица I

Современные супер-ЭВМ

Фирма,

страна

Название

супер-ЭВМ

дата

первой

постав¬

ки

Стои¬

мость

млн.

долл.

Кол-во

машин

устан./

заказ.

Максималь¬

ная произ¬

водитель¬

ность ,

млн.оп./с

Кол-во

процес¬

соров

Емкость

ОЗУ,

Мбайт

Тип

архитек¬

туры

Amdahl,

США

Model 1100*

1985

7,7-

12,5

3/1

267

128

Конвейерная

Model 1200*

1985

10,7-

20

2/1

533

I

256

Конвейерная

Model 1400*

1986

12,5-

114 и

64-256

Конвейерная

21,8

Control

Cyber 205

1981

5-12

40/

г 5U

1

8-65

Конвейерная

Data,

(скалярн.)

скалярн.

США

400’

I

(векторы.)

векторы.

Cray

Cray I-MP-

1983

9-16

16/

470

1-4

32-128

Конвейерная,

Research,

(скалярн.)

многопроцес¬

США

1000

(векторы.)

сорная

Cray 2

1985

17,6

3/

200

4

2048

Конвейерная,

(скалярн.)

многопроцес¬

1200

(векторы.)

сорная

Cray 3

1987

6000

16

Конвейерная,

(векторы.)

многопроцес -

сорная

ETA

ETA-10

1987

20

/I

2000-3000

8

2048

Конвейерная,

многопроцес¬

Systems,

(скалярн.)

США

10000

сорная

(векторы.)

IBM,США

GF-11**

1985

II520

576

1125

Многопроцес¬

(векторы.)

сорная

RP3***

1987

1000

512

Многопроцес¬

сорная

Pujitsu,

PACOM VP-100

1983

8 ■

9/

250

I

128

Конвейерная

Япония

.(векторы.)

PACOM VP-200

1983

11,3

5/

500

1

256

Конвейерная

(векторы.)

FACOM VP-400

1985

/17

1140

256

Конвейерная

(векторы.)

Hitachi,

S-810/10

1983

315

128

Конвейерная

Япония

► 1/9

(векторы.)

S-810/20

1984

630

256

Конвейерная

(векторы.)

NEC,

SX-1

1984

570

256****

Конвейерная

Япония

> 2/5

(векторы.)

SX-2

1985

1300

256****

Конвейерная

(векторы.)

♦ Разработка фирмы Fujitsu , предназначенная для реализации в США.

*♦ Целевая разработка.

*** Экспериментальная разработка.

♦*♦• Имеется расширяемая память емкостью 2048 Мбайт.

- 5 -

набор из 10 Fortran-программ, содержащих каадая от 400

до 3000 строк. Подтверждена сильная зависимость произ¬

водительности супер-ЭВМ от доли векторных вычислений, а

также соблюдение "закона Амдала" для векторного процес¬

сора.

По результатам проведенных испытаний в скалярном

режиме VP-200 и Cray х-мр оказались чрезвычайно быстры¬

ми машинами примерно равных вычислительных возможностей.

В векторном режиме для длинных векторов производитель¬

ность VB-200 была в 2-3 раза больше, чем у Cray х-мр.

Производительность s-810/20 оказалась примерно вдвое

меньше, чем у vp-200 и Cray х-мр как в скалярном, так и

векторном режимах /8/.

Существует несколько подходов при расчете произво¬

дительности многопроцессорных ВС, содержащих N процес¬

соров. На практике чаще используется "закон Амдала", в

соответствии с которым производительность ВС, реализую¬

щей быструю параллельную и более медленную последова¬

тельную обработку, лимитируется медленной составляющей,

что обеспечивает увеличение производительности N-про¬

цессорной системы в i/[f+(i-f)/n] раз, где f - доля

(в %) последовательных операций. Это означает, что даже

небольшая доля (~ 10%) последовательных операций резко

ухудшает производительность системы. Следовательно, для

создания высокопроизводительных параллельных ВС необхо¬

димо использовать соответствующее ПО и алгоритмы с вы¬

сокой степенью параллелизма. Показано, что при исполь¬

зовании разной степени распараллеливания производитель¬

ность многопроцессорной ВС может быть увеличена по срав¬

нению с однопроцессорной от 0,3 N раз (работы D.Kuck*а)

до практически N раз (0,94 » для системы Калифор¬

нийского технологического института с архитектурой Cos¬

mic Cube, содержащей 64 и 128 ПЭ) /9/.

Дальнейшего увеличения производительности разраба¬

тываемых супер)-ЭВМ фирмы Cray Research, ETA Systems,NEC,

Fujitsu, Hitachi планируют достичь за счет использова¬

ния архитектур с относительно небольшим числом высоко¬

- 6 -

производительных процессоров с оптимальным использова¬

нием векторной обработки, конвейерной организации, раз¬

витых систем памяти.

Следует отметить, что, несмотря на стабильное уве¬

личение производительности ЭВМ за 30 лет развития при¬

близительно в 10 раз каждые 5 лет, для решения сложных

крупномасштабных научных и инженерных проблем всегда

не хватало вычислительной мощности имеющихся средств.

Так, решение наиболее сложных проблем сегодня требует

от 500 до 1000 ч счета на супер-ЭВМ /4,10/. Кроме того,

большинство пользователей считают, что плата за супер¬

ЭВМ 10-20 млн.долл, или их аренда по цене от I до 8 тыс.

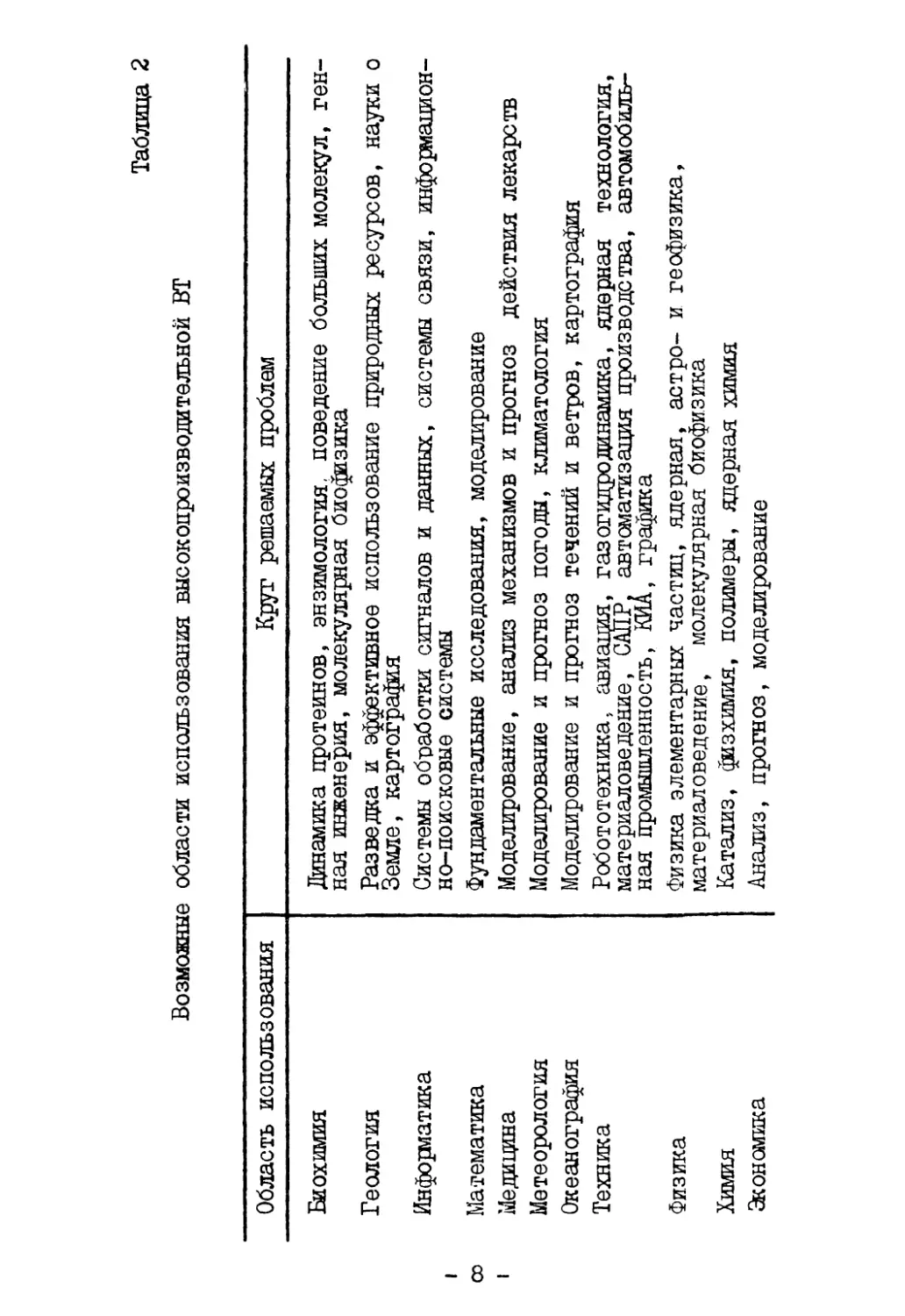

долл./ч для них слишком велика /9/. Появление в 1985 г.

на рынке средств ВТ минисупер-ЭВМ с соотношением произ-

водительность/стоимость примерно в 10 раз лучше, чал у

обычных супер-ЭВМ, может существенно изменить данную си¬

туацию. Минисупер-ЭВМ - модульно наращиваемые, сравни¬

тельно дешевые (до I млн.долл.) и доступные для пользо¬

вателя высокопроизводительные (40-60 млн.оп.пл.зап./с)

ВС на основе ОС unix с развитыми возможностями вектор¬

ной обработки должны существенно расширить сферы исполь¬

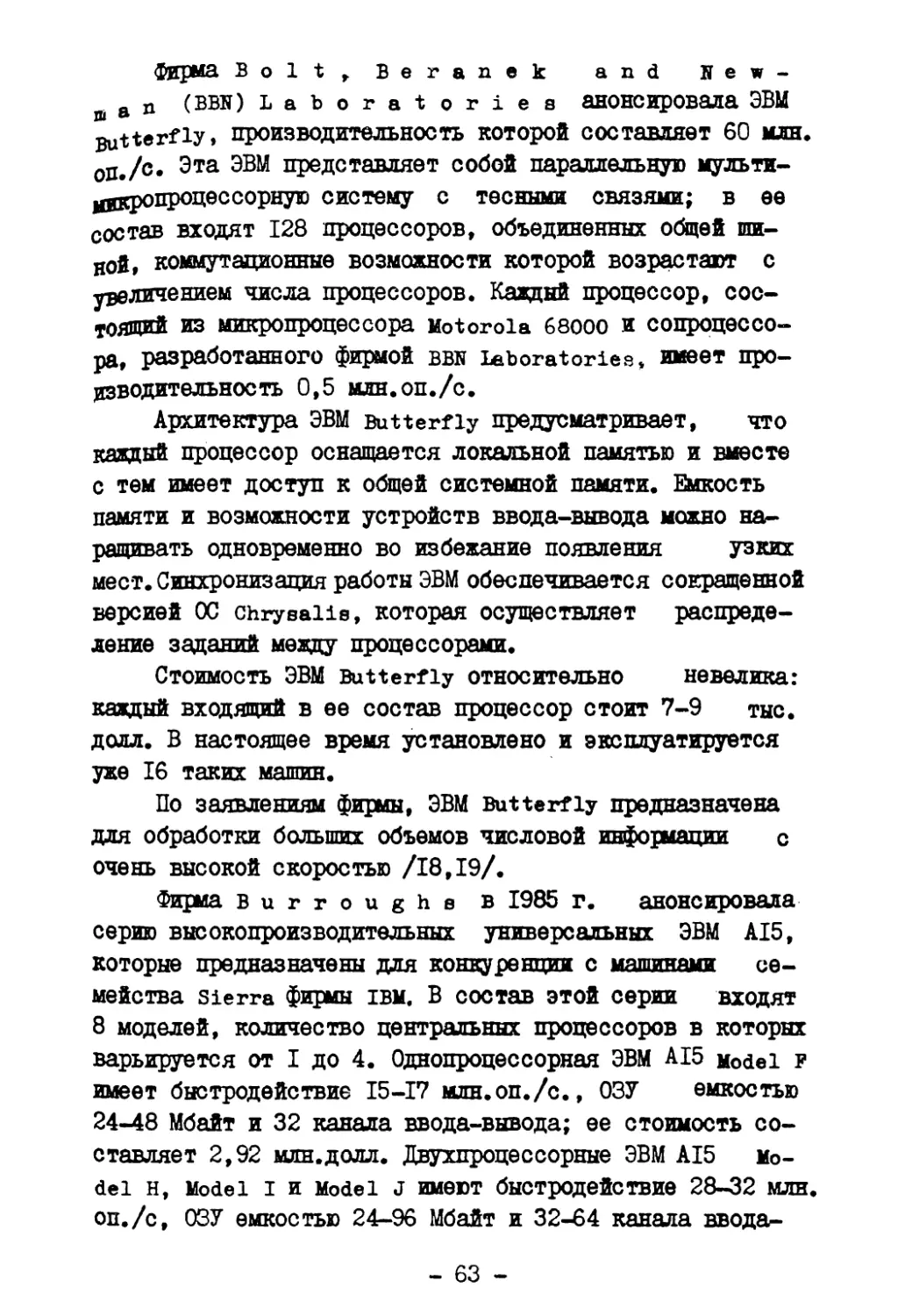

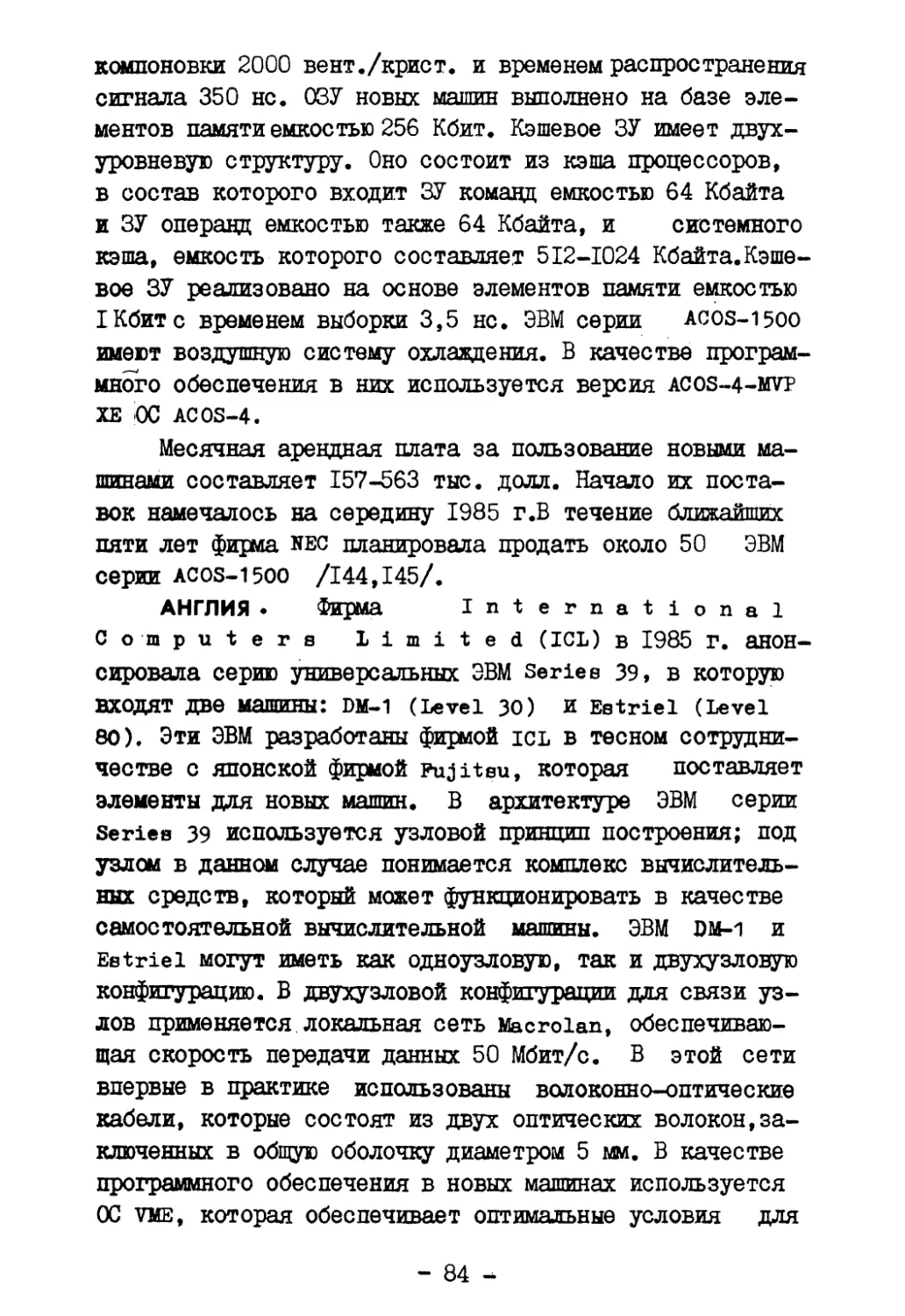

зования высокопроизводительной ВТ (табл.2) /II/.

Объем продаж минисупер-ЭВМ в 1985 г. составил 100-

125 млн.долл., в ближайшие годы для этого сектора рынка

средств ВТ ожидается максимальный темп роста (40-60% в

год); прогнозируемый к 1990 г. объем их продаж состав¬

ляет 1-1,1 млрд.долл./год /12,13/.

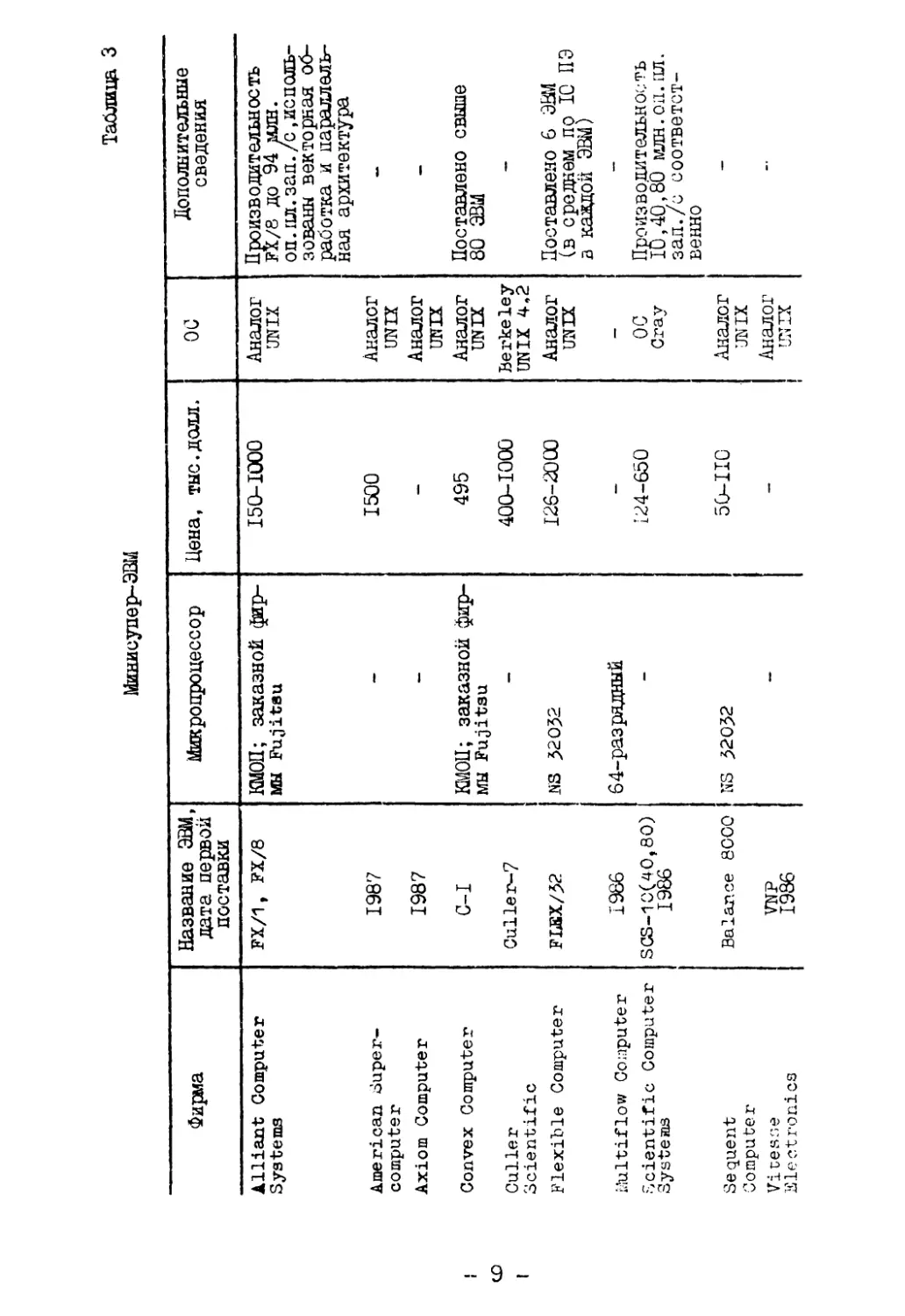

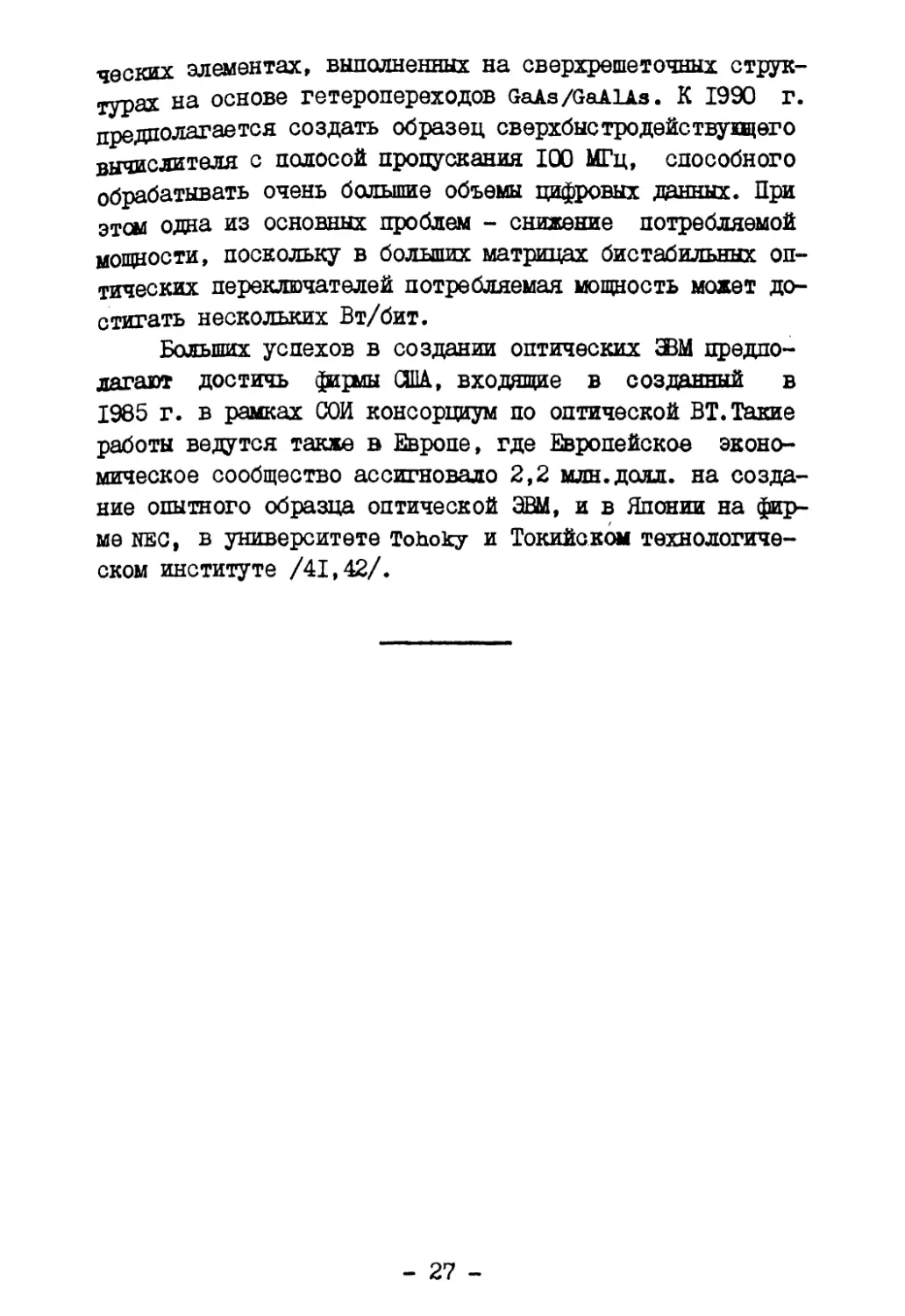

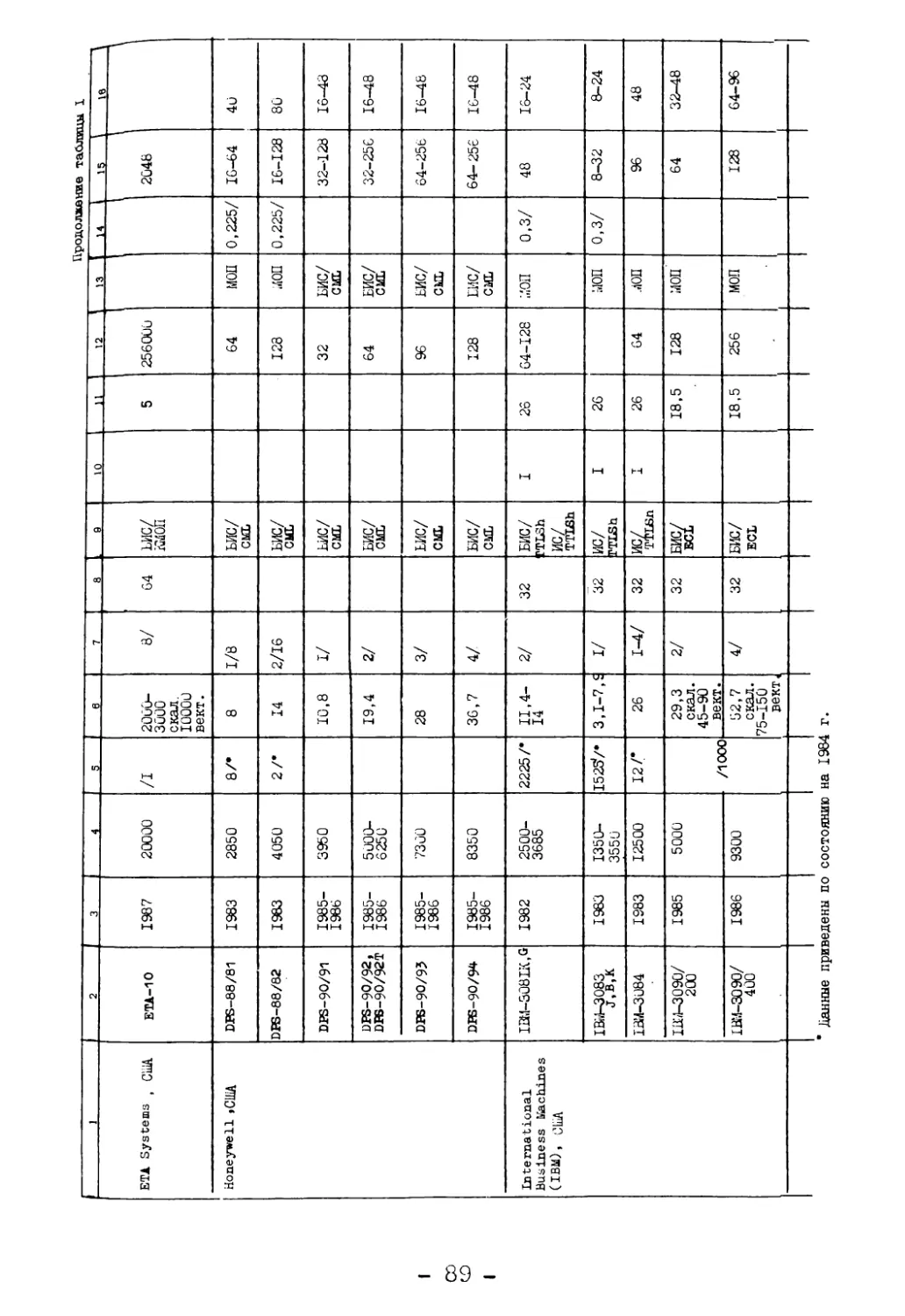

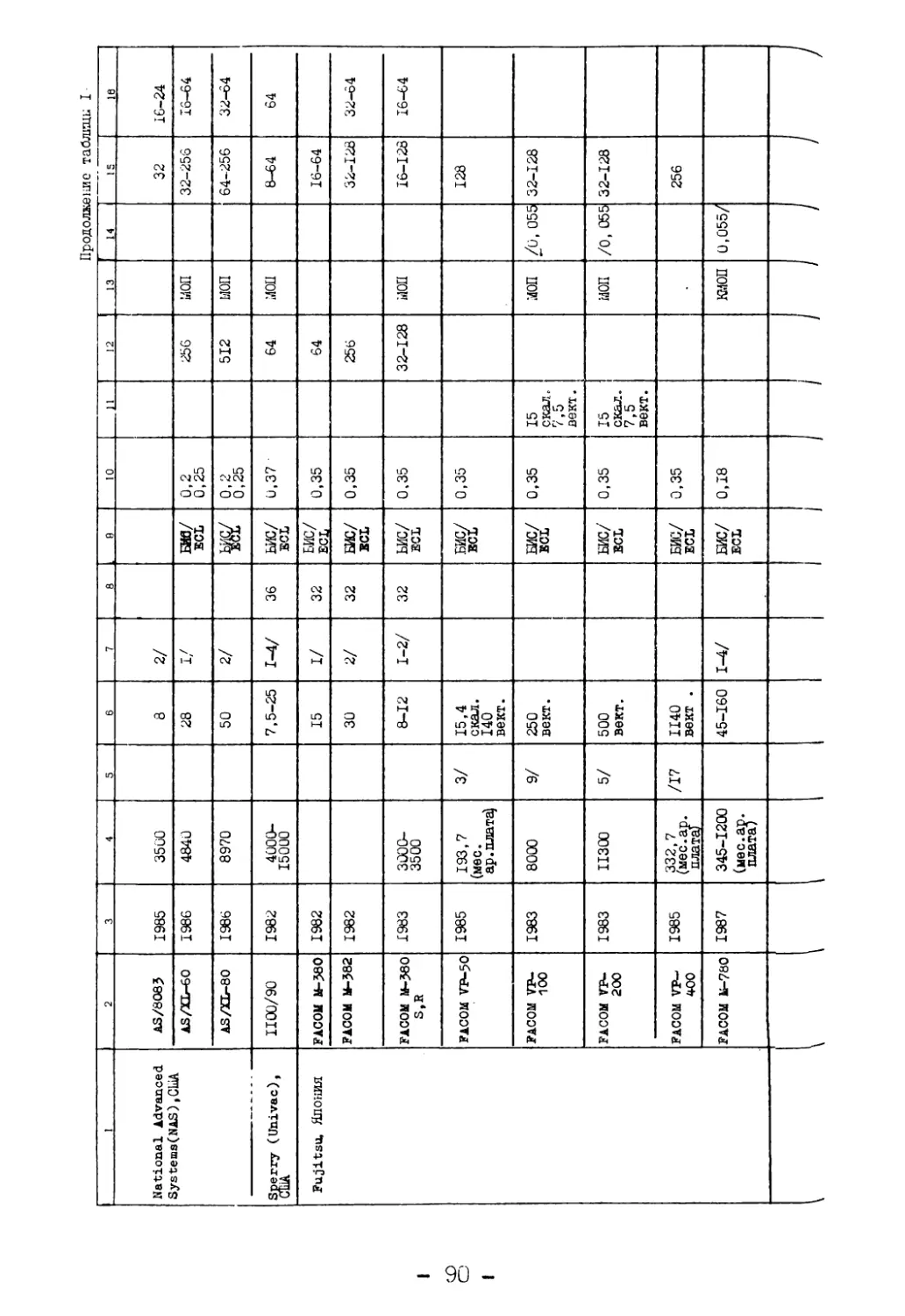

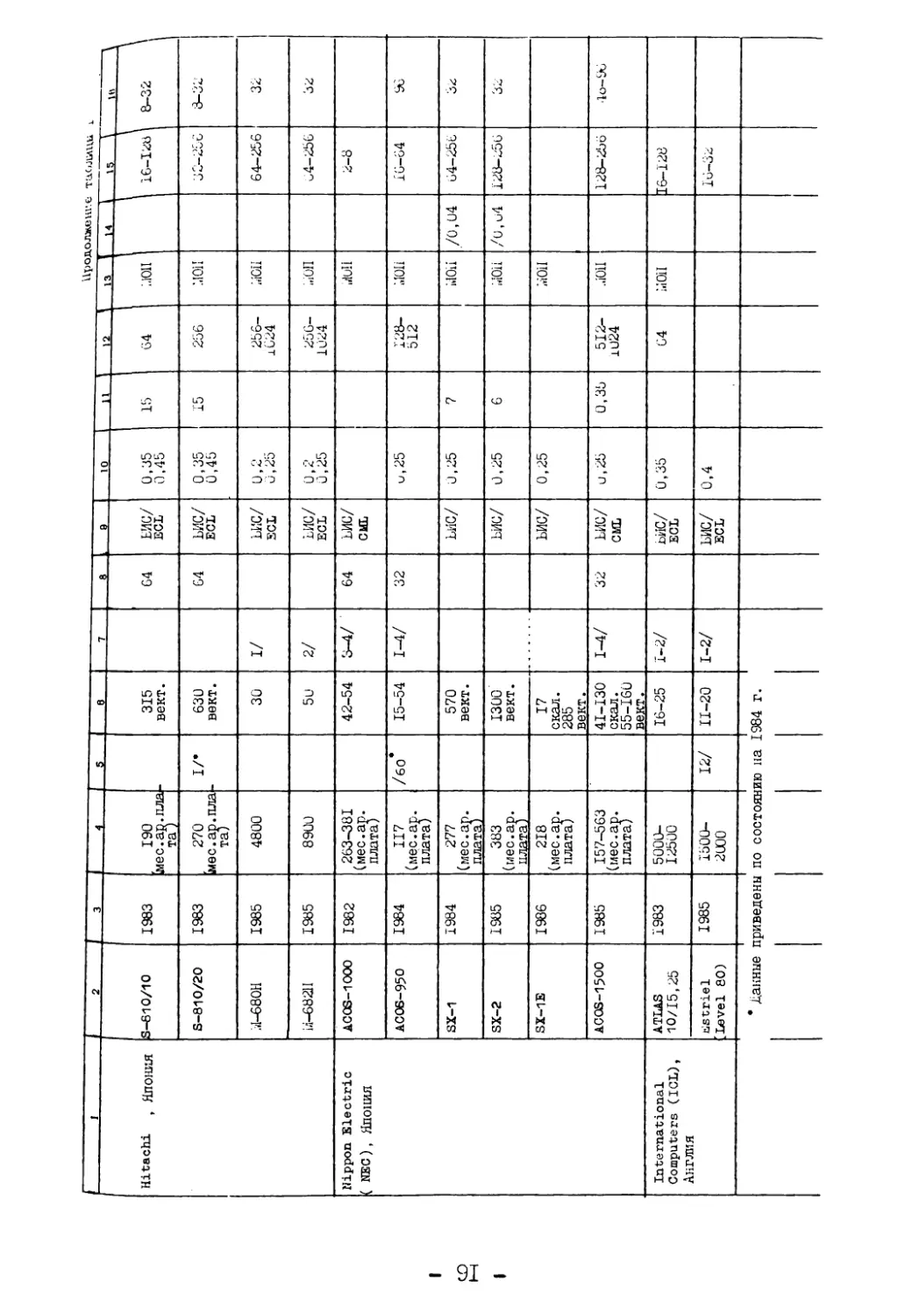

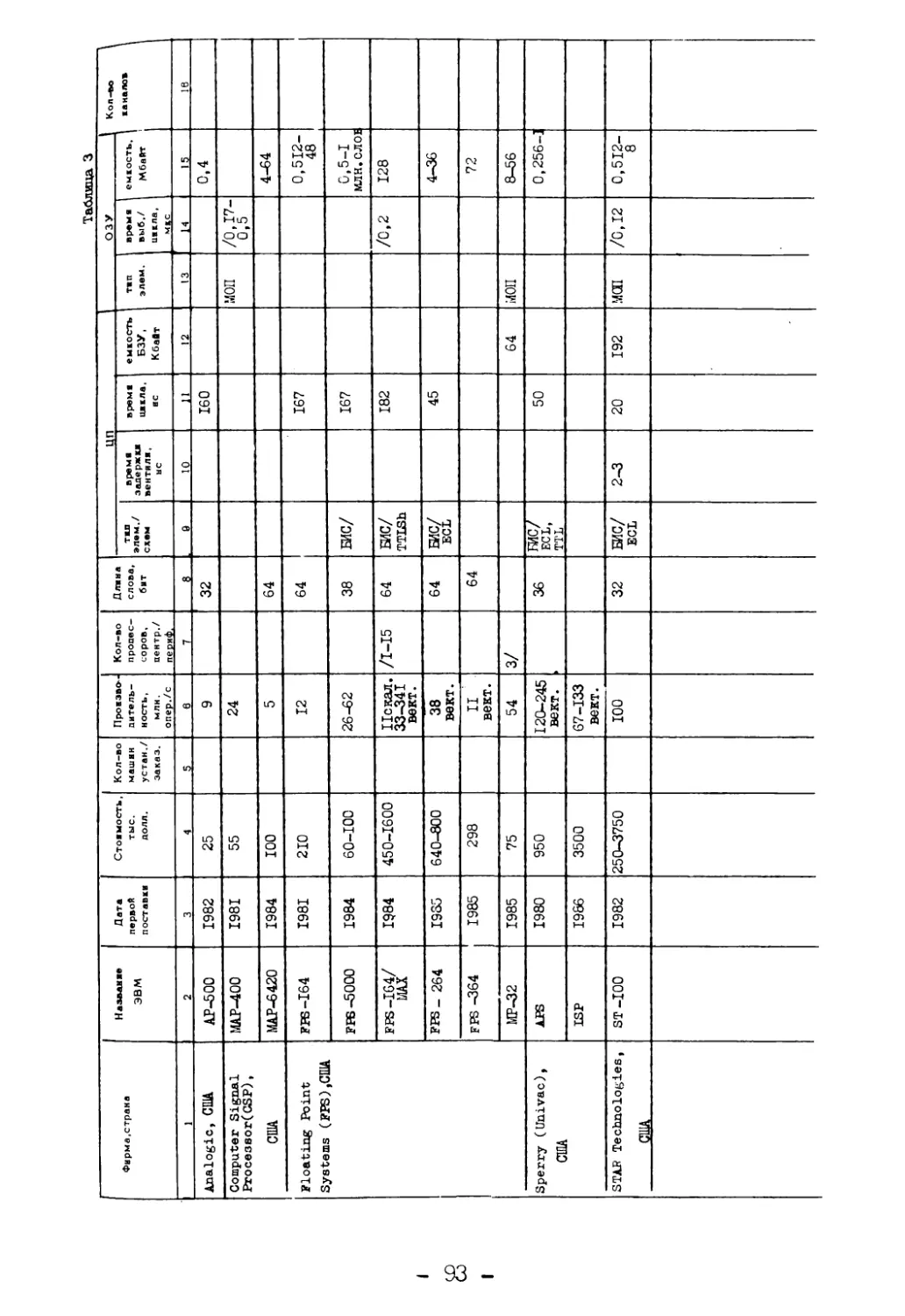

В табл.З представлены характеристики основных раз¬

работанных и перспективных минисупер-ЭВМ. В настоящее

время их разработкой и выпуском в ОПА занимаются около

10 специально созданных фирл /12,14,15/.

В последние годы появились также относительно не¬

дорогие "гибридные" высокопроизводительные ВС, состоя¬

щие из специальных процессоров-приставок в комплекте с

универсальной машиной в роли управляицАй ЭВМ. Сейчас ши¬

роко используются процессоры для обработки сигналов в

реальном масштабе времени (HIB) (fps-sooo и др.) и мат-

- 7 -

Возможные области использования высокопроизводительной ВТ

Р< О)

сб о Д

е s s s

sA

1иСО О «

8

СО

I

о

к

ф

SO

21»-ч

со

О'—

о

о

о

Д 1

К Ф

ф

W

§3

Д ф Pf

Е-«Э

н §<aj

О

о «

ОО

о д

доо

М'-' rq

Рч Pi

О X он

Минисудер-ЭВМ

о

§

6

ю

НЧ

S

3 3

О

О

о

ю

СО

рч

о5

(J0

00

г

1

со

1 1

о

00

с\?

*-Ч

--I

о

ы

1—1

ю

I

Pl

о

о

о

I

OJ

со

а

1

о

I

ф ф

s а

а

о

СО

О Рчс8

§ 5S

а

а

е<

й

я ф

Й

ф

р

й

ф

р

о

0)

1

й

р

я

Ре

р

Й

й

ф

я

Ре

а

а

Ф

Ф

р

Ре

Г1

О

Ре

Ре

Р

3

а

о

О

Й

3

3

&

о

о

со

о

'0

Ре

В

о

о

о

о

о

а

о

‘И

•гЧ

•н

Д й

о

о

<н

ф

о

Vt

Я

я

Р и

об Ф

о

•Н

гЧ

гЧ

•гЧ СП

р ф

Ф о

Я а

О Р

а

и

Й Р

гР

«н

р а

я -р

С й

ГО Ф

•Н 3

ф

Ф я

•гЧ

•<Ч

Я ф

Ф Я

к р

•Н Р

Й Ре

о

£

г—1 ф

X

Р

фр

Я Ре

Ф о

гЧ СП

Ф S

•н

я

1—1 -Н

ф

гЧ

•Н ф

сч а

р ф

гЧ {*>

а о

Н

о

Я о

гЧ

О

ф о

•И'—!

◄ СО

◄ о

◄

о

о со

йч

(;?С0

со со

>r=q

9

ричные процессоры (64-разрядные FBS-I64, 264; 24-, 52-,

58-разрядаые МАР и MiniMap и др.) /13/.

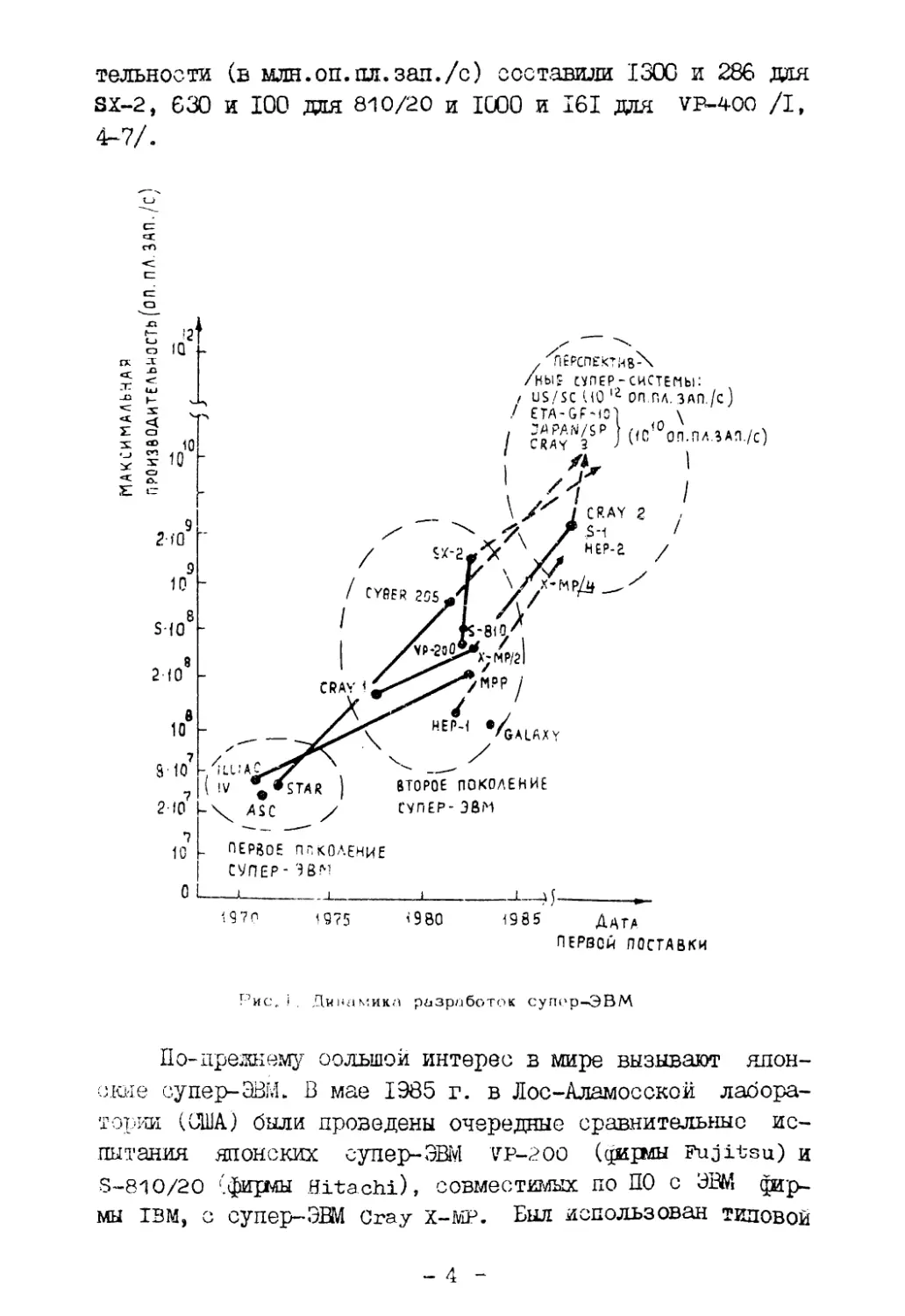

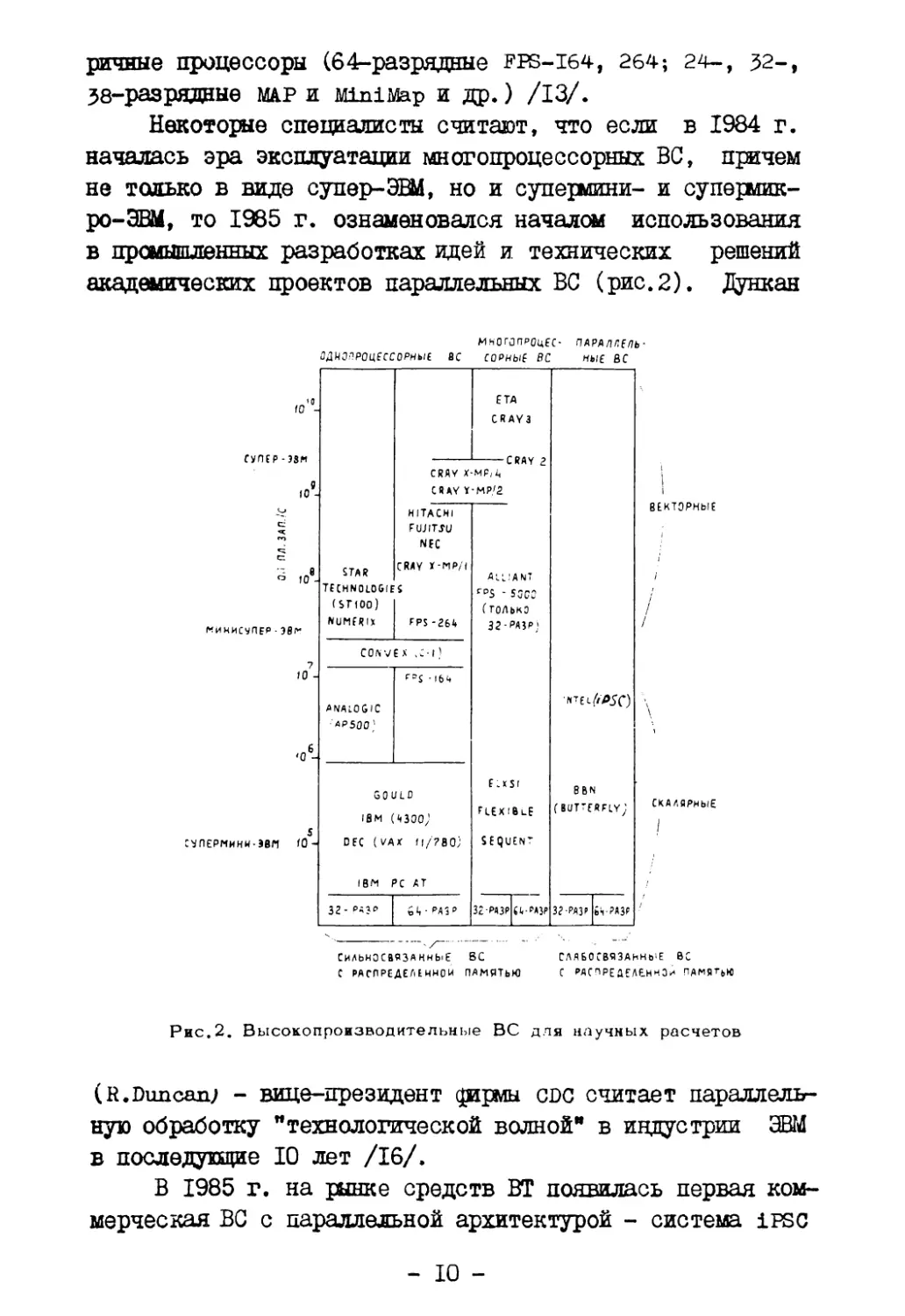

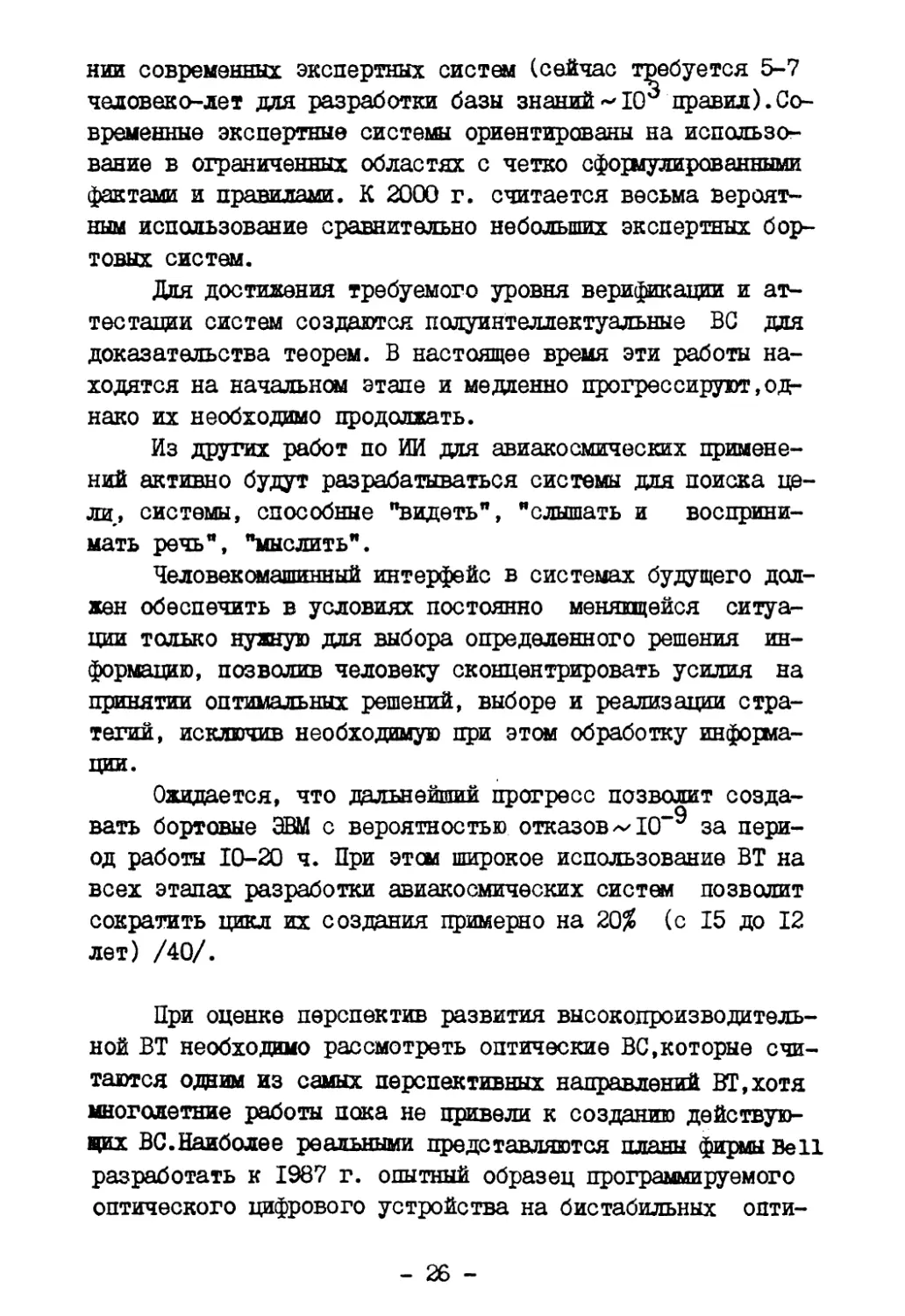

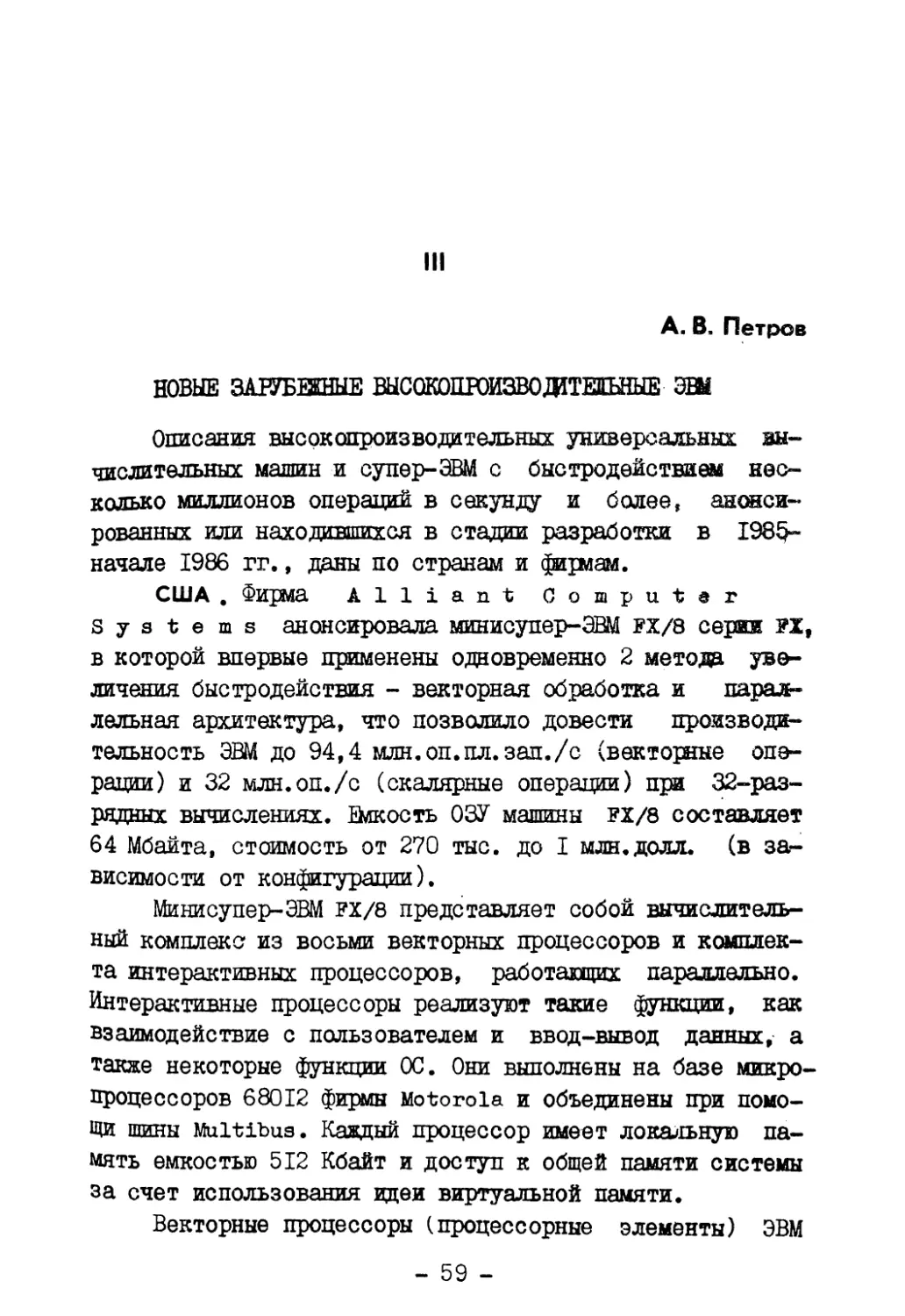

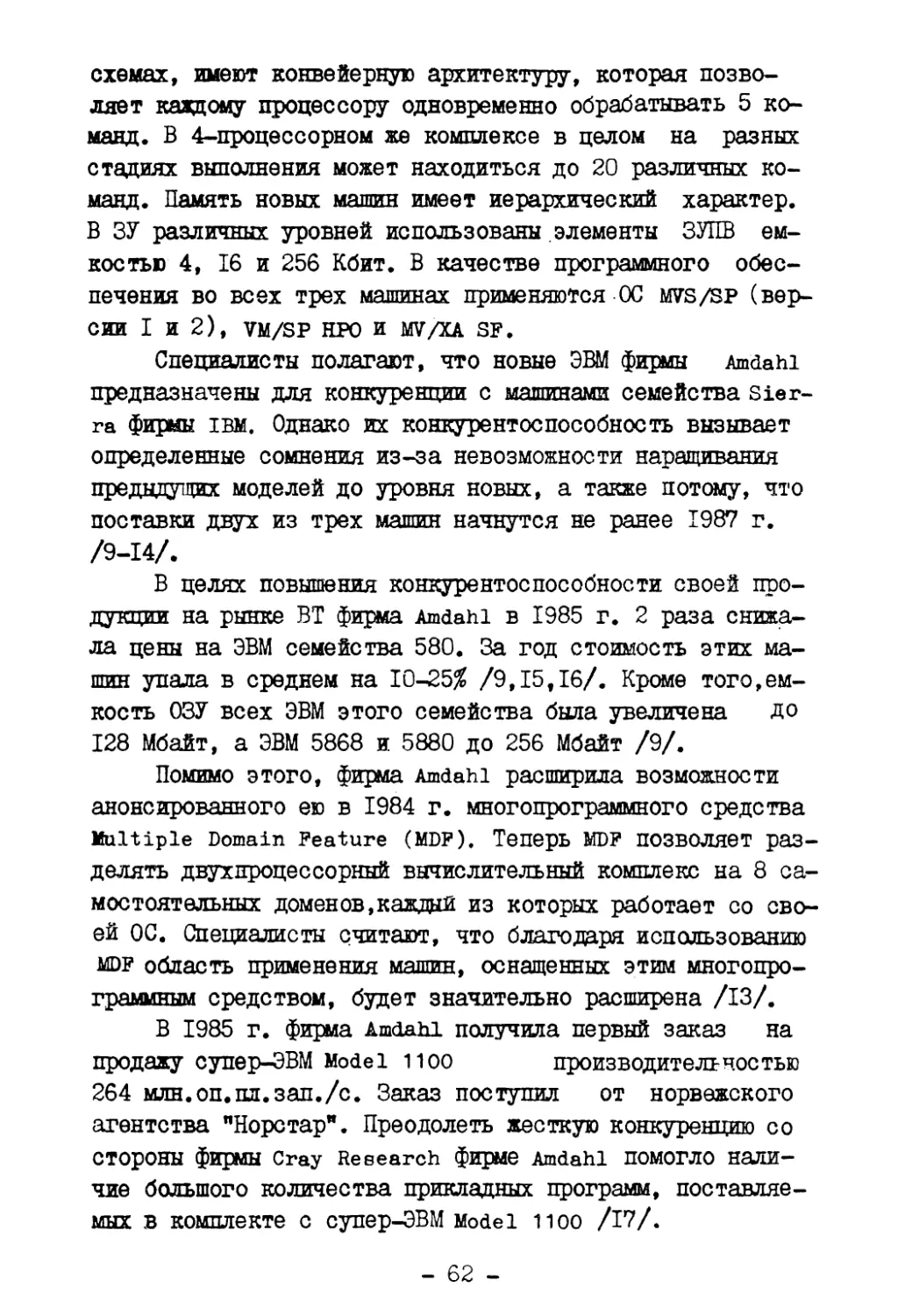

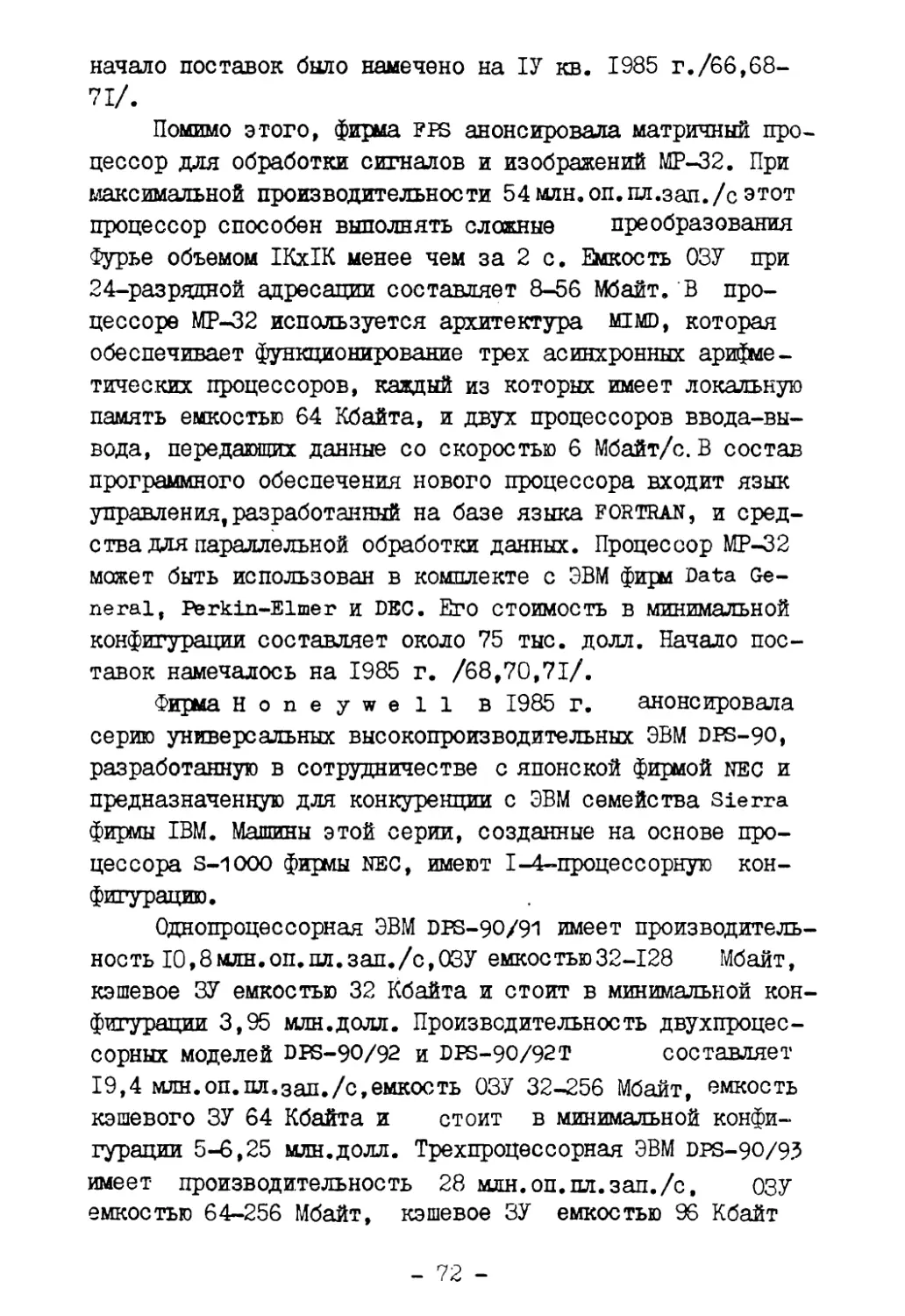

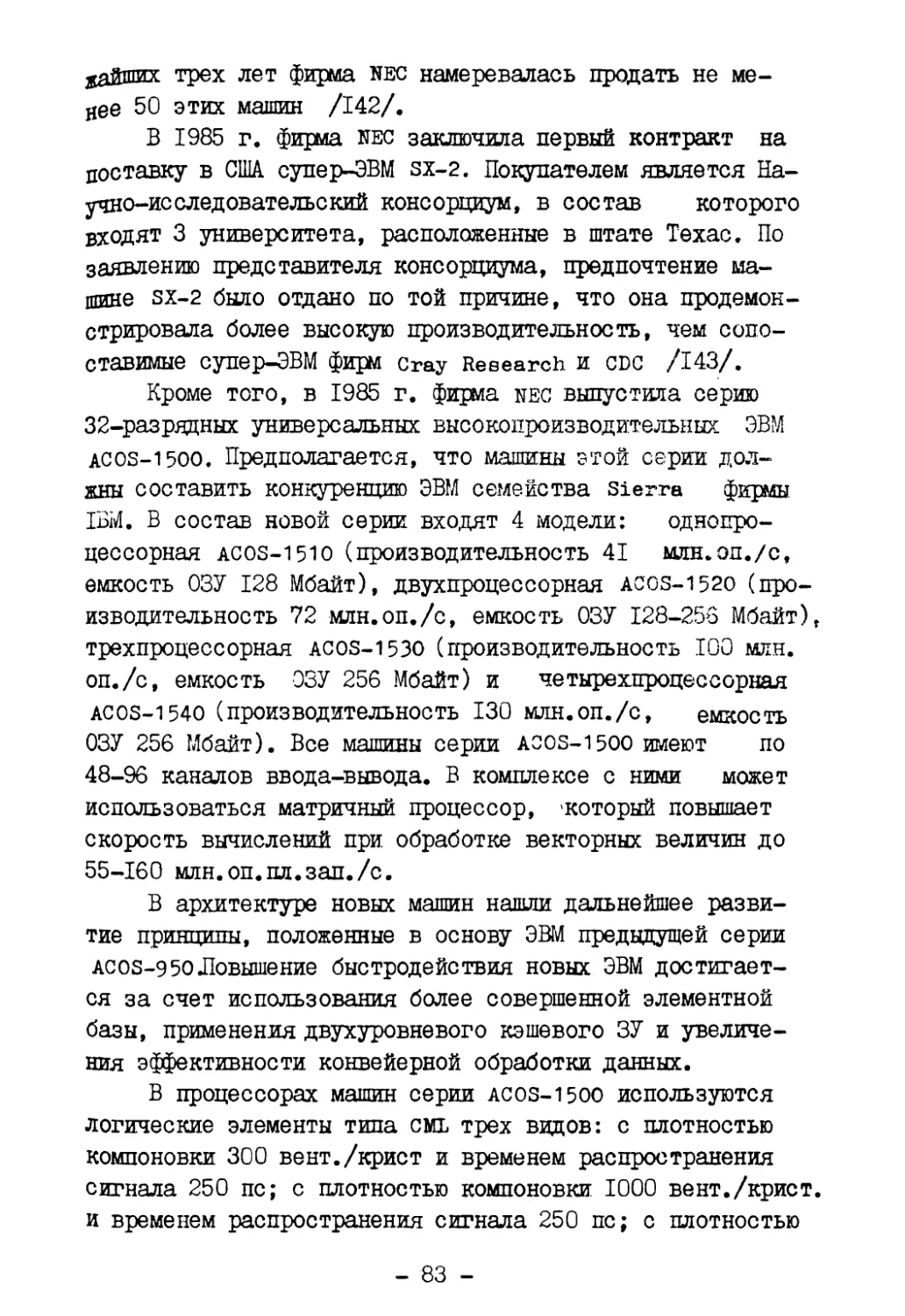

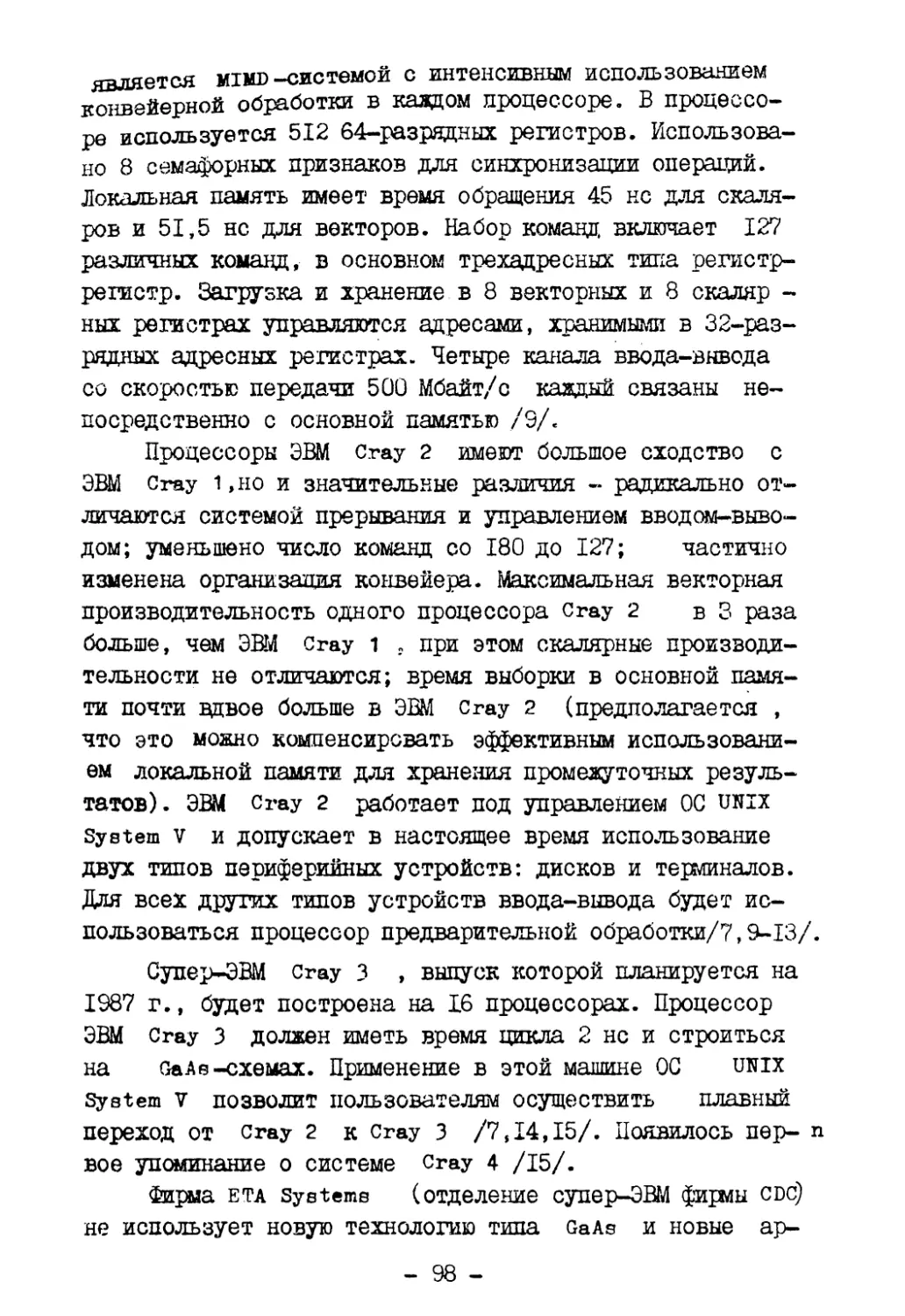

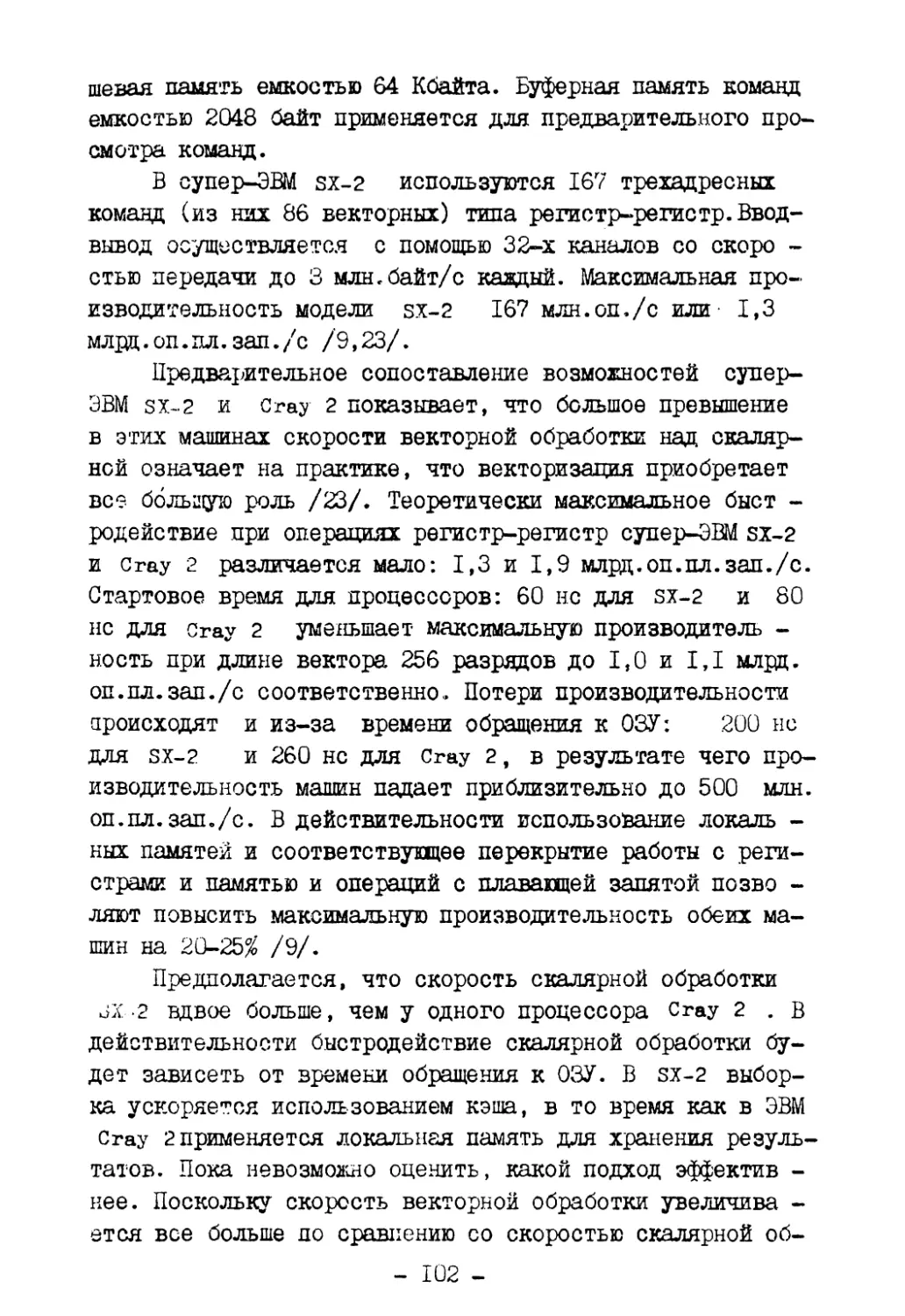

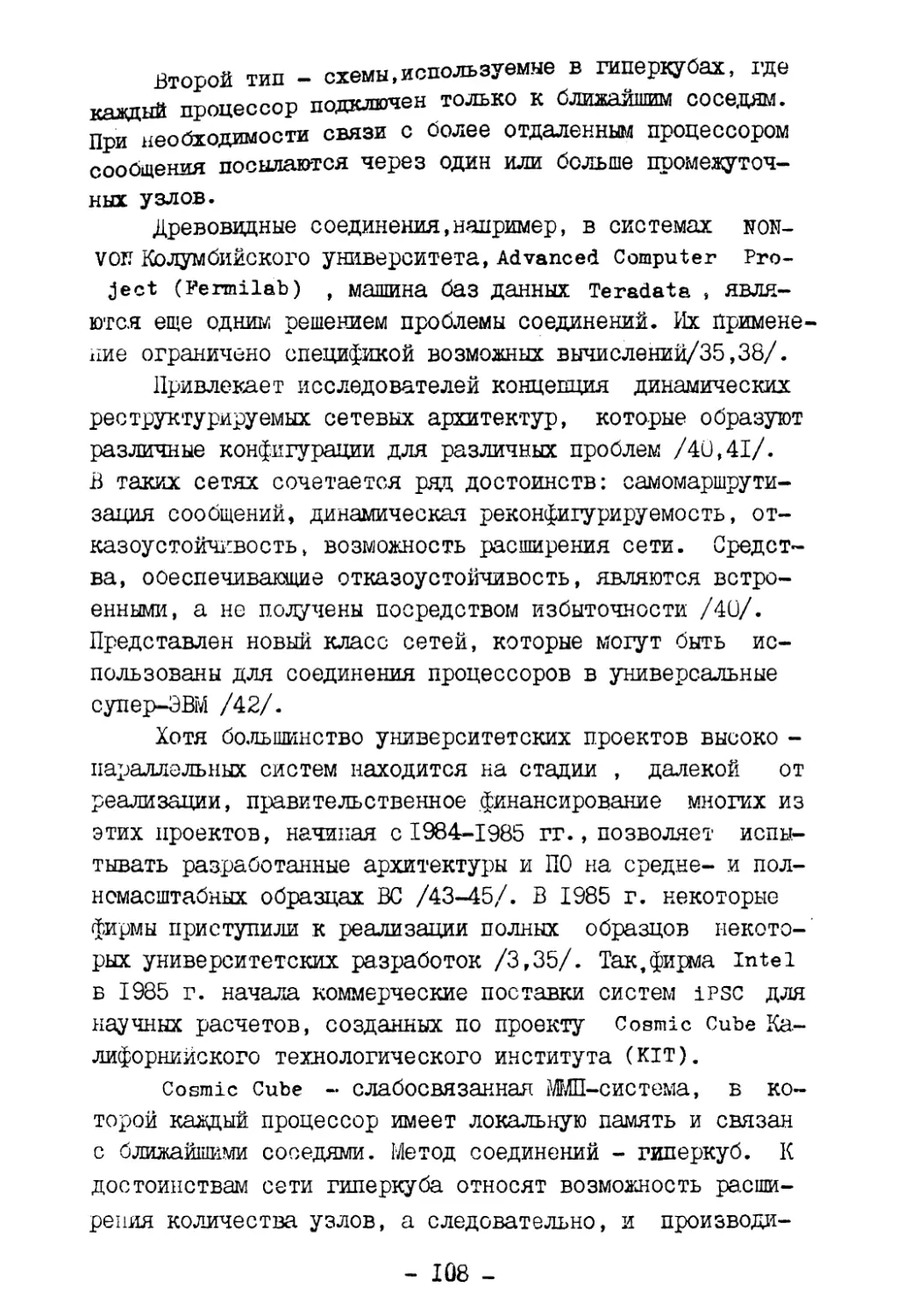

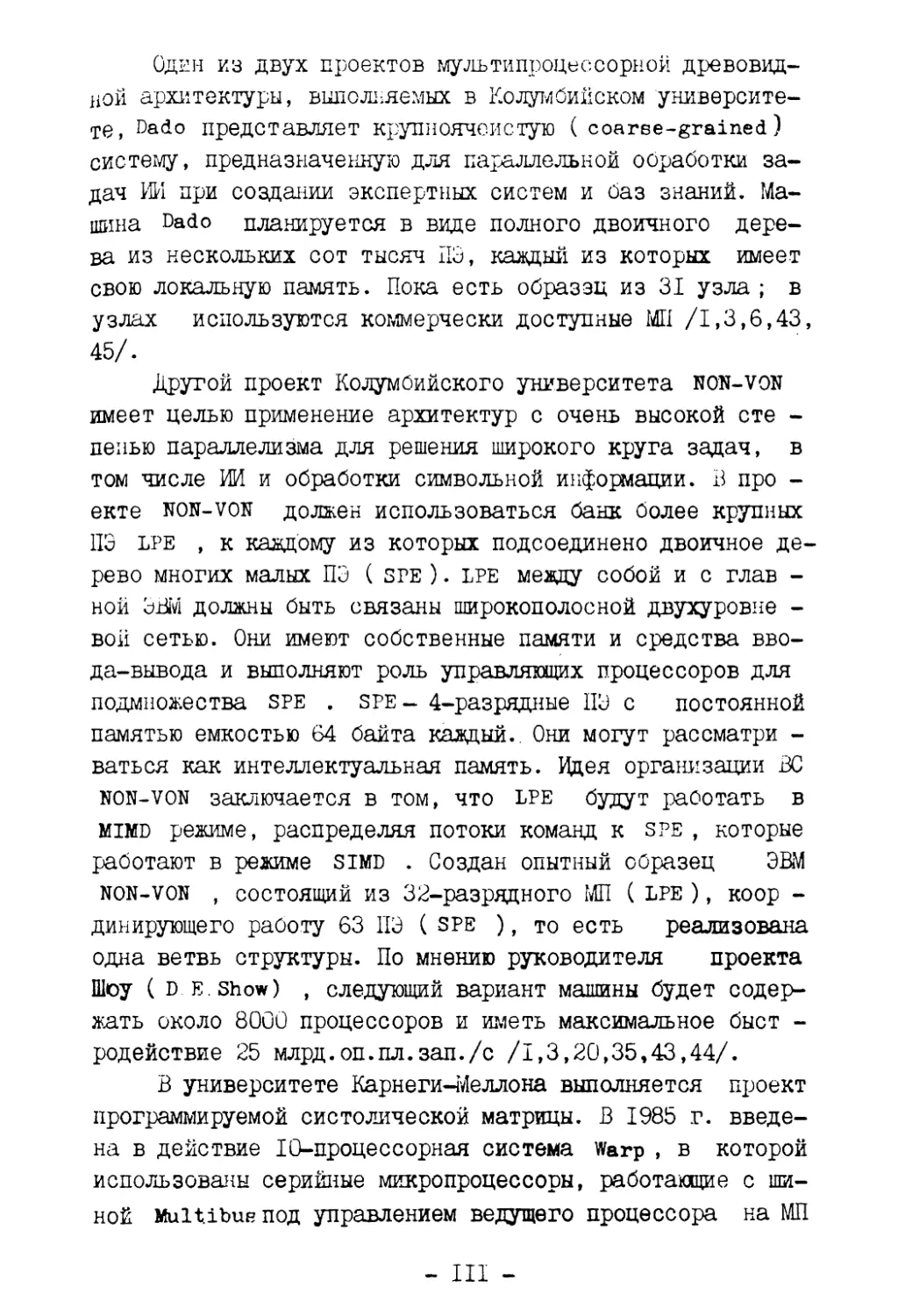

Некоторые специалисты считают, что если в 1984 г.

началась эра эксплуатации многопроцессорных ВС, причем

не только в виде супер-ЭВМ, но и супермини- и супермик-

ро-ЭВМ, то 1985 г. ознаменовался началом использования

в промышленных разработках идей и технических решений

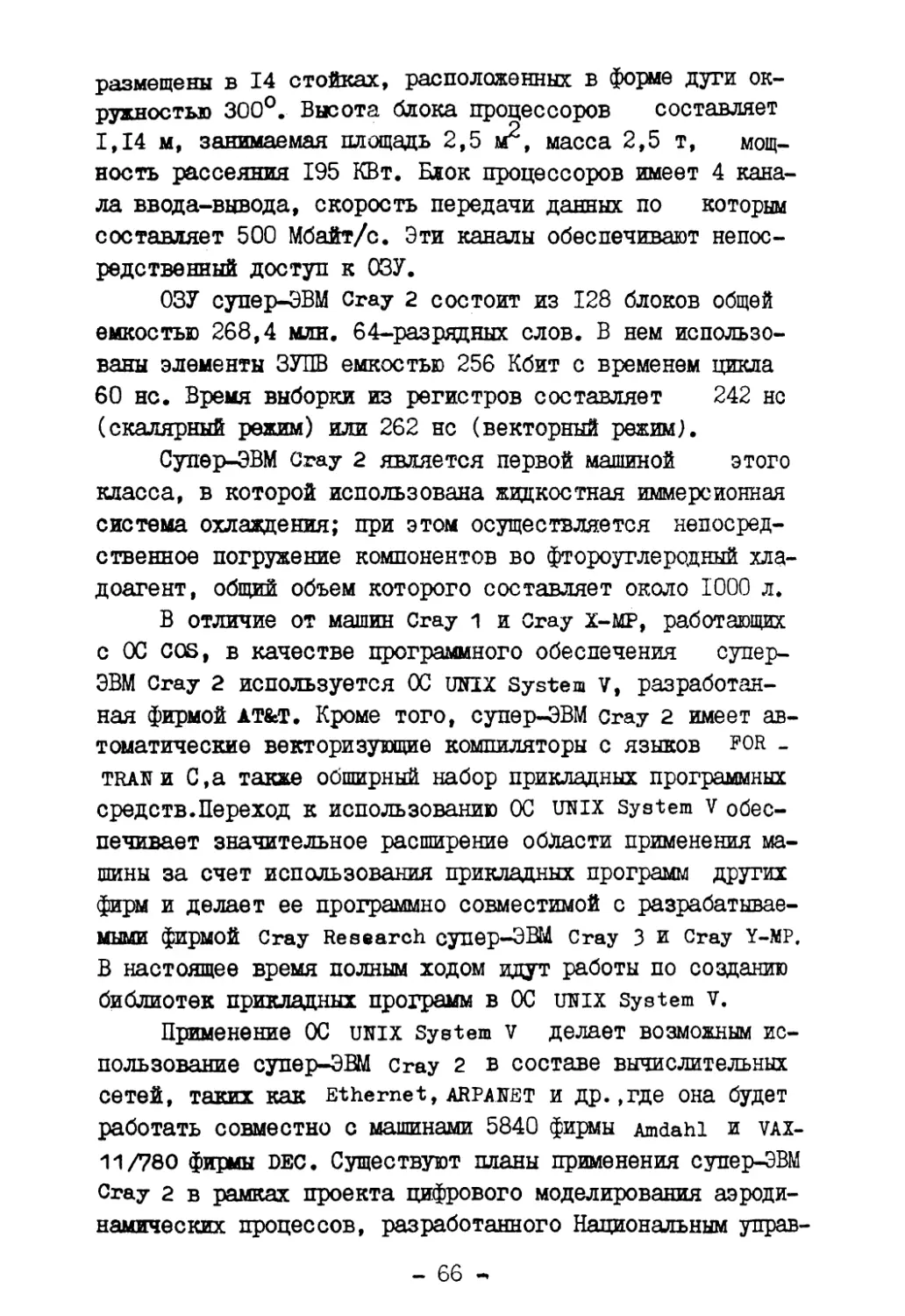

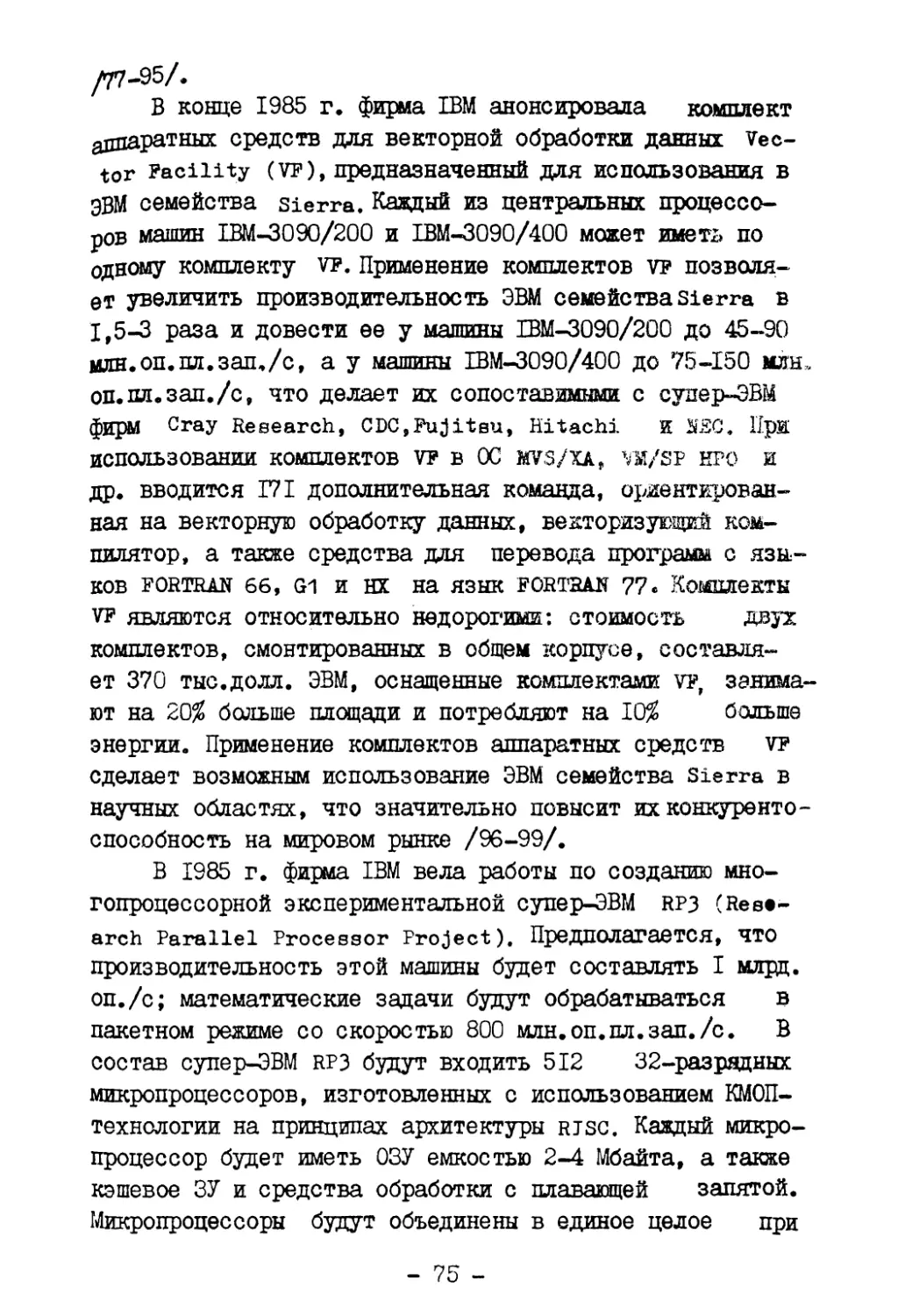

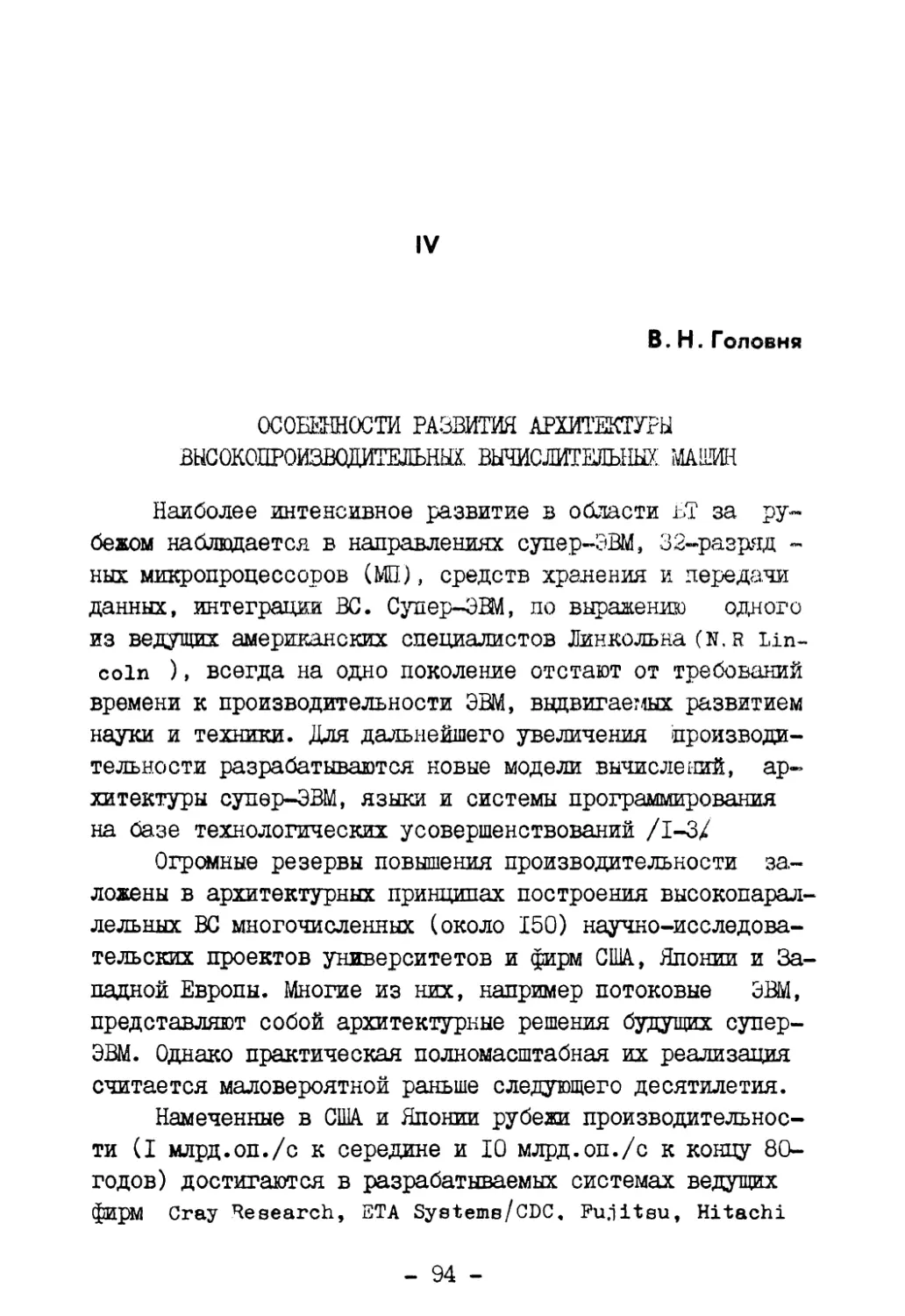

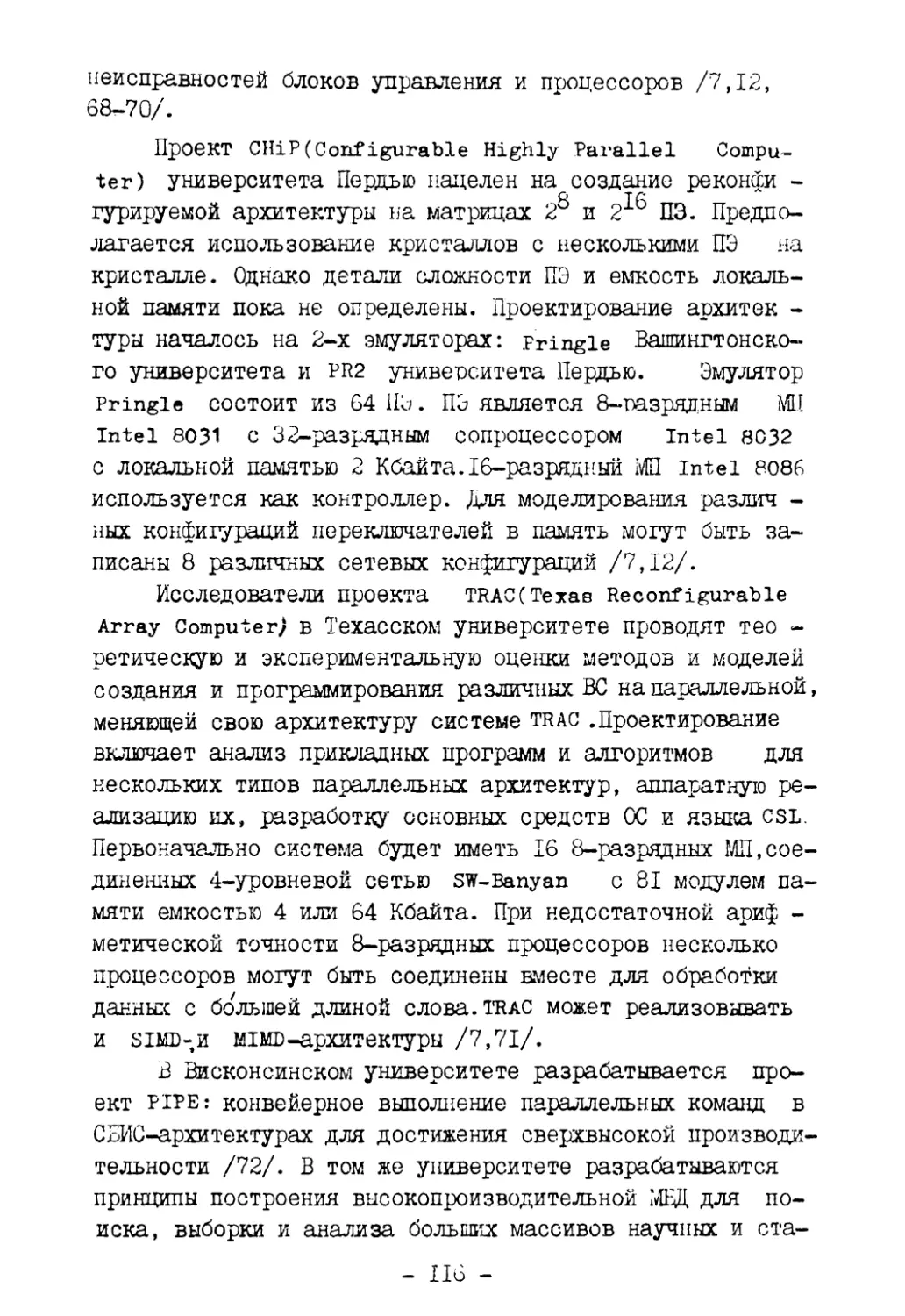

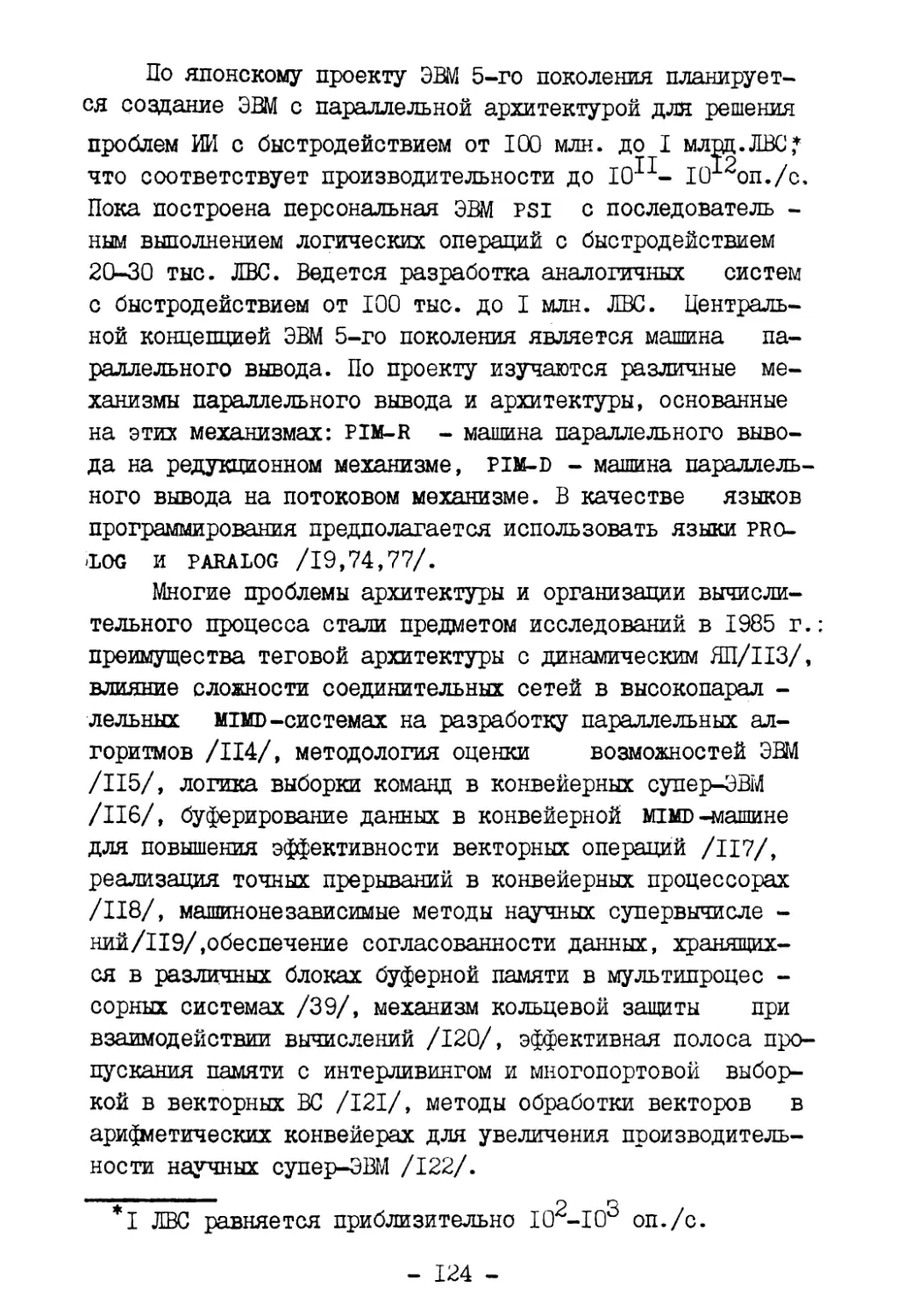

академических проектов параллельных ВС (рис.2). Дункан

МНОГОПРОцЕС- ПАРАЛЛЕЛЬ-

СДНОПРОЦЕССОРНЫЕ ВС СОРНЫЕ ВС НЫ£ вс

STAR

TECHNOLOGIE

(ST100)

NUMfRIX

CRAY X-

CRAV Г

HITACHI

FUJITSU

NEC

CRAY X-MP/f

$

EPS-264

CONVEX ,;-l )

ANALOGIC

■apsoo;

-1бй

GOULD

IBM (4300;

DEC (YAX f 1/780;

IBM PC AT

32-pa?p |

G4 ■ РАЗР

ETA

CRAY3

CRAY 2

-MP; 4

-MP/2

AlLlANT

fpS - 5000

(только

32-PA3P!

thelMc)

E. XS l

flexible

SEQUEN’

8BN

(BUTTERFLY;

32-pa3p|gu-РДЗР

32 -PA3P |bi ?A3F

СиЛЬН0СаЯЗАННЬ|£ ВС

С РАСПРЕДЕЛЕННОЙ ПАМЯТЬЮ

СЛЯБО'ВЯЗАННЬ'Е ВС

С РАСПРЕДЕЛЕННОЕ ПАМЯТЬЮ

Рис.2. Высокопроизводительные ВС для научных расчетов

(R.Duncan? - вице-президент дирмы cdc считает параллель¬

ную обработку "технологической волной" в индустрии ЭВМ

в последующие 10 лет /16/.

В 1985 г. на рынке средств ВТ появилась первая ком¬

мерческая ВС с параллельной архитектурой - система irsc

- 10 -

фирмы Intel, реализованная на базе университетской раз¬

работки Cosmic Cube Калифорнийского технологического ин¬

ститута. В состав iPSC входят до 128 микро-ЭВМ. Эффек¬

тивное быстродействие системы до 10 млн.он.пл.зап./с,

цена до 500 тыс.долл. /17/.

Архитектура Cosmic Cube использована также при раз¬

работке параллельной мию-системы Ncube на 32-разрядных

микропроцессорах. Каждый узел системы может обеспечить

производительность до 500 млн.оп.пл.зап./с. Полная кон¬

фигурация системы содержит 1024 ПЭ. Для повышения на¬

дежности, упрощения программирования, повышения скоро¬

сти ввода-вывода данных, снижения стоимости и габаритов

системы в каждом узле использованы только 7 СШС: спе¬

циально разработанный кристалл ПЭ, содержащий скалярный

и векторный блоки, и 6 кристаллов ДЗУПВ 64Кх4 бит.В на¬

стоящее время несколько блоков системы переданы заказ¬

чикам на испытания /18/.

Модификация архитектуры Cosmic Cube использована

при разработке в Принстонском университете по контракту

НАСА супер-вычислителя для гидродинамических расчетов.

Производительность одного узла системы до 400 млн.оп.

пл.зап./с, производительность всей системы, содержащей

до 128 узлов, оценивается в десятки млрд.оп.пл.зап./с.

Система реализуется на 32-разрядных Есь-микропроцессо-

рах типа Ат 29525 с общей памятью до 2 Гбайт. Создан 3-

процессорный экспериментальный образец системы /19/.

В апреле 1985 г. проведены испытания 148-процес¬

сорной системы Butterfly, разрабатываемой по программе

Управления перспективных исследований МО США (darpa) на

основе микропроцессоров 68000 фирлы Motorola. Использу¬

ется архитектура системы с общей памятью. Ведутся рабо¬

ты по созданию ВС с 256, 512 и 1000 связанных процессо¬

ров. В 1987 г. предполагается испытать универсальную ма¬

тричную систему для военных применений, содержащую 10®

ПЭ. Разрабатывается специальное ПО системы /20,21/.

На базе потоковой архитектуры, разработанной Мас¬

сачусетским и другими университетами США, создан специ¬

II -

ализированный процессор для обработки сигналов и дру¬

гих задач, решаемых в JMB - ldf-ioo, который объявлен

первым коммерческим программируемым параллельным процес¬

сором с потоковой архитектурой. Он имеет модульную кон¬

струкцию, реализован на 32-разрядаых микропроцессорах

фирмы National Simiconductor типа 32016, производитель¬

ность от 5 до 256 млн.оп./с /22/.

В существующих системах для массовых параллельных

вычислений (с сотнями и тысячами ПЭ) не решены проблемы

взаимодействия ПЭ, распараллеливания программ,ввода-вы¬

вода данных. Затраты времени на коииутацию, синхрониза¬

цию, разрешение конфликтов из-за совместного использо¬

вания ресурсов значительно снижают теоретическую произ¬

водительность таких систем. Ключевым моментом при со¬

здании быстродействующих высокоэффективных параллельных

ВС считается синхронизация работы отдельных процессоров

с помощью аппаратных средств и ОС /23/.

Несмотря на указанные трудности создания ВС с па¬

раллельной архитектурой, два фактора делают создание та¬

ких систем сегодня реальным и экономически оправданным

делом. Это - широкое распространение дешевых 32-разряд-

ных микропроцессоров с соответствующими заказными, по-

лузаказными и стандартными схемами обрамления, а также

дальнейшее увеличение требований к росту производитель¬

ности используемых ВС.

Расширяется фронт работ по параллельным архитекту¬

рам в университетах и крупных политехнических институ¬

тах.в настоящее время только в США выполняется около 50

программ и проектов по данному направлению. Наиболее

крупные из них, финансируемые правительством США, ука¬

заны в табл.4. Кроме darpa, которое выделяет на работы

по параллельным архитектурам до 25$ общей стоимости

программы стратегических разработок в области ВТ - SCP

(Strategic Computing Program), в 1985 г. ассигнования

на эти цели увеличили на 15-20$ Министерство энергетики

США, Национальный научный фонд и другие правительствен¬

ные организации /24,25/.

- 12 -

Таблица 4

Работы по параллельным архитектурам,

финансируемые правительственными

организациями США

Финансирующая

организация

Организация-исполнитель.

Проекты,направления работ

Управление националь¬

ной безопасности

(National Security

Agency - NSA)

Центр исследований по cynej>-3BM(SRC).

Алгоритмы и системы для параллельной

обработки

Министерство энерге¬

тики

(Department of Energy

- DOE)

Сверхбыстродействующие многопроцессор¬

ные супер вычислители для научных при¬

менений о

Проекты: Ultracomputer Ныо-Иоркско-

го ун-та, Cosmic Cube Калифорнийско¬

го технологического ин-та, Cedar

Иллинойского центра супер-ЭВМ, стати¬

ческих потоковых архитектур Массачу -

сетского технологического ин-та, ди -

намической многомашинной системы для

управления базами данных по науке и

технике ун-та шт.Флорида, TRAC ун-та

шт.Техас, ЭВМ для больших статистиче¬

ских баз данных ун-та шт. Висконсин,

Lemur для расчетов в физике высоких

энергий Аргоннской национальной лабо¬

ратории, многопроцессорных ВС Лос-Ала¬

мосской, Ливерморе кой национальных

лабораторий п лаборатории в Oak Ridge

Управление перспектив¬

ных исследований МО

США

(Defense Advanced

Research Projects

Agency - DARPA)

Архитектура многопроцессорных ВС,

Проекты: Butterfly фирмы BBN, Con¬

nection Machine фирмы Thinking

Machines, систолические матрицы -

Warp-процессор ун-та Карнеги-Меллона,

NON-VONи Dado Колумбийского ун-та.

Средства эмуляции многопроцессорных

ВС Массачусетского технологического

ин-та

Национальный науч¬

ный фонд

(National Science

Foundation-NSF)

Разработки и исследования новых архи¬

тектурных концепций

Финансирующая

организация

Продолжение таблицу 4

Организ ация-исполнитель.

Проекты, направления работ

Управление научно-

исследовательских

работ ВМС

(Office of Naval

Research - ONR)

Национальное управле¬

ние по аэронавтике и

исследованию космиче¬

ского пространства

(National Aeronautics

& Space Administration

- NASA)

Проекты: Ultracomputeг Нью-Йоркского

ун-та, потоковых архитектур Массачусет¬

ского технологического ин-та, архитек¬

туры ЭВМ для несвязанных процессов об¬

ращения и диспетчеризации ун-та шт.Ви¬

сконсин, Boolean Vector Ma chine (BVM)

ун-та Duke; проблемы координации в ко¬

оперативных распределенных системах

ун-та шт. Массачусетс, алгоритмы и се¬

тевые архитектуры ун-та шт. Висконсин,

многопроцессорные архитектуры ун-та шт.

Сев.Каролина, мультимикрокомпьютерные

архитектуры Иллинойского ун-та, TRAC

ун-та шт. Техас, Cedar Иллинойского

ун-та

Систолические матрицу ун-та Карнеги-

Меллона.

Программы: Large Scale Scientific Com¬

puting Стэнфордского и др. ун-тов по

разработке алгоритмов и ПО для парал¬

лельных вычислений

Проекты: МРР фирмы Goodyear Aerospace,

NAS, fem исследовательского центра

NASA в Лэнгли, многопроцессорных ВС

для гидродинамических расчетов Эимско-

го исследовательского центра, ЭВМ для

решенил уравнений Навье-Стокса (NSC)

Принстонского ун-та

- 14 -

Работы по созданию высокопроизводительных ВС буду¬

щих поколений ведутся во всех развитых странах чрезвы¬

чайно широким фронтом. Только в США. объем капиталовло¬

жений в супер-ЭВМ на 10 лет составляет свыше 8 млрд,

долл. (табл.5) /II/.

США . Основные работы по созданию высокопроизво¬

дительных ВС будущих поколений ведутся в рамках СОИ,

включая программу scp, финансируемую dabpa. В рамках

СОИ для ведения "звездных войн" предполагается создать

"щит" от баллистических ракет противника. Центральным

звеном этой системы долина стать автоматизированная си¬

стема управления, использующая ВС нового поколения.Важ¬

нейшей проблемой создания такой системы является разра¬

ботка средств ПО, требуемый объем которого оценивается

в 10? строк и более. Большинство специалистов считают

задачу создания и отладки ПО такой системы неразрешимой

/26/.

Важнейшим направлением работ в рамках SOP является

разработка экспертных систем военного назначения, в том

числе системы управления ресурсами, полезной загрузкой

и ремонтно-восстановительными работами для космического

корабля многоразового использования и создаваемой к

1992 г. космической станции. Испытания экспертной сис¬

темы должны начаться в конце 1986 г. После испытаний

предполагается в течение 3 лет создать базовую диагно¬

стическую систему в рамках разрабатываемой полностью ав¬

томатизированной контрольно-испытательной системы. В

1985 г. DARPA ассигновало на исследования по созданию

экспертных систем порядка 20 млн.долл. /27,28/.

В рамках scp создаются вычислительные системы во¬

енного, применения производительностью до 10® (1986 г.)

и Ю12 (1989-1992 гг.) оп.пл.зап./с. Создаваемые ЭВМ

должны обеспечить автономное функционирование военных

систем в боевых условиях в JMB,моделирование боевых си¬

туаций, быстрый поиск и выборку информации из очень

больших массивов данных. Предусмотрены разработка ПО ре-

- 15 -

Капиталовложения СИЛ в супер-ЭВМ

(на 10 лет)

Таблица 5

Организация

Программа, направление

работ

Объем

финансиро¬

вания,

млн. долл.

Правительственные

организации:

Ю (DOD)

Программа стратегических раз¬

работок в области ВТ (SCPJ

СОИ, робототехника и ИИ

1000

1200

Национальный

научный фонд

(NSF)

Университетские центры

супер-ЭВМ

Сети связи

200

5

Министерство

энергетики (doe)

-

200

HAGA (NASA)

Космические станции, автома¬

тизация, ИИ

600

Национальные ин¬

ституты здравоох¬

ранения (NIH)

Медицинские информационные

системы, биотехнология

Прочие

100

45

Всего: 3,35

млрд. долл.

Фирмы:

Основные изготови¬

тели супер-ЭВМ

Разработка и выпуск

супер-ЭВМ

1500

Вспомогательные и

новые фирмы

1000

Всего: 2,5

'млрд. долл.

Консорциумы и исследовательские центры:

Microelectronic & Computer IOOO

Technology Corp.

Semiconductor Research Corp. TOO

Stanford University Center 500

Massachusetts Microelectronic Center 100

NSF University Supercomputer Centers 300

И др.

Всего: 2,285 млрд.долл.

ИТОГО: 8,135 млрд.долл.

- 16 -

чевого ввода, визуального обнаружения и распознавания

объектов, а также использование программирования на ес¬

тественном языке. Первоначальный объем финансирования

на 1984-1986 гг. составил 300 млн.долл., общий объем

финансирования программы оценивается в I млрд.долл./29,

30/.

Предполагается, что возможности разрабатываемых ВС

будут продемонстрированы первоначально в 3-х экспери¬

ментальных военных системах для Армии, ВВС и ВМС: авто¬

матическом транспортном средстве-, электронном "ассоциа¬

тивном" пилоте и системе управления боевыми действиями

кораблей ВМС.

Автоматическое транспортное средство для разведки,

снабжения войск и доставки боеприпасов будет оснащено

навигационной системой и системой технического зрения

для распознавания дороги и препятствий. Этот робот дол¬

жен "воспринимать и интерпретировать" окружающую среду

и команды высокого уровня, обладать особенностью "пла¬

нировать" свои действия в соответствии с поставленными

перед ним задачами. Транспортное средство предполагает¬

ся создать к 1990 г., оно должно передвигаться со ско¬

ростью 10-20 км/ч по пересеченной местности, включая

лесистые и пустынные участки. Необходимая для этого ЭВМ

должна иметь производительность до 10^ оп. пл. зап. /с и

память емкостью 10-100 Гбайт /29-31/.

Система электронного "асссоциативного" пилота (си¬

стема-помощник летчиков самолетов-истребителей) должна

обеспечить распознавание целей и определять сбои в ра¬

боте бортового оборудования в жестких условиях эксплуа¬

тации (уровень шумов до II5 дБ, ускорение - несколько

g). ЭВМ системы производительностью от 4-107 ЛВС* *

(1986 г.) до 2«10^ ЛВС (1992 г.) будет автоматически

обрабатывать данные с РЛС, оптических и других датчиков.

Выходная информация будет сообщаться летчику в форме

синтезированной речи. Потребуется база знаний, содержа¬

щая несколько тысяч логических правил. ПО создаваемого

2 3

* 1 ЛВС примерно эквивалентен 10 -10 оп./с.

- 17 -

аппарата может отлаживаться как путем моделирования его

работы, так и в реальных полетах /29-31/.

Система управления боевыми действиями кораблей ВМС

будет выполнена как распределенная экспертная система,

использующая базу знаний с 2-10^ логических правил, уп¬

равляемую от ЭВМ производительностью ~ 10^ оп./с. Она

должна обеспечить вывод на дисплей детальной картины

боя, включая диспозицию сил, окружающую обстановку для

средств радиоэлектронного подавления, план нанесения

удара, прогноз погоды и т.д. Взаимодействие с системой

будет осуществляться с помощью средств машинной графики

и устройств речевого ввода и вывода. Она будет обеспе¬

чивать 4-суточный прогноз по сценарию "что будет, если"

и в обычных условиях заменит в центре управления 20-40

человек /29-31/.

В обеспечение вышеуказанных 3-х систем ведутся об¬

ширные исследования по "машинному зрению",речевому вво¬

ду и выводу, экспертным системам, аппаратному и програм¬

мному обеспечениям, микроэлектронике. При этом предпо¬

лагается использовать ВС с новыми параллельными архи¬

тектурами, обеспечивающими сверхвысокопроизводительную

обработку. Требования к элементной базе перспективных

военных ВС в основном будут обеспечиваться программой

разработки ССИС. Для сверхвысокопроизводительных ВС наи¬

более перспективны быстродействующие КМОП-матрицы со

степенью интягрануги^TO^-TQ^ вент./крист..работающие на

частоте 50 МГц и выше, биполярные логические ИС с высо¬

кой плотностью размещения элементов и GaAs-схемы со

степенью интеграции несколько сотен вентилей на кри¬

сталл.

В рамках программы предполагается создать новые

параллельные ЭВМ для обработки сигналов, символов и мно¬

гофункциональной обработки. Создаваемые супер-ЭВМ для

обработки сигналов (производительность до I0-1-2 оп.пл.

зап./с) должны обеспечить фильтрацию и анализ корреля¬

ции сигналов, поступающих от датчиков, анализ волновых

функций. Основные направления работ здесь: создание про¬

- 18 -

цессорных элеменов на систолических матрицах, програм¬

мируемые матричные процессоры, твердотельные структуры,

осуществляющие функции распознавания и счета. Символь¬

ные процессоры должны обеспечить выполнение быстра па¬

раллельных символьных вычислений и быструю расшифровку

карт и схем за счет использования супер-ЭВМ с семантиче¬

ской памятью и поиска в базах данных по образцам.Супер¬

ЭВМ дня многофункциональной обработки должны выполнять

широкий спектр различных параллельных вычислений с про¬

изводительностью, характерной для сигнальных или сим¬

вольных процессоров /29,32/. Финансируются и могут быть

использованы такие проекты параллельных архитектур, как

проект программируемого систолического процессора уни¬

верситета Карнеги-Меллона, ЭВМ Dado и NON-VOW Колумбий¬

ского университета, ЭВМ Ultracomputer Нью-Йоркского уни¬

верситета, проект потоковой ЭВМ Массачусетского техно¬

логического института, ЭВМ Butterfly и др. Однако, не¬

смотря на крупные научно-технические и финансовые ресур¬

сы программы SCP,многие специалисты в академических и

военных кругах сомневаются в возможности успешной ее

реализации в столь короткие сроки.

Появилось краткое сообщение об испытаниях фириой

Raytheon аппаратуры для спутниковых ЭВМ следующего по¬

коления производительностью до 1,6 млрд.оп.пл.зап./с,

разработанной в рамках программы scp /33/.

Исследования по программе будут осуществляться под

руководством двух органов: Information Processing Tech¬

niques Office и Defense Sciences Office . ВйОВЬ создан¬

ный орган Engineering Application Office ответственен

за разработку экспериментальных систем для военных при¬

менений и создание испытательных стендов. Общий уровень

финансирования программы оценивается от 10-15 до 20-30%

всего бюджета darpa .

При проведении работ должны быть созданы около 10

основных и ряд вспомогательных исследовательских цент¬

ров. Вычислительные средства всех исследовательских цен¬

тров, задействованных в программе, должны быть объеди¬

- 19 -

нены в единую вычислительную сеть, что считается одной

из основных целей работ. Создание такой сети для межди¬

сциплинарных исследований рассматривается в качестве

начального этапа создания общества на основе интеллек¬

туальных ВС (проект sumbx-aim в медицине - один из пер¬

вых шагов в этом направлении). На начальном этапе для

подключения к новым ВЦ предполагается использовать су¬

ществующие сети, включая Arpanet и Bitnet МО. США/29/.

ЯПОНИЯ . Продолжались работы по проекту ЭВМ 5-го

поколения и национальному проекту супер-ЭВМ. После 2-й

Международной конференции по ВС 5-го поколения, состо¬

явшейся в Токио в ноябре 1984 г., была произведена ре¬

организация Института по разработке машин нового поко¬

ления (ICOT), сделан акцент на работы по параллельной

обработке.

В настоящее время работы по проекту ЭВМ 5-го поко¬

ления находятся на промежуточной стадии (1985-1988 гг.).

Основная цель этой стадии проекта - создать параллель¬

ную машину логического вывода PIM (Parallel Inference

Machine),содержащую порядка 100 процессоров. Параллель¬

но прорабатываются 4 механизма для создания ИМ:

1) редукционный с использованием базового языка

ИЛ;

2) потоковый с параллельным выполнением prolog- и

Concurrent PROLOG-программ;

3) с полным копированием (типа редукционного);

4) с обработкой блоков предложений.

Разрабатываются два варианта параллельной машины

логического вывода: Им-R (с редукционным механизмом) и

PIM-D (с потоковым механизмом). Предварительные сравни¬

тельные данные результатов моделирования ПО pim-r и pim-d

приведены в работе /34/. В 1986 г. будет выбрана одна

из разрабатываемых моделей им. На конечной стадии пред¬

полагается создать PIM из I03 процессоров.

Продолжалась разработка машины реляционной базы

данных Delta, преследовавшая 2 цели: I) создать экспе¬

- 20 -

риментальные возможности изучения различных механизмов

обеспечения функций базы знаний и методов реализации

этих механизмов; 2) создать экспериментальную систему -

средство разработки ПО для пользователей базового язы¬

ка KLO /34/-

Цель проекта ЭВМ 5-го поколения - создать сверхвы¬

сокопроизводительные высокопараллельные системы, соче¬

тающие процессоры различных типов (матричные, обычные,

процессоры баз знаний). Одной из важнейших проблем,воз¬

никающих при создании новых ВС, является проблема надеж¬

ности, включая самотестирование и использование ИИ для

диагностики сбоев /35/.

В 1935 г. в рамках национального проекта создания

супер-ЭВМ начаты исследования по биофизике и "биологи¬

ческим кристаллам", сверхрешеткам и трехмерным ИС с

целью создать элементную базу ВС 6-го поколения. С ап¬

реля 1985 г. Министерство внешней торговли и промышлен¬

ности финансирует новый 5-летний проект sigma, с бюдже¬

том свыше 100 млн.долл. Цель проекта - разработка сети,

содержащей более IO4 АРМ с общим ПО. Основное направ¬

ление работ здесь - разработка соответствующих средств

ПО, поскольку японские специалисты считают, что в об¬

ласти ПО Япония отстает от США и Европы на несколько

лет /26/.

ЗАПАДНАЯ ЕВРОПА. Продолжались работы в рам¬

ках совместной Европейской стратегической программа ис¬

следований в области информационной технологии -ESPRIT.

В начале 1985 г. работы по программе велись в раисах

104 проектов, охватывающих специалистов из 265 органи¬

заций. До конца года должны были начаться работы еще по

90 проектам, в 1986 г. предполагается анонсировать свы¬

ше 90 проектов. К началу 1986 г. количество участвующих

организаций увеличилось до 450 и к середине 198? г. по

программе должны работать около 2 тыс.человек. Одна из

важнейших проблем для успешной работы в рамках програм¬

мы ESPRIT - создание сети для связи и информационного

- 21 -

обмена участников программы между собой. В настоящее

время такая сеть создается на базе сети в University

College в йгблине, для обращения к ней используются об¬

щедоступные сети.

Высказывается много критических замечаний относи¬

тельно бюрократизма, неправильного финансирования и пло¬

хой организации работ по программе: малые фирмы

заявляют, что у них нет средств и возможностей реализо¬

вать свои идеи, даже если они так же хороши, как идеи

фон Неймана; крупные фифмы обвиняются в расходовании

средств программы на свои собственные нужда без всяко¬

го взаимодействия с партнерами. Несмотря на это, преоб¬

ладает мнение, что программа esphit выполнит свою коор¬

динирующую роль в масштабе Европы /26,36/.

В английском ответе на японский проект создания

ЭВМ 5~го поколения - программе Alvey - основные работы

ведутся по 4 направлениям: автоматизации производства,

экспертной системе для социальных целей,печатающему уст¬

ройству с речевым вводом и интеллектуальной системе,уп¬

равляющей автоматическими транспортными средствами. Про¬

грамма должна обеспечить новый уровень координации уси¬

лий академических и промышленных организаций; в 85% из

ведущихся 174 проектов участвуют и те и другие органи¬

зации. руководство программы считает, что благодаря ей

быстро ликвидируется разрыв между промышленностью и уни¬

верситетами. Одно из традиционно сильных в Англии на¬

правлений исследований по архитектурам ЭВМ ведется по

отдельному проекту Flagship стоимостью около 20 млн.

долл., который рассматривается в качестве основного на¬

правления работ программы по созданию ЭВМ 5-го поколе¬

ния. В проект включены работы по машине Alice и потоко¬

вой ЭВМ Манчестерского университета. Опытный образец ма¬

шины Alice на транспьютерах фирмы inmos создается фир¬

мой ICL. Работы по ПЭ нацелены на создание декларатив -

ного объектного языка DACTL - компилятора Alvey. Язык

dactl ориентирован на виртуальную машину, отличающуюся

стабильной архитектурой, удобной для разработки систем-

- 22 -

них программ,и позволяющей переносить ПО с одной сис¬

темы на другую» Создатели языка считают, что dactl мо¬

жет стать международным стандартным языком для ЭВМ 5-го

поколения /37—39/.

В ответ на СОИ США (но с промышленной ориентацией)

и как реакция на "бесполезную бюрократическую" програм¬

му ESPRIT во Франции выдвинута программа Eureca (Euro¬

pean Research Coordinational Agency),которая является не

исследовательской программой как таковой, а только ор¬

ганизационной схемой, предлагающей финансовую поддержку

в ряде областей исследований, включая супер-ЭВМ, парал¬

лельные архитектуры, ИИ, кремниевые и GaAs сверхбыстро¬

действующие СБИС, автоматизацию производства,робототех¬

нику, лазеры, телесвязь, биотехнологию и новые материа¬

лы. В частности, предполагается включить в программу

французские и норвежские разработки супер-ЭВМ производи¬

тельностью 100 млн.оп.пл.зап./с, французские и западно¬

германские разработки векторного процессора производи¬

тельностью 30 млн.оп.пл.зап./с, разработки Англии, ФРГ

и Франции в области ПО. Первоначальный уровень финанси¬

рования программы - 230 млн.ф.ст. для 18 стран-участ¬

ниц /26,36/.

Для оценки перспектив высокопроизводительной ВТ

представляет интерес прогноз развития бортовой ВТ др

2000 г., выработанный на симпозиуме в Остине (США) в

1984 г. Симпозиум проведен по инициативе rasa и прог¬

ноз ориентирован на авиакосмические применения. Исполь¬

зовалась экстраполяция тенденций при допущении возмож¬

ности появления принципиально новых результатов. Прог¬

ноз возможностей производился в предположении наличия

соответствующих ресурсов /40/.

Отмечалось, что наиболее существенные изменения до

2000 г. ожидаются в следующих областях: ПО, верификация

и аттестация систем, связь и управление, использование

систем ИИ. Ключевыми моментами названы супер-ЭВМ, стан¬

дартизация интерфейсов и форм представления данных, со¬

- 23 -

здание ВС в обеспечение верификации и аттестации систем.

Ожидается, что к 2000 г. соотношение цена/эффектив¬

ность и габариты ВС должны уменьшиться в 102-10° раз;

это произойдет главным образом за счет использования мно¬

гопроцессорных параллельных и распределенных архитектур.

ВС будут синтезироваться из разнородных процессоров с

производительностью некоторых из них до 10 оп./с при

ОЗУ 5-10? слов. Будут широко использоваться 32-разряд-

ные AIM производительностью I08-I08 оп.пл.зап./с с ОЗУ

5-Ю7 слов, ВЗУ емкостью IO^-IO1* слов и супер-ЭШ,со¬

держащие 102-10° ПЗ производительностью до Ю^2 оп.пл.

зап./с с ОЗУ емкостью до слов. ВЗУ будут либо оп¬

тическими, либо в виде комбинации оптической и магнит¬

ной памяти. Дисплеи АШ будут иметь специальное аппа¬

ратное обеспечение для обработки цветных изображений с

разрешающей способностью Жх8К элементов. Будут разра -

ботаны средства ПО для работы с распределенными гетеро¬

генными базами данных и для ВС, управляющих траектори¬

ей полета в ШВ и помогающих экипажу. Наряду с цифровой

будет обрабатываться символьная информация и ■ осущест¬

вляться управление информационными базами данных. Миниа¬

тюрные микропроцессоры будут управлять высокоэффективны¬

ми графически ориентированными AIM, объединенными в

крупномасштабные системы.

ВС будут иметь распределенную структуру и повышен¬

ную надежность за счет использования универсальных и

специализированных подсоединяемых процессоров.Специаль¬

ные сенсорные и исполнительные подсистемы обеспечат не¬

посредственное выполнение многих функций (преобразова¬

ние данных в стандартные форматы, интерфейс с сетями

связи, обнаружение и ликвидация сбоев и др.). Отказо¬

устойчивость ВС будет обеспечиваться дальнейшей интегра¬

цией аппаратного и программного обеспечений, а также ре¬

конфигурацией систем. Все подсистемы бортовых ВС будут

связаны между собой широкополосными волоконнооптически¬

ми каналами связи в единую сеть.

До конца столетия ожидается увеличение степени ин-

- 24 -

теграпии логических устройств и устройств памяти пример¬

но на порядок каждые 5 лет. Увеличение емкости магнит¬

ных ЗУ будет происходить более медленными темпами, чем

полупроводниковых. Это приведет к сдвигу современного

баланса между встроенной и автономной памятью.

Существующие серьезные трудности в компоновке и

использовании НШ и НЦД для бортовых систем должна раз¬

решить возможность использования оптических дисков. Ши¬

рокое развитие получит волоконная оптика, которая обес¬

печит в одном кабеле до 50 каналов с полосой пропуска¬

ния от 0,5 до I Гбит/с. Оптические линии обеспечат на¬

дежную связь на расстоянии до I км. Значительная часть

проблем межсоединений будет решена за счет использова¬

ния нового уровня интеграции моно- и мультифункциональ-

ных устройств на кристаллах и пластинах.

Программное обеспечение призвано сыграть ведущую

роль в развитии будущих высокоинтегрированных распреде¬

ленных систем, работающих в ШВ. К 2000 г. будут разра¬

ботаны базовые алгоритмы для эффективного управления па¬

раллельными и распределенными архитектурами,программные

средства для новых крупномасштабных проблем, связанных

с математическим моделированием и решением сложных сим¬

вольных задач. Так, будущие супер-ЭВМ должны обеспечить

к 2000 г. возможность точного моделирования полной кон¬

струкции самолетов (крылья, двигатели .фюзеляж), при этом

использование вычислительных методов должно уменьшить

стоимость работ по созданию разрабатываемых систем по

крайней мере на 50%. Более весомыми станут аспекты эф¬

фективности и используемости программных средств.

Основная трудность при создании систем ИИ - исчер¬

пывающая спецификация. К 2000 г. ожидается широкое ис¬

пользование специализированных экспертных систем,содер¬

жащих от нескольких сотен до нескольких тысяч фактов и

правил. Основные успехи здесь будут связаны с формами и

методами накопления и организации знаний для различных

областей использования, поскольку именно эта чрезвычай¬

но трудоемкая область является узким местом при созда¬

- 25 -

нии современных экспертных систем (сейчас требуется 5-7

человеко-лет для разработки базы знаний - Ю3 правил).Со¬

временные экспертные систем ориентированы на использо¬

вание в ограниченных областях с четко сформулированными

фактами и правилами. К 2000 г. считается весьма вероят¬

ным использование сравнительно небольших экспертных бор¬

товых систем.

Для достижения требуемого уровня верификации и ат¬

тестации систем создаются полуинтеллектуальные ВС для

доказательства теорем. В настоящее время эти работы на¬

ходятся на начальной этапе и медленно прогрессируют,од¬

нако их необходимо продолжать.

Из других работ по ИИ для авиакосмических примене¬

ний активно будут разрабатываться системы для поиска пе¬

ли., системы, способные "видеть", "слышать и восприни¬

мать речь", "мыслить".

Человекомашинный интерфейс в системах будущего дол¬

жен обеспечить в условиях постоянно меняющейся ситуа¬

ции только нужную для выбора определенного решения ин¬

формацию, позволив человеку сконцентрировать усилия на

принятии оптимальных решений, выборе и реализации стра¬

тегий, исключив необходимую при этом обработку информа¬

ции.

Ожидается, что дальнейший прогресс позволит созда¬

вать бортовые ЭВМ с вероятностью отказов^10“® за пери¬

од работы 10-20 ч. При этом широкое использование ВТ на

всех этапах разработки авиакосмических систем позволит

сократить цикл их создания примерно на 20% (с 15 до 12

лет) /40/.

При оценке перспектив развития высокопроизводитель¬

ной ВТ необходимо рассмотреть оптические ВС,которые счи¬

таются одним из самых перспективных направлений ВТ,хотя

многолетние работы пока не привали к соатутию действую¬

щих ВС.Наиболее реальными представляются планы фирмы Bell

разработать к 1987 г. опытный образец программируемого

оптического цифрового устройства на бистабильных опти¬

- 26 -

ческих элементах, выполненных на сверхрешеточных струк¬

турах на основе гетеропереходов GaAs/GaAlAs. К 1990 г.

предполагается создать образец сверхбыстродействуицего

вычислителя с полосой пропускания 100 МГц, способного

обрабатывать очень большие объемы цифровых .данных. При

этом одна из основных проблем - снижение потребляемой

мопутпсти, поскольку в больших матрицах бистабильных оп¬

тических переключателей потребляемая мощность может до¬

стигать нескольких Вт/бит.

Больших успехов в создании оптических ЭВМ предпо¬

лагают достичь фирмы СШ, входящие в созданный в

1985 г. в рамках СОИ консорциум по оптической ВТ. Такие

работы ведутся также в Европе, где Европейское эконо¬

мическое сообщество ассигновало 2,2 млн.долл, на созда¬

ние опытного образца оптической ЭВМ, и в Японии на фир¬

ме нес, в университете Tohoky и Токийском технологиче¬

ском институте /41,42/.

II

В. К. Зейденберг

КАПИТАЛИСТИЧЕСКИЙ РЫНОК ВТ

В 1985 г. во всем мире набладался спад экономичес¬

кой активности, и, по оценкам фирмы юс , этот спад,

невидимому, захватит весь 1986 г. /1,2/. Журнал "Elec¬

tronics” отмечает заметный спад активности такие на рын¬

ке электроники*, однако ожидает, что в 1986 г. на этом

рынке наступит новое оживление /2/. В 1985 г. количест¬

во работапдих в электронной промышленности США сократи¬

лось на 2,3%, в том числе в области производства ЭВМ и

конторского оборудования на 8$ (на 42 тыс.чел.)/3/.

Анализ данных по расходам разных фирм США на ВТ

показывает, что 1986 г. ожидается столь же трудным для

рынка сбыта ВТ, как и 1985 г., а может быть даже труд¬

нее. Рост затрат всевозможных фирм на ВТ в 1986 г. со¬

ставит только 4,2% (в 1985 г. было 7,4%). Средний рост

доходов фирм в 1986 г. составит только 3,1%. В частнос¬

ти, расходы на приобретение персональных ЭВМ существен¬

но уменьшатся /4/. Из-за вялости рынка многие малые фир¬

мы в США по выпуску персональных ЭВМ разорялись, а бо¬

лее крупные свертывали свои производства /5/. В связи с

затруднениями на рынке сбыта капиталовложения в отрасли

ВТ в 1986 г. возрастут лишь на 4,5% /6/.

Рынок ВТ стал в последние годы очень запутанным. В

связи с усложнением архитектуры машин и наделением ка-

* Всюду будет иметься в виду и радиоэлектроника тоже»

- 28 -

тегорий их (супер-ЭВМ, большие универсальные, супермини-

ЭВМ, малые коммерческие, мини-ЭВМ, персональные ЭВМ,тек¬

стовые процессоры, терминалы) проводились исследования

зависимости стоимости от производительности и справед¬

ливости закона Гроша. Доказывается, что закон Гроша ос¬

тается в силе, но теряет свою универсальность: он ока¬

зывается справедливым внутри отдельных категорий ЭВМ.

При этом коэффициенты в формуле закона Гроша оказывают¬

ся разными для разных категорий. В целом выгоднее, на¬

пример, использовать супер-ЭВМ по сравнению с большими

универсальными машинами; однако не только экономические

соображения определяют целесообразность приобретения

той или иной системы /7,8/.

Развитие разных категорий ЭВМ происходит неравно -

мерно.Считают, что 1984 г. был годом микро-ЭВМ, а 1985г.

явился годом больших универсальных машин /9/. По прог -

нозу, сумма продаж универсальных ЭВМ с 1982 по 1987 г.

возрастет с 11,9 до 15,2 млрд.долл, (на 28%, то есть на

5% в год), а доля этих ЭВМ на всем рынке перечисленных

выше категорий упадет за то же время с 42,5 до 26,2%.

Наиболее стремительно растет рынок персональных ЭВМ: с

3,9 до 19,4 млрд.долл, за гот же период ( на 397%, то

есть на 38% в год), а доля их от общего рынка вырастет

с 3,9 до 33,4 %. Весь рынок вырастет с 28 до 58 млрд,

долл, (на 107%, то есть на 16% в год) /8/.

Очень интенсивно развивается рынок супер-ЭВМ. Пер¬

вые из современных супер-ЭВМ, которые иногда называют

супер-ЭВМ 2-го поколения*, появились 10 лет назад, ког¬

да в марте 1976 г. была поставлена в Лос-Аламосскую на¬

циональную лабораторию ЭВМ Cray 1 . Машина была постав¬

лена условно, и официальная продажа состоялась только

после полугодовой успешной эксплуатации. Фирма ожидала

тогда, что спрос составит с десяток таких машин. Однако

♦ К первому поколению относят ILLIAC—IV , единственный экземп¬

ляр которой был создан фирмой Burroughs в Иллинойском универ¬

ситете, машину ASC , выпущенную фирмой Texas Instruments

в 7 экз., и STAR—100 фирмы CDC (в 4-х экэ.)

-.29 -

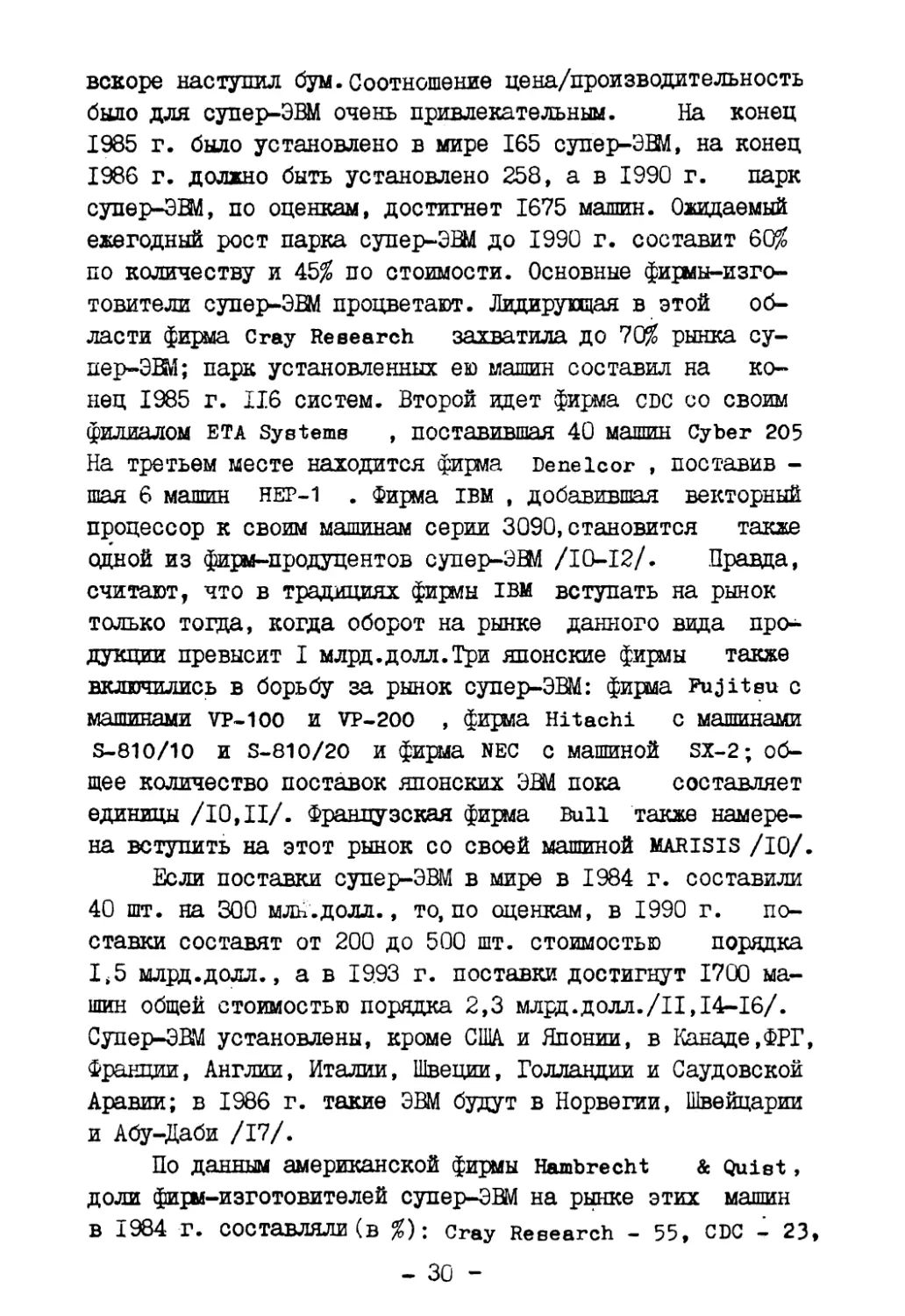

вскоре наступил бум. Соотношение цена/производительность

было для супер-ЭВМ очень привлекательным. На конец

1985 г. было установлено в мире 165 супер-ЭВМ, на конец

1986 г. должно быть установлено 258, а в 1990 г. парк

супер-ЭВМ, по оценкам, достигнет 1675 машин. Ожидаемый

ежегодный рост парка супер-ЭВМ до 1990 г. составит 60$

по количеству и 45% по стоимости. Основные фирмы-изго¬

товители супер-ЭВМ процветают. Лидирующая в этой об¬

ласти фирма Cray Research захватила до 70% рынка су¬

пер-ЭВМ; парк установленных ею машин составил на ко¬

нец 1985 г. 116 систем. Второй идет фирма cdc со своим

филиалом eta Systems , поставившая 40 машин Cyber 205

На третьем месте находится фирма Deneicor , поставив -

шая 6 машин нер-1 . Фирма IBM , добавившая векторный

процессор к своим машинам серии 3090,становится также

одной из фирм-продуцентов супер-ЭЕМ /10-12/. Правда,

считают, что в традициях фирмы IBM вступать на рынок

только тоцца, когда оборот на рынке данного вида про¬

дукции превысит I млрд.долл.Три японские фирмы также

включились в борьбу за рынок супер-ЭВМ: фирма Fujitsu с

машинами VP-1OO и vp-200 , фирма Hitachi с машинами

S-810/10 и S-810/20 и фирма nec с машиной sx-2; об¬

щее количество поставок японских ЭВМ пока составляет

единицы /10,11/. Французская фирма Bull также намере¬

на вступить на этот рынок со своей машиной marisis /10/.

Если поставки супер-ЭВМ в мире в 1984 г. составили

40 шт. на 300 млн.долл., то, по оценкам, в 1990 г. по¬

ставки составят от 200 до 500 шт. стоимостью порядка

1,5 млрд.долл., а в 1993 г. поставки достигнут 1700 ма¬

шин общей стоимостью порядка 2,3 млрд.долл./II,14-16/.

Супер-ЭЕМ установлены, кроме США. и Японии, в Канаде,ФРГ,

Франции, Англии, Италии, Швеции, Голландии и Саудовской

Аравии; в 1986 г. такие ЭВМ будут в Норвегии, Швейцарии

и Абу-Даби /17/.

По данным американской фирмы Hambrecht & Quist,

доли фирм-изготовителей супер-ЭЕМ на рынке этих машин

В 1984 Г. составляли (в %); Cray Research - 55, CDC - 23,

- 30 -

pujiteu - 5,Hitachi - 5, и т.д. ,a в 1990 г. составят

(в $): Research ~ 38» CDC/ETA - 21, Pujitsu - 11 ,

Hitachi - 10, нес - 8, прочие - 12. Из поставок 1984 г.

50^ использовались в правительственных организациях,40$

в коммерческих фирмах и 10$ в университетах и научно-

исследовательских организациях;ожидаемое распределение в

1990 г. будет несколько иным:30,50 и 20$ соответственно

/15/, Цо некоторым оценкам,из 180 установленных и наме -

ченных к установке супер-ЭВМ 30 приходится на универси¬

теты, в том числе II в США, 8 в Западной Европе,6 в Япо¬

нии И 2 в Канаде /12/.

Широкое распространение супер-ЭВМ и интенсивное их

использование приводит к тому, что ставятся на повестку

дня задачи (например, из области ядерпого оружия и изу¬

чения плазмы), требующие от десятков до тысяч часов ра¬

боты существующих супер-ЭВМ. В связи с этим интенсивно

ведутся работы по созданию все более совершенных супер¬

ЭВМ, в частности, с производительностью до 1000 млрд,

оп.пл.зап./с. Прямые и косвенные ассигнования на НИОКР

в этой области в США составляют 8,14 млрц.долл. на 10

лет(то есть приблизительно столько же, сколько и на раз¬

работку обитаемой космической лаборатории), в том числе

3,35 млрц.долл. по линии федеральных ведомств (2,2 -DOD,

0,2 - NSF , 0,2 - DOE , 0,6 - NASA ), 2,5 МЛрЦ. ДОЛЛ,

вкладывают промышленные фирмы и 2,3 млрц.долл. - различ¬

ные консорциумы и университеты /II/.

В настоящее время общее количество потенциальных

пользователей ЭВМ класса Cray оценивается в 30000.Од¬

нако многие фирмы и учебные заведения не могут позво -

лить себе приобрести в свое пользование супер-ЭВМ из-за

их высокой цены (до 10-15 млн.долл.), хотя и нуждаются

в машинах более высокопроизводительных, чем имеющиеся

суперыини-ЭВМ. Выходом из положения оказываются появив¬

шиеся недавно минисупер-ЭВМ ( minisupercomputer?, near¬

supercomputers, Crayettea, entry level supercomputers,

Minisupers.affordable supersomputers ), обеспечивающие

производительность лишь раза в 4 меньше производительно-

- 31

сти супер-ЭЕМ, но зато при цене раз в 10 меньшей /16,

18/.

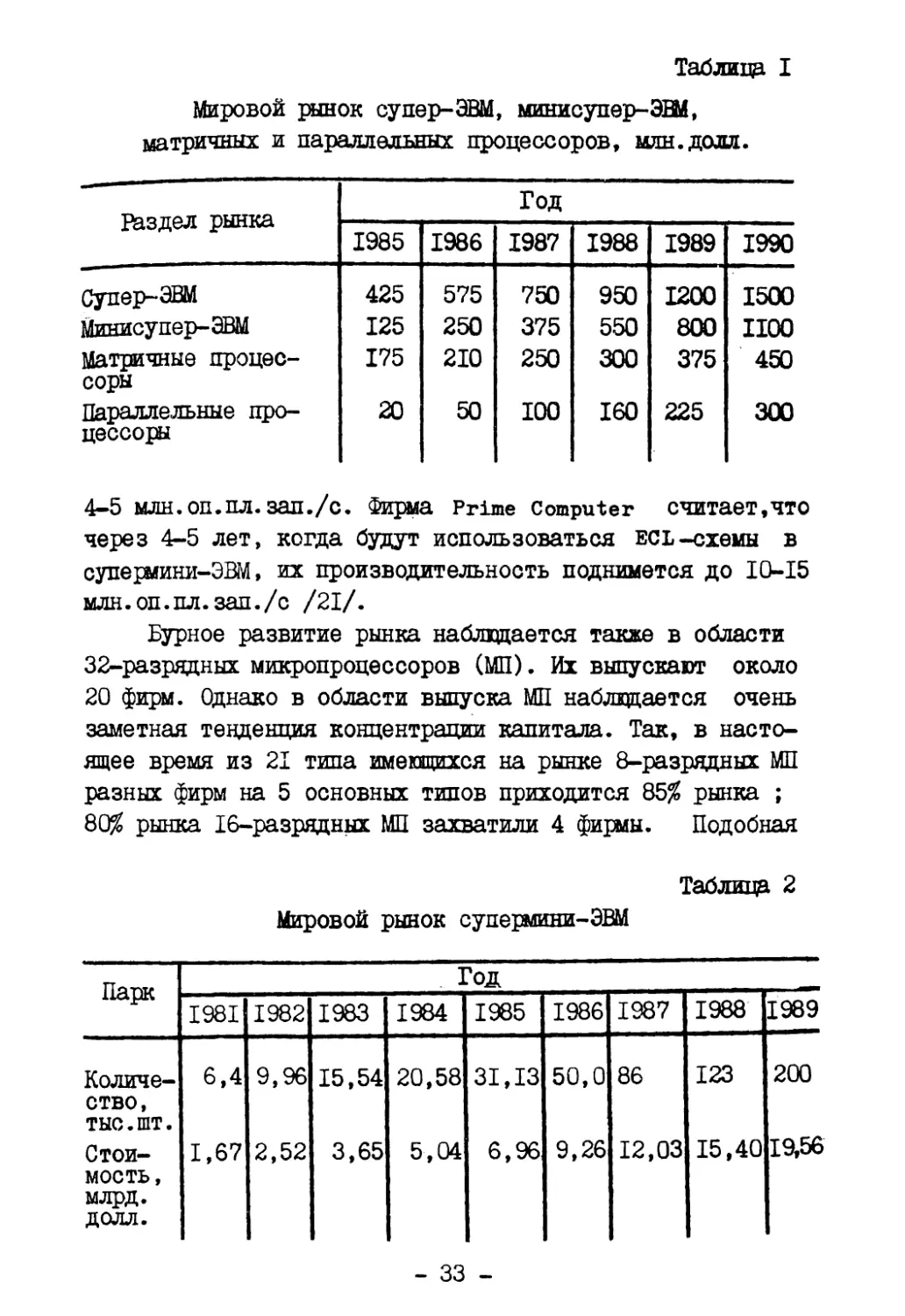

Первой фирмой, выпустившей такую машину в сентябре

1984 Г., была фирма Convex Computer Corp.; ДО конца

1985 г. она уже продала 80 шт. До десятка фирм, в ос¬

новном мелких, начали также разрабатывать и выпускать

подобные маптинн, иногда совместимые по ПО с машинами се¬

мейства Cray /10,16/. На рынке супер-ЭЕМ сложился от¬

дельный сектор минисупер-ЭВМ; рост его ожидается с 125

млн.долл, в 1985 г. до 1,1 млрд.долл, в 1990 г. ( рост

40-60% в год) /16,19/.

Другим выходом для маломощных организаций, нуждаю¬

щихся в супер-ЭВМ, является установка больших серийных

универсальных ЭВМ (чаще всего фирмы IBM) совместно с

матричными процессорами (в частности,фирмы fps ), что

позволяет при сравнительно небольших затратах получать

достаточно высокую производительность /12/. Продажи мат¬

ричных процессоров за 1985-1990 гг. будут возрастать на

25% в год /19/.

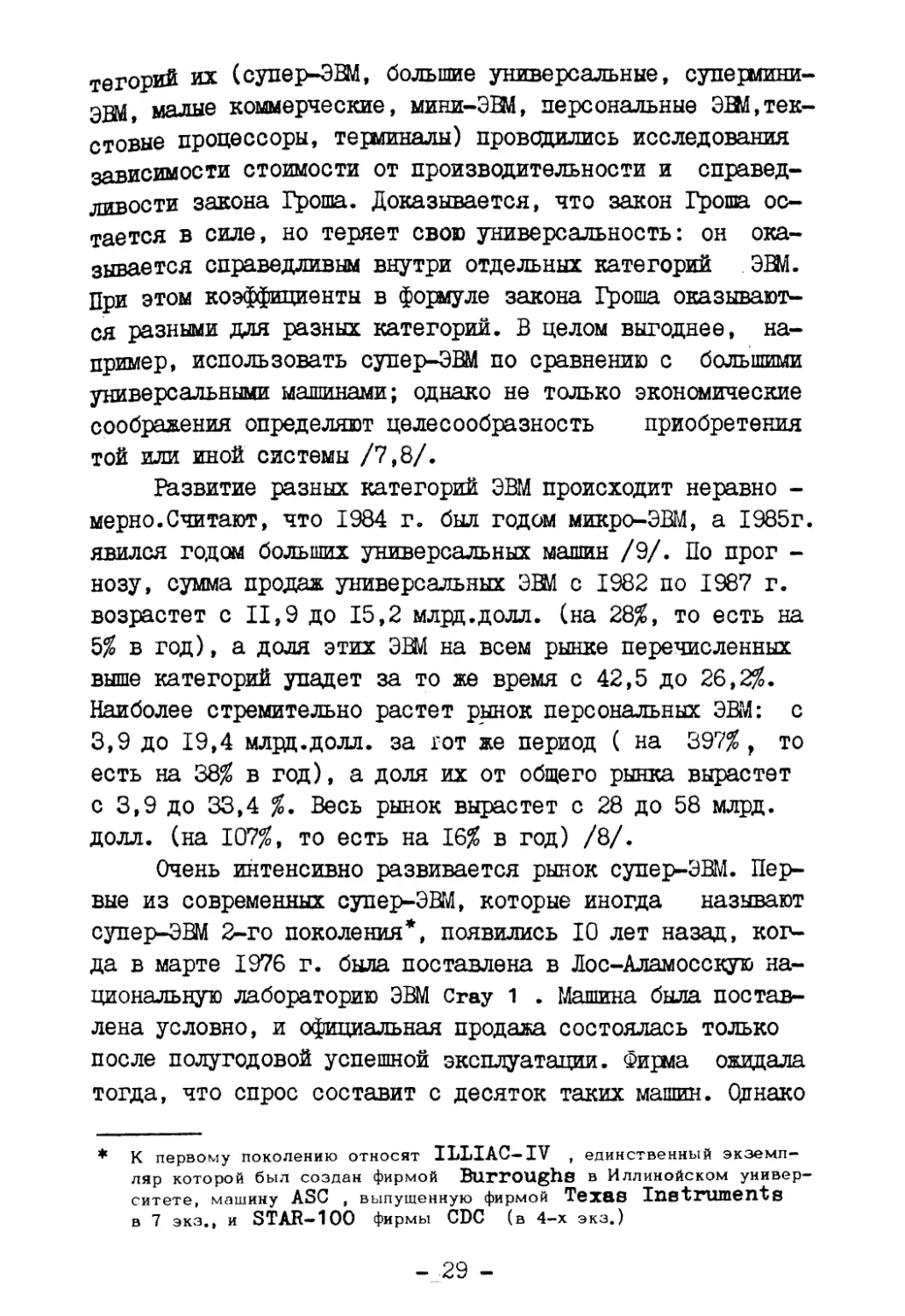

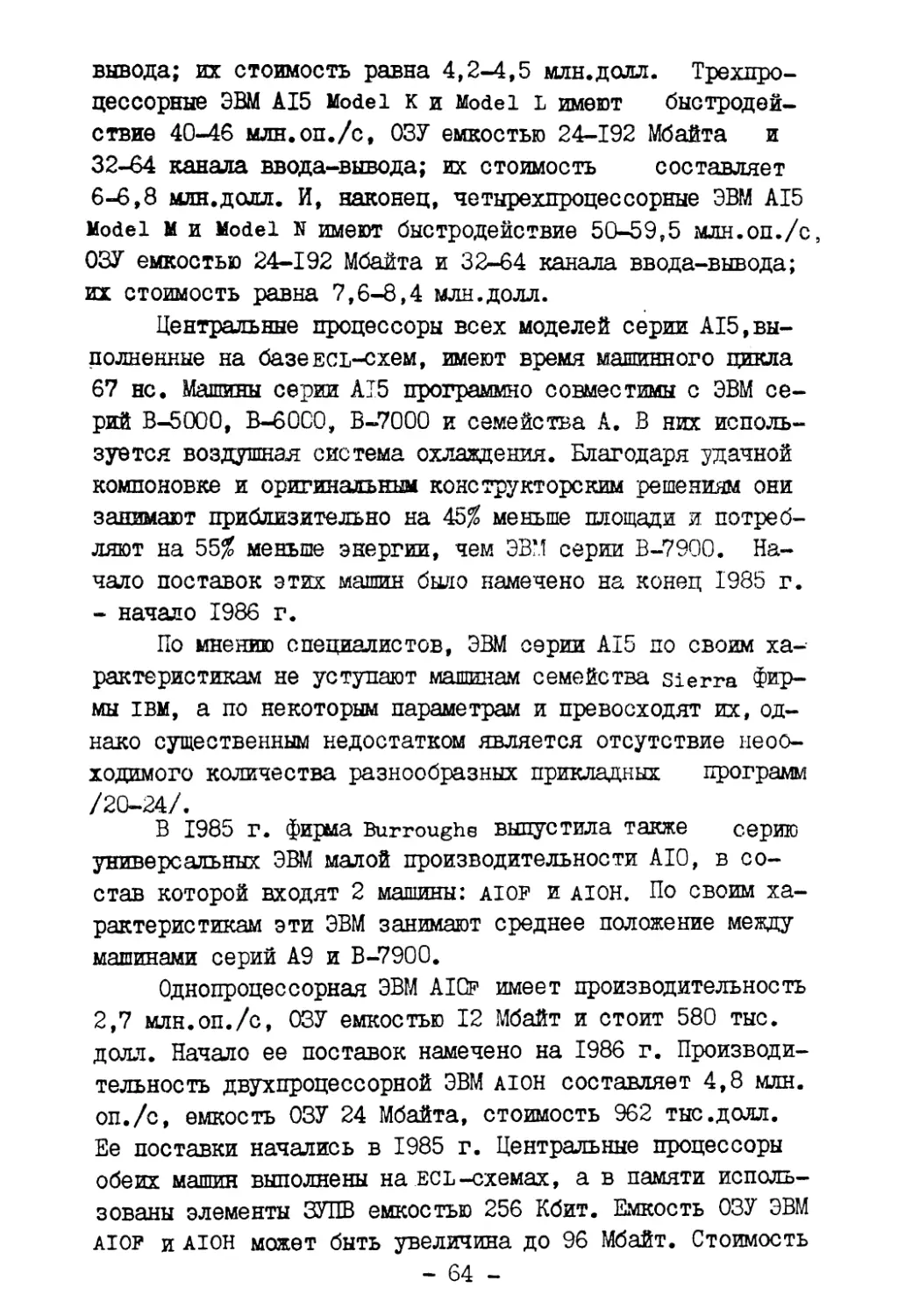

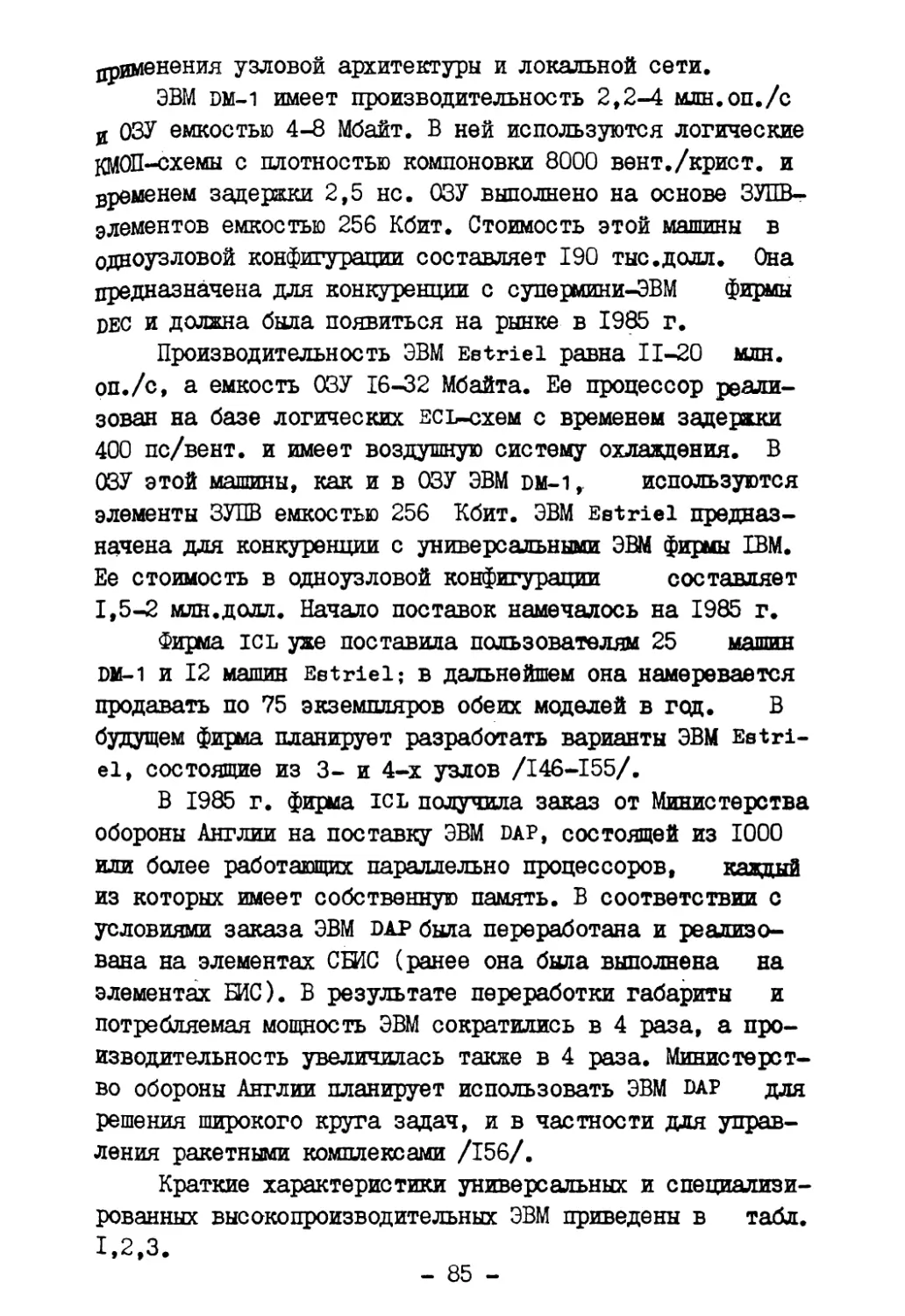

В 1985 г. появился новый подкласс машин, которые

условно можно назвать параллельными процессорами. Это

машины со специализированной архитектурой, позволяющей

использовать внутренний параллелизм задач и тем самым

получать очень высокую производительность. Такие машины

выпускают фирмы Intel (ЭВМ iPSC ), BBN Inc (Butter¬

fly) и некоторые другие. Прогноз мировых продаж описан¬

ных четырех видов высокопроизводительных ВС приведен в

табл.1 /16/.

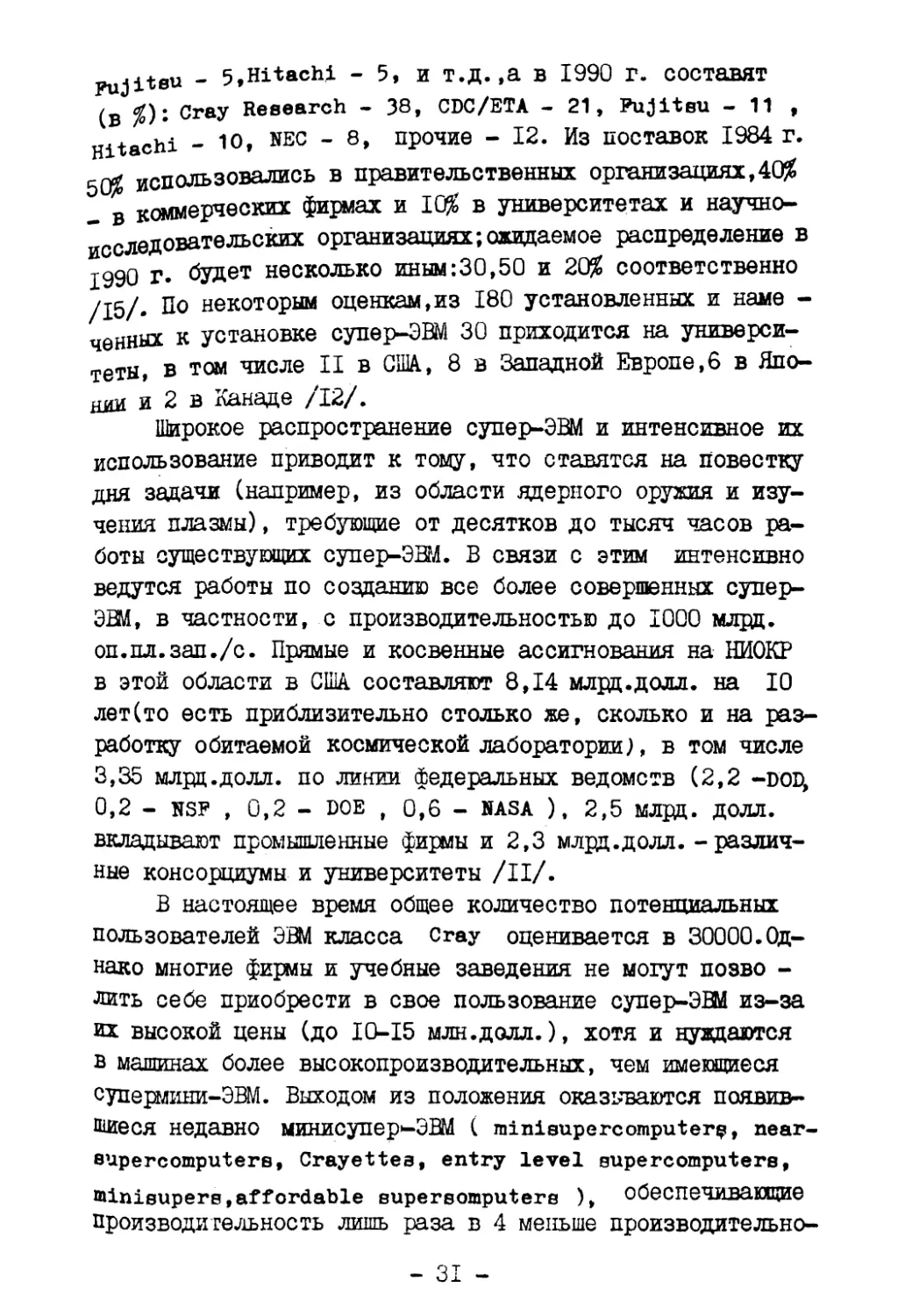

Продолжал быстро развиваться рынок супермини-ЭВМ.

В 1985 г. он достиг почти 7, а в 1989 г. достигнет поч¬

ти 20 млрд.долл. (табл.2). Для сравнения указано, что

мировой рынок больших универсальных ЭВМ составлял в

1983 г. 16 млрд.долл. /20/. По данным другого источника,

мировые продажи супермини-ЭВМ в 1984 г. составили 8,94

млрд.долл. При этом на долю Фирмы IBM приходилось 41,9,

DEC-27,6, Data General-6, Prime Computer-5,6% И т.д.

Большинство машин этого класса имеет производительность

- 32 -

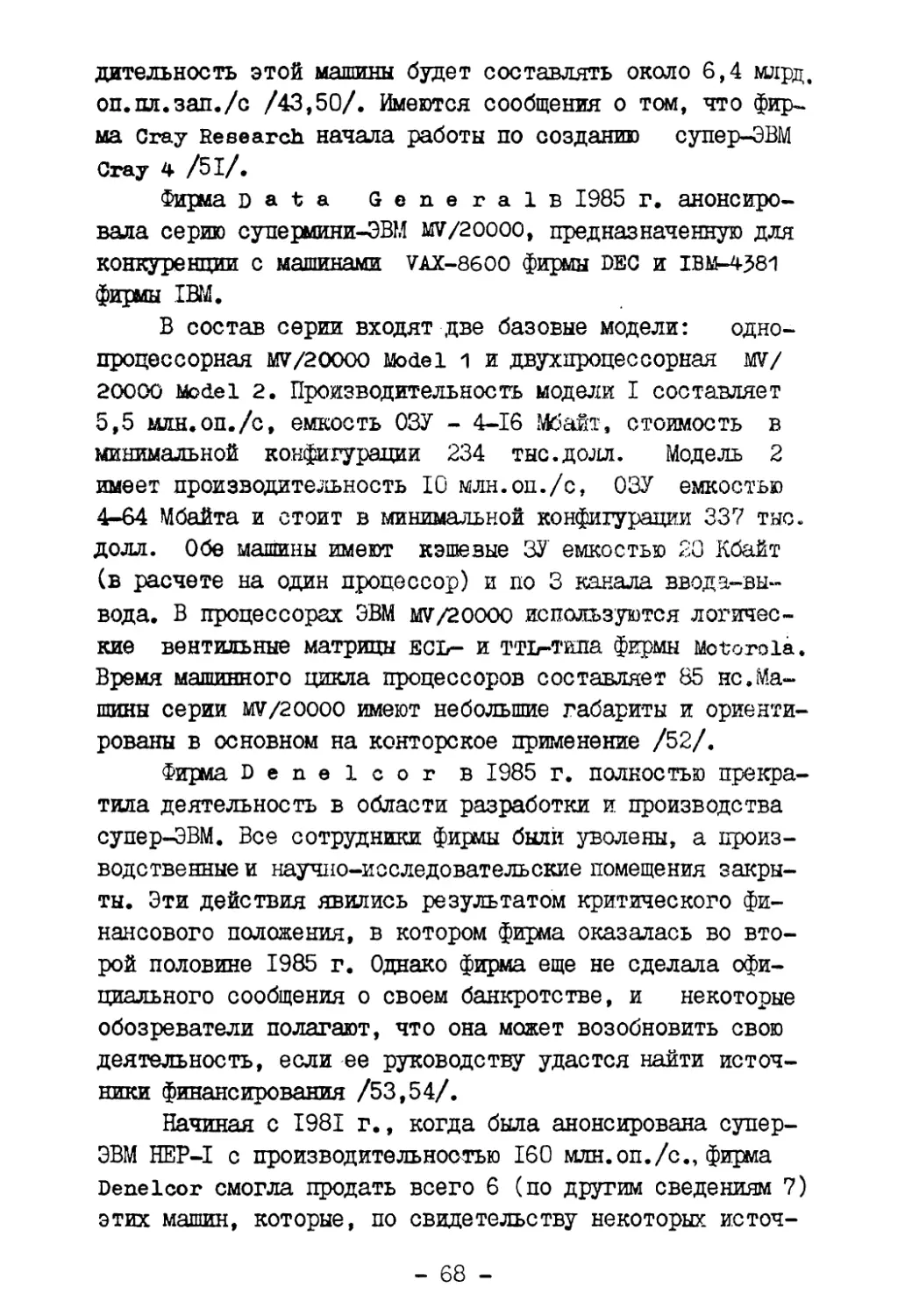

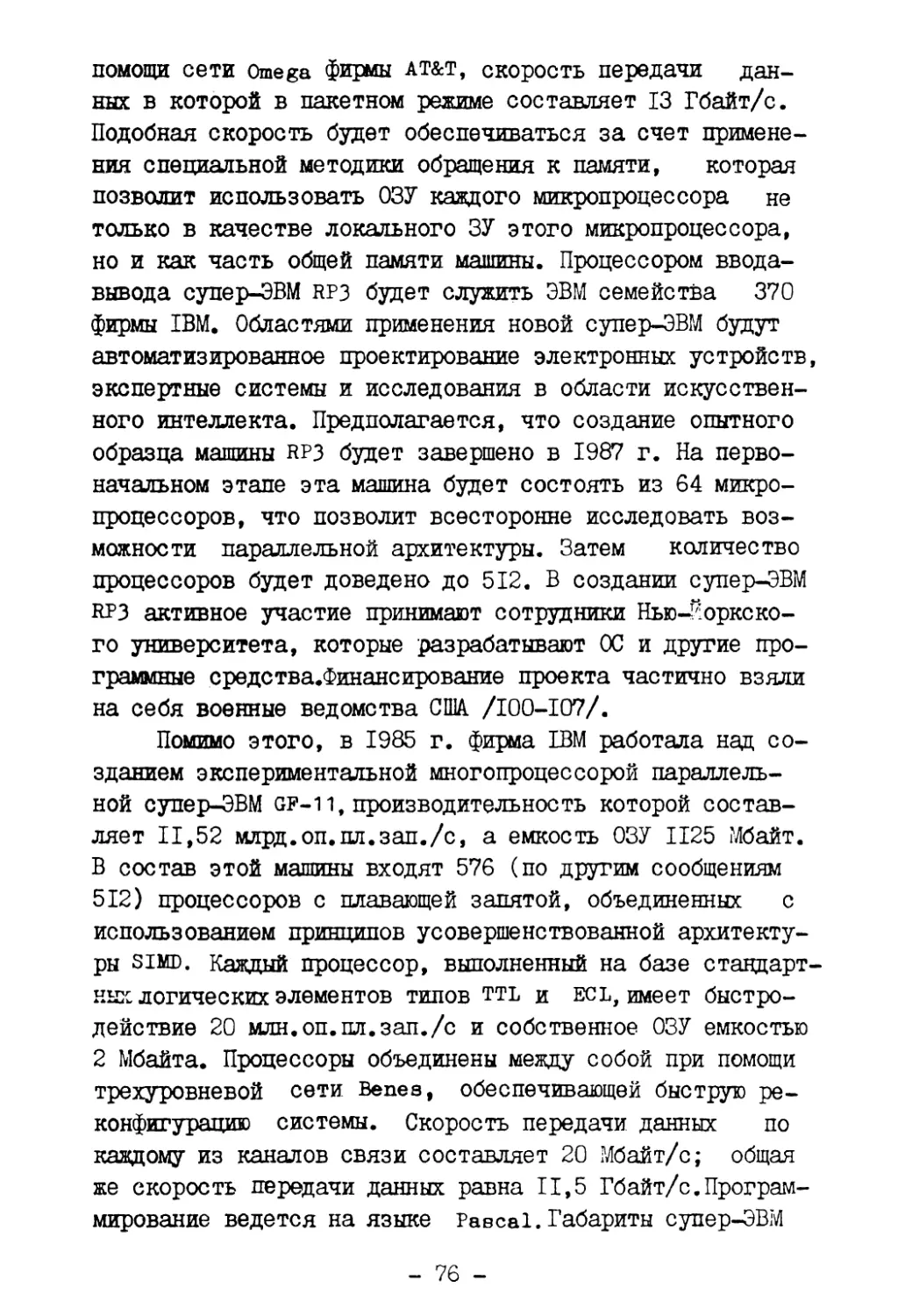

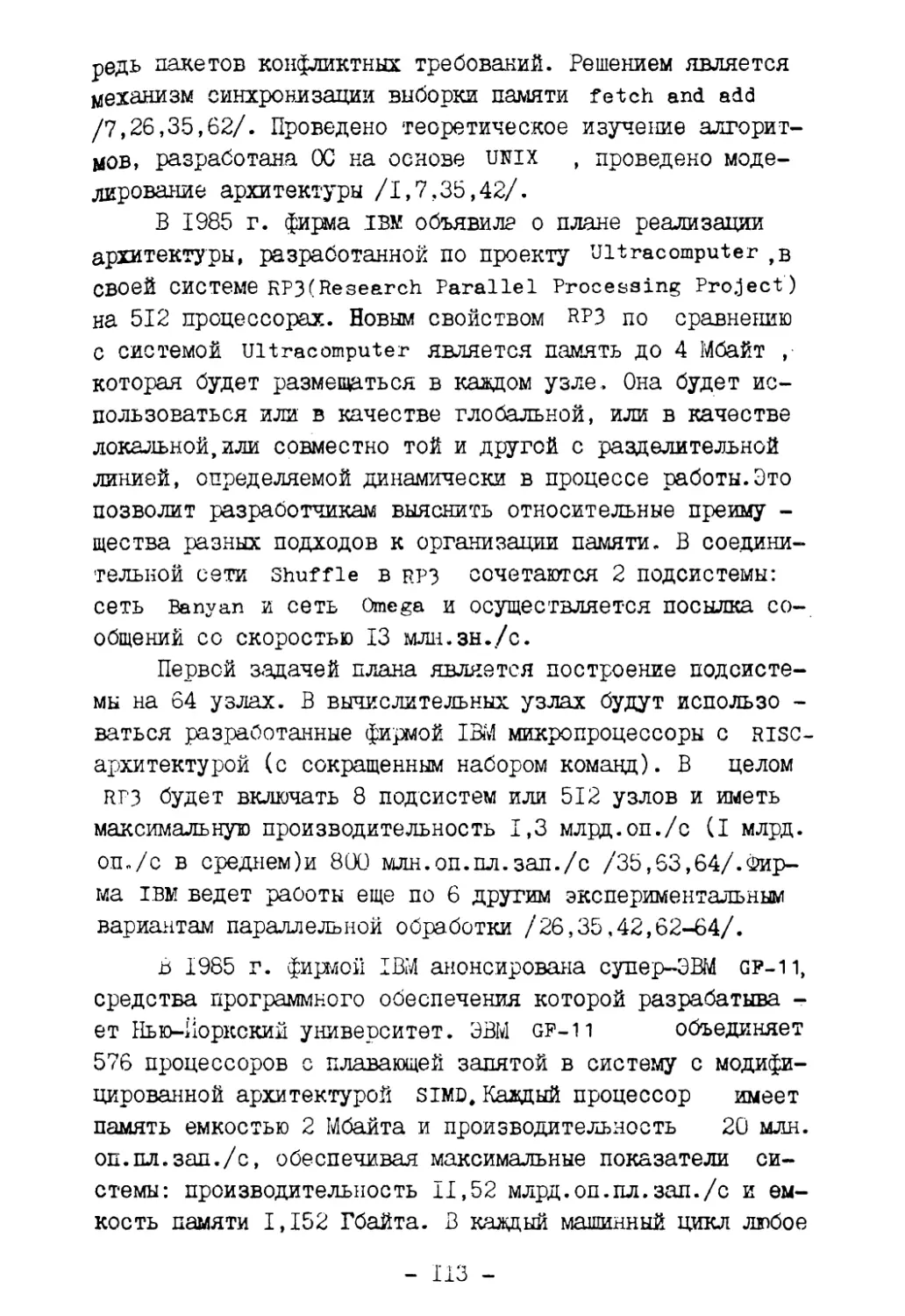

Таблица I

Мировой рынок супер-ЭВМ, минисупер-ЭВМ,

матричных и параллельных процессоров, млн. долл.

Раздел рынка

Год

1985

1986

1987

1988

1989

1990

Супер-ЭВМ

425

575

750

950

1200

1500

Минисупер-ЭВМ

125

250

375

550

800

1100

Матричные процес¬

соры

175

210

250

300

375

450

Параллельные про¬

цессоры

20

50

100

160

225

300

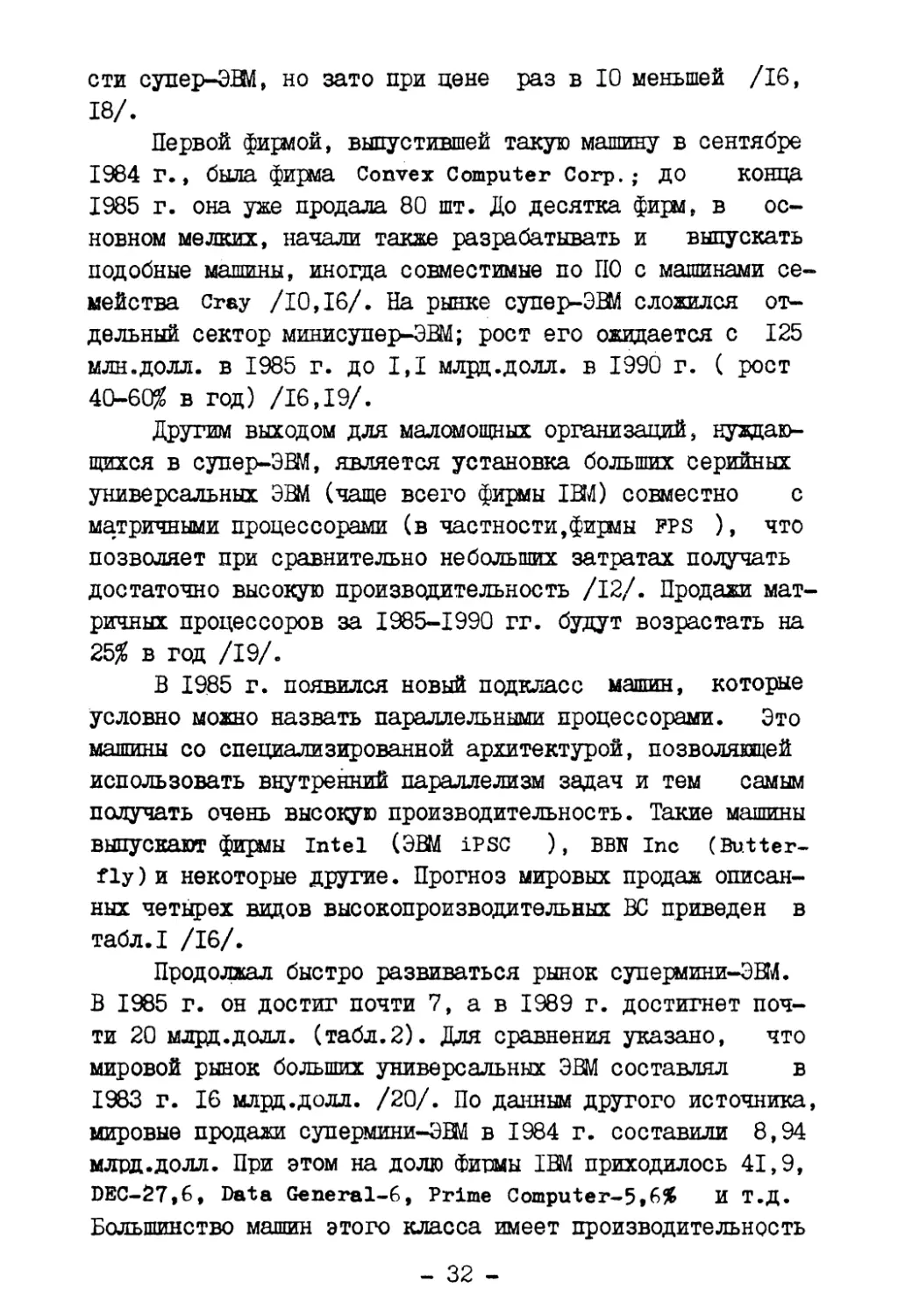

4-5 МЛН.ОП.пл. зап./с. Фирма Prime Computer считает,ЧТО

через 4-5 лет, когда будут использоваться ECL—схемы в

суперыини-ЭВМ, их производительность поднимется до 10-15

млн.оп.пл.зап./с /21/.

Бурное развитие рынка наблюдается также в области

32-разрядных микропроцессоров (МП). Их выпускают около

20 фирм. Однако в области выпуска МП наблюдается очень

заметная тенденция концентрации капитала. Так, в насто¬

ящее время из 21 типа имеющихся на рынке 8-разрядных МП

разных фирм на 5 основных типов приходится 85% рынка ;

80% рынка 16-разрядных МП захватили 4 фирмы. Подобная

Таблица 2

Мировой рынок суперыини-ЭВМ

ГТ О ТУГГ

Год

llcipK

1981

1982

1983

1984

1985

1986

1987

1988

1989

Количе¬

ство,

тыс.шт.

6,4

9,96

15,54

20,58

31,13

50,0

86

123

200

Стои¬

мость ,

млрд,

долл.

1,67

2,52

3,65

5,04

6,96

9,26

12,03

15,40

19,56

- 33 -

перспектива ожидается и для 32-разрядных МП. Появления

64- и 128-разрядных МП не ожидается главным образом из-

за большой сложности архитектуры супермини-ЭВМ, созда¬

ваемых на уровне кристалла и работающих на языках высо¬

кого уровня. В 1984 г. было продано около 100 тыс. кри¬

сталлов 32-разрядных МП; в 1990 г. ожидается продажа

4,7 млн.шт. Рост мировых продаж 32-разрядных МП ожида¬

ется следукщим(млн.долл.): 1984 г. - 1,2; 1985 г. -

16,8; 1986 г. - 36,1; 1987 г. - 57,8; 1988 г. - 89,6 ;

1989 Г.-134.4 и 1990 г. - 194,8 /22/.

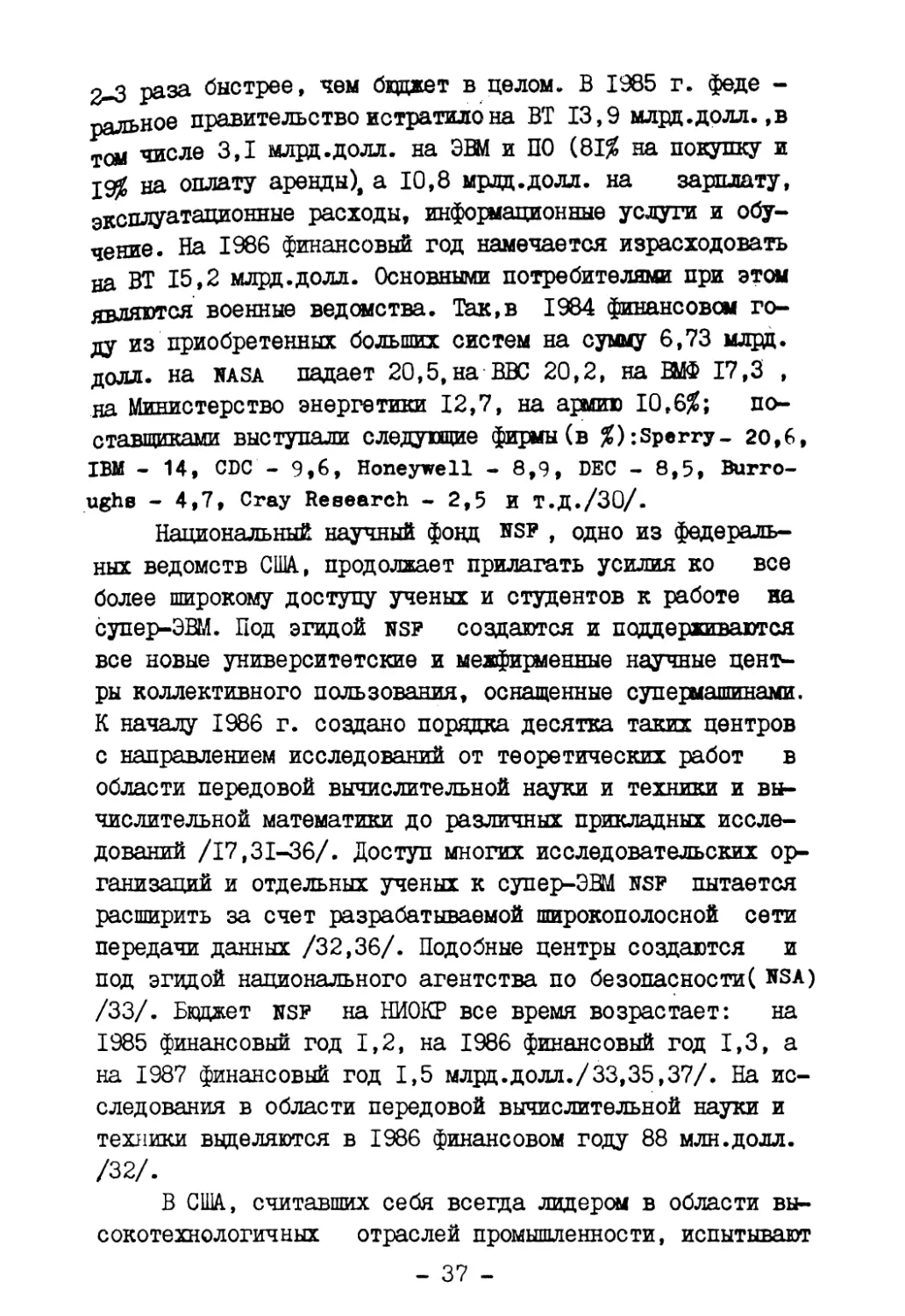

США . Прошедший 1985 г. был годом спада экономи¬

ки, затронувшим и область электроники. По данным жур¬

нала " Electronics" , в конце 1985 г. наметился некою -

рый подъем /23/. Реальный ВНП США. в 1985 г. увеличился

лишь на 3%, а в 1986 г. ожидается рост на 4%; по другим

оценкам, рост ВНП в течение ближайших 10 лет в среднем

составит 2,8% в год /24/. Обращается внимание на то,что

объем капиталовложений в 1986 г. в большинстве основных

отраслей промышленности сократится на 1%, а это означа¬

ет снижение спроса на вычислительное оборудование. Кро¬

ме того, много оборудования было закуплено в 1984 г. и

его еще не все задействовали. Сумма продаж средств ВТ

в 1985 г. составила 57,4 млрд.долл., а в 1986 г. должна

достичь 65,3 млрд.долл., что составит 49% от суммы про¬

даж всех средств электроники 131,8 млрд.долл. (табл.З).

Сумма продаж вычислительных систем в 1985 г. составила

28,5 млрд.долл., а в 1986 г., по оценкам, составит 32,0

млрд.долл. Наибольший рост продаж из всех категорий ЭВМ

приходится на супер-ЭВМ - 62%/23/. Рынок средств ВТ ста¬

новится все более зрелым; этим объясняют замедление тем¬

пов его роста. Если в 1984 г. рост объема продаж соста¬

вил порядка 16% и по причине общего спада его рост соста¬

вил в 1985 г. 10%, то в 1986 г. ожидается его рост на

15%, а в последующие 5 лет рост снизится до 12% в год

/25/.

Продолжают сохраняться трудности в связи с разра-

- 34 -

Таблица 3

Сумма продаж средств ВТ в США., млн. долл.

Вид оборудования

Год

1984

1985

(оценка)

1986

(прогноз)

ЭВМ, всего

в том числе:

25568

28090

31956

супер-ЭВМ

520

840

1020

универсальные ЭВМ

(0,4-5 млн.долл.)

8290

8870

9897

супермини-ЭВМ

(100-400 тыс.долл.)

6545

7060

7836

мини-ЭВМ (20-100 тыс.долл.)

5870

6395

7099

микро-ЭВМ (5-20 тыс.долл.)

2374

2778

3361

персональные ЭВМ

(< 5 тыс.долл.)

1180

1090

1260

AIM

789

1057

1483

Подсистемы ЗУ

5624

6274

7312

Цифровые терминалы

6834

7459

8417

Системы ввода-вывода

5930

6630

7821

Средства автоматизации кон¬

торской деятельности

7785

8920

9783

боткой программного обеспечения. Требования к объему ПО

растут на 20-25% в год, а численность программистов воз¬

растает только на 5-6%. Для решения этой проблемы, в

частности, создается специальная аппаратура для облег -

чения разработки ПО(например, машина R-ЮОО фирмы Ra¬

tional) . Примером сложности создаваемого ПО является ПО

для управления космическими станциями 90-х годов, объем

которого будет исчисляться десятками миллионов строк

программы /26/.

Наиболее важными событиями на рынке ВТ США в 1985г.

были следующие :

ввделение на рынке супер-ЭВМ рынка минисупер-ЭВМ и

- 35 -

мультипроцессоров (параллельных процессоров);

анонсирование фирмой ibm ЭВМ Sierra и начало

поставок машин этого семейства IBM-3090/200:

появление Micro VAX и фирмы вес (машины типа

VAX на одном кристалле );

усиление борьбы в области полупроводников (chip

war ) между США и Японией ;

анонсирование фирмой ibm кольцевой сети с мар¬

керным доступом Token Ring ;

большая равномерность по месяцам объема суммарного

оборота фирм в течение всего года ;

заметные признаки разрушения фирмы cdc;

затруднения ведущих в области разработки ПО фирм

( Lotus , Cullinet и др.).

Ожидаемые события на рынке ВТ в 1986 г.:

рост продаж больших ЭВМ на уровне 15%;

появление ЭВМ Spectrum (на основе Rise ) фирмы

Hewlett-Packard , что явится сигналом к усилению борь¬

бы между основными продуцентами ЭВМ ;

анонсирования фирмы IBM (монопроцессор из семейст¬

ва ibm-3090 , инженерное арм на 32-разрядном микро -

процессоре, новые модели ЭВМ серий 4300 и S/36 , новые

модели персональных ЭВМ );

появление дешевых персональных ЭВМ, совместимых с

мялтипями фирмы IBM ;

выпуск фирмой dec мультипроцессорного варианта

ЭВМ VAX ;

продолжение агонии фирмы с г*с ;

большие слияния в группе фирм bunch /9,27/.

Суммарная производительность парка больших и сред¬

них универсальных ЭВМ, установленных в США, составила в

1984 г. 180 млрд.оп./с, в том числе 41% за счет больших

и 59% за счет средних ЭВМ /28/.

В США в 1985 г. было более 5 млн. персональных ЭВМ,

а к концу десятилетия ожидается их 24,4 млн.шт./29/.

Федеральное правительство США большое внимание уде¬

ляет состоянию ВТ. Его бюджет на развитие ВТ растет в

- 36 -

2^3 раза быстрее, чем бюджет в целом. В 1965 г. феде -

ральное правительство истратило на ВТ 13,9 млрд .долл., в

том числе 3,1 млрд .долл. на ЭВМ и ПО (81% на покупку и

19% на оплату аренды), а 10,8 мрлд.долл. на зарплату,

эксплуатационные расходы, информационные услуги и обу¬

чение. На 1986 финансовый год намечается израсходовать

на ВТ 15,2 млрд.долл. Основными потребителями при этом

являются военные ведомства. Так,в 1984 финансовом го¬

ду из приобретенных больших систем на сумму 6,73 млрд,

долл, на rasa падает 20,5,на ВВС 20,2, на ВМФ 17,3 ,

на Министерство энергетики 12,7, на армию 10,6%; по¬

ставщиками выступали следующие фирмы (в %):Sperry_ 20,6,

IBM - 14, CDC - 9,6, Honeywell - 8,9, DEC - 8,5, Burro¬

ughs - 4,7, Cray Research - 2,5 И Т.Д./30/.

Национальный научный фонд hsf , одно из федераль¬

ных ведомств США., продолжает прилагать усилия ко все

более широкому доступу ученых и студентов к работе на

супер-ЭВМ. Под эгидой nsf создаются и поддерживаются

все новые университетские и межфирменные научные цент¬

ры коллективного пользования, оснащенные супермашинами.

К началу 1986 г. создано порядка десятка таких центров

с направлением исследований от теоретических работ в

области передовой вычислительной науки и техники и вы¬

числительной математики до различных прикладных иссле¬

дований /17,31-36/. Доступ многих исследовательских ор¬

ганизаций и отдельных ученых к супер-ЭВМ nsf пытается

расширить за счет разрабатываемой широкополосной сети

передачи данных /32,36/. Подобные центры создаются и

под эгидой национального агентства по безопасности( HSA)

/33/. Бвджет ksf на НИОКР все время возрастает: на

1985 финансовый год 1,2, на 1986 финансовый год 1,3, а

на 1987 финансовый год 1,5 млрц.долл./33,35,37/. На ис¬

следования в области передовой вычислительной науки и

техники выделяются в 1986 финансовом году 88 млн.долл.

/32/.

В США, считавших себя всегда лидером в области вы¬

сокотехнологичных отраслей промышленности, испытывают

- 37 -

все большее беспокойство достижениями Японии в области

технологии. Со своей стороны Япония в конкурентных уси¬

лиях обогнать США отмечает, что в США. из 60 млрд.долл,

федерального бюджета на 1986 г. 40 млрд.долл, предна -

значены на НИОКР Министерства обороны США., то есть в

основном на высокотехнологичные отрасли промышленности.

Японский бвджет на НИОКР составляет около 6 млрд.долл.,

то есть в 7 раз меньше американского /38/. В. США про¬

вели анкетный опрос большого количества фирм в области

электроники. Свыше 80% ответивших считают, что США опе¬

режают Японию в области ЭВМ и ПО, а менее 10% имеют про¬

тивоположное мнение; 50% считают, что Япония опережает

США в области технологии изготовления и производства

(packaging and production); 85% считают, что Япония

превосходит США по производительности труда.Только 59%

опрошенных считают, что лидером в области электронной

техники в 2000 г. будут США, 34% - что Япония, а 1% от¬

дает первое место Западной Европе /39/.

Положительный мировой торговый баланс США в облас¬

ти ВТ с 5,78 млрд.долл, в 1983 г. снизился до 4,75 млрд,

долл, в 1984 г. (на 17,8%). Однако по отношению к Япо -

нии ситуация другая: экспорт ЭВМ из США в Японию в

1984 г. составил 1,15 млрд.долл., а экспорт из Японии

в США - 3,2 млрд.долл. Общий дефицит США в торговле с

Японией в 1984 г. составил 4,1 млрд.долл.(вырос за год

на 77,9%) /40/.

Рост объема американских продаж ЭВМ и конторского

оборудования в мире характеризуется следующими данными

(млрд.долл.): 1985 г. - 61,3, 1986 Г.-67.7, 1987 г. -

77,4, 1988 г. - 91,5, 1989 г. - 102,6, 1990 г. - III,4,

1995 г. - 191,4 /41/. Увеличение стоимости доллара (до

50% по сравнению с 1980 г.) по отношению к иностранным

валютам приводит к затруднениям для американских элек -

тронных фирм в международных торговых операциях, снижа¬

ет их доходы /42/.

В США в среднем по всем фирмам в области ВТ на рек¬

ламу расходуется все большая часть дохода (%): 1981 г.

- 38 -

_ 0,89, 1982 г. - 1,0, 1983 г. - 1,43, 1984 г. - 1,64.

В абсолютных величинах это выглядит так (млн.долл.):

1982 г. - 850, 1983 г. - 1380, 1984 г. - 1865, 1985 г.

(по оценке) - 2140, в том числе по фирмам в 1984 г.( в

МЛН.ДОЛЛ.): IBM - 518, Apple - 180, DEC - 91, Tandy-74,

jjeWlett-Packard - 65, Commodore - 62, NCR - 60, CDC -42,

aT&t - 40, Wang - 39, а всего no 10 первым по величи¬

не этих расходов фирмам 1175 млн.долл. Однако ана¬

лиз расходов на рекламу фирм в области ВТ показывает,

что для фирм-продуцентов больших универсальных ЭВМ чис¬

ло конкурентов невелико, объяснять роль своей продукции

не столь необходимо, как для поставщиков супермини-ЭЕМ,

систем автоматизации учрежденческой деятельности, авто¬

матизации проектирования, персональных ЭВМ, ПО и внеш¬

него оборудования,да и продажи больших машин в основном

идут на уровне фирм, а не частным лицам. Поэтому доля

расходов на рекламу от суммы доходов фирм оказывается

меньшей для крупных фирм, чем для малых, (в : ibm-1,2;

DEC - 1,6; CDC - I,I,a Apple - 11,8; Tandy - 8,1; Com¬

modore - 4,9 и т.д. /43,44/. Вообще вопросы сбыта на¬

ходятся всегда в центре внимания фирм. Так, например,в

фирме IBM все сотрудники отделов сбыта 20 дней в году

проходят переподготовку /44/.

Борьба монополий за рынки сбыта приводит ко все

большему взаимопроникновению фирм одной страны на ры¬

нок другой, все больше возрастает роль транснациональ -

ных корпораций и все больше теряются национальные осо¬

бенности отдельных фирн. Отражением этого является объе¬

динение журналом "Datamation" данных по ведущим фирмам

в области ВТ всего мира в одну общую таблицу (табл.4).

Сумма продаж 100 крупнейших фирм мира в этой области в

1984 г. составила 132 млрд.долл. При этом,кроме фирм

США,в перечень вошли 26 фирм других стран, в том числе

7 - Японии, 6 - Англии, 5 - ФРГ, 3 - Франции и по I -

Италии, Швеции, Голландии, Финляндии и Норвегии/45,46/.

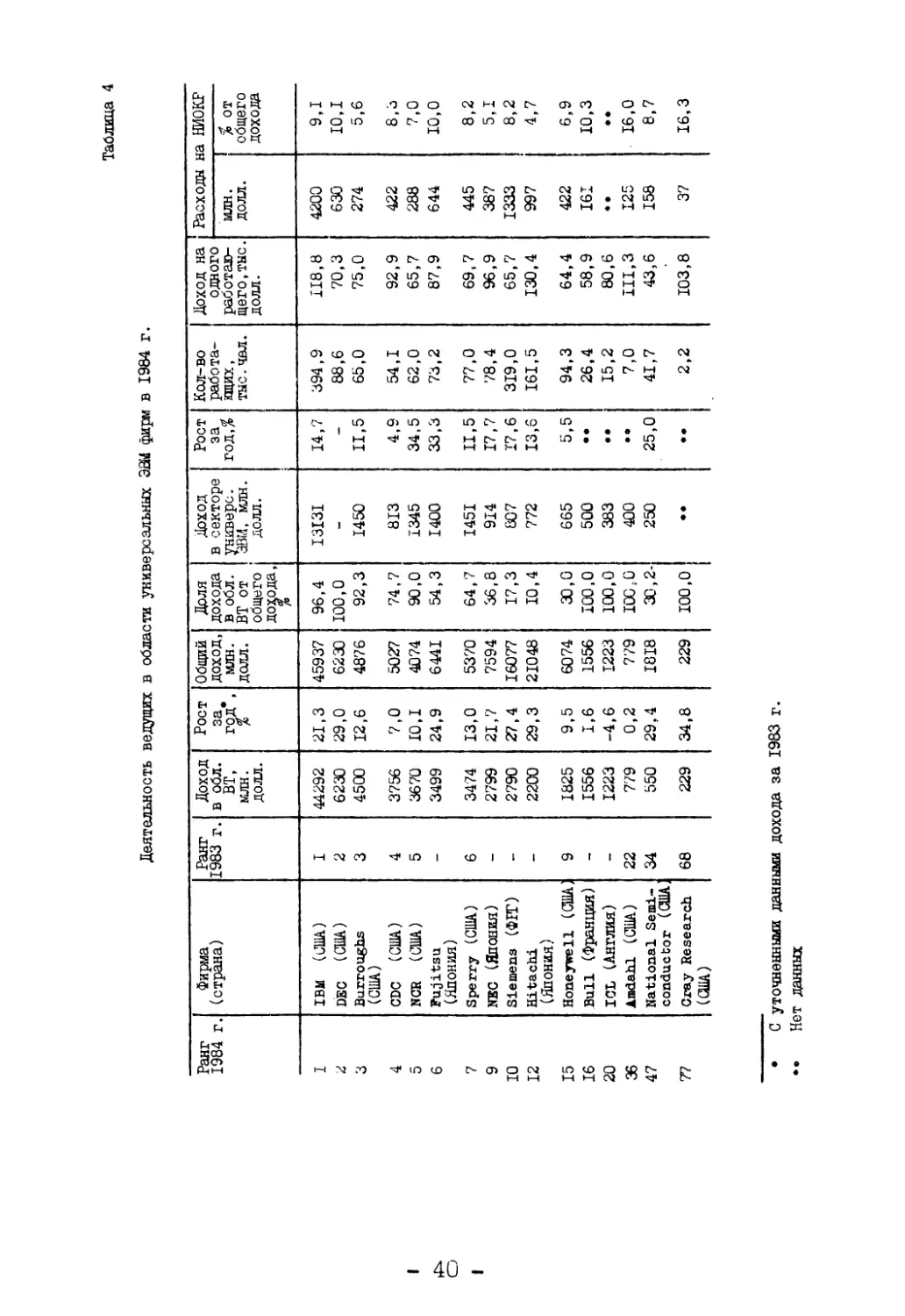

Среди фирм-изготовителей больших универсальных ЭВМ

наиболее быстрый среднегодовой рост за I98I-I985 гг.по-

- 39 -

эх

уло о

о Ч

t-i М <О О О О

СП О 1О СО О- О

00 со О СП О СП

00 О Ю C'J ю >

1-4 О- О СП СО СО

см i-i см г-

СО 1Л 00 4

О> СП О 4*

СП СО LD Q

<о Ф со со

СП СО О

О О • СО 00

со

со

4* сп со со со со

4* 00

со in

со

о

Деятельность ведущих в области универсальных ЭВМ фирм в 1984 г.

д ь

Зш

СП СО О Ы О см О 4* О Ю со 4* см о о см

■4» СО СО 4* см О о со’ СП 1-1 4* CD lO t>- ы см

СП СО со ID СО О !> > Н О СП СМ М 4*

.о со i-i

е< VC

О Д -

О со Ч

Оч о

Си

О LD СП ID СО Ю > Ф СО LO о

- 1 - “ -•••'• •

4* Ы 4* 4* СО Ж О- О- СО Ю • • • 1Л *

1-ЧИ со СО ы Ж Ж Ж см

0)

rtojg .

д

Ж Q СО ID О Ж 4* О' СМ Ю а П О Q •

СО ID Н 4 Q CD Ж Q Г- СО О СО О Ю «.

•—•14* СО СО 4* 4* СП 25 О- со ID СО 4* СМ

СО 1-1 1—1 к—1 1—«

ж

Д’ од

W fcf Ч ЕЧ р, t=(

►1000 1) О

OXO

40 КО О

4Д« О 14

СО О О СО Г- со СО 4* о о о о см о

4* О - - • - * * -

- -СМ 4 0 4 4* СО о- О Q Р Q Q О О

СО О СП О- СП tn СО СО Hl-ч соОООСО о

СП о ж ж ж ж

1—1

Общий

доход,

МЛН.

долл.

й8g &s3 gsfcs sms я

СП CM СО Q Q 4* СО m Q О Q ID СМ О СО СМ

ID СО 4* 25 4* СО ID О- СО Ж (2 Н Н 1—<

4* 1-1 СМ

%Ч-

о cd н

О coOVi.

СХ, Рч

СО О СО О Ж СП О>- 4* СО Ю СО СО СМ 4* СО

1—1 СП СМ 0 0 4* СО Ж г^. ф СП Ж 4* О СП 4*

СМ СМ Ж Ж СМ Ж СМ СМ СМ 1 см со

Доход

в обл.

ВТ,

млн.

долл.

CM О О СО О СП 4* ф Q Р ID СО СО СП О Ф

сп со о in г> сп ф сп о см ю см к со см

СМ СМ ю > ф 4 4 > > W 00 Ю СМ сП СМ

СО 4* СО СО СО (О СМ СМ СМ Ж Ж Ж

Ранг

1983 г.

ж см со 4*ioi <о 1 1 1 сп г 1 см ао

Фирма

(страна)

В 5 *£<

эыо Я S g из <й

55^ е5*§ ьё 3

в 22 Я§ »3

я о Pi Э о W -гэИ а> О Ф -Р £1 Д Н й <6 ₽ Я ей 3

« М d О Я О 3^ Л М Ж -Н« О 4 О В Сбо So

М Q 3}^ О Й Ь'- и g и И СР Н 4 » о о

Ранг

1984 г.

н \1 4* Ю СО К СП О CM LO <О О «О О

ЖЖ Н Н СМ СП 4* С-

С уточненными данными дохода за 1983 г.

Нет данных

40

казали следующие фирмы (в Cray Research - 44,3, Bur¬

roughs - 25,6, Amdahl - 16,9, IBM - 13,8 /47/.

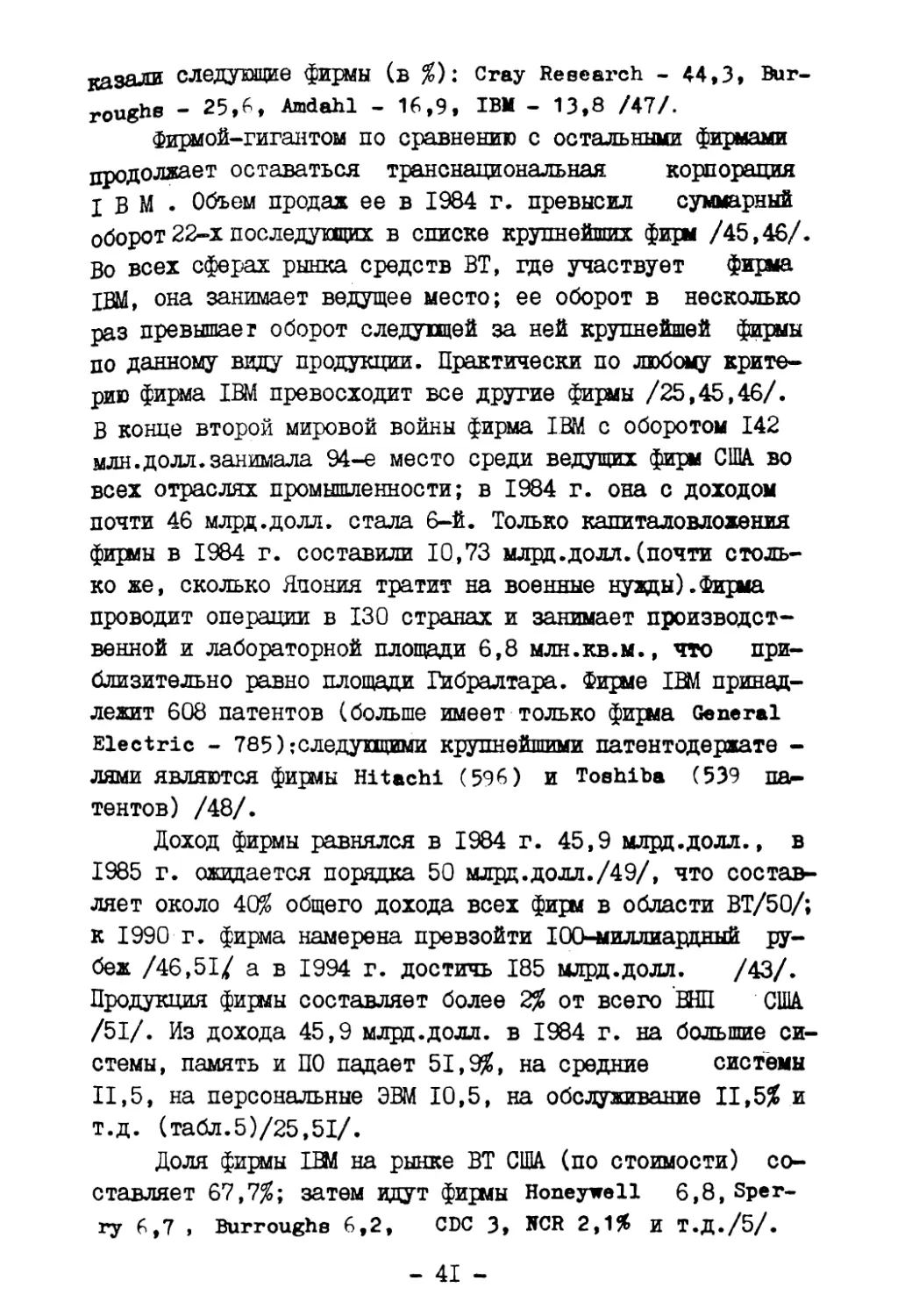

Фирмой-гигантом по сравнению с остальными фирмами

продолжает оставаться транснациональная корпорация

IBM. Объем продаж ее в 1984 г. превысил суммарный

оборот22-хпоследующих в списке крупнейших фирм /45,46/.

Во всех сферах рынка средств ВТ, цце участвует фирма

IBM, она занимает ведущее место; ее оборот в несколько

раз превышает оборот следующей за ней крупнейшей фирмы

по данному виду продукции. Практически по любому крите¬

рию фирма IBM превосходит все другие фирмы /25,45,46/.

В конце второй мировой войны фирма IBM с оборотом 142

млн.долл.занимала 94-е место среди ведущих фирм США. во

всех отраслях промышленности; в 1984 г. она с доходом

почти 46 млрд.долл, стала 6-й. Только капиталовложения

фирмы в 1984 г. составили 10,73 млрд.долл.(почти столь¬

ко же, сколько Япония тратит на военные нужды).Фирма

проводит операции в 130 странах и занимает производст¬

венной и лабораторной площади 6,8 млн.кв.м., что при¬

близительно равно площади Гибралтара. Фирме IBM принад¬

лежит 608 патентов (больше имеет только фирма General

Electric - 785):следующими крупнейшими патентодержате -

ЛЯМИ ЯВЛЯЮТСЯ фирмы Hitachi (596) и Toshiba (539 па<-

тентов) /48/.

Доход фирмы равнялся в 1984 г. 45,9 млрд.долл., в

1985 г. ожидается порядка 50 млрд.долл./49/, что состав¬

ляет около 40% общего дохода всех фирм в области ВТ/50/;

к 1990 г. фирма намерена превзойти 100-миллиардный ру¬

беж /46,51/ а в 1994 г. достичь 185 млрд.долл. /43/.

Продукция фирмы составляет более 2% от всего ВНП США

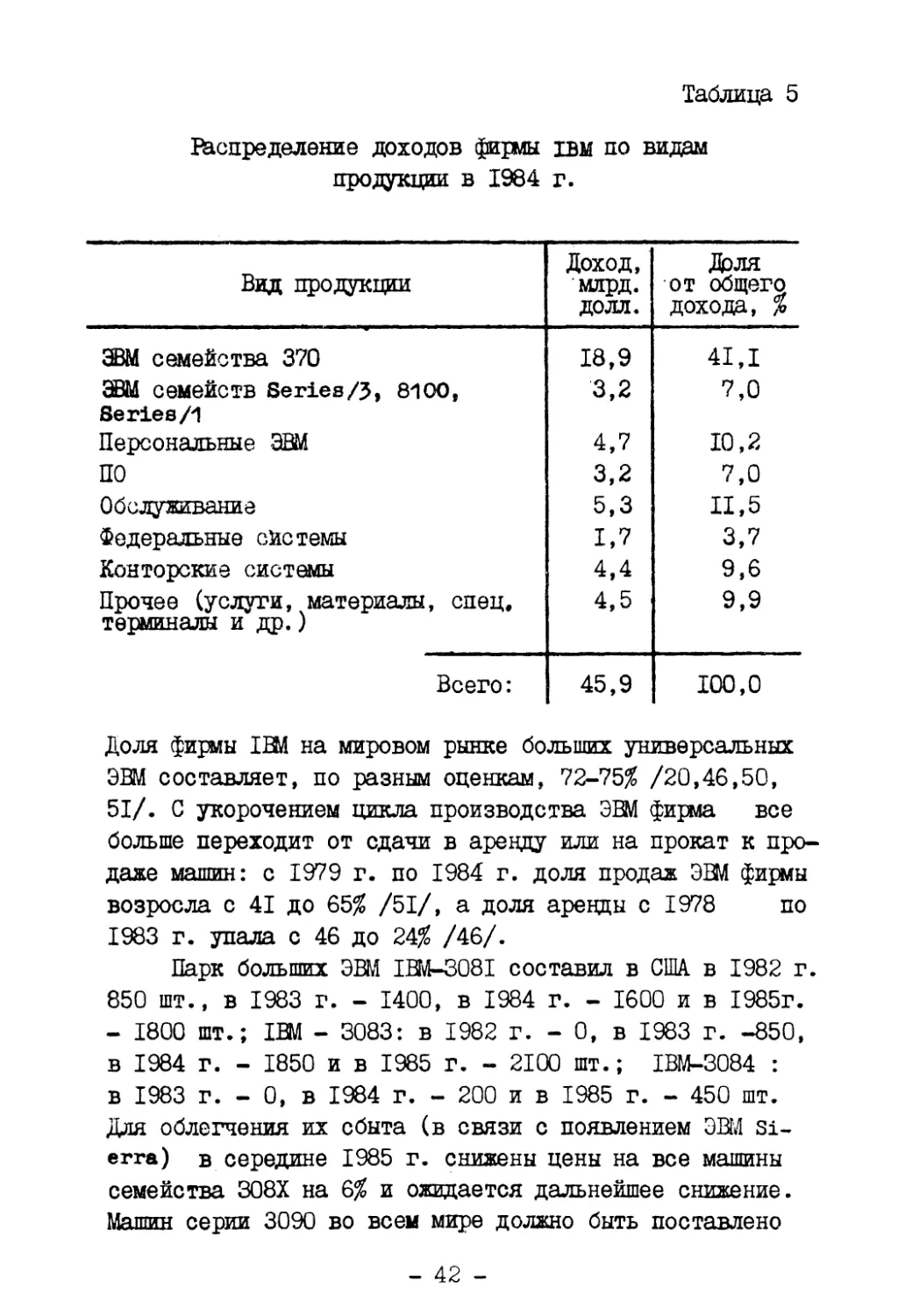

/51/. Из дохода 45,9 млрд.долл, в 1984 г. на большие си¬

стемы, память и ПО падает 51,9%, на средние системы

11,5, на персональные ЭВМ 10,5, на обслуживание 11,5% и

т.д. (табл.5)/25,51/.

Доля фирмы IBM на рынке ВТ США (по стоимости) со¬

ставляет 67,7%; затем идут фирмы Honeywell 6,8, Sper¬

ry 6,7 , Burroughs 6,2, CDC 3, HCR 2,1% и Т.Д./5/.

- 41 -

Таблица 5

^определение доходов фирмы ibm по видам

продукции в 1984 г.

Вид продукции

Доход,

млрд,

долл.

Доля

от общего

дохода, %

ЭВМ семейства 370

18,9

41,1

ЭВМ семейств Series/3, 8100,

Series/1

3,2

7,0

Персональные ЭВМ

4,7

10,2

ПО

3,2

7,0

Обслуживание

5,3

11,5

Федеральные системы

1,7

3,7

Конторские системы

4,4

9,6

Прочее (услуги, материалы, спец,

терминалы и др.)

4,5

9,9

Всего:

45,9

100,0

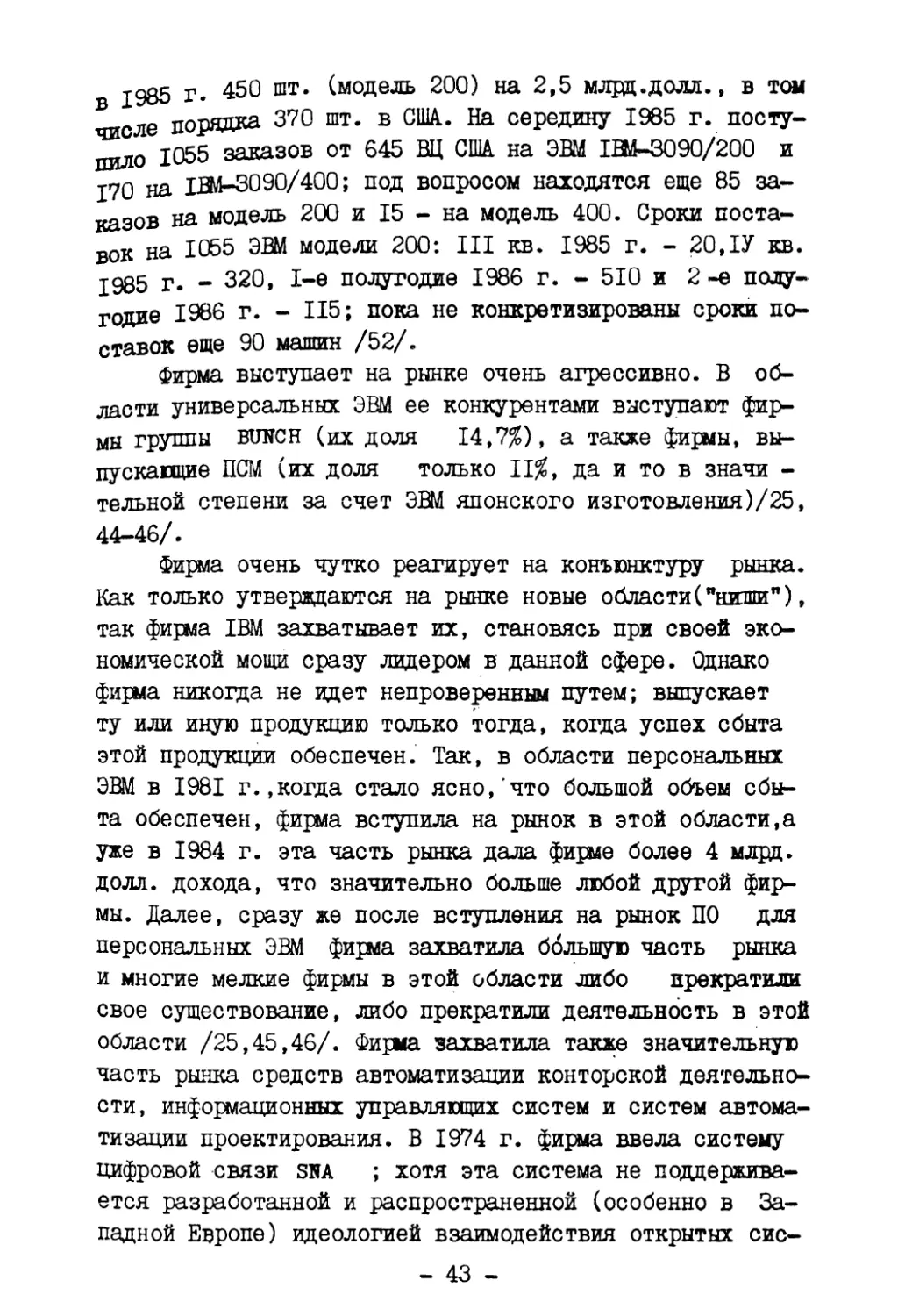

Доля фирмы IEM на мировом рынке больших универсальных

ЭВМ составляет, по разным оценкам, 72-75% /20,46,50,

51/. С укорочением цикла производства ЭВМ фирма все

больше переходит от сдачи в аренду или на прокат к про¬

даже машин: с 1979 г. по 1984 г. доля продаж ЭВМ фирмы

возросла с 41 до 65% /51/, а доля аренды с 1978 по

1983 г. упала с 46 до 24% /46/.

Парк больших ЭВМ IBM-308I составил в США в 1982 г.

850 шт., в 1983 г. - 1400, в 1984 г. - 1600 и в 1985г.

- 1800 шт.; IBM - 3083: в 1982 г. - 0, в 1983 г. -850,

в 1984 г. - 1850 и в 1985 г. - 2100 шт.; IBM-3084 :

в 1983 г. - 0, в 1984 г. - 200 и в 1985 г. - 450 шт.

Для облегчения их сбыта (в связи с появлением ЭВМ Si¬

erra) в середине 1985 г. снижены цены на все машины

семейства 308Х на 6% и ожидается дальнейшее снижение.

Машин серии 3090 во всем мире должно быть поставлено

- 42 -

1985 г. 450 шт. (модель 200) на 2,5 млрд.долл., в том

числе порядка 370 шт. в США. На середину 1985 г. посту¬

пило 1055 заказов от 645 ВЦ США на ЭВМ IEM-3090/200 и

170 на IBM-3090/400; под вопросом находятся еще 85 за¬

казов на модель 200 и 15 - на модель 400. Сроки поста¬

вок на 1055 ЭВМ модели 200: III кв. 1985 г. - 20,1У кв.

1985 г. - 320, 1-е полугодие 1986 г. - 510 и 2-е полу¬

годие 1986 г. - 115; пока не конкретизированы сроки по¬

ставок еще 90 машин /52/.

Фирма выступает на рынке очень агрессивно. В об¬

ласти универсальных ЭВМ ее конкурентами выступают фир¬

мы группы bunch (их доля 14,7%), а также фирмы, вы¬

пускающие ПСМ (их доля только 11%, да и то в значи -

тельной степени за счет ЭВМ японского изготовления)/25,

44-46/.

Фирма очень чутко реагирует на конъюнктуру рынка.

Как только утверждаются на рынке новые области("ниши"),

так фирма IBM захватывает их, становясь при своей эко¬

номической мощи сразу лидером в данной сфере. Однако

фирма никогда не идет непроверенным путем; выпускает

ту или иную продукцию только тогда, когда успех сбыта

этой продукции обеспечен. Так, в области персональных

ЭВМ в 1981 г..когда стало ясно, что большой объем сбы¬

та обеспечен, фирма вступила на рынок в этой области,а