Author: Нарышкин А.К.

Tags: электротехника учебники и учебные пособия по радиотехнике электроника радиотехнический журнал цифровые устройства

ISBN: 5-7695-1618-6

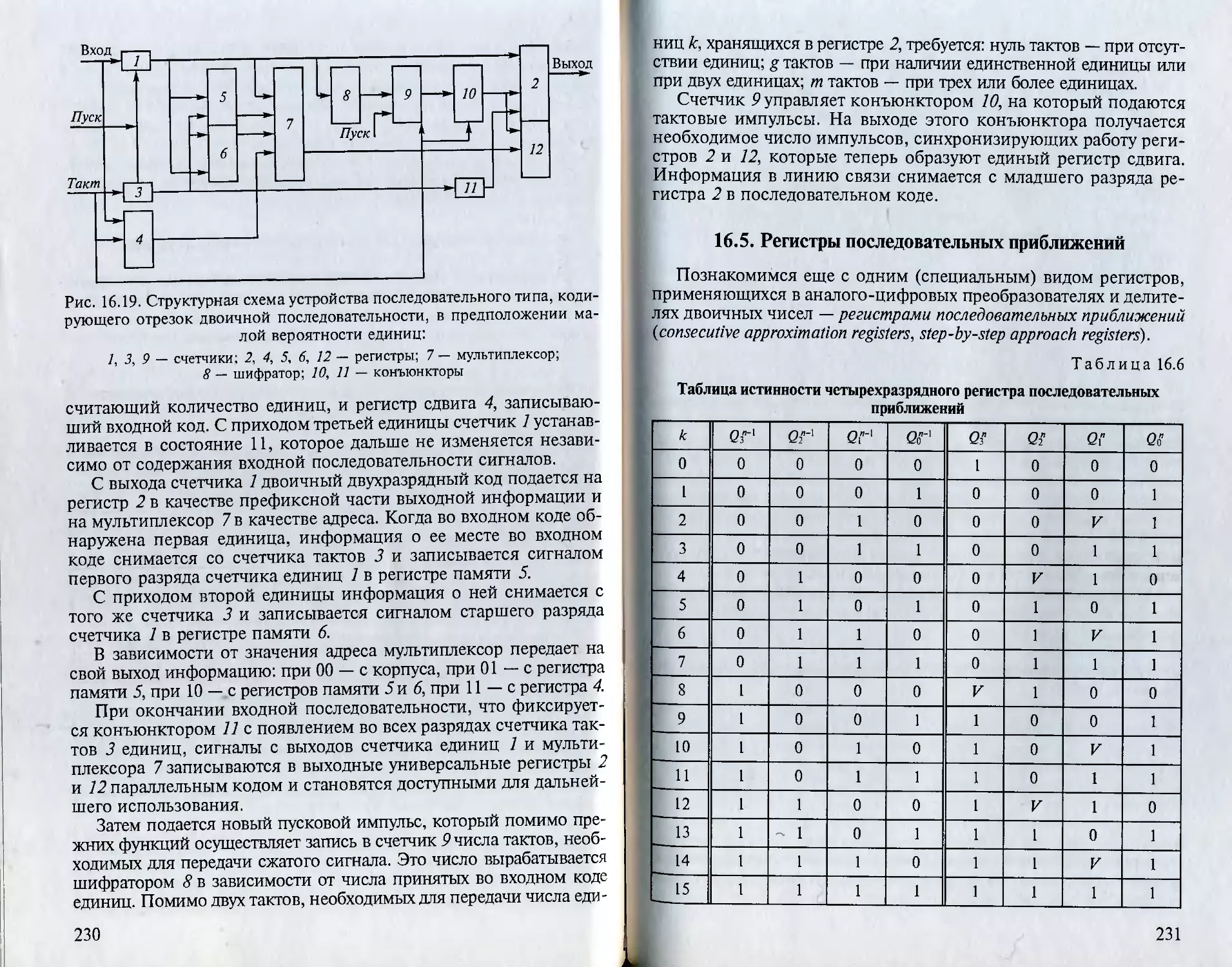

Year: 2006

Text

УДК 621.377.6 (075.8)

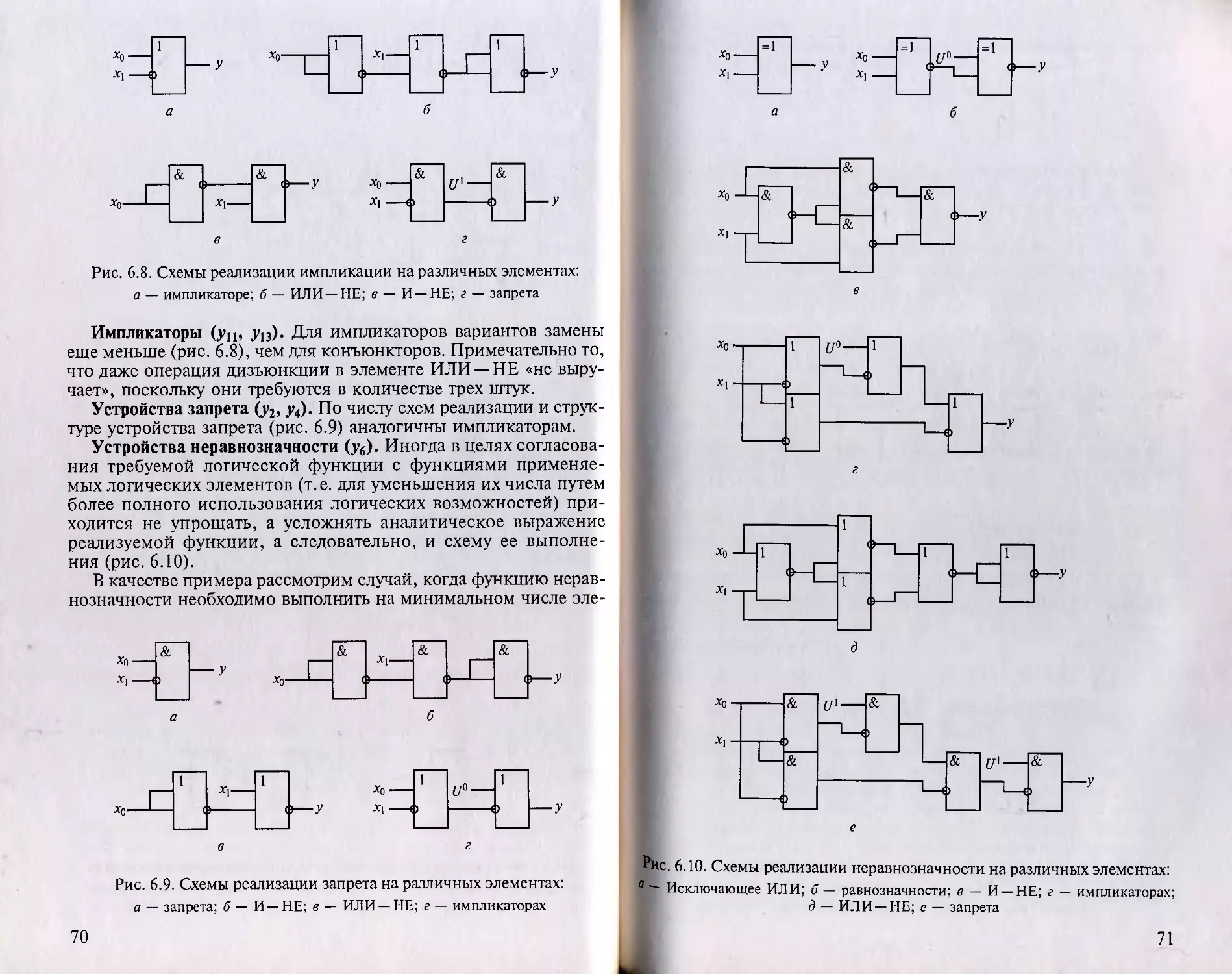

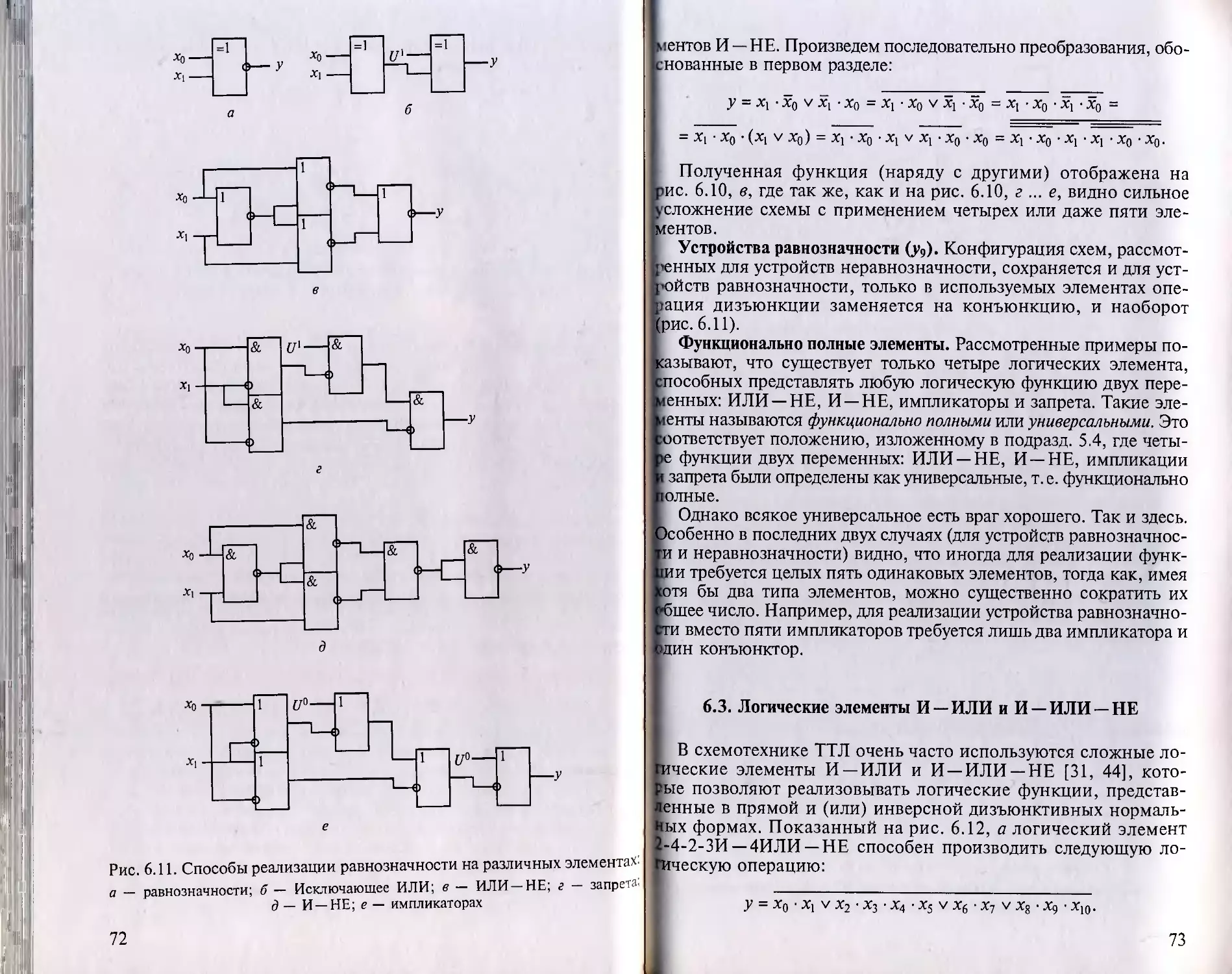

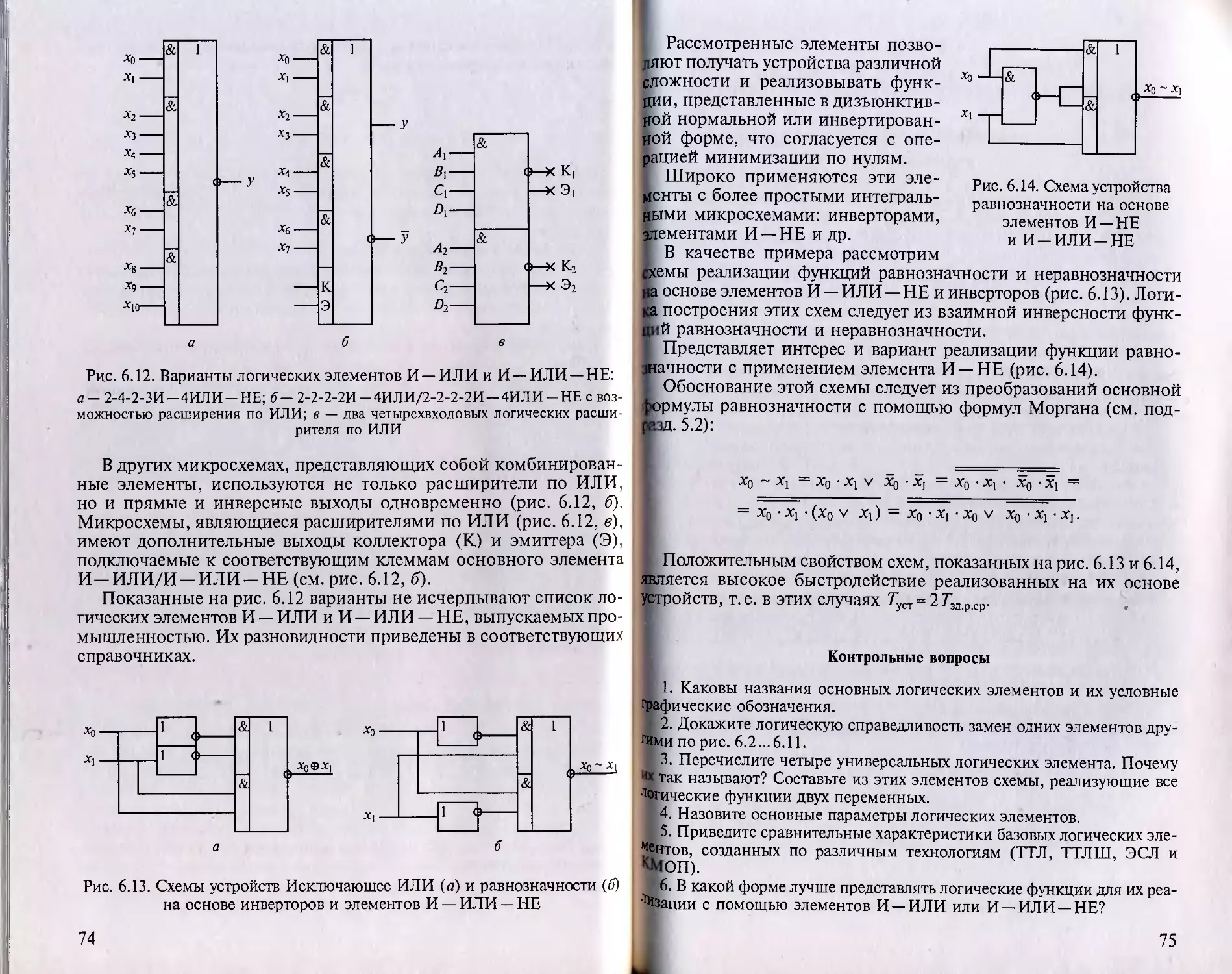

ББК 32.84я73

Н308

Рецензенты:

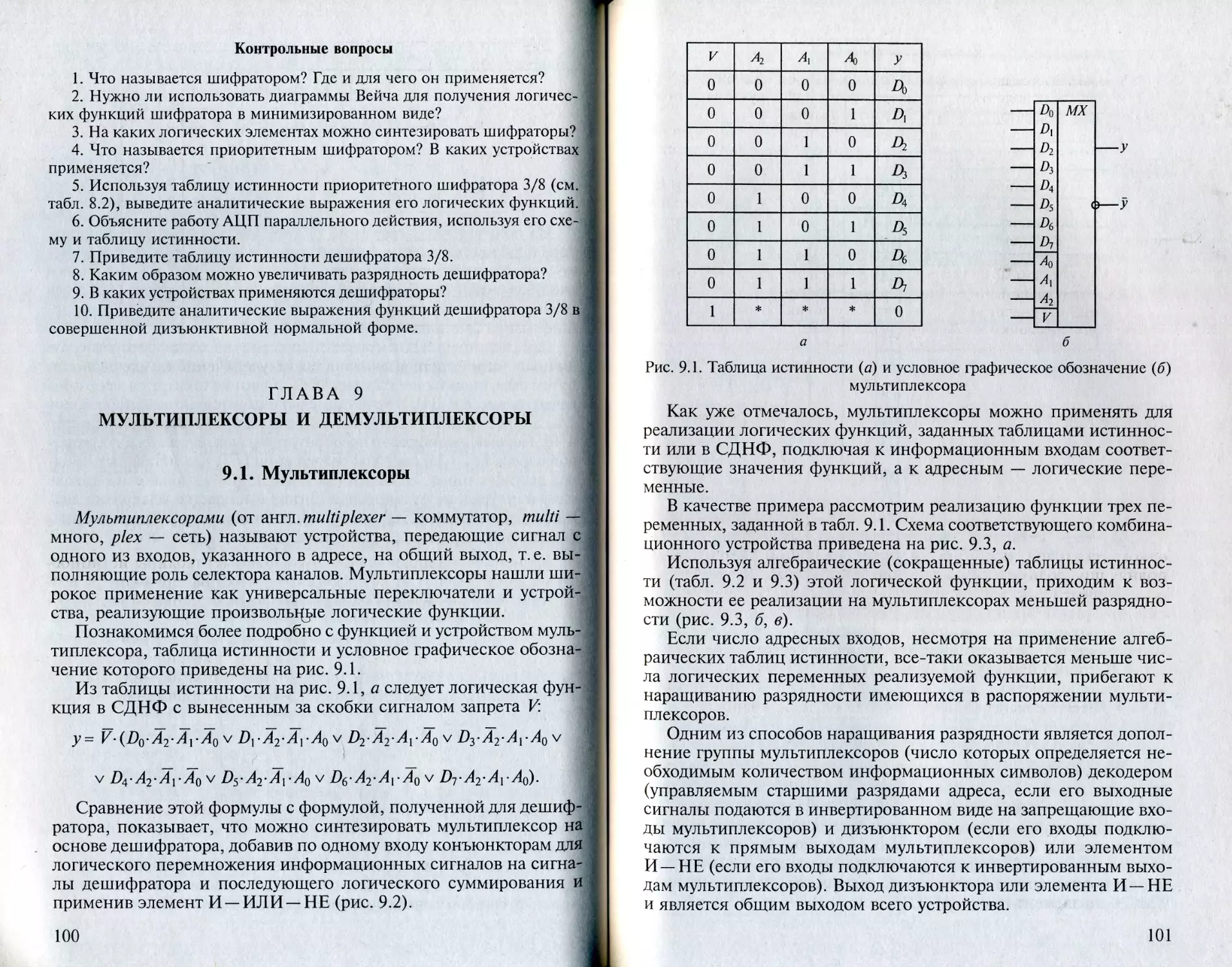

зам. директора ФГУП НИКФИ, зав. лабораторией электроакустики НИКФИ,

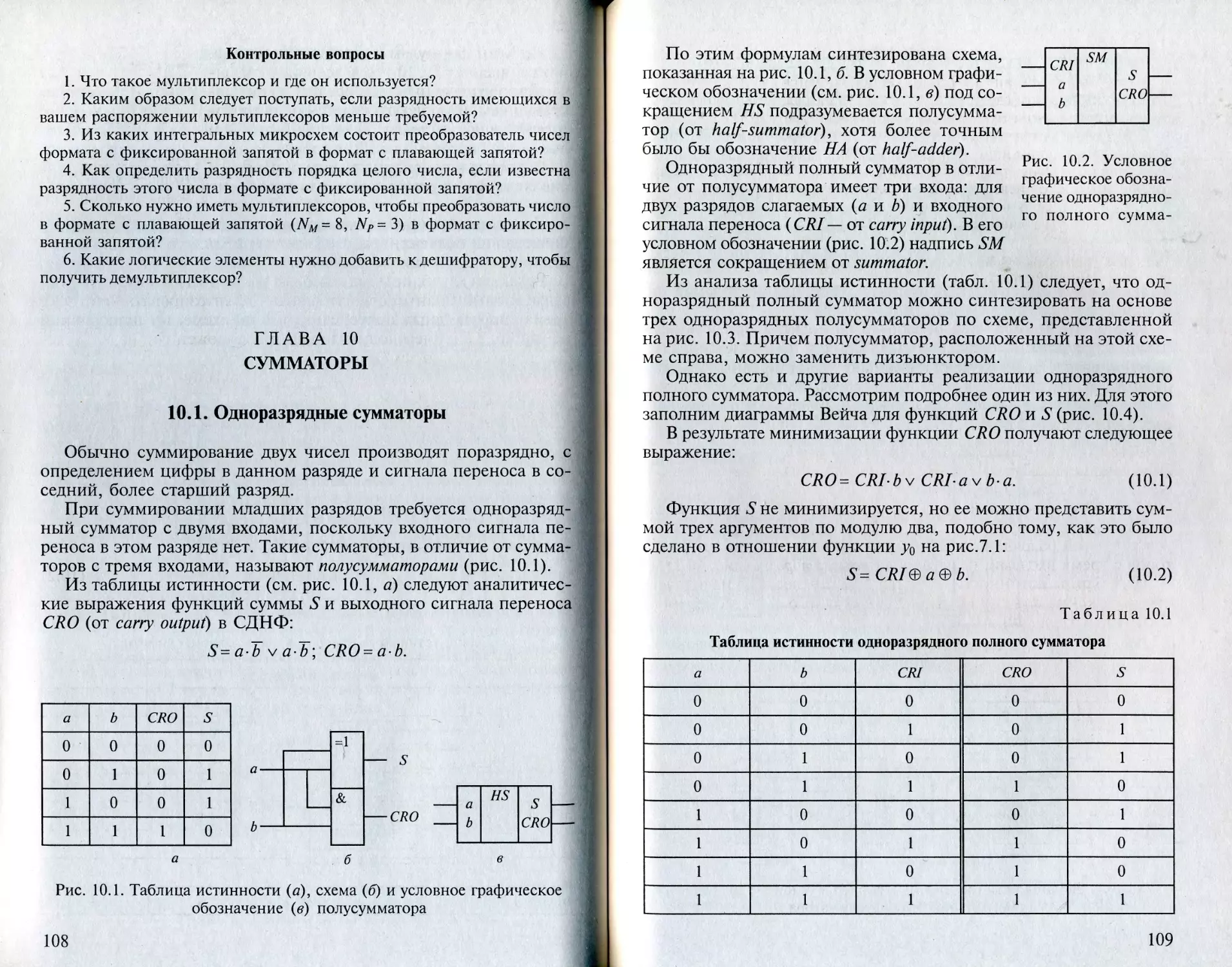

канд. техн, наук К. В. Неверовский',

зав. лабораторией цифровых методов обработки сигналов

НИКФИ Ю. Н. Барышненков',

доцент кафедры конструирования и производства

РЭС МГИРЭА, канд. техн, наук А. Н. Богаченков

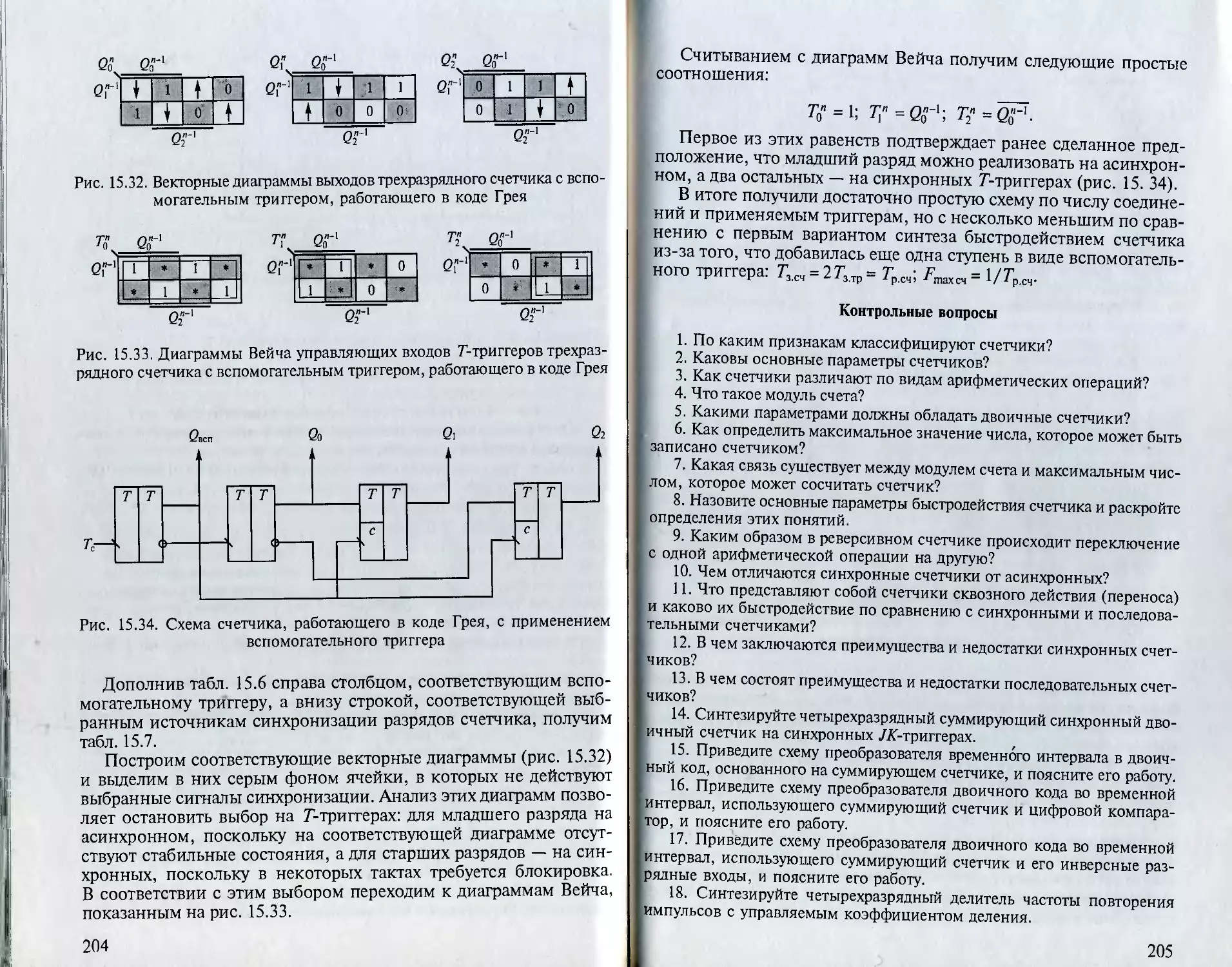

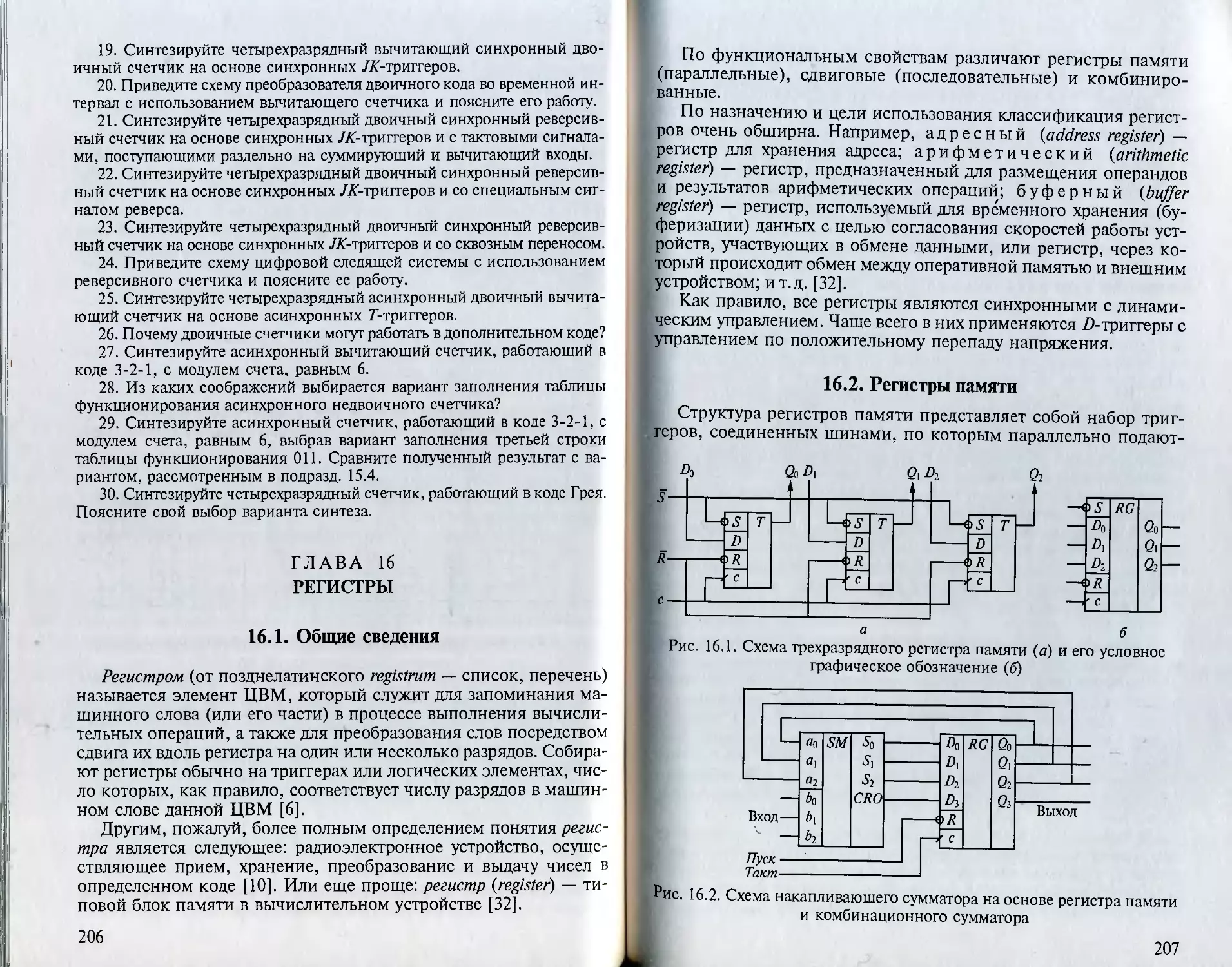

Нарышкин Л.К.

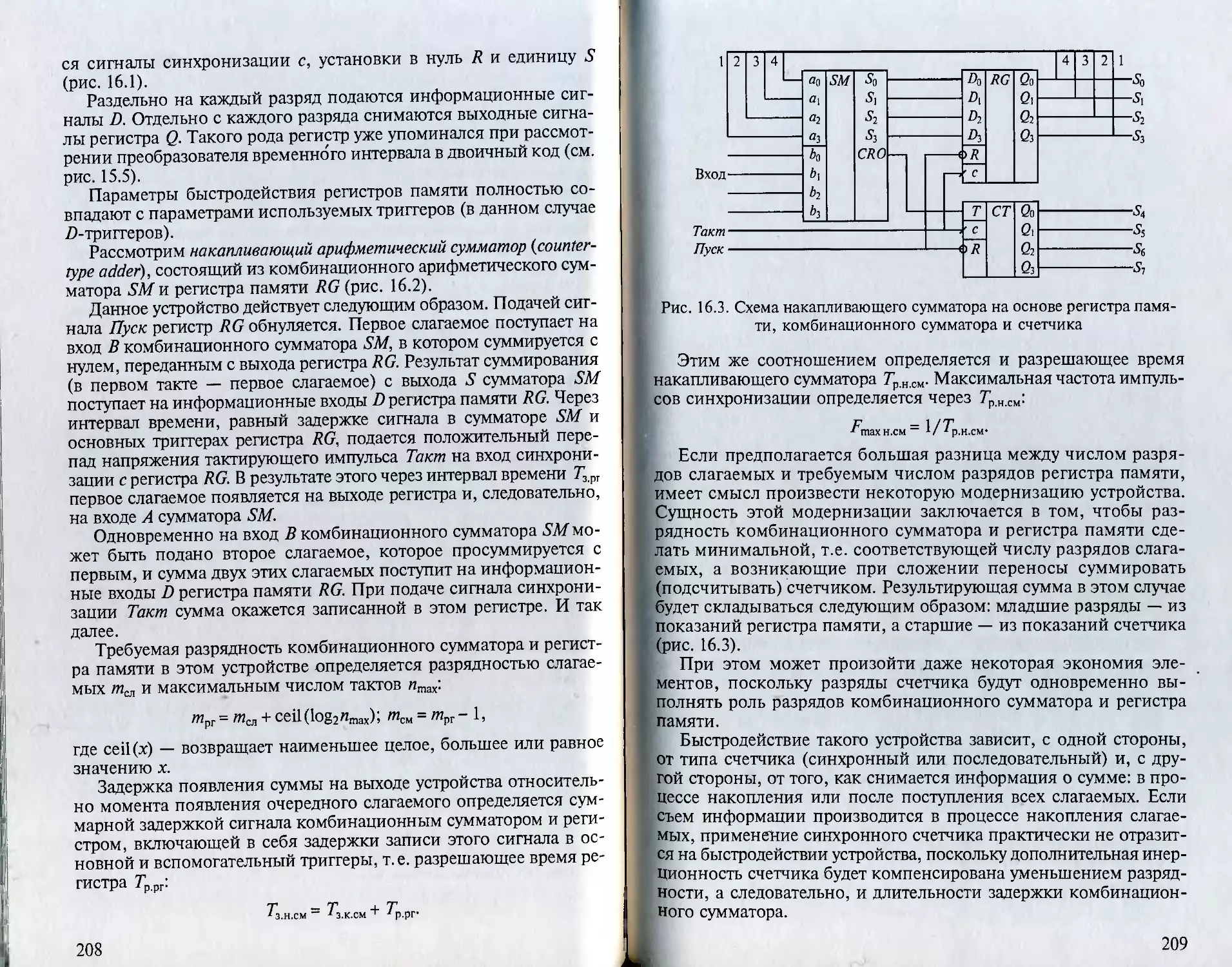

Н308 Цифровые устройства и микропроцессоры: Учеб, пособие

для студ. высш. учеб, заведений / Александр Кириллович На-

рышкин. — М.: Издательский центр «Академия», 2006. — 320 с.

ISBN 5-7695-1618-6

Рассматриваются основы алгебры логики, теории переключательных

функций, теории асинхронных потенциальных и синхронных автоматов,

синтез цифровых узлов (триггеров, счетчиков, сдвигающих регистров,

мультиплексоров, демультиплексоров, сумматоров), применение 'интег-

ральных схем для проектирования цифровых устройств, а также архитек-

тура, система команд, шинные приемопередатчики, проектирование

микроконтроллеров на микропроцессорах, разработка программного обес-

печения. Наряду с известными приводятся разработанные автором в пос-

ледние годы новые методики анализа и синтеза цифровых устройств.

Для студентов вузов радиотехнических специальностей. Может быть по-

лезно студентам техникумов радиотехнического профиля.

УДК 621.377.6(075.8)

ББК 32.84я73

Оригинал-макет данного издания является собственностью

Издательского центра «Академия», и его воспроизведение любым способом

без согласия правообладателя запрещается

© Нарышкин А. К., 2006

ISBN 5-7695-1618-6 © Издательский центр «Ака темня». 2006

СПИСОК СОКРАЩЕНИЙ

А — аккумулятор

АЛУ — арифметико-логическое устройство

АЦП — аналого-цифровой преобразователь

БИС — большая интегральная схема

БМК — базовый матричный кристалл

БР — буферный регистр

БРА — буферный регистр адреса

БРД — буферный регистр данных

ГПМС — глобальная программируемая матрица соединений

ГТИ — генератор тактовых импульсов

ДБЯ — дизъюнктивная бистабильная ячейка

ДНФ — дизъюнктивная нормальная форма

дшк — дешифратор команд

ЗУ — запоминающее устройство

ЗЭ — запоминающий элемент

имс — интегральная микросхема

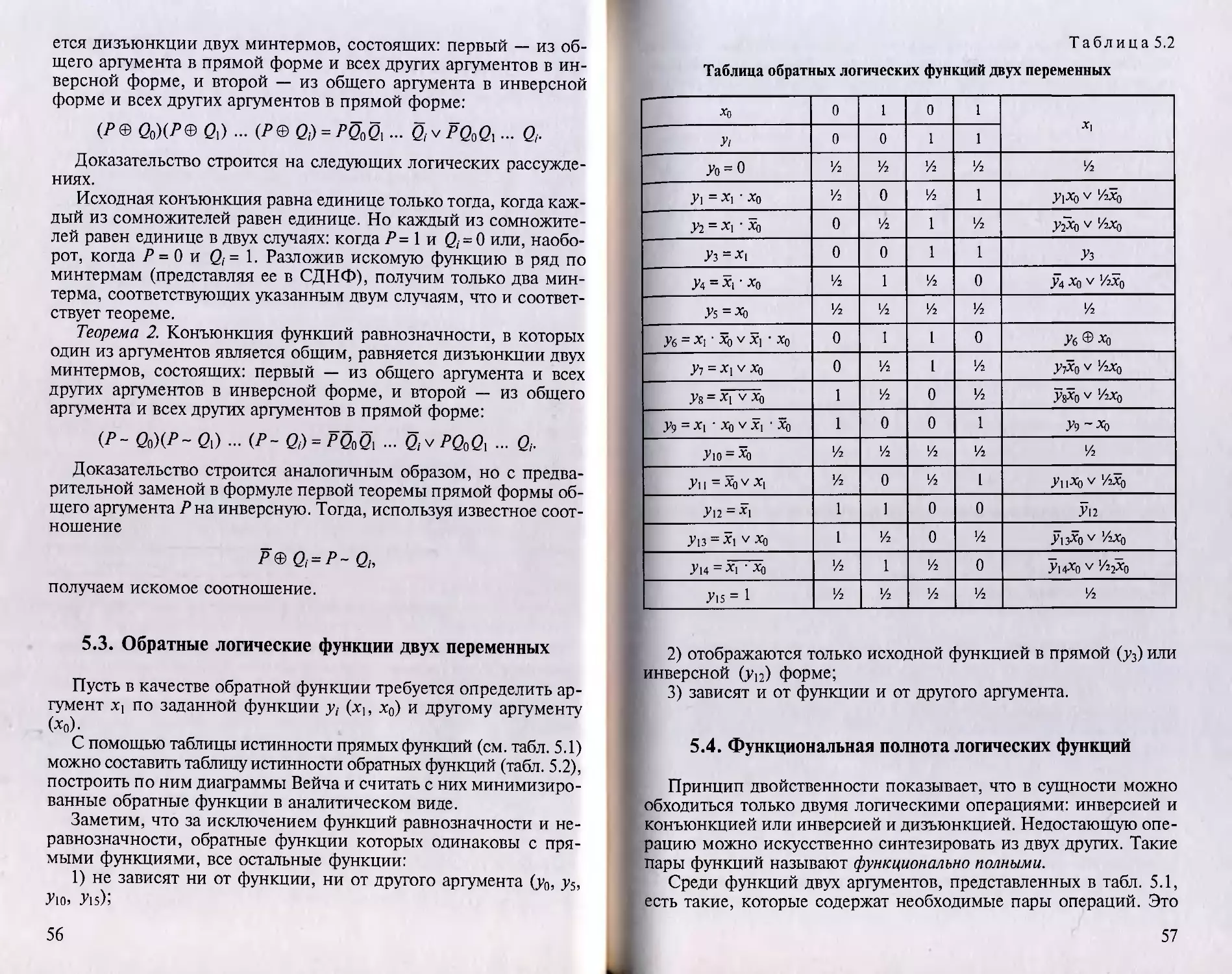

ИС — интегральная схема

КБЯ — конъюнктивная бистабильная ячейка

КМОП — комплементарный МОП-элемент

кои — код операции индикатора

КЦУ — комбинационное цифровое устройство

ЛБ — логический блок

липз — лавинно-инжекционный с плавающим затвором

лэ — логический элемент

МА — магистраль адреса

МБА — младший байт адреса

МБР — многорежимный буферный регистр

МД — магистраль данных

мк — микроконтроллер

МЛБ — матричный логический блок

мноп — металл —нитрид кремния—оксид кремния—полупроводник

МОП — металл — оксид—полупроводник

МП — микропроцессор

мпк — микропроцессорный комплект

МУ — магистраль управления

ндк — натуральный двоичный код

НМД — контроллер на жестком магнитном диске

ОЗУ — оперативное запоминающее устройство

3

ОУ — операционный усилитель

ПВМ — программируемая вентильная матрица

ПЗУ — постоянное запоминающее устройство

ПКМБ — программируемый коммутируемый матричный блок

ПЛИС — программируемая логическая интегральная схема

ЦЛМ — программируемая логическая матрица

ПМЛ — программируемая матричная логика, программируемая макро-

логика

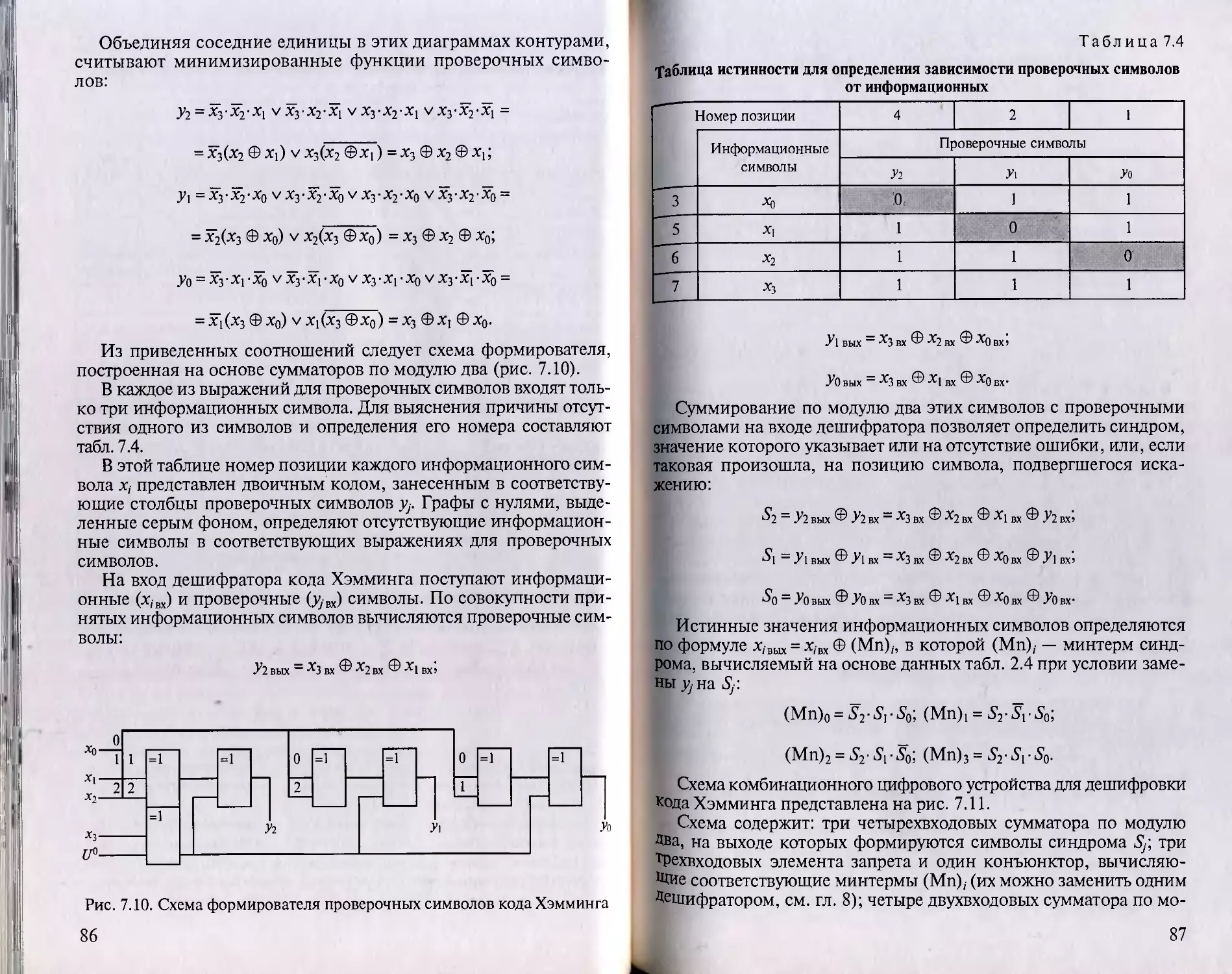

ППЗУ — программируемое постоянное запоминающее устройство

ПЦУ — последовательностное цифровое устройство

РА — регистр адреса

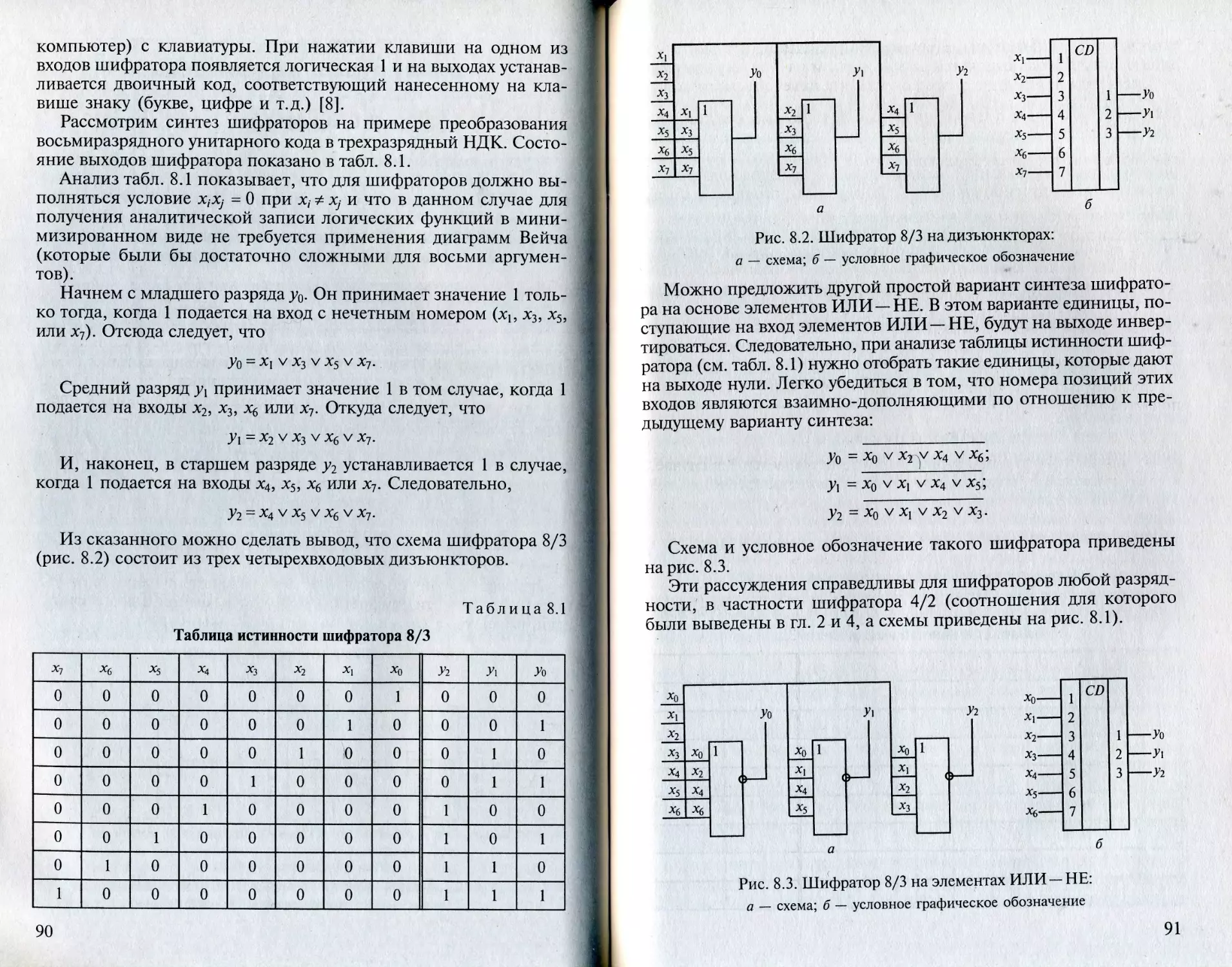

РК — регистр команд

РМП — реконфигурируемый модуль памяти

РОН — регистр общего назначения

РП — регистр признаков

РПЗУ — репрограммируемое постоянное запоминающее устройство

САПР — система автоматизированного проектирования

СБА — старший байт адреса

СДНФ — совершенная дизъюнктивная нормальная форма

СИС — средняя интегральная схема

СКНФ — совершенная конъюнктивная нормальная форма

СУП — секция ускоренного переноса

ТП — таблица перекодировки

ТТЛ — транзисторно-транзисторная логика

ТТЛШ — ТТЛ с диодами Шоттки

УВВ — устройство ввода-вывода

УВХ — устройство выборки и хранения

УГО — условное графическое обозначение

УУ — устройство управления

ФСУ — формирователь сигналов управления

ЦАП — цифроаналоговый преобразователь

ЦВМ — цифровая вычислительная машина

ЦОС — цифровая обработка сигнала

ЦПЭ — центральный процессорный элемент

ЦУ — цифровое устройство

ШД — шинный драйвер

ШФ — шинный формирователь

ЭПЛ — логика на эмиттерных повторителях

ЭППЗУ — электрически программируемое постоянное запоминающее

устройство

ЭСЛ — эмиттерно-связанная логика

ЭФЛ — эмиттерно-функциональная логика

СПИСОК УСЛОВНЫХ ОБОЗНАЧЕНИЙ

— — NOT, НЕ — операция логического отрицания (инверсия)

fc, •, а — AND, И — операция логического умножения (конъюнкция)

© — операция суммирования по модулю 2, неравнозначность

--- равнозначность

А — операция запрета

X — стрелка Пирса

Z) — импликация

I — штрих Шеффера

*, !6 — неопределенность, факультатив, запрещенное состояние

/ — логическое деление

\ — логическое вычитание

= = — компаратор

=1 — элемент неравнозначности, сумматор по модулю 2

1, v — OR, ИЛИ — операция логического сложения (дизъюнкция)

А — address — адрес; accumulator — аккумулятор

АВ — address bus — адресная шина

А С — analog comparator — аналоговый компаратор

A/D — analog-digital — аналого-цифровой

ALU — arithmetic and logic unit — арифметико-логическое устройство

В — binary — бинарный; двоичный; bit — бит, двоичный разряд

BUBR — bidirectional unibus buffer register — двунаправленный буфер-

ный регистр общей шины

С, CLK — clock — сигнал синхронизации

CARG — consecutive approximation register — регистр последовательных

приближений

c.d. — count down — считать в обратном направлении

"\см. — count up — считать в прямом направлении

' CD — coder — шифратор

CLR — clear — очищать

CRG — carry of group — сигнал группового переноса

CRI — carry input — входной сигнал переноса

CRO — carry out put — выходной сигнал переноса

CRP — carry prompting — разрешение группового переноса

CS — chip select — выбор микросхемы

СТ — counter — счетчик

CY — carry — перенос; сигнал переноса

D — data — информационные данные; delay — задержка, запазды-

вание; decimal — десятичный

5

DA — differential amplifier — дифференциальный усилитель

D/А — digital-analog — цифроаналоговый

DB — data bus — шина данных, информационная шина

DC — decoder — дешифратор

DD — digital device — цифровой элемент

DM — demultiplexer — демультиплексор

DVD — dividend — делимое

DVS — divisor — делитель

E, EN — enable — разрешающий сигнал, разрешение; разрешающий

вход

F — function — функция

FR — flag register — флаговый регистр; регистр признака

G — carry generator — генератор сигнала переноса; generator — гене-

ратор

GRD — ground — общая шина, земля

GS — gate signal — строб-сигнал стробирующий сигнал

Н — high — высокий; hexadecimal — шестнадцатеричный

НА — half-adder — полусумматор

HS — hat, -summator — полусумматор

I — input — вход

IB — input bus — входная шина

INT — interrupt — прерывание

I/OR — input/output read — считывание из устройства ввода/вывода

I/OW — input/output write — запись в устройство ввода/вывода

L — low — низки! t

/ — line — строка

MBR — multiregime buffer register — многорежимный буферный регистр

MD — mode — режим работы

MEMR — memory read — считывание из памяти

MEMW — memory write — запись в память

MPL — multiplier— множитель; сомножитель; умножитель

MX — multiplexer — мультиплексор; коммутатор

О — output — выход; вывод; выходное устройство; устройство вы-

вода

OB — output bus — выходная шина

OF — overflow — переполнение; признак переполнения

Р —propagation — распространение; product— произведение двух чи-

сел

PAL — programmable array logic — программируемая матричная логика

PC — program counter — программный счетчик, счетчик клманд; parity

of carry — контроль четности переноса

PCD — priority-oriented coder — приоритетный шифратор

PLA — programmable logic array — программируемая логическая матрица

PLD — programmable logic device — программируемое логическое уст-

ройство

PR — parity of result — контроль четности переноса

PROM — programmable read-only memory — программируемая постоян-

ная память, программируемое постоянное ЗУ

Q — quotien — частное; отношение

6

R — reset — восстанавление, возврат в исходное положение; уста-

новка в «О»; reverse — реверс, обратный ход; receiver — при-

емник

RG — register — регистр

5 — set — устанавливать; sign — знак; sum — сумма; switch — пере-

ключатель

SIB — scale index byte — байт масштабируемого индекса

SM — summator — сумматор, суммирующее устройство

SP — stack pointer — указатель стека

STB — strobe — строб-импульс, стробирующий импульс

Т — trigger — триггер; пусковая схема; transmitter — передатчик;

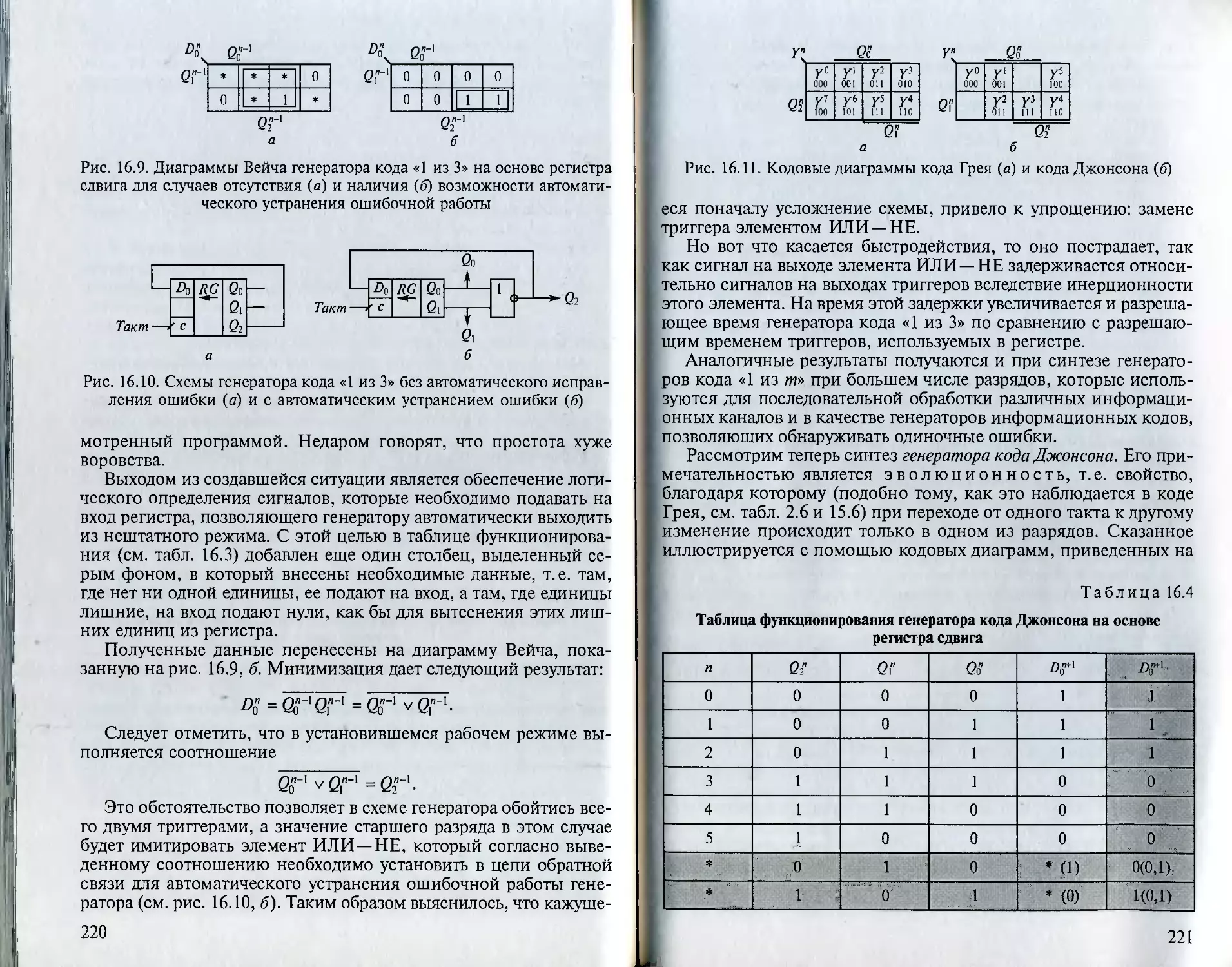

topple — опрокидываться; time — время

V — veto — запрет

W — write — запись

Z — zero — нуль

ZD — zero definition — задание нуля; zero drift — шумоподавитель

ПРЕДИСЛОВИЕ

Учебное пособие является обобщением многолетнего научно-

методического и практического опыта автора.

Помимо известных методик автор использует разработанные

им новые методики анализа и синтеза цифровых устройств. В каче-

стве примеров приводятся функции, имеющие практическое зна-

чение.

В первом разделе предлагаемого учебного пособия приведены

все основные положения современной алгебры логики.

В первой главе приведены основные обозначения и постулаты

бинарной (аристотелевой) алгебры логики.

Во второй главе рассмотрены основные логические функции и

их свойства.

В третьей главе обсуждаются алгоритмы программ, позволяю-

щих минимизировать логические функции с помощью компью-

терной техники.

В четвертой главе представлено применение арифметических и

алгебраических диаграмм.

В пятой главе исследованы все функции двух переменных, их

свойства и взаимосвязь.

Второй раздел посвящен комбинационным цифровым устрой-

ствам, которые отличаются от последовательностных тем, что у

них нет памяти по предыдущему состоянию. Комбинационные циф-

ровые устройства (КЦУ) реализуют заданные математические и

логические операции над действующими в данный момент вре-

мени комбинациями входных информационных сигналов в соот-

ветствии с поданными управляющими сигналами и не зависят от

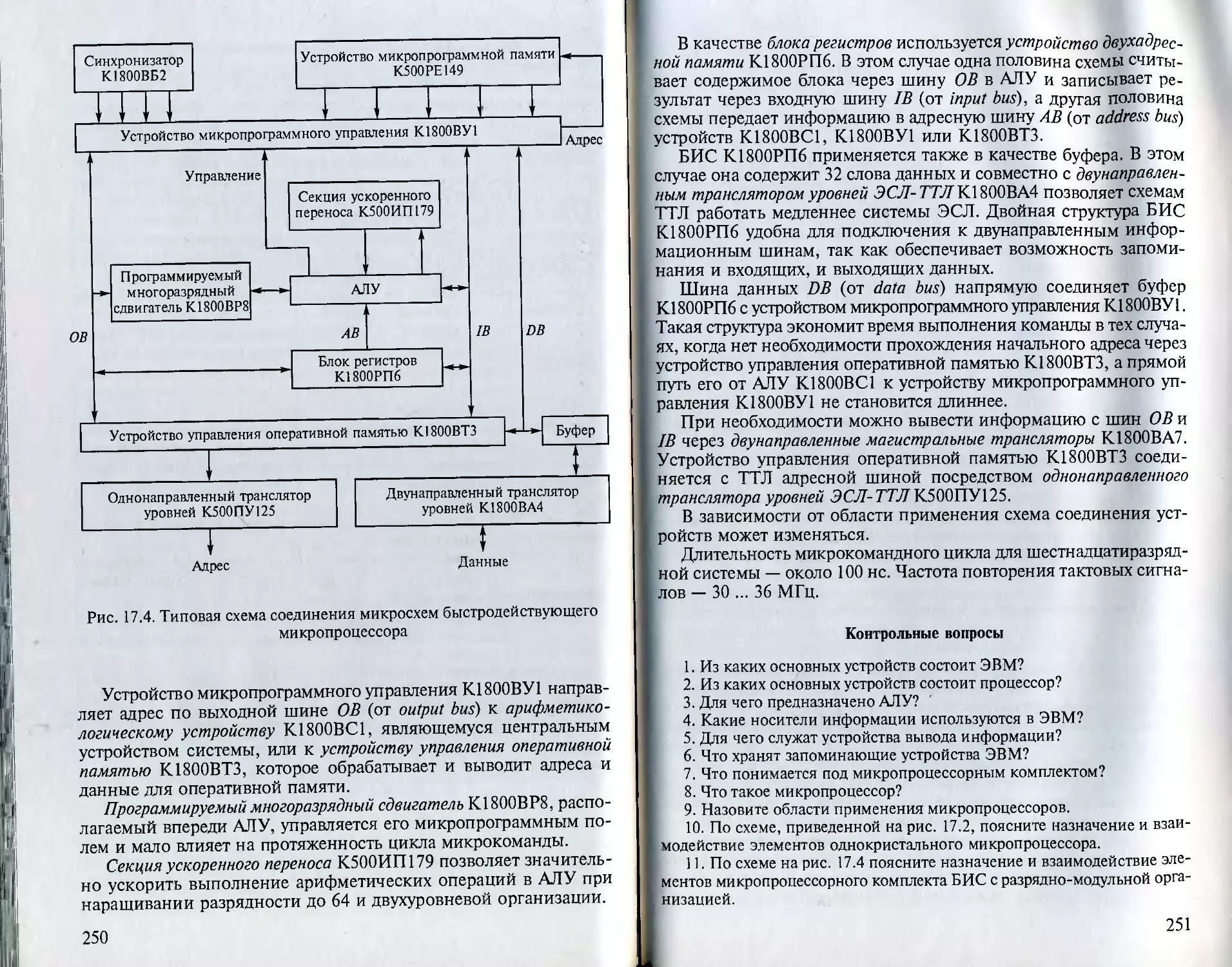

предыдущих сигналов. Методы синтеза цифровых устройств осно-

ваны на использовании положений алгебры логики, изложенных

в первом разделе пособия.

В шестой главе рассматриваются основные логические элемен-

ты, с помощью которых синтезируются КЦУ. Здесь приводятся

только самые общие параметры логических элементов без их схем-

ных подробностей. Также в этой главе демонстрируется возмож-

ность взаимной замены логических элементов, приводятся при-

меры функционально полных логических элементов, упоминают-

ся элементы И—ИЛИ и И—ИЛИ—НЕ.

8

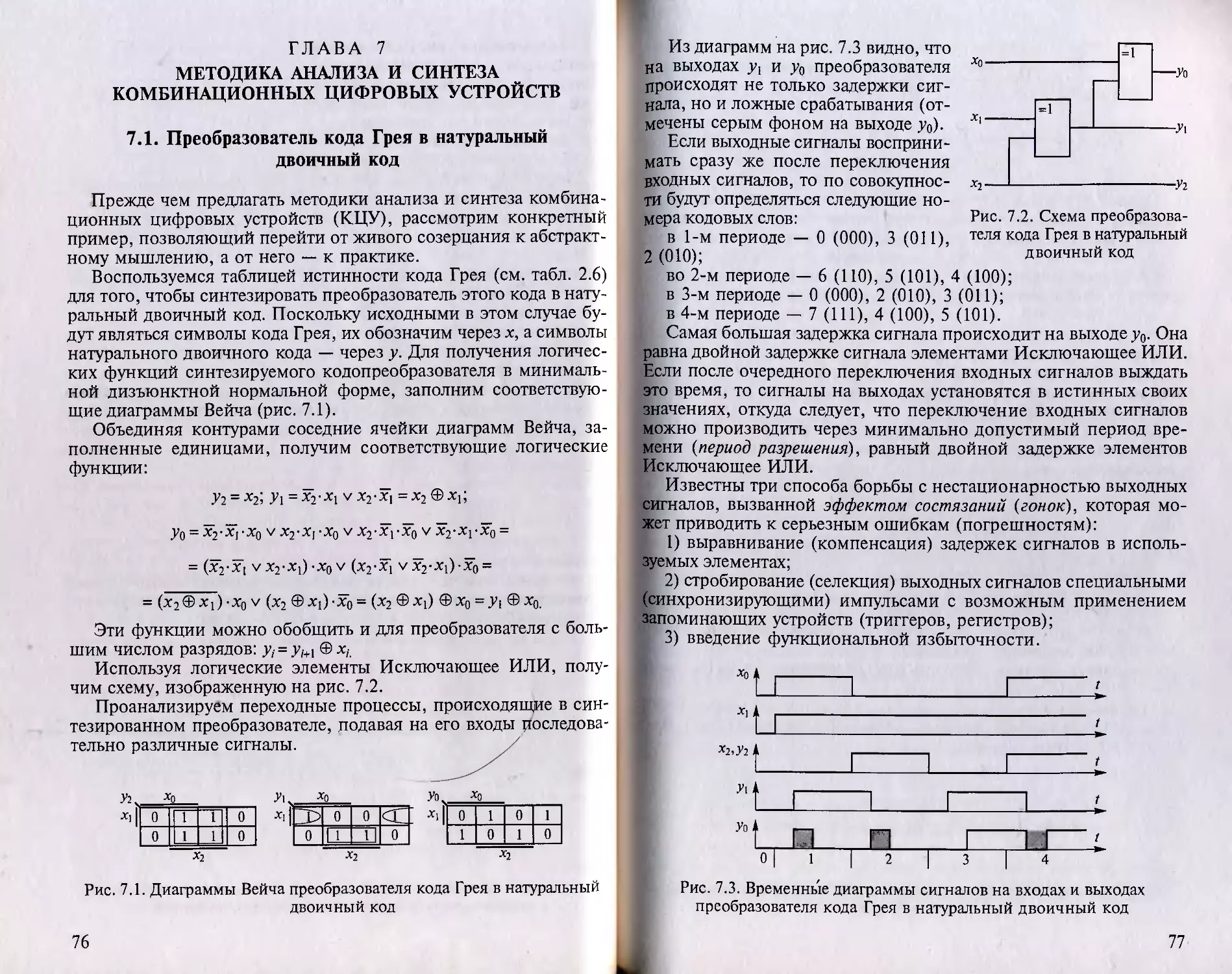

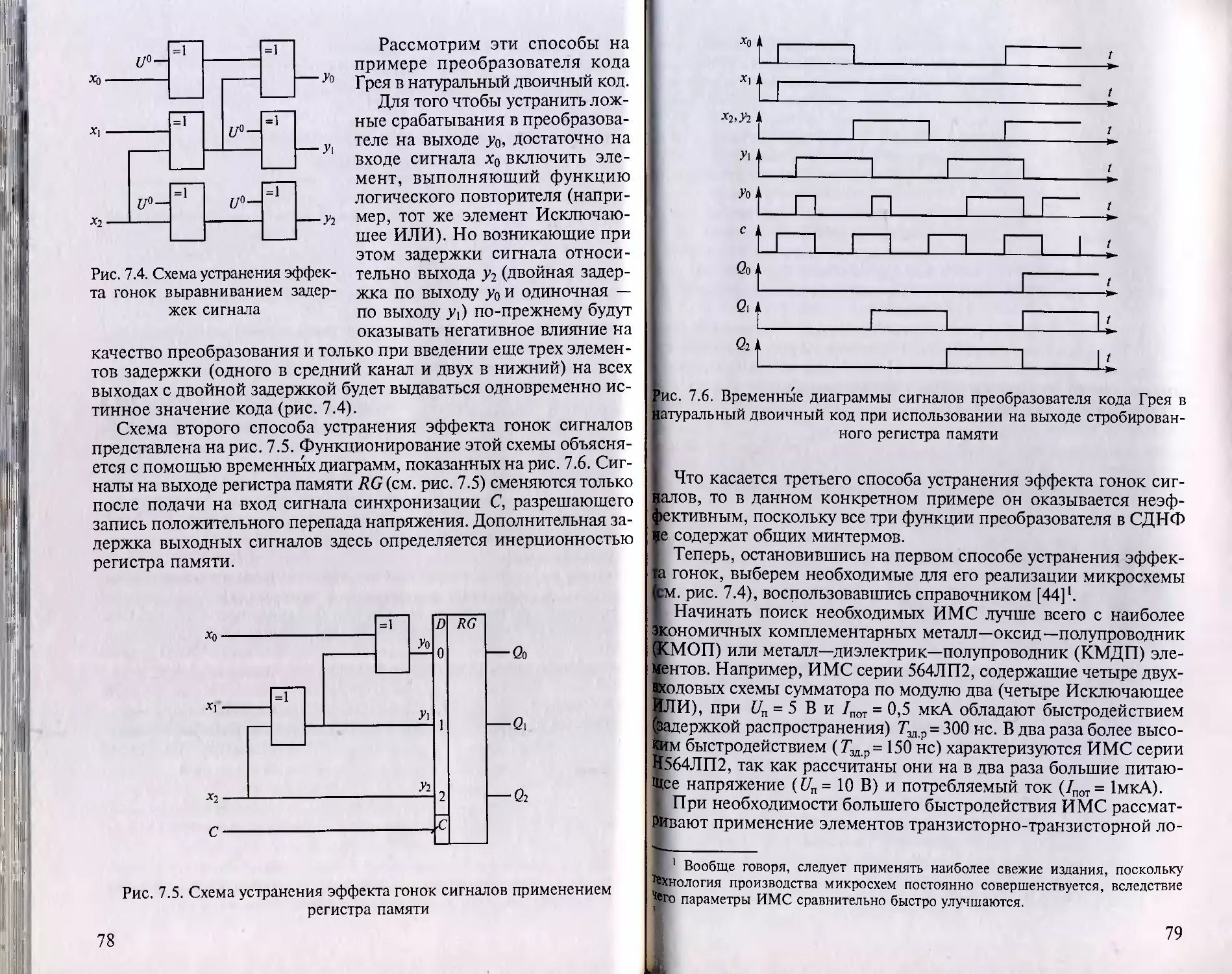

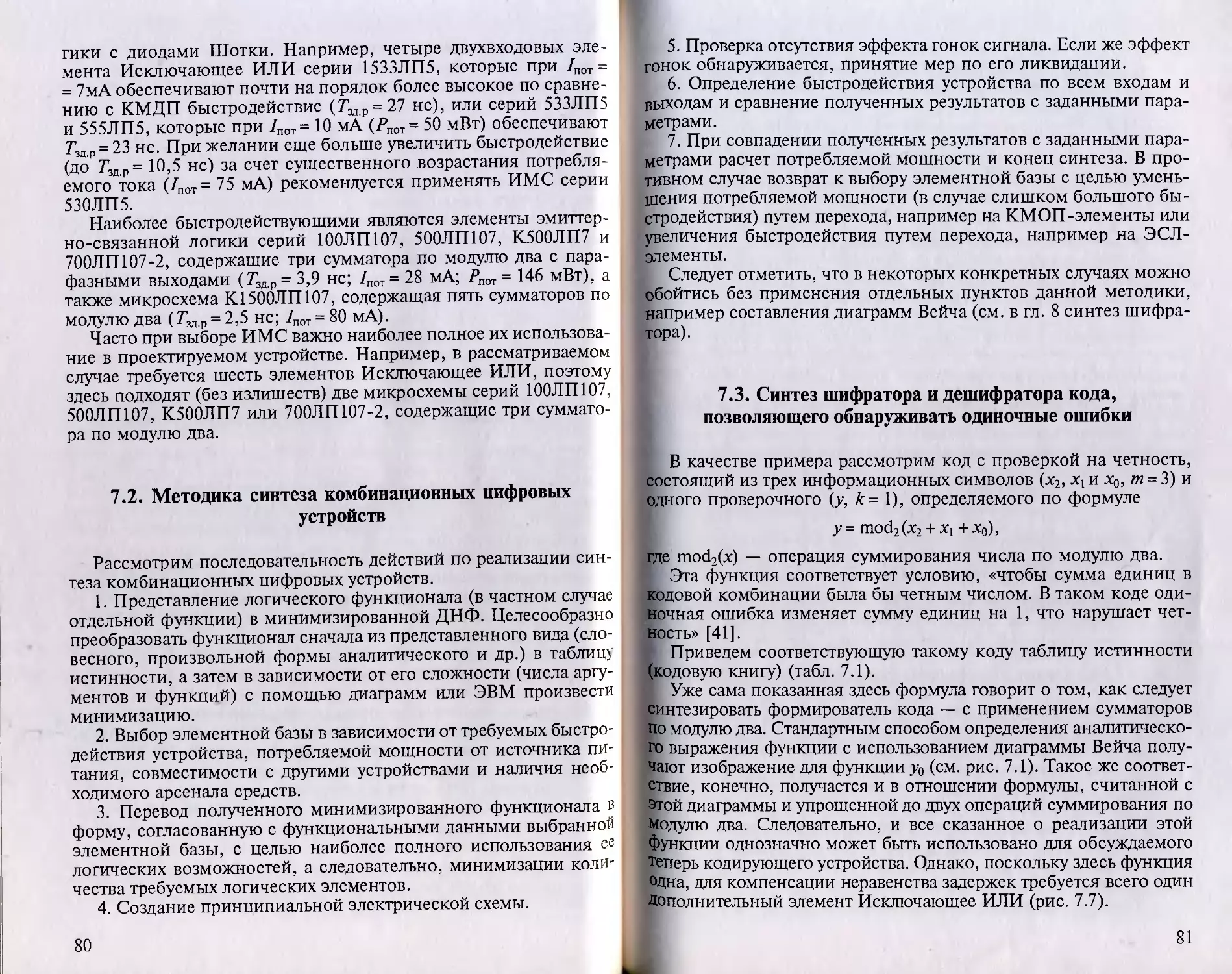

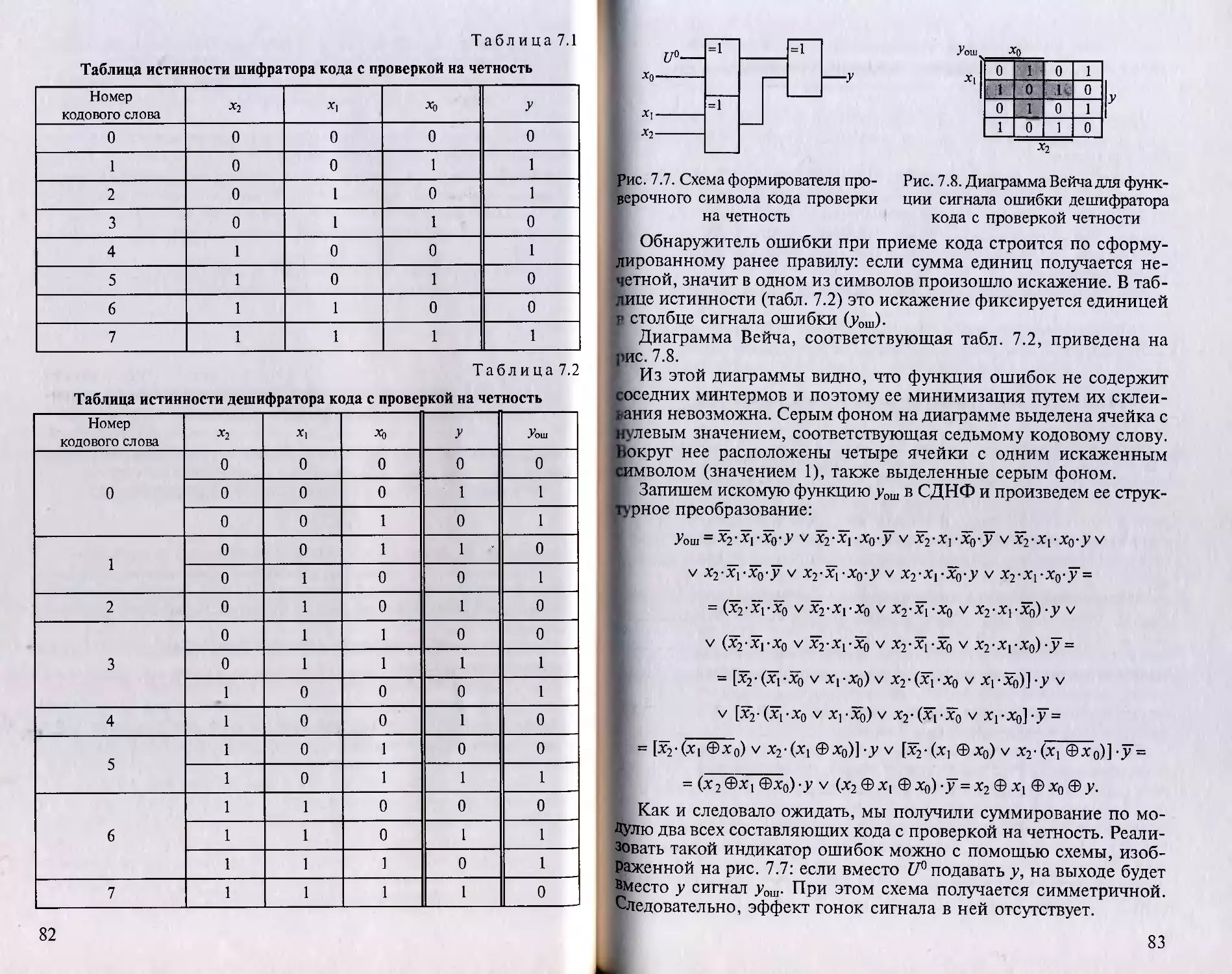

Седьмая глава посвящена изучению методики анализа и син-

теза комбинационных цифровых устройств на основе преобразо-

вателя кода Грея в натуральный двоичный код. Здесь рассмотрены

меры, позволяющие устранять эффект гонок; синтез формирова-

теля и приемного устройства кода с проверкой на четность, по-

зволяющего обнаруживать одиночные ошибки, а также шифрато-

ра и дешифратора кода Хэмминга, исправляющего одиночные

ошибки.

Шифраторы и дешифраторы в узком значении этих понятий,

т. е. как преобразователи кода «1 из т» в натуральный двоичный и

обратно, изучаются в восьмой главе, где также рассматриваются

назначение и применение приоритетных шифраторов.

Сведения о мультиплексорах и демультиплексорах и их приме-

нении изложены в девятой главе.

В десятой главе рассмотрены одно- и многоразрядные арифме-

тические и алгебраические сумматоры, представленные в форма-

те с фиксированной и плавающей запятыми, приведены краткие

сведения об арифметических умножителях.

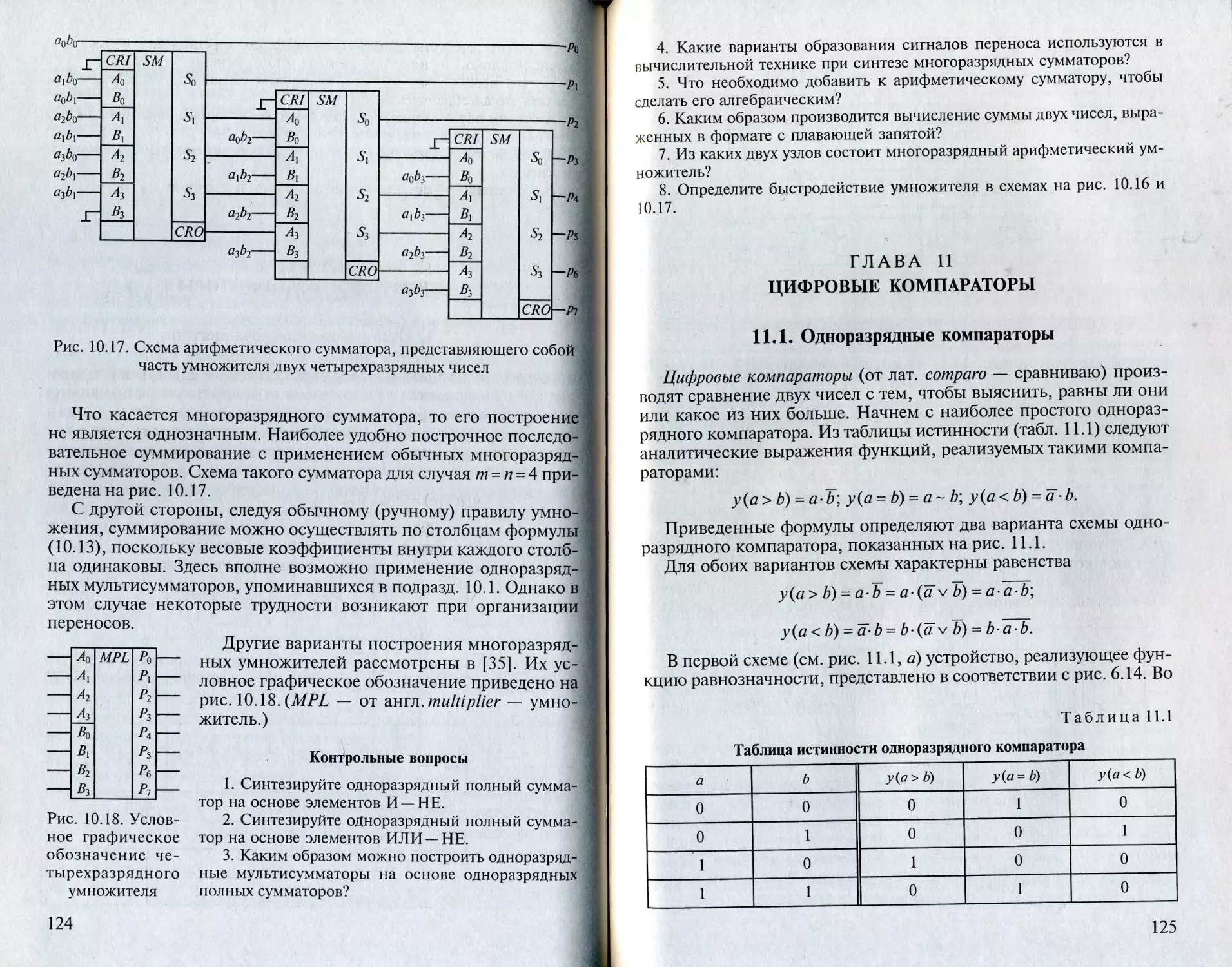

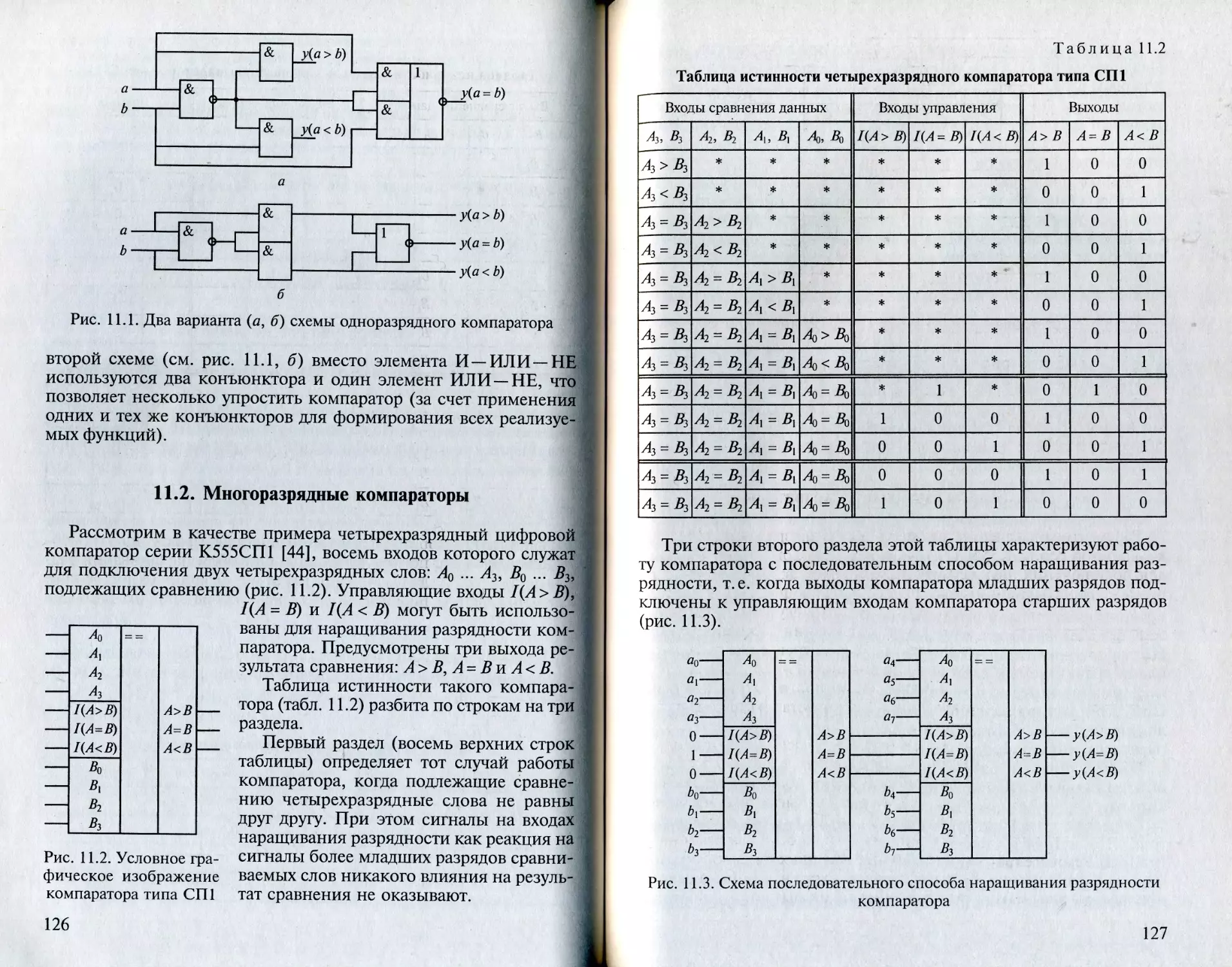

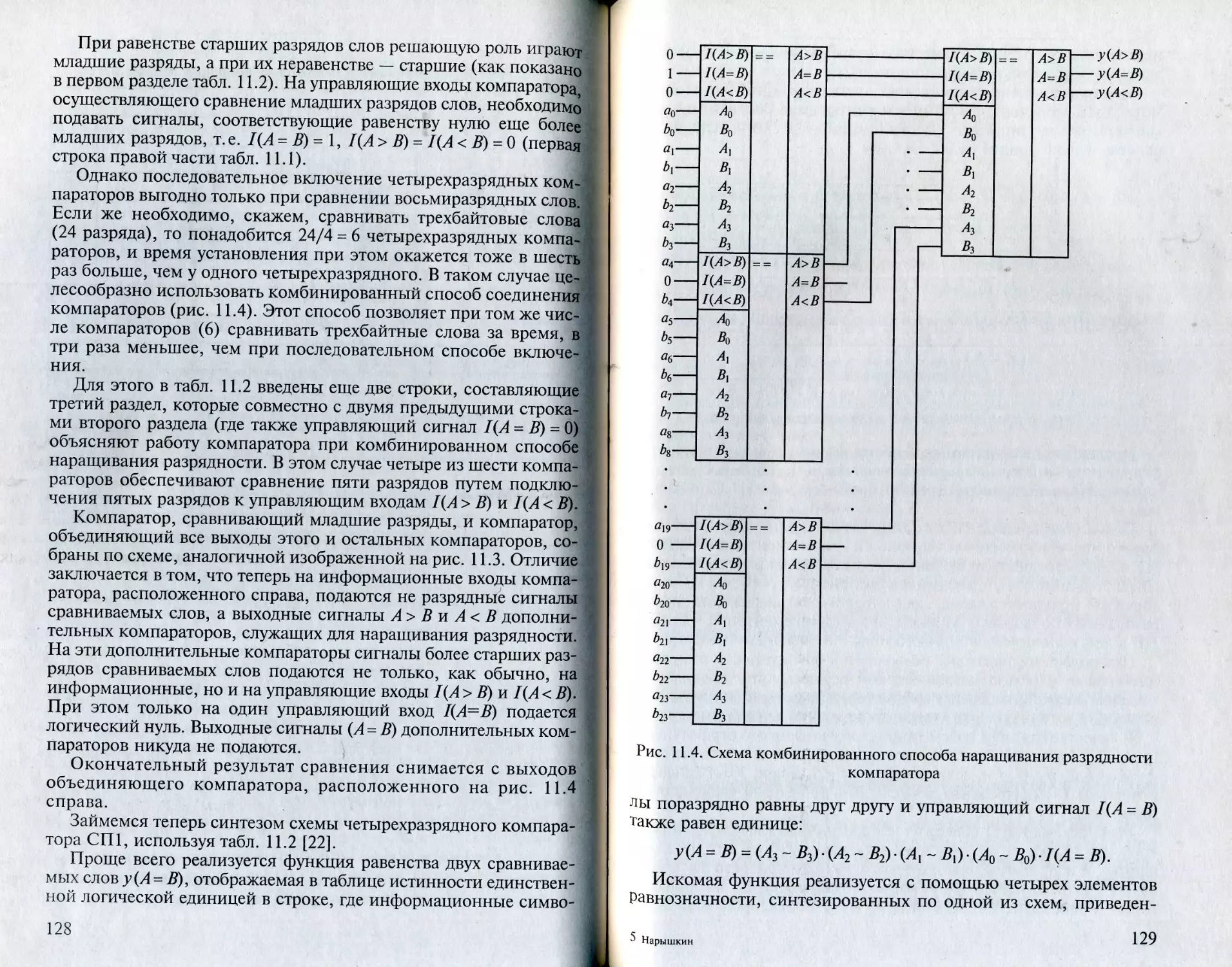

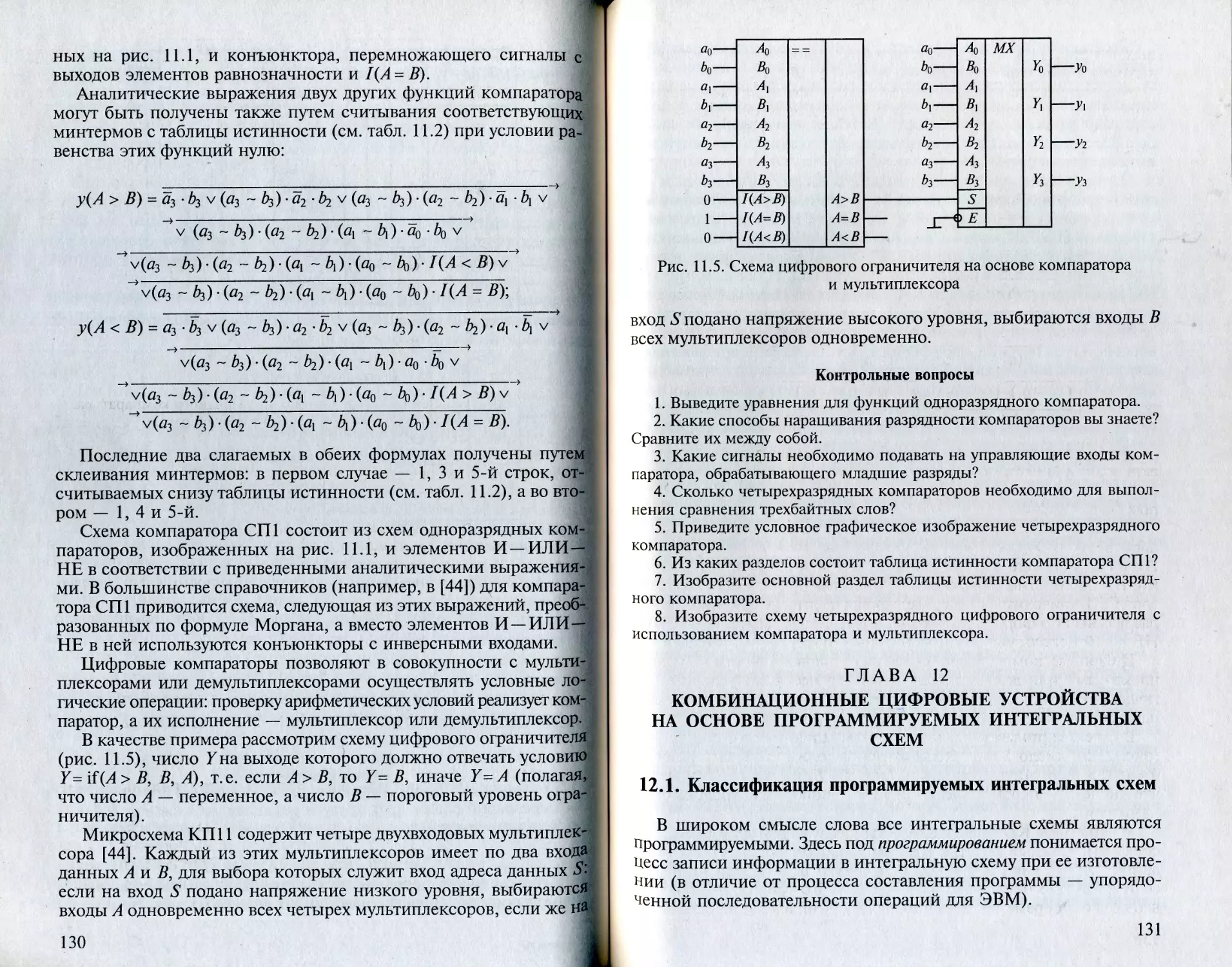

В одиннадцатой главе синтезируются одно- и многоразрядные

компараторы, показаны способы наращивания разрядности и

приведены примеры их использования.

Двенадцатая глава посвящена возможности реализации ком-

бинационных цифровых устройств на основе программируемых

интегральных схем. Особое внимание здесь уделено перспектив-

ным в настоящее время программируемым логическим интеграль-

ным схемам (ПЛИС).

В третьем разделе после общих сведений, приведенных в гл. 13,

рассмотрены во всем их разнообразии наиболее важные последова-

тельностные цифровые устройства, такие как триггеры (гл. 14),

счетчики (гл. 15) и регистры (гл. 16).

В четвертом разделе описаны микропроцессоры: их классифи-

кация и архитектура (гл. 17), системы команд (гл. 18), шинные

приемопередатчики (гл. 19), структура и основные элементы ариф-

метико-логического устройства (гл. 20), даны сведения о разра-

ботке программного обеспечения (гл. 21), микроконтроллерах (гл. 22)

и некоторых функциональных узлах микропроцессорных систем

(гл. 23).

В конце каждой главы предлагаются контрольные вопросы и

упражнения.

ВВЕДЕНИЕ

В настоящее время практически во всех радиотехнических уст-

ройствах и системах используется цифровая техника. Это связано

с целым рядом преимуществ цифровых сигналов перед аналого-

выми и, в первую очередь, с точностью, помехоустойчивостью и

возможностью хранения информации. Уточним некоторые основ-

ные определения и понятия, используя энциклопедический [6] и

толковые словари [10, 32].

Цифры (от позднелатинского cifra} — знаки для обозначения

чисел. Первые цифры появились у египтян и вавилонян. У ряда

народов (древних греков, финикиян, евреев, сирийцев) цифра-

ми служили буквы алфавита, что сохранилось частично в шест-

надцатеричной системе счисления; аналогичная система до XVI в.

применялась и в России. В средние века в Европе пользовались

системой римских цифр (I, II, III, IV, V, VI и т.д.), основанной

на употреблении особых знаков для десятичных разрядов 1=1,

X = 10, С = 100, М = 1000 и их половин V = 5, L = 50, D = 500.

Современные цифры (арабские), перенесенные в Европу араба-

ми в XIII в. (по-видимому, из Индии), получили широкое рас-

пространение во второй половине XV в. В узком смысле слова циф-

рами называются знаки: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9.

Счисление (нумерация) — выражение и обозначение чисел.

В развитых системах счисления некоторое число п единиц (на-

пример, десять) объединяется в одну единицу 2-го разряда (де-

сяток), то же число единиц 2-го разряда объединяется в единицу

3-го разряда (сотню) и т.д.

Число единиц п называется основанием системы счисления, а

знаки, употребляемые для обозначения количества единиц каж-

дого разряда, — цифрами. Наиболее применяемая система счисле-

ния — десятичная, с цифрами 0, 1, 2, 3, 4, 5, 6, 7, 8, 9. Проис-

хождение десятичной системы счисления связано с пальцевым

счетом. Некоторые народы пользовались пятеричной системой счис-

ления; в Древнем Вавилоне была распространена шестидесяте-

ричная система, следы которой сохранились в делении часа и гра-

дуса на 60 минут и минуты на 60 секунд.

В электронных вычислительных машинах (ЭВМ) применяется

двоичная система счисления, в которой каждое число выражается

10

при помощи двух цифр 0 и 1. В специализированных электронных

цифровых устройствах иногда используются комбинированные (сме-

шанные) системы, в которых каждый разряд имеет свой индиви-

дуальный весовой коэффициент. Например, в коде 3—2—1 старший

разряд имеет весовой множитель 3, средний — 2 и младший — 1.

Устройство — конструктивно законченное техническое сред-

ство, имеющее определенное функциональное назначение.

Цифровое устройство (ЦУ) обрабатывает цифровые воздействия

различной физической природы.

Первые арифметические ЦУ были позиционного типа механи-

ческого действия и назывались — абаки (от греч. abax — доска).

Абак — доска, разделенная на полосы, где передвигались камеш-

ки, кости (как в русских счетах), использовалась для арифмети-

ческих вычислений в Древней Греции, Риме, а затем и в Запад-

ной Европе до XVIII в.

В 50-е годы XX в. еще широко применялись арифмометры «Фе-

ликс» механического типа и начинали применяться клавишные и

счетно-перфорационные машины на электронных лампах.

Исключительно важное значение для всего последующего раз-

вития электронных цифровых устройств имело открытие, сделан-

ное в 1918 г. советским ученым М. А. Бонч-Бруевичем, обнару-

жившим, что напряжение и ток в апериодическом усилителе с

замкнутой петлей положительной обратной связи приобретают спо-

собность к скачкам (регенеративным процессам, т. е. очень быст-

рым изменениям). Изобретенное им спусковое устройство, в ко-

тором использовалось это открытие, явилось основой для полу-

чивших широкое применение в различных областях техники (в

том числе и вычислительной) всякого рода реле (триггеров) и

релаксационных генераторов (мультивибраторов и других уст-

ройств).

В цифровой вычислительной технике используются цифровые

сигналы, которые в промежутках между быстрыми перепадами

принимают лишь определенные квантованные значения. В более

узком смысле слова, быстрые перепады цифровых сигналов дол-

жны происходить в строго определенные моменты времени, за-

данные системой синхронизации.

Двоичный цифровой сигнал имеет два фиксированных уров-

ня, условно обозначаемые нулем х° и единицей х1, разделенные

между собой пороговым уровнем хпор.

Различают потенциальное и импульсное кодирование. При по-

тенциальном кодировании сигнал, превышающий пороговый уро-

вень (х > хпор), обозначается логической единицей (лог. 1), а сигнал,

который ниже порогового уровня (х < хпор) обозначается логичес-

ким нулем (лог. 0).

При импульсном кодировании существенным является не абсо-

лютный уровень сигнала, а знак (направление) перепада. Если

принято, что работа происходит по положительному перепаду,

фронт импульса кодируется логической единицей, а вся осталь-

ная часть сигнала — логическим нулем. При работе по отрица-

тельному перепаду срез импульса кодируется логической едини-

цей, а все остальное — логическим нулем.

Таким образом, кодирование цифрового сигнала информаци-

онными (логическими) символами является условным и требует

обязательной оговорки.

Цифровая вычислительная машина (ЦВМ) выполняет по задан-

ной программе обработку информации, представленной в циф-

ровой форме. Каждой цифре в ЦВМ соответствует один или не-

сколько дискретных сигналов, например электрических импуль-

сов. Процесс обработки информации на ЦВМ сводится к такому

преобразованию сигналов, при котором результирующий сигнал

численно равен итогу соответствующей вычислительной опера-

ции. Принципиально ЦВМ состоит из следующих устройств: ариф-

метического, памяти, управления и ввода-вывода данных.

Блок ЦВМ, который управляет ее работой, называется процес-

сором. Процессор, созданный на основе интегральной микросхе-

мы, называется микропроцессором (МП).

Изобретение транзистора Д. Бардиным, У. Браттейном и

У. Шокли (США) в конце 40-х годов XX в. произвело революци-

онное действие в электронике, радиотехнике и вычислительной

технике. Полупроводниковые приборы, имеющие значительно

меньшие габариты и массы, чем радиолампы, обусловили повы-

шение надежности работы радиоаппаратуры, счетно-математичес-

ких машин и других установок.

В радиотехнике цифровые вычислительные устройства обеспе-

чивают:

1) формирование и обработку сигналов в системах радиолока-

ции, телевидения, радионавигации, радиоуправления, передачи

информации;

2) моделирование реальных радиотехнических устройств, сис-

тем и комплексов;

3) анализ и оптимизацию характеристик отдельных устройств

(например, распределения электромагнитного поля в ближней зоне

раскрыва антенны);

4) работу систем автоматизированного проектирования.

Все перечисленные задачи, за исключением первой, решаются

с помощью универсальных цифровых вычислительных машин. Что

касается первой задачи, как правило, она решается путем исполь-

зования как специализированных цифровых вычислительных уст-

ройств (синхронизаторов, формирователей зондирующих широ-

кополосных сигналов, аналого-цифровых и цифроаналоговых пре-

образователей, устройств первичной по одному циклу обзора об-

работки информации, т.е. устройств обнаружения и оценки пара-

12

метров сигнала), так и универсальных (от микро- до больших

ЭВМ).

Все проблемы вычислительной техники складываются из трех

основных компонентов: создания элементной базы; разработки

самих ЭВМ и программного обеспечения к ним; экономически

выгодного использования вычислительной техники в народном

хозяйстве.

Следует отметить, что резкое изменение элементной базы пу-

тем перехода от схем на дискретных элементах к интегральным

микросхемам различной степени интеграции привело к качествен-

ному скачку в области инженерных методов синтеза цифровых

вычислительных устройств на их основе.

Понимание работы цифровых устройств, а тем более их разра-

ботка, невозможны без глубокого знания основ алгебры логики.

Алгебра логики — система алгебраических методов решения ло-

гических задач; в узком смысле — это табличное, матричное по-

строение логики высказываний, определяющее логические опе-

рации над ними.

Исторические корни алгебры логики обнаруживаются в Древ-

ней Греции и связаны в первую очередь с именем философа Ге-

раклита (конец VI—начало V вв. до н.э.), одного из основателей

диалектики.

Закон, которым связано всякое изменение и движение, Герак-

лит называет Логосом (от греч. logos — речь, слово, разумное ос-

нование). Этот термин впервые вводится в философию Геракли-

том для обозначения закономерностей связи вещей [5].

Диалектика (от греч. dialektike — искусство вести беседу, спор) —

это философское учение о становлении и развитии бытия и позна-

ния и основанный на этом учении метод мышления. В истории

философии выдвигались различные толкования диалектики: как

учения о вечном становлении и изменчивости бытия (Гераклит);

искусства диалога, достижения истины путем противоборства мыс-

лей (Сократ, 470—399 гг. до н.э.); метода расчленения и связыва-

ния понятий с целью постижения сверхчувственной (идеальной)

сущности вещей (Платон, 428/427 — 348/347 гг. до н.э.) и др. [6].

Алгебра (арабское слово) — часть математики, связанная с ре-

шением алгебраических уравнений (приравниванием двух алгеб-

раических выражений). В современной алгебре изучаются алгебраи-

ческие операции, аналогичные действиям над числами. Такие опе-

рации могут выполняться над многочленами, векторами, матри-

цами и т. д.

Алгебраическое выражение составляется из букв и чисел, соеди-

ненных или отмеченных знаками алгебраических действий и зна-

ками последовательности выполнения этих действий.

Логика (от греч. logike) — наука о способах доказательств и

опровержений; совокупность научных теорий, в каждой из ко-

13

торых рассматриваются определенные способы доказательств и

опровержений. Основателем логики считается ученик Платона,

древнегреческий философ и ученый Аристотель1 (384—322 гг.

до н.э.).

Силлогистика (от греч. syllogistikos — выводящий умозаключе-

ние) — исторически первое, созданное Аристотелем учение о

логической дедукции, в котором рассматриваются рассуждения в

форме силлогизмов.

Чтобы отличить логические формы от содержания и логичес-

кие константы от логических переменных, Аристотель первый ввел

специальные обозначения для тех и других: логические констан-

ты он обозначал словесно, а логические переменные — буквами

греческого алфавита2.

В качестве примера можно привести выражение первой фигу-

ры силлогизма: «Если А сказывается о всяком В, а В сказывается о

всяком Г, то А необходимо сказывается о всяком Г». Здесь слова-

ми «если ..., то» и «сказывается о всяком» выражаются логичес-

кие константы следования и суждения, т. е. логические связи за-

конченных мыслей друг с другом и элементов отдельных закон-

ченных мыслей — посылок, а буквами греческого алфавита обо-

значаются логические переменные, допускающие подстановку на

их место определенных терминов [5].

1 Аристотель родился в 384 г. до н.э. в Стагире — греческой колонии на Фра-

кийском побережье. Его отец Никомах был придворным врачом и другом маке-

донского царя Аминты II. В 343 г. македонский царь Филипп приглашает Аристо-

теля заняться воспитанием своего сына Александра (будущего Александра Ма-

кедонского), которому тогда исполнилось 13 лет. Аристотель отправляется в Пел-

лу, где и руководит воспитанием Александра более трех лет. После того как

Александр стал царем, Аристотель переехал в свой родной город Стагир, а в 335 г.

вернулся снова в Афины. В предместье Афин — Ликее (Лицее) около храма Апол-

лона Ликейского он создает свою собственную школу. В этот период у Аристоте-

ля созревает критическое отношение к учению Платона (в частности, к учению

об идеях) [6]. Необходимо заметить, что сочинения Аристотеля охватывают все

области тогдашних знаний.

Аристотель видел свою заслугу главным образом в том, что он открыл сил-

логизм, который есть прежде всего средство доказывания объективной истины.

Логика Аристотеля основана на объективном различении истины и лжи (от

греч. pseudos — псевдо). Истина понимается Аристотелем материалистически —

как соответствие утверждения или отрицания бытия, действительности, неза-

висимой от сознания, а ложь — как несоответствие.

Индукция по Аристотелю — это та же силлогистическая связь, но в обратном

порядке: это не вывод через знание причины или следствия, а вывод о причине

и следствии через знание носителей причины и следствия. Осуществляется ли

познание в направлении от общего к единичному (в силлогизме) или от еди-

ничного к общему (в индукции), связь между общим и единичным, определяю-

щим и определяемым остается одной и той же.

2 Буквы, употребляемые Аристотелем первоначально для сокращения слов

(впоследствии их стали называть аббревиатурой), позже стали использоваться им

в качестве настоящих логических переменных.

14

В соответствии с учением о

суждении как утверждении или

отрицании Аристотель различа-

ет в суждении два элемента: под-

лежащее — то, относительно

чего что-то сказывается, разумея

под подлежащим то, на что на-

правлена мысль, и сказуемое,

т. е. все то, что утверждается или

отрицается [5].

Впоследствии Боэций1 объе-

динил все возможные четыре

случая отрицания членов соеди-

нения коннексии (отрицание отсутствия двух членов коннексии;

отрицание сосуществования двух членов коннексии; отрицание

наличия одного и отсутствия другого; отрицание отсутствия од-

ного и наличия другого) и создал учение об эквивалентности форм

коннексии, дизъюнкции и условной связи [5] — это то, что те-

перь называют формулами Моргана [6]2.

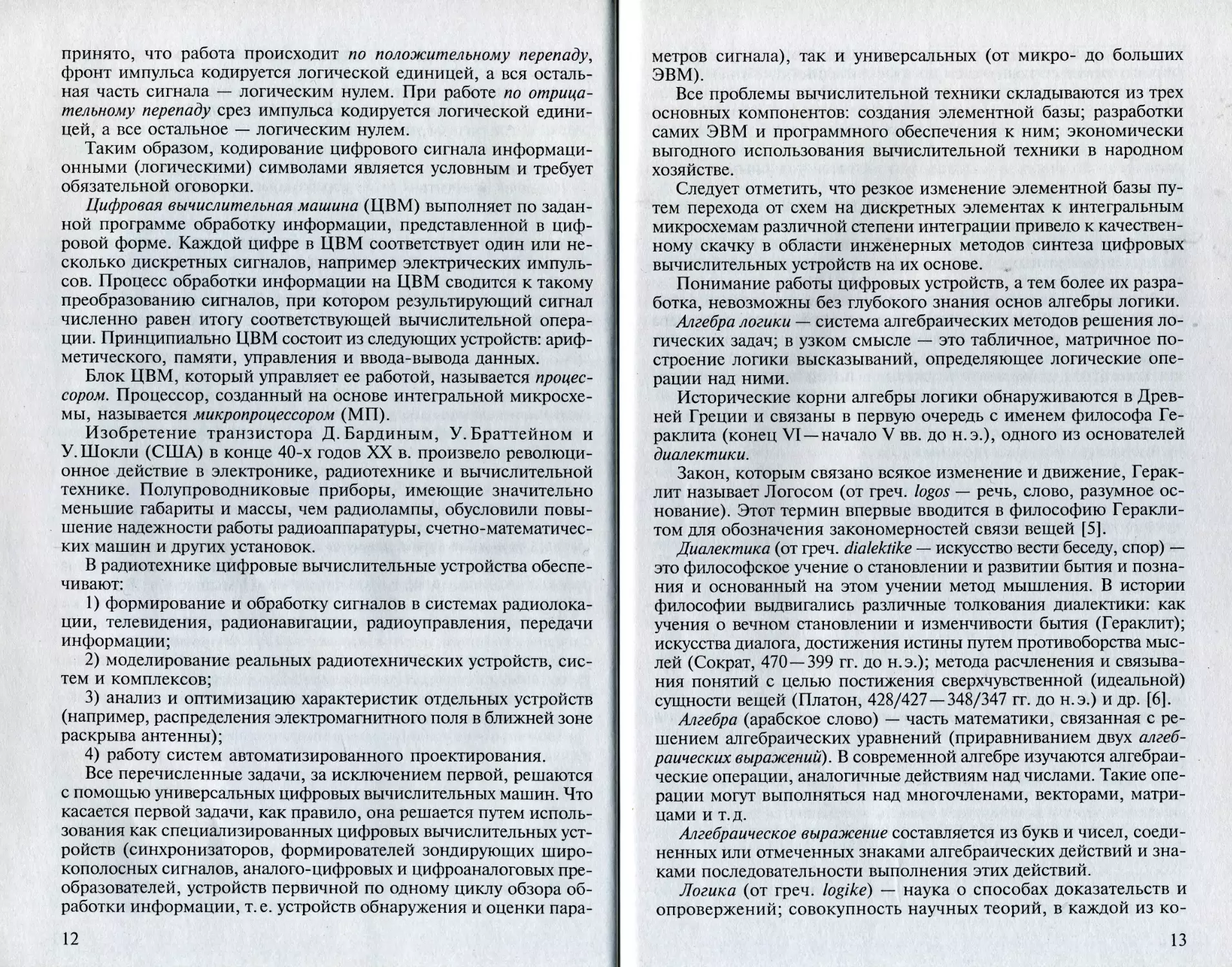

Леонард Эйлер3 предложил изображать логические объекты в

виде диаграмм (рис. В.1). Спустя более чем 100 лет это же предло-

жил Джон Венн4. Такие диаграммы иллюстрируют отношения в

алгебре классов. Если прямоугольник, круг, квадрат и треуголь-

ник обозначены соответственно I, хь х2, х3, то диаграмма показы-

вает, что всякая логическая функция от хь х2, х3 может быть пред-

ставлена как объединение минимальных многочленов (минтер-

мов) от хь х2, х3 [13]. Это по существу предвосхищает теорему

Клода Шеннона5 о представлении логических функций в канони-

ческом виде: в совершенной дизъюнктивной нормальной форме

(СДНФ) или, что то же самое, теорему о разложении логических

1 Боэций (ВоёЕих) Аниций Манлий Северин (470—525) — христианский

философ и римский государственный деятель. Перевел на латинский язык логи-

ческие сочинения Аристотеля и Порфирия, «Арифметику» Никомаха, «Начала»

Евклида.

2 Морган (De Morgan) Огастес (Августус) (1806—1871) — шотландский ма-

тематик и логик. Создал труды по алгебре, теории рядов. Независимо от Дж. Буля

пришел к основным идеям математической логики.

3 Эйлер (Euler) Леонард (1707—1783) — математик, механик, физик и аст-

роном, швейцарец по происхождению, в 1726 г. был приглашен в Петербургс-

кую Академию Наук и в 1727 г. переехал в Россию. Впоследствии академик Пе-

тербургской АН.

4 Венн (Venn) Джон (1834—1923) — английский логик, разработал графи-

ческий аппарат диаграмм, фактически эквивалентный логике классов. Создал

труды в области вероятностной и индуктивной логики.

5 Шеннон (Shannon) Клод Элвуд (1916—2001) — американский инженер и

математик. Один из создателей математической теории информации. Его основ-

ные труды по теории релейно-контактных схем, математической теории связи,

кибернетике.

15

функций в ряд по минтермам. Во второй половине XX в. эти диаг-

раммы приобрели матричный вид и стали называться в честь их

создателей картами Карно и диаграммами Вейча1.

И наконец {«Last of list is not last of means!»), о Джордже Буле2,

обобщившем алгебру логики, которая поэтому, как правило, на-

зывается булевой алгеброй.

Вопрос о том, в каких отношениях находятся старая логика и

логика новая, современная, всегда интересовал исследователей и

до сих пор является предметом дискуссий и обсуждений. С одной

стороны, речь идет о том, как вписываются в современную логи-

ку результаты многовекового опыта по исследованию силлогис-

тики, и на этот вопрос в какой-то мере отвечает анализ, пред-

принятый в [7]. С другой стороны, представляет интерес и обрат-

ная задача — уточнение того, какая часть современной логики

может быть описана силлогистически. Предлагаемый в [7] ответ

состоит в следующем: что «вся элементарная булева алгебра ока-

зывается содержащейся в некоторой силлогистической теории.

А так как элементарная булева алгебра эквивалентна одноместно-

му первопорядковому исчислению предикатов, то данный ответ

означает, что одноместный фрагмент исчисления предикатов со-

держится в силлогистике».

Контрольные вопросы

1. Кто является основателем алгебры логики?

2. Приведите определение понятия алгебры логики.

3. Дайте определение понятия силлогизма.

4. Чем отличается индукция от силлогизма?

1 Предлагается отличникам самостоятельно разгадать принцип, по которому

каждому участку диаграммы на рис. В.1 присвоена надпись из трех букв, с чер-

точками над некоторыми.

2 Буль (Bool) Джордж (1815—1864) — английский математик и логик, один

из основоположников математической логики, усовершенствовавший ее до со-

временного состояния [5,7,13]. Кстати, он — отец известной романистки Этель

Лилиан Войнич, автора «Овода».

РАЗДЕЛ I

ОСНОВЫ АЛГЕБРЫ ЛОГИКИ*

ГЛАВА 1

ОСНОВНЫЕ ОБОЗНАЧЕНИЯ И ПОСТУЛАТЫ

1.1. Основные высказывания и переменные

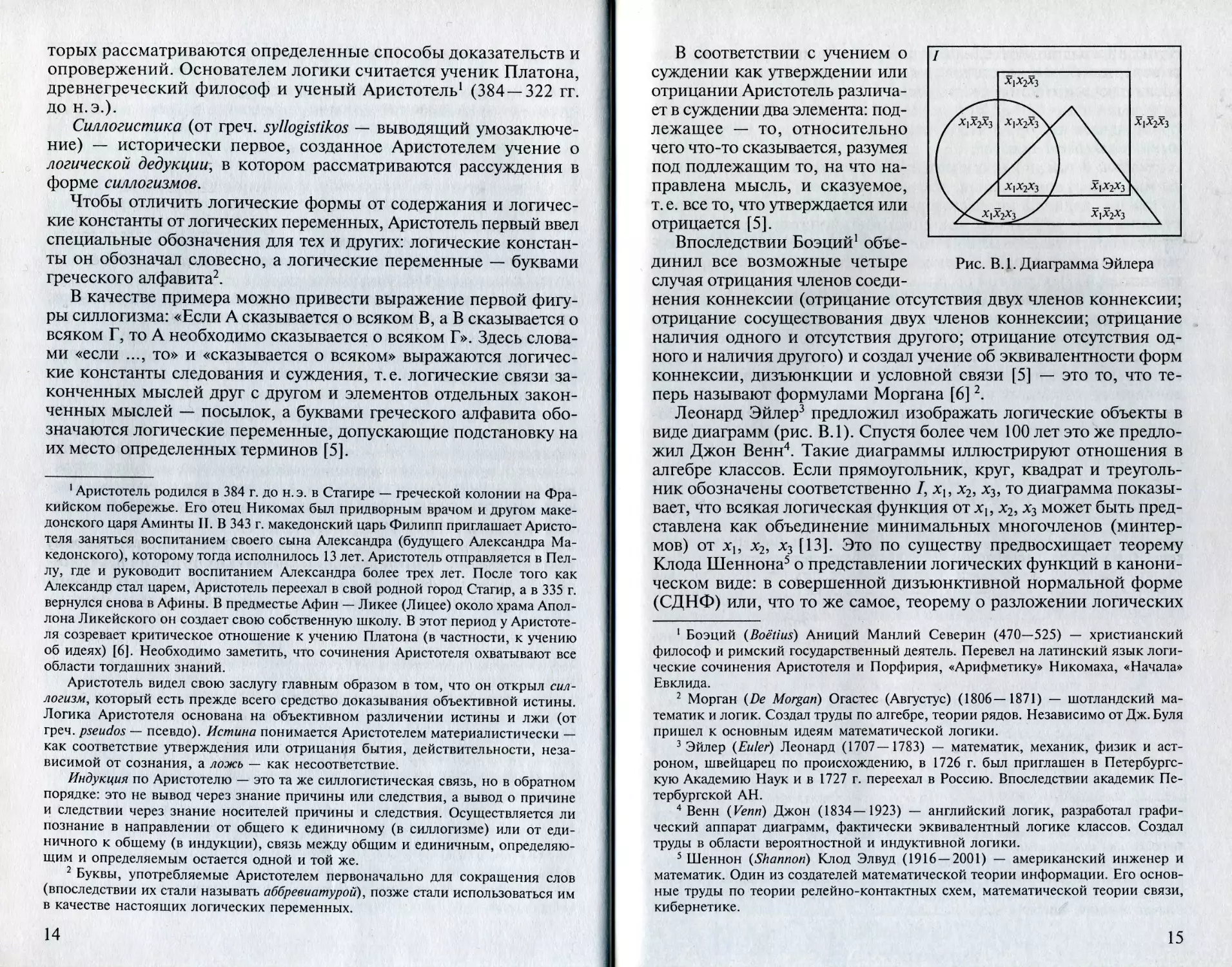

Каждое высказывание в бинарной (аристотелевой) алгебре

логики может быть представлено переменной, которая обычно

обозначается латинскими строчными буквами х или у. Высказыва-

ния могут быть утвердительными (определенными) и неопреде-

ленными (безразличными).

Утвердительных высказываний два: истинное и ложное, нео-

пределенное — только одно (табл. 1.1).

Следует отметить, что высказывания Ложь и Истина в со-

временных компьютерных программах также используются как

обозначения. Например, если в WinWord курсором мыши в стро-

ке меню нажать кнопку Таблица, а затем Формула и Вставить

функцию и выбрать одну из функций: FALSE или TRUE, на

экране будет напечатано 0 или 1. Попробуйте это сами прове-

рить.

Обозначение неопределенности пока еще не установлено. Пред-

ложение использовать в качестве символа 1А (или 0,5) обосновано

далее.

* В зарубежных изданиях алгебру логики в применении к цифровым устрой-

ствам называют алгеброй переключательных функций {algebra of the switching

functions)

17

1.2. Основные логические операции

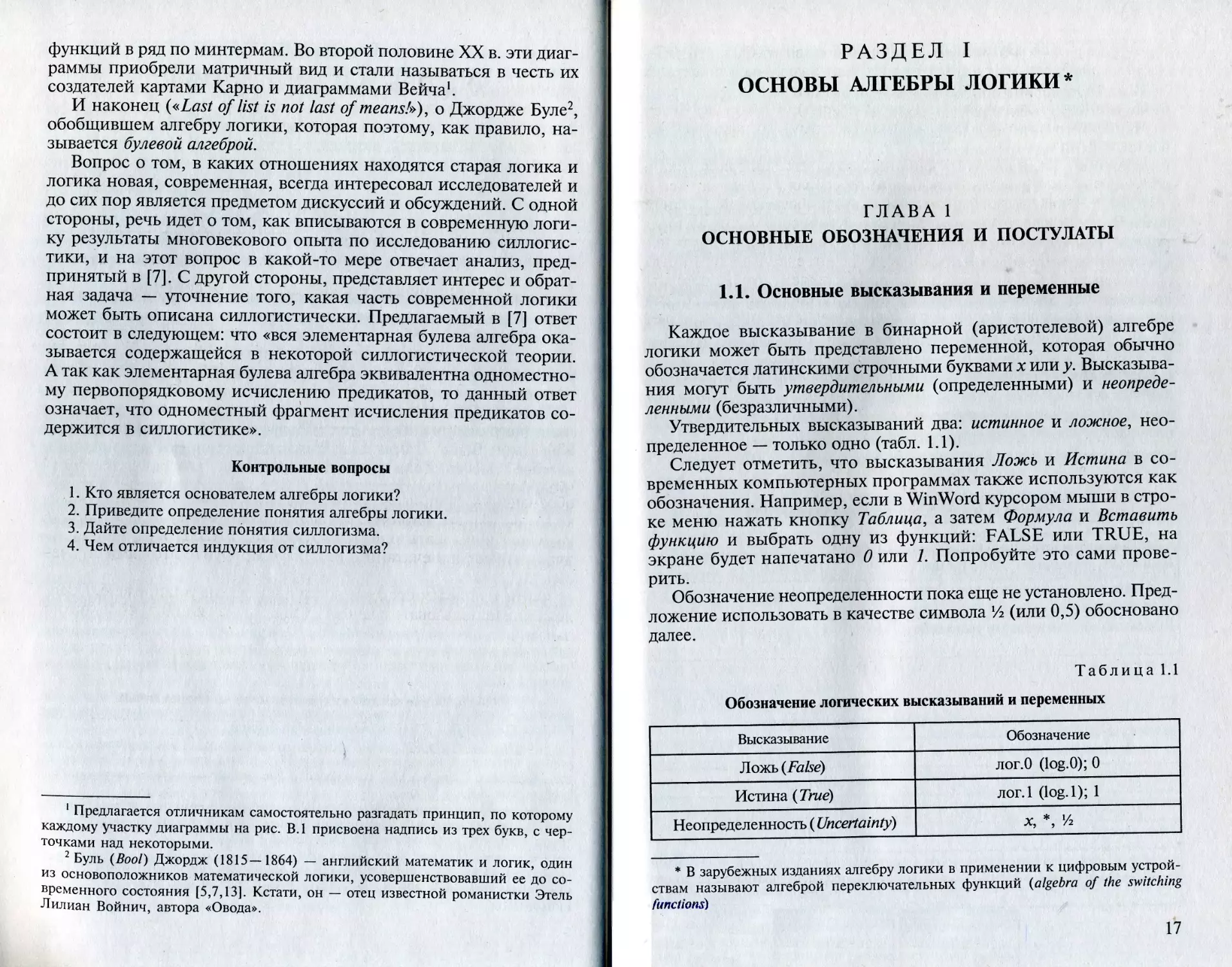

Всего логических операций три: одна унарная — инверсия и две

бинарных — дизъюнкция и конъюнкция (табл. 1.2).

Чаще всего инверсия (от лат. inversio — перестановка) обозна-

чается чертой над аргументом (х), дизъюнкция (от лат. disjunctio —

разобщение) — значком v, а конъюнкция (от лат. conjunctio —

союз, связь) — символом обычного умножения (•) [6].

Смысл логических операций раскрывается с помощью диаг-

рамм Эйлера (рис. 1.1) и перебора всех возможных значений аргу-

ментов, над которыми проводятся эти операции (табл. 1.3).

Проанализируем данные табл. 1.3.

Инверсия. Сопоставление столбцов таблицы Xi с х i и х0 с *о по-

казывает, что операцию инверсии можно выполнять чисто ариф-

метически: 0 = 1-0; 1 = 1 - 1 и алгебраически: х = 1 - х. Отсюда и

возникло еще одно название этой операции — дополнение. В случае

неопределенности (если ее обозначить ’Л), получим % = 1 - !6 = !4,

т. е. инверсия неопределенности равна самой неопределенности, что

очевидно. Отсюда же можно сделать вывод, что двойная инверсия

приводит к исходному аргументу, т.е. х=1-х = 1- (1-х) = х, и это

называется законом двойного отрицания.

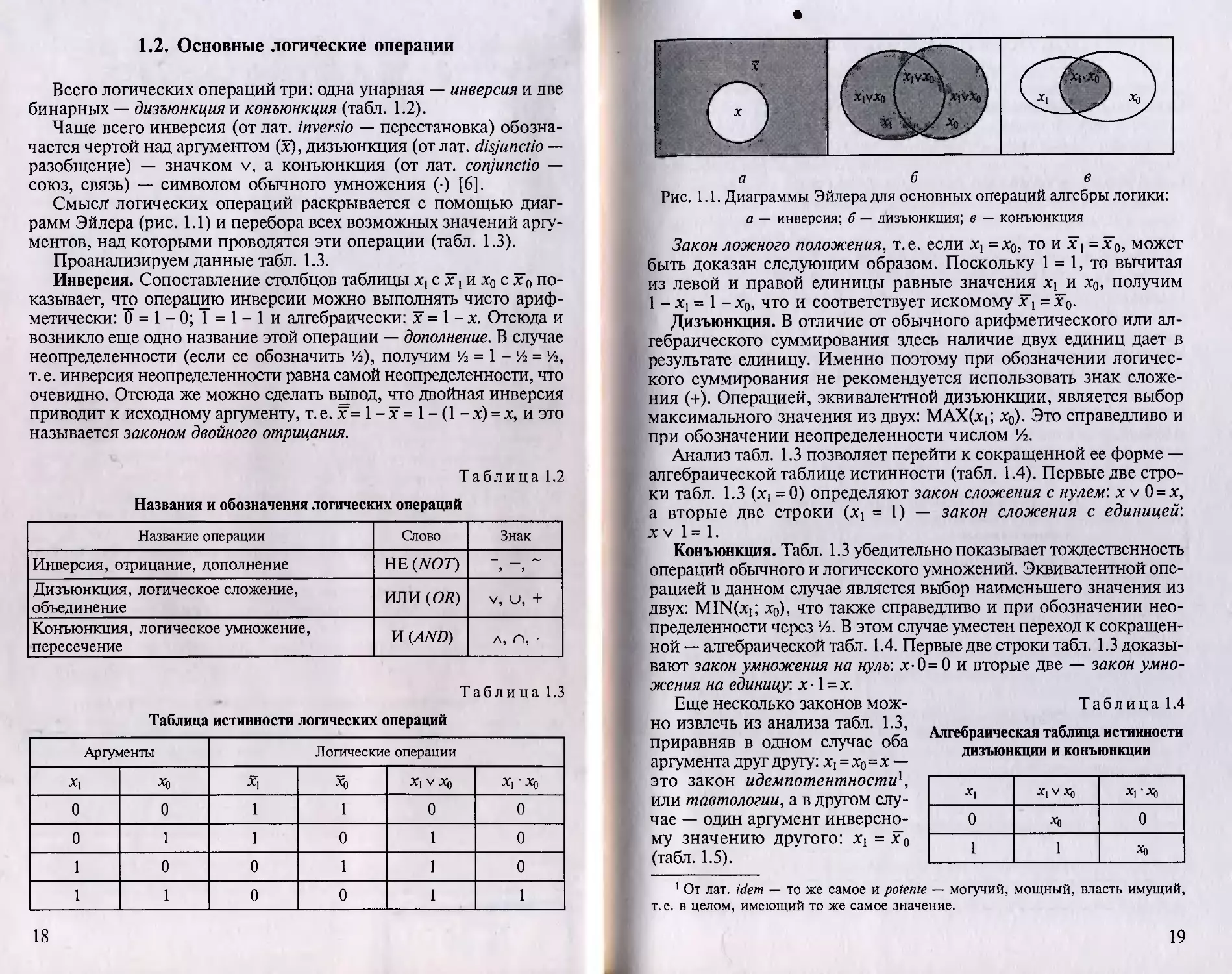

Таблица 1.2

Названия и обозначения логических операций

Название операции Слово Знак

Инверсия, отрицание, дополнение НЕ (NOT) 5 5

Дизъюнкция, логическое сложение, объединение ИЛИ (OR) V, и, +

Конъюнкция, логическое умножение, пересечение И (AND) Л, п, •

Таблица 1.3

Таблица истинности логических операций

Аргументы Логические операции

Х1 Xj Х| X) х, vxj Xi -X)

0 0 1 1 0 0

0 1 1 0 1 0

1 0 0 1 1 0

1 1 0 0 1 1

18

а б в

Рис. 1.1. Диаграммы Эйлера для основных операций алгебры логики:

а — инверсия; б — дизъюнкция; в — конъюнкция

Закон ложного положения, т.е. если %i = х$, то и х\ = Xq, может

быть доказан следующим образом. Поскольку 1 = 1, то вычитая

из левой и правой единицы равные значения Х[ и х0, получим

1 - %! = 1 -х0, что и соответствует искомому х i = х0.

Дизъюнкция. В отличие от обычного арифметического или ал-

гебраического суммирования здесь наличие двух единиц дает в

результате единицу. Именно поэтому при обозначении логичес-

кого суммирования не рекомендуется использовать знак сложе-

ния (+). Операцией, эквивалентной дизъюнкции, является выбор

максимального значения из двух: МАХ(хв х0). Это справедливо и

при обозначении неопределенности числом ‘Л.

Анализ табл. 1.3 позволяет перейти к сокращенной ее форме —

алгебраической таблице истинности (табл. 1.4). Первые две стро-

ки табл. 1.3 (Х| = 0) определяют закон сложения с нулем: х v 0 = х,

а вторые две строки (xt = 1) — закон сложения с единицей:

xv 1=1.

Конъюнкция. Табл. 1.3 убедительно показывает тождественность

операций обычного и логического умножений. Эквивалентной опе-

рацией в данном случае является выбор наименьшего значения из

двух: х0), что также справедливо и при обозначении нео-

пределенности через Уг. В этом случае уместен переход к сокращен-

ной — алгебраической табл. 1.4. Первые две строки табл. 1.3 доказы-

вают закон умножения на нуль: х-0 = 0 и вторые две — закон умно-

жения на единицу: х • 1 = х.

Еще несколько законов мож- но извлечь из анализа табл. 1.3, приравняв в одном случае оба аргумента друг другу: х1 = х0=х — это закон идемпотентности1, или тавтологии, а в другом слу- чае — один аргумент инверсно- му значению другого: х{ = х0 (табл. 1.5). Таблица 1.4 Алгебраическая таблица истинности дизъюнкции и конъюнкции

*1 *1 хгхь

0 Ла 0

1 1 Ла

1 От лат. idem — то же самое и potente — могучий, мощный, власть имущий,

т.е. в целом, имеющий то же самое значение.

19

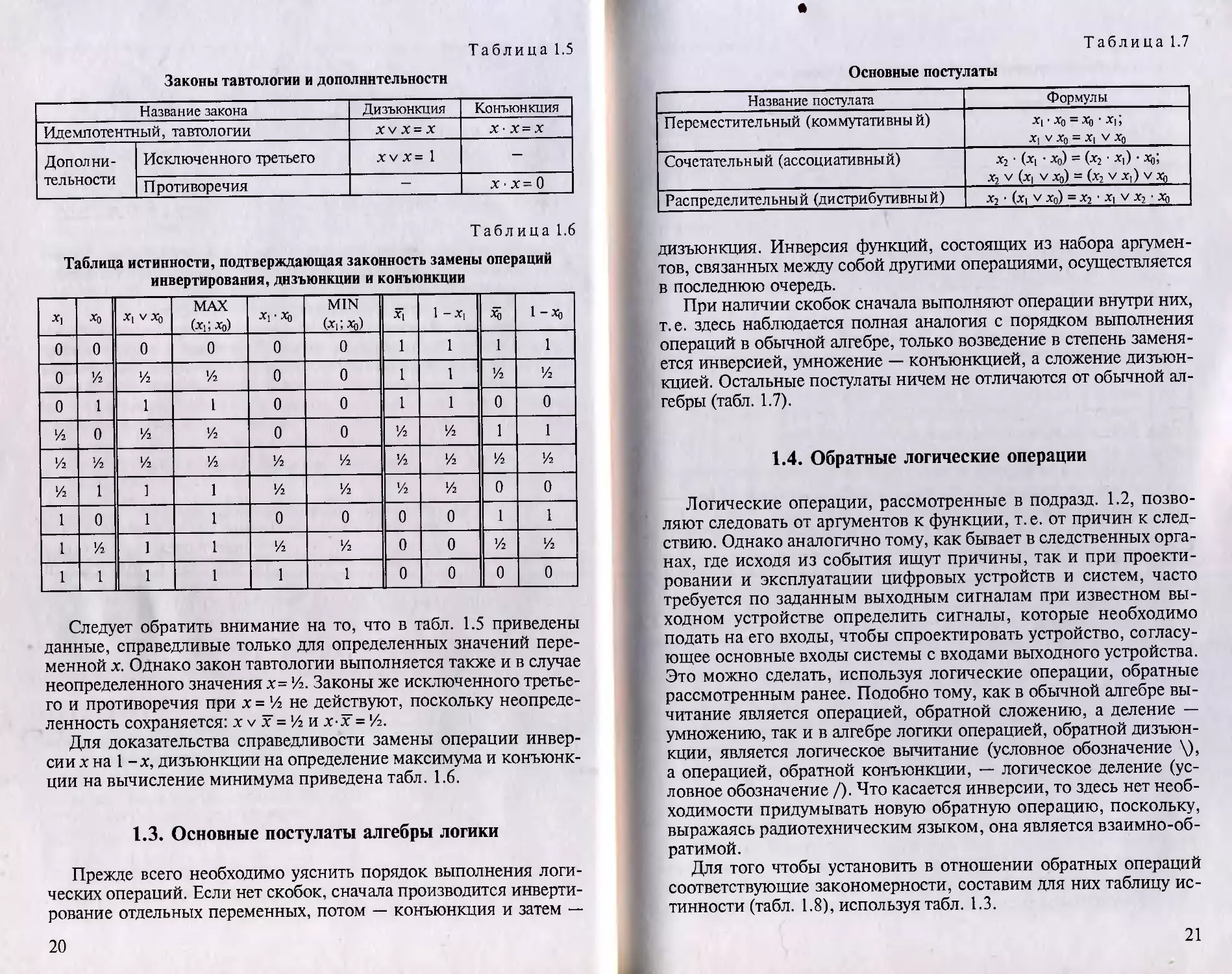

Таблица 1.5

Законы тавтологии и дополнительности

Название закона Дизъюнкция Конъюнкция

Идемпотентный, тавтологии X V Х = X X х= X

Дополни- Исключенного третьего х v х= 1 —

шльносш Противоречия — х • х= 0

Таблица 1.6

Таблица истинности, подтверждающая законность замены операций

инвертирования, дизъюнкции и конъюнкции

*1 х, vxb МАХ (хьхь) Х1 л<, MIN Х1 1 -Х1 1 -Xfl

0 0 0 0 0 0 1 1 1 1

0 и А А 0 0 1 1 а а

0 1 1 1 0 0 1 1 0 0

И 0 А А 0 0 А А 1 1

!4 ‘А а А А а А А А А

И 1 1 1 А а А А 0 0

1 0 1 1 0 0 0 0 1 1

1 А 1 1 А А 0 0 А А

1 1 1 1 1 1 0 0 0 0

Следует обратить внимание на то, что в табл. 1.5 приведены

данные, справедливые только для определенных значений пере-

менной х. Однако закон тавтологии выполняется также и в случае

неопределенного значения х= !4. Законы же исключенного третье-

го и противоречия при х = % не действуют, поскольку неопреде-

ленность сохраняется: х v х = ’/> и х-х = */2.

Для доказательства справедливости замены операции инвер-

сии х на 1 -х, дизъюнкции на определение максимума и конъюнк-

ции на вычисление минимума приведена табл. 1.6.

1.3. Основные постулаты алгебры логики

Прежде всего необходимо уяснить порядок выполнения логи-

ческих операций. Если нет скобок, сначала производится инверти-

рование отдельных переменных, потом — конъюнкция и затем —

20

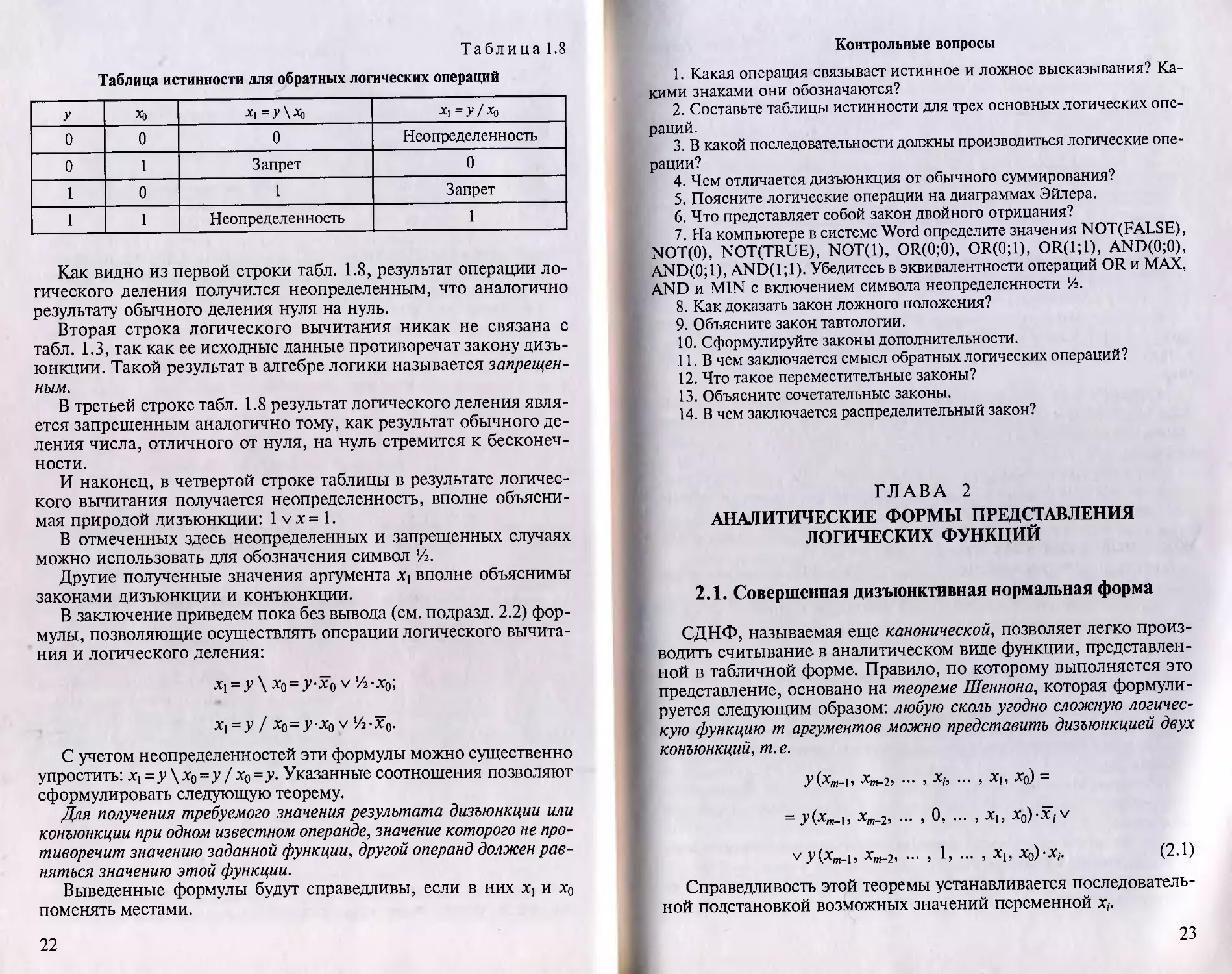

Т аблица 1.7

Основные постулаты

Название постулата Формулы

Переместительный (коммутативны й) ХГХо = ХЬ -Хь Х| V Хо = Х| V х0

Сочетательный (ассоциативный) Х2 (х, х0) = (х2 Xi) • Xq, Х2 V (Х| V Хо) = (х2 V Х|) V Хо

Распределительный (дистрибутивный) Х2 • (х, V Хо) = Х2 • Х[ V Х2 Хо

дизъюнкция. Инверсия функций, состоящих из набора аргумен-

тов, связанных между собой другими операциями, осуществляется

в последнюю очередь.

При наличии скобок сначала выполняют операции внутри них,

т.е. здесь наблюдается полная аналогия с порядком выполнения

операций в обычной алгебре, только возведение в степень заменя-

ется инверсией, умножение — конъюнкцией, а сложение дизъюн-

кцией. Остальные постулаты ничем не отличаются от обычной ал-

гебры (табл. 1.7).

1.4. Обратные логические операции

Логические операции, рассмотренные в подразд. 1.2, позво-

ляют следовать от аргументов к функции, т. е. от причин к след-

ствию. Однако аналогично тому, как бывает в следственных орга-

нах, где исходя из события ищут причины, так и при проекти-

ровании и эксплуатации цифровых устройств и систем, часто

требуется по заданным выходным сигналам при известном вы-

ходном устройстве определить сигналы, которые необходимо

подать на его входы, чтобы спроектировать устройство, согласу-

ющее основные входы системы с входами выходного устройства.

Это можно сделать, используя логические операции, обратные

рассмотренным ранее. Подобно тому, как в обычной алгебре вы-

читание является операцией, обратной сложению, а деление —

умножению, так и в алгебре логики операцией, обратной дизъюн-

кции, является логическое вычитание (условное обозначение \),

а операцией, обратной конъюнкции, — логическое деление (ус-

ловное обозначение /). Что касается инверсии, то здесь нет необ-

ходимости придумывать новую обратную операцию, поскольку,

выражаясь радиотехническим языком, она является взаимно-об-

ратимой.

Для того чтобы установить в отношении обратных операций

соответствующие закономерности, составим для них таблицу ис-

тинности (табл. 1.8), используя табл. 1.3.

21

Таблица 1.8

Таблица истинности для обратных логических операций

У ЛЬ *1 = У \ ЛЬ X) = У / Хо

0 0 0 Неопределенность

0 1 Запрет 0

1 0 1 Запрет

1 1 Неопределенность 1

Как видно из первой строки табл. 1.8, результат операции ло-

гического деления получился неопределенным, что аналогично

результату обычного деления нуля на нуль.

Вторая строка логического вычитания никак не связана с

табл. 1.3, так как ее исходные данные противоречат закону дизъ-

юнкции. Такой результат в алгебре логики называется запрещен-

ным.

В третьей строке табл. 1.8 результат логического деления явля-

ется запрещенным аналогично тому, как результат обычного де-

ления числа, отличного от нуля, на нуль стремится к бесконеч-

ности.

И наконец, в четвертой строке таблицы в результате логичес-

кого вычитания получается неопределенность, вполне объясни-

мая природой дизъюнкции: 1 v х = 1.

В отмеченных здесь неопределенных и запрещенных случаях

можно использовать для обозначения символ 'А.

Другие полученные значения аргумента X] вполне объяснимы

законами дизъюнкции и конъюнкции.

В заключение приведем пока без вывода (см. подразд. 2.2) фор-

мулы, позволяющие осуществлять операции логического вычита-

ния и логического деления:

*1 = У\xb=y-X(>v‘Л-хь;

Х\ = У / х0=у-х0 v */2-х0.

С учетом неопределенностей эти формулы можно существенно

упростить: х, = у \ х0 = У / х0=у. Указанные соотношения позволяют

сформулировать следующую теорему.

Для получения требуемого значения результата дизъюнкции или

конъюнкции при одном известном операнде, значение которого не про-

тиворечит значению заданной функции, другой операнд должен рав-

няться значению этой функции.

Выведенные формулы будут справедливы, если в них %! и х0

поменять местами.

22

Контрольные вопросы

1. Какая операция связывает истинное и ложное высказывания? Ка-

кими знаками они обозначаются?

2. Составьте таблицы истинности для трех основных логических опе-

раций.

3. В какой последовательности должны производиться логические опе-

рации?

4. Чем отличается дизъюнкция от обычного суммирования?

5. Поясните логические операции на диаграммах Эйлера.

6. Что представляет собой закон двойного отрицания?

7. На компьютере в системе Word определите значения NOT(FALSE),

NOT(O), NOT(TRUE), NOT(l), OR(0;0), OR(0;1), OR(l;l), AND(0;0),

AND(O;1), AND(1;1). Убедитесь в эквивалентности операций OR и MAX,

AND и MIN с включением символа неопределенности 14.

8. Как доказать закон ложного положения?

9. Объясните закон тавтологии.

10. Сформулируйте законы дополнительности.

11. В чем заключается смысл обратных логических операций?

12. Что такое переместительные законы?

13. Объясните сочетательные законы.

14. В чем заключается распределительный закон?

ГЛАВА 2

АНАЛИТИЧЕСКИЕ ФОРМЫ ПРЕДСТАВЛЕНИЯ

ЛОГИЧЕСКИХ ФУНКЦИЙ

2.1. Совершенная дизъюнктивная нормальная форма

СДНФ, называемая еще канонической, позволяет легко произ-

водить считывание в аналитическом виде функции, представлен-

ной в табличной форме. Правило, по которому выполняется это

представление, основано на теореме Шеннона, которая формули-

руется следующим образом: любую сколь угодно сложную логичес-

кую функцию т аргументов можно представить дизъюнкцией двух

конъюнкций, т. е.

У(хт-\, хт^, ... , xh ... , х„ х0) =

= Хт_2, - , 0, ... , Xb X0)-X,-V

vy(xm_l; xffl_2, ... , 1, ... , х„ Xo)-x,-. (2.1)

Справедливость этой теоремы устанавливается последователь-

ной подстановкой возможных значений переменной х,.

23

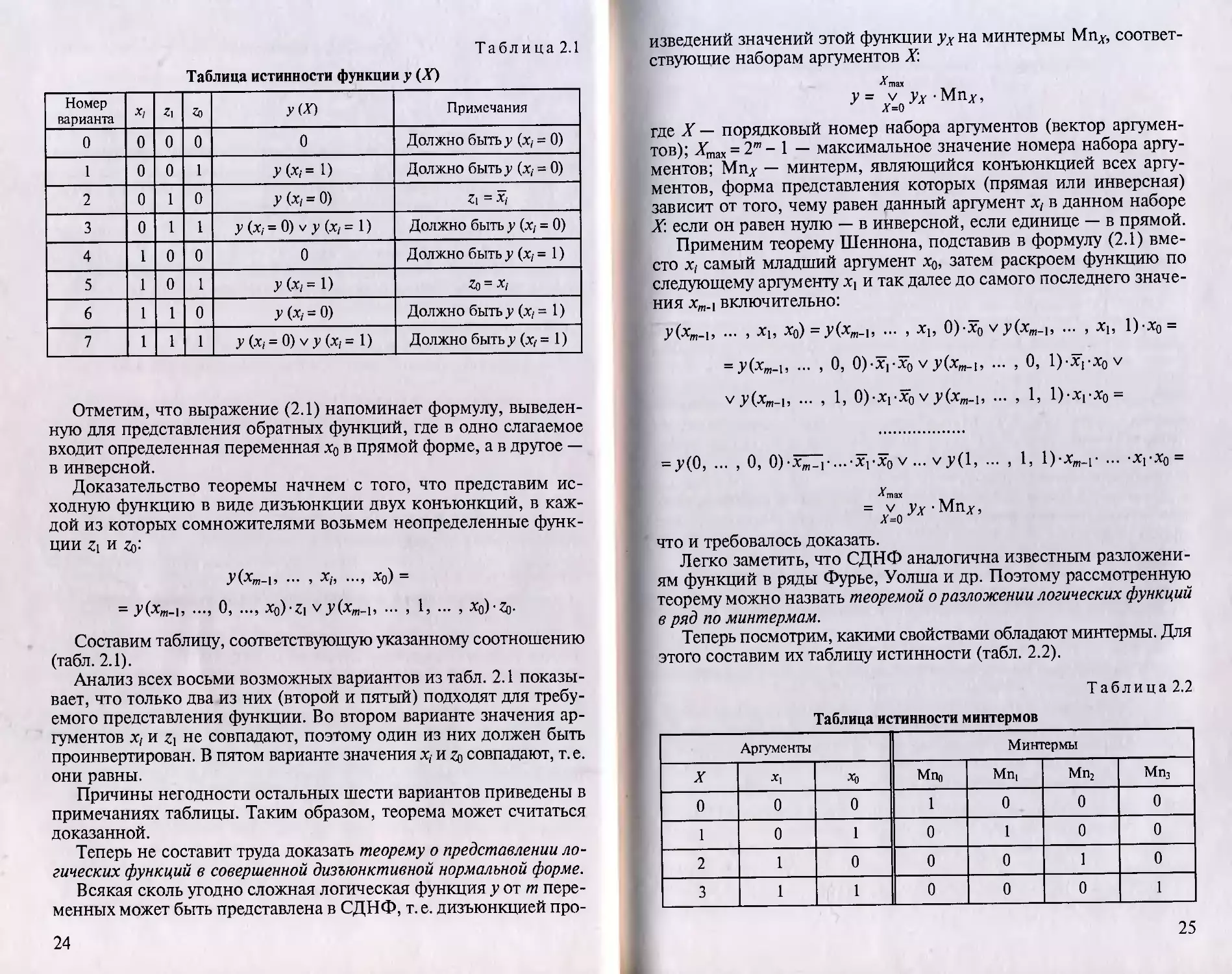

Таблица 2.1

Таблица истинности функции у (X)

Номер варианта xi Z} Zo У(Х) Примечания

0 0 0 0 0 Должно быть у (х,- = 0)

1 0 0 1 У (Х, = 1) ДОЛЖНО бЫТЬ у (Х; = 0)

2 0 1 0 У (Xi = 0) Z1 =Xi

3 0 1 1 у (х, = 0) v у (х, = 1) Должно быть у (Х/ = 0)

4 1 0 0 0 Должно быть у (х, = 1)

5 1 0 1 У(.Х;= 1) Zo = x,-

6 1 1 0 У (Xi = 0) Должно быть у (х,- = 1)

7 1 1 1 у (Xi = 0) V у (Х; = 1) Должно быть у (х,= 1)

Отметим, что выражение (2.1) напоминает формулу, выведен-

ную для представления обратных функций, где в одно слагаемое

входит определенная переменная х0 в прямой форме, а в другое —

в инверсной.

Доказательство теоремы начнем с того, что представим ис-

ходную функцию в виде дизъюнкции двух конъюнкций, в каж-

дой из которых сомножителями возьмем неопределенные функ-

ции Z\ и Zo-

у(хт-1, ... , xh ..., х0) =

= ..., О, ..., x0)-Zi vy(xm_,, ... , 1, ... , хь)-3).

Составим таблицу, соответствующую указанному соотношению

(табл. 2.1).

Анализ всех восьми возможных вариантов из табл. 2.1 показы-

вает, что только два из них (второй и пятый) подходят для требу-

емого представления функции. Во втором варианте значения ар-

гументов х,- и Zi не совпадают, поэтому один из них должен быть

проинвертирован. В пятом варианте значения х, и Zo совпадают, т.е.

они равны.

Причины негодности остальных шести вариантов приведены в

примечаниях таблицы. Таким образом, теорема может считаться

доказанной.

Теперь не составит труда доказать теорему о представлении ло-

гических функций в совершенной дизъюнктивной нормальной форме.

Всякая сколь угодно сложная логическая функция у от т пере-

менных может быть представлена в СДНФ, т. е. дизъюнкцией про-

24

изведений значений этой функции уд-на минтермы Мпд-, соответ-

ствующие наборам аргументов X:

X max

У = V Ух -Мпд-,

х=о

где X — порядковый номер набора аргументов (вектор аргумен-

тов); Хтт = 2й - 1 — максимальное значение номера набора аргу-

ментов; Мпд- — минтерм, являющийся конъюнкцией всех аргу-

ментов, форма представления которых (прямая или инверсная)

зависит от того, чему равен данный аргумент х, в данном наборе

X. если он равен нулю — в инверсной, если единице — в прямой.

Применим теорему Шеннона, подставив в формулу (2.1) вме-

сто Xj самый младший аргумент х0, затем раскроем функцию по

следующему аргументу Х| и так далее до самого последнего значе-

ния хт.\ включительно:

у(х„.,, ... , хь х0) =у(х„_„ ... , х„ О)-хо vy(x/n_„ ... , хь 1)-х0 =

= у(хт_,, ... , 0, O)-xrxo vy(xffl_b ... , 0, l)-xrxov

vy(xm_b ... , 1, O)-xrxovy(xm-i, ... , 1, 1)-х,-х0 =

= у(0, ... , 0, O)-xm_1-...-X]-xo V... vy(l, ... , 1, l)-xm_r ... •хгхь =

^max

= V Ух • МПд-,

х=о л

что и требовалось доказать.

Легко заметить, что СДНФ аналогична известным разложени-

ям функций в ряды Фурье, Уолша и др. Поэтому рассмотренную

теорему можно назвать теоремой о разложении логических функций

в ряд по минтермам.

Теперь посмотрим, какими свойствами обладают минтермы. Для

этого составим их таблицу истинности (табл. 2.2).

Таблица 2.2

Таблица истинности минтермов

Аргументы Минтермы

X х. хь Мпо Мп, Мп2 Мп3

0 0 0 1 0 0 0

1 0 1 0 1 0 0

2 1 0 0 0 1 0

3 1 1 0 0 0 1

25

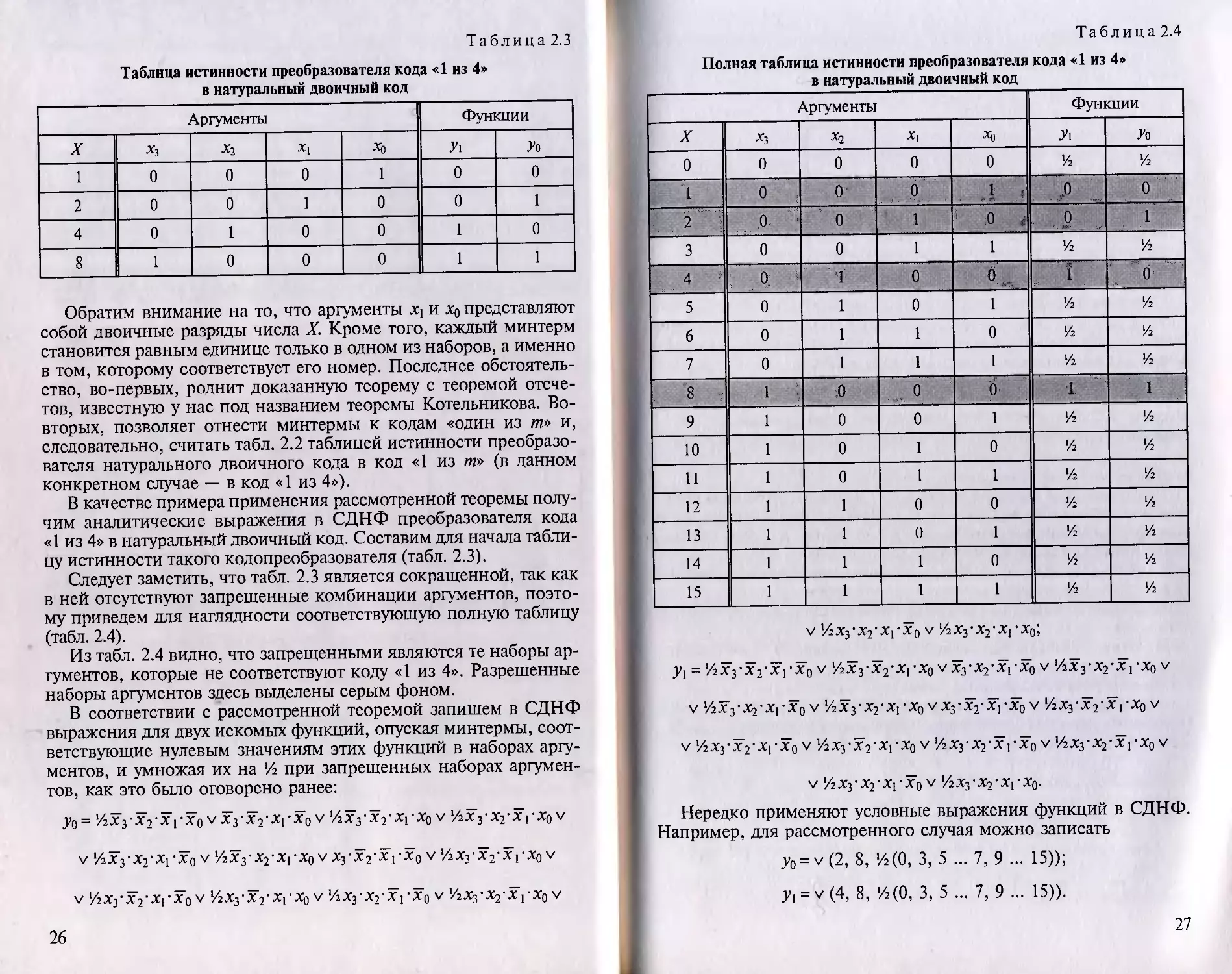

Таблица 2.3

Таблица истинности преобразователя кода «1 из 4»

в натуральный двоичный код

Аргументы Функции

X Xj X2 X! Хз Уо

1 0 0 0 1 0 0

2 0 0 1 0 0 1

4 0 1 0 0 1 0

8 1 0 0 0 1 1

Обратим внимание на то, что аргументы х( и х0 представляют

собой двоичные разряды числа X. Кроме того, каждый минтерм

становится равным единице только в одном из наборов, а именно

в том, которому соответствует его номер. Последнее обстоятель-

ство, во-первых, роднит доказанную теорему с теоремой отсче-

тов, известную у нас под названием теоремы Котельникова. Во-

вторых, позволяет отнести минтермы к кодам «один из т» и,

следовательно, считать табл. 2.2 таблицей истинности преобразо-

вателя натурального двоичного кода в код «1 из т» (в данном

конкретном случае — в код «1 из 4»).

В качестве примера применения рассмотренной теоремы полу-

чим аналитические выражения в СДНФ преобразователя кода

«1 из 4» в натуральный двоичный код. Составим для начала табли-

цу истинности такого кодопреобразователя (табл. 2.3).

Следует заметить, что табл. 2.3 является сокращенной, так как

в ней отсутствуют запрещенные комбинации аргументов, поэто-

му приведем для наглядности соответствующую полную таблицу

(табл. 2.4).

Из табл. 2.4 видно, что запрещенными являются те наборы ар-

гументов, которые не соответствуют коду «1 из 4». Разрешенные

наборы аргументов здесь выделены серым фоном.

В соответствии с рассмотренной теоремой запишем в СДНФ

выражения для двух искомых функций, опуская минтермы, соот-

ветствующие нулевым значениям этих функций в наборах аргу-

ментов, и умножая их на 'Л при запрещенных наборах аргумен-

тов, как это было оговорено ранее:

у0= /2Хз’Х2-Х1-хо v*3‘*2’xr*ov '/zXyXz'Xi-Xov

V '/iXj-XyXi-Xo V УгХуХуХ] -Xb V X3-X2-x\ -Xq v УгХз'^'Х^ХдУ

V yiXj-Xi'Xt’Xo V УгХуХу Xf Xq V '/гХз'Хг'Х^Хо V '/2X3-X2-X}-Xq V

26

Таблица 2.4

Полная таблица истинности преобразователя кода «1 из 4»

в натуральный двоичный код

Аргументы Функции

X х3 Х2 Х1 У1 Уо

0 0 0 0 0 !4 72

1 0 0 0 J л ,о..... 0

2 о ; 0 1 о < 0 Г

3 0 0 1 1 •/2 72

4 I 0 * 1 0 0 1 "о

5 0 1 0 1 !4 72

6 0 1 1 0 71 72

7 0 1 1 1 71 /2

8 1 0 z 0 0 1 1

9 1 0 0 1 /1 72

10 1 0 1 0 V1 72

И 1 0 1 1 72 72

12 1 1 0 0 72 72

13 1 1 0 1 72 72

14 1 1 1 0 72 72

15 1 1 1 1 72 72

V ,/2X3-X2‘XI-X0 V '/гХз-Хз'Х^Хо;

Ji = 'Лхз-хух^Хоv Тгхз-хухгхо vSyx/Xi’Xo v 72Хз-х2-Х! ’Хо v

V '/2X3-X2-Xl-X0 V '/гХз-Хз’Х^Хо VX3-X2-X|-Xo V ,/2X3-X2-Xi-XqV

V ,/2X3-X2-Xi‘X0 V У2Х3-Х2-Х1-Хо V ,/2Х3-Х2-Х1-Хо V ,/2Х3-Х2-Х1-Хо v

V '/2X3-X2-Xi-Xg V t/2X3-X2'XI-X0.

Нередко применяют условные выражения функций в СДНФ.

Например, для рассмотренного случая можно записать

y0 = v(2, 8, >/2(0, 3, 5 ... 7, 9 ... 15));

y, = v(4, 8, ‘Л(0, 3, 5 ... 7, 9 ... 15)).

27

В качестве другого примера применения рассмотренной теоре-

мы получим в СДНФ функцию, определенную дизъюнкцией. Из

табл. 1.3 имеем

у = X 1 • Хо v Xi -Хо v Х| -Хо-

Используя свойства дизъюнкции, можно перейти от СДНФ к

более коротким аналитическим выражениям.

В развитие закона ложного положения и в качестве следствия

теоремы о представлении логических функций в СДНФ можно

заключить, что инверсия отсчетов логической функции приводит

к инверсии самой функции:

Хщах _

У(Х) = у_оух -Мпа-.

Это свойство будем использовать в дальнейшем.

Следует отметить, что для представления логических функций

помимо СДНФ применяется (хотя и не часто) и совершенная конъ-

юнктивная нормальная форма (см. подразд. 2.3).

2.2. Сокращенные, тупиковые и минимальные

дизъюнктивные нормальные формы представления функций

Логические функции, представленные в СДНФ, удобны при

их считывании с таблиц истинности, однако в общем они гро-

моздки и для их сокращения используют методы минимизации.

Причем минимизацию проводят в три этапа, получая на пер-

вом этапе сокращенные функции, на втором — тупиковые и на

третьем — минимальные. Рассмотрим последовательно эти эта-

пы.

На первом этапе производится склеивание соседних минтер-

мов и импликант, на втором — исключение избыточных' импли-

кант, на третьем — выбор наименьшего варианта тупиковой фун-

кции, полученного в результате второго этапа.

Сопряженными1 2 (соседними, или смежными)3 являются минтер-

мы, отличающиеся только одной переменной (т.е. в один мин-

терм переменная х, входит в прямой форме, а в другой — в инвер-

сной). Например, если минтерм вектора аргументов X

1 Избыточными они называются потому, что в совокупности с другими мин-

термами и импликантами не оказывают никакого влияния на значения функции

при любых значениях ее аргументов.

2 Сопряженными они называются по аналогии с комплексными переменны-

ми, сумма которых при равенстве их мнимых составляющих по абсолютному

значению и различии только в знаках лишена мнимой составляющей.

3 Соседними, или смежными, они называются потому, что при внесении в

таблицу истинности кода Грея, их строки оказываются соседними.

28

МПу = X„.! Xffl_2•.• X,+I • x, Xi-1•• X| • Xb,

то сопряженным ему по переменной х, будет минтерм

М n/(z) = Xffl_j • хт_2 ... • Х,+1 X, -X,-! ... хг х0.

Дизъюнкция двух сопряженных минтермов (склеивание) при-

водит к образованию импликанты первого уровня — простой конъ-

юнкции, содержащей (т - 1) переменную:

МПу V Мп/(/) = Xm-i • Х„_2•.•• • Х/+1 • (X,-V X,) • ХМ •• X] • х0 =

= х„_гхт_2-... -х/+, •х/_| •... -xt -Хо= Imp//).

Аналогично осуществляется дальнейшая минимизация логи-

ческой функции путем поиска и склеивания сопряженных имп-

ликант первого, второго, третьего уровней и т.д.

В результате первого этапа минимизации могут образоваться

избыточные импликанты, которые необходимо исключить из со-

става логической функции, что и выполняется на втором этапе.

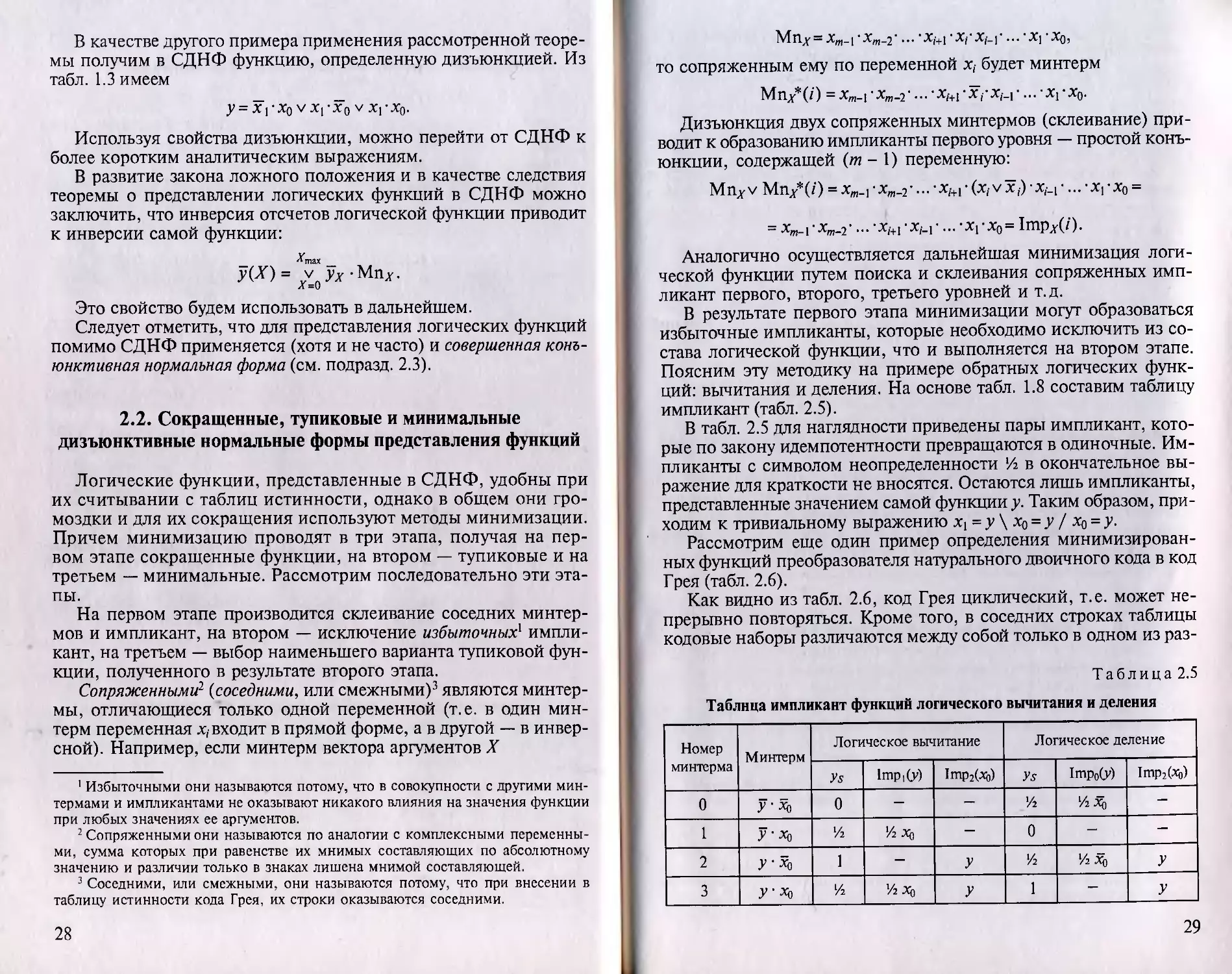

Поясним эту методику на примере обратных логических функ-

ций: вычитания и деления. На основе табл. 1.8 составим таблицу

импликант (табл. 2.5).

В табл. 2.5 для наглядности приведены пары импликант, кото-

рые по закону идемпотентности превращаются в одиночные. Им-

пликанты с символом неопределенности !/г в окончательное вы-

ражение для краткости не вносятся. Остаются лишь импликанты,

представленные значением самой функции у. Таким образом, при-

ходим к тривиальному выражению Xj = у \ х0 = у / х0 = у.

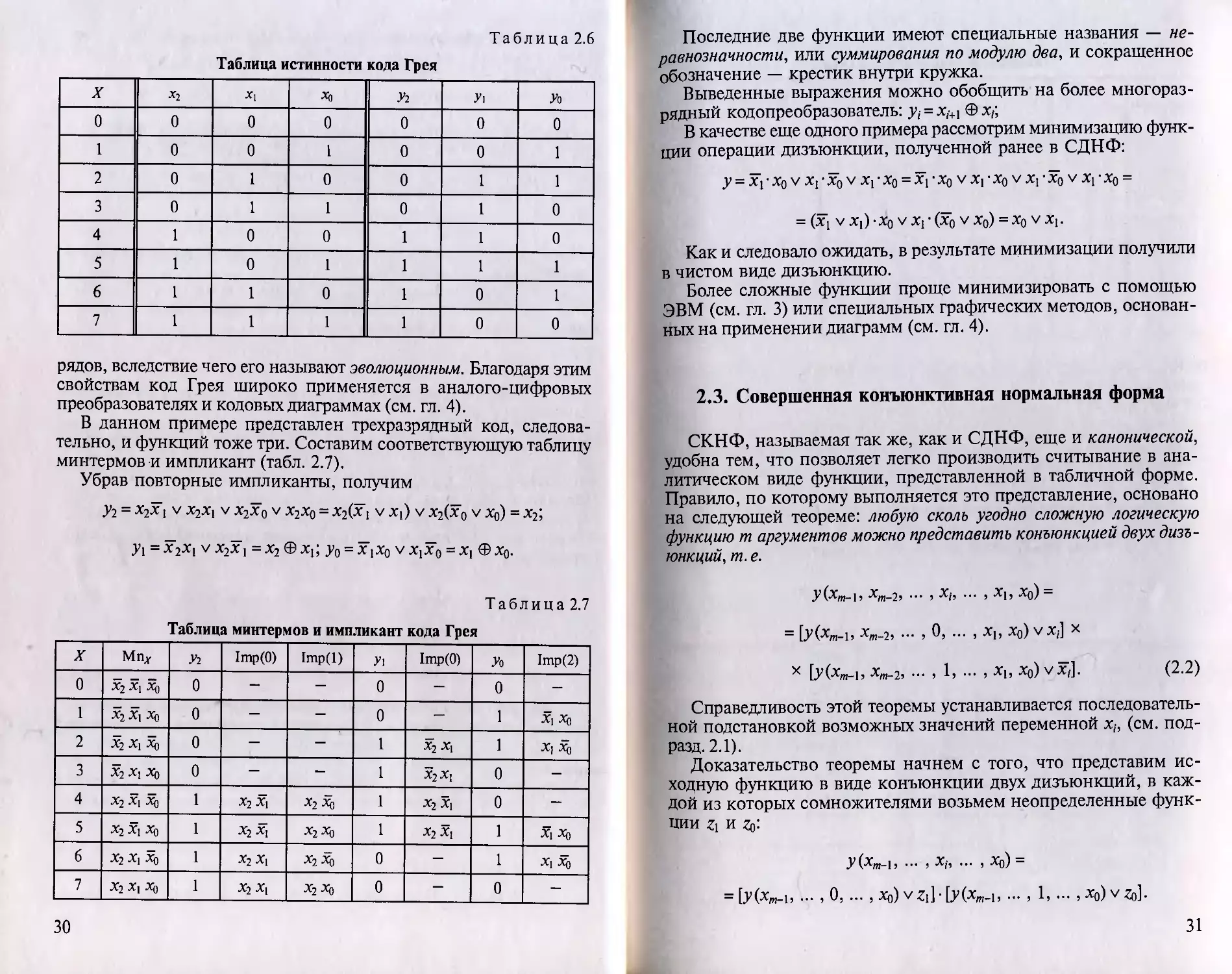

Рассмотрим еще один пример определения минимизирован-

ных функций преобразователя натурального двоичного кода в код

Г рея (табл. 2.6).

Как видно из табл. 2.6, код Грея циклический, т.е. может не-

прерывно повторяться. Кроме того, в соседних строках таблицы

кодовые наборы различаются между собой только в одном из раз-

Таблица 2.5

Таблица импликант функции логического вычитания и деления

Номер минтерма Минтерм Логическое вычитание Логическое деление

Уз Imp, (у) Imp^) Уз 1тро(у) 1тр2(хь)

0 0 — — '/2 '/гХо —

1 У-Хо ‘/2 '/2X3 — 0 — —

2 УЪ 1 — У !6 1/2Хо У

3 У-Хо !6 ’/гЛЬ У 1 — У

29

Таблица 2.6

Таблица истинности кода Грея

X *2 X X) У1 У1 Уо

0 0 0 0 0 0 0

1 0 0 1 0 0 1

2 0 1 0 0 1 1

3 0 1 1 0 1 0

4 1 0 0 1 1 0

5 1 0 1 1 1 1

6 1 1 0 1 0 1

7 1 1 1 1 0 0

рядов, вследствие чего его называют эволюционным. Благодаря этим

свойствам код Грея широко применяется в аналого-цифровых

преобразователях и кодовых диаграммах (см. гл. 4).

В данном примере представлен трехразрядный код, следова-

тельно, и функций тоже три. Составим соответствующую таблицу

минтермов и импликант (табл. 2.7).

Убрав повторные импликанты, получим

у2 = х2х! Vx2Xi V х2х0 V х2х0 = х2(х j Vх0 Vх2(х0 VХо) = х2;

У! = х2х, v х2х । = х2 ® Xjj у0 = X1Х0 v XiX0 = Xi © х0.

Таблица 2.7

Таблица минтермов и импликант кода Грея

X Мп,- У1 1тр(0) Imp(l) У1 1тр(0) Уо Imp(2)

0 Х2Х, X) 0 — — 0 — 0 —

1 Х2Х( Xfl 0 — — 0 — 1 X, Xfl

2 х2х, X) 0 — — 1 Х2 X, 1 X, X)

3 Х2Х, Хо 0 — — 1 Х2Х] 0 —

4 Х2Х, X) 1 Х2 Xi Х2Хд 1 Х2 Xj 0 —

5 Х2Х1 -У) 1 Х2Х1 Х2Хд 1 Х2 X, 1 Xi X)

6 Х2Х( X) 1 Х2 X, X2Xq 0 — 1 Xi Xi

7 Х2 Xi Хд 1 Х2 X! X2Xfl 0 — 0 —

30

Последние две функции имеют специальные названия — не-

равнозначности, или суммирования по модулю два, и сокращенное

обозначение — крестик внутри кружка.

Выведенные выражения можно обобщить на более многораз-

рядный кодопреобразователь: у( = х,+1 ®х(-;

В качестве еще одного примера рассмотрим минимизацию функ-

ции операции дизъюнкции, полученной ранее в СДНФ:

у = XfXo V X) -Хо V X, -Х0 = *Г-*0 v Х1 'х0 v •хГ*0 v *1 '*0 =

= (Х[ V Xi) -Х0 V X! (х0 V Хо) = хо V Хь

Как и следовало ожидать, в результате минимизации получили

в чистом виде дизъюнкцию.

Более сложные функции проще минимизировать с помощью

ЭВМ (см. гл. 3) или специальных графических методов, основан-

ных на применении диаграмм (см. гл. 4).

2.3. Совершенная конъюнктивная нормальная форма

СКНФ, называемая так же, как и СДНФ, еще и канонической,

удобна тем, что позволяет легко производить считывание в ана-

литическом виде функции, представленной в табличной форме.

Правило, по которому выполняется это представление, основано

на следующей теореме: любую сколь угодно сложную логическую

функцию т аргументов можно представить конъюнкцией двух дизъ-

юнкций, т. е.

У(хт-\, хт.2, , xh ... , х,, х0) =

= [у(*т-Ь хт-2, - , 0, - , *Ь) VX;] X

Х хт-2, ... , 1, ... , Xi, xo)vx,].

(2.2)

Справедливость этой теоремы устанавливается последователь-

ной подстановкой возможных значений переменной х,, (см. под-

разд. 2.1).

Доказательство теоремы начнем с того, что представим ис-

ходную функцию в виде конъюнкции двух дизъюнкций, в каж-

дой из которых сомножителями возьмем неопределенные функ-

ции Zi и Zo-

у(хтЧ, ... , Xi, ... , Xfl) =

= [y(xm_b ... , 0, ... ,Xo)vzi]-[y(xm_b ... , 1, ... ,x0)v^].

31

Табл и ц a 2.8

Таблица истинности функции у(.¥)

Номер варианта X/ 21 zo у(Х) Примечания

0 0 0 0 у (х,-= 0) • у (х,-= 1) ДОЛЖНО бЫТЬ у (Xj = 0)

1 0 0 1 У (х, = 0) Zi = xt

2 0 1 0 у(х, = 1) Должно быть у (х, = 0)

3 0 1 1 1 Должно бытьу (х,- = 0)

4 1 0 0 У(*/=0)-у (х,= 1) Должно бытьу (х, = 1)

5 1 0 1 У& = 1) Zo = Xi

6 1 1 0 у (х, = 0) Должно бытьу (х,- = 1)

7 1 1 1 1 Должно бытьу (X/ = 1)

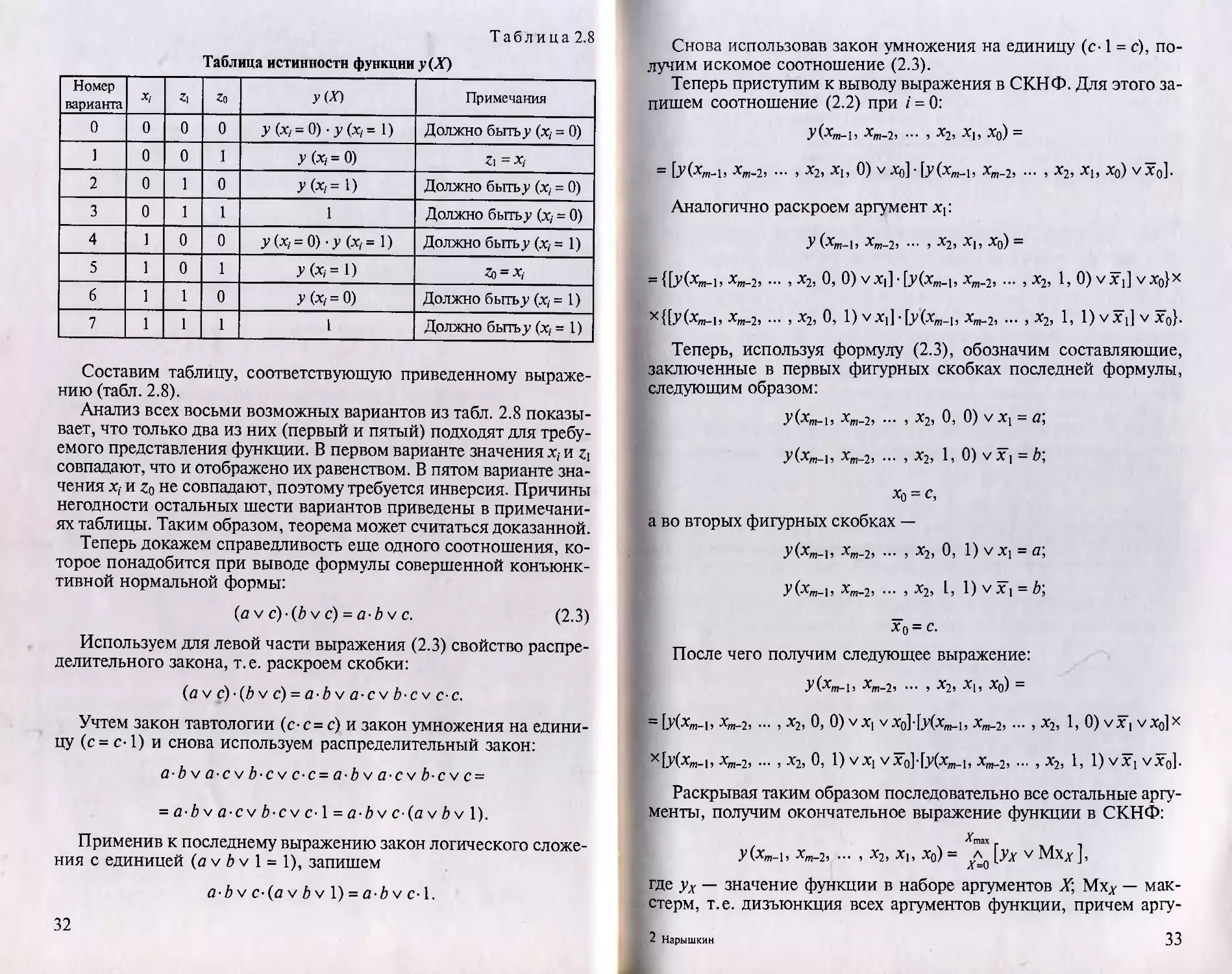

Составим таблицу, соответствующую приведенному выраже-

нию (табл. 2.8).

Анализ всех восьми возможных вариантов из табл. 2.8 показы-

вает, что только два из них (первый и пятый) подходят для требу-

емого представления функции. В первом варианте значения х, и Zi

совпадают, что и отображено их равенством. В пятом варианте зна-

чения х, и Zo не совпадают, поэтому требуется инверсия. Причины

негодности остальных шести вариантов приведены в примечани-

ях таблицы. Таким образом, теорема может считаться доказанной.

Теперь докажем справедливость еще одного соотношения, ко-

торое понадобится при выводе формулы совершенной конъюнк-

тивной нормальной формы:

(a v c)-(bv c) = a-bv с. (2.3)

Используем для левой части выражения (2.3) свойство распре-

делительного закона, т.е. раскроем скобки:

{a v с) • (b v с) = а• b v а- с v b• с v с-с.

Учтем закон тавтологии (с- с= с) и закон умножения на едини-

цу (с = с-1) и снова используем распределительный закон:

a-Z>va-cvZ>-cvc-c=o-Z>va-cv(>-cvc =

= «-Z>va-cvZ>-cvc-l = <2-Z>vc-(ovZ)vl).

Применив к последнему выражению закон логического сложе-

ния с единицей (avZ>vl = l), запишем

a-b v с-(a v b v 1) = a-b v с-1.

32

Снова использовав закон умножения на единицу (с -1 = с), по-

лучим искомое соотношение (2.3).

Теперь приступим к выводу выражения в СКНФ. Для этого за-

пишем соотношение (2.2) при i - 0:

jU»-b Х„_2, ... , Х2, Х\, Хо) =

= [у(х„-ь Хт-2, ... , Х2, Xi, 0) V Xq] • [у(х„_ь хт.2, ... , Х2, Xi, Хо) vx0].

Аналогично раскроем аргумент хь

y(xm_,, хт_2, ... , х2, х„ Хо) =

= {[yUm-1, хт.2, ... , х2, 0, 0) VX,]• [y(xm_b хт_2, ... , х2, 1, 0) vxj VX0}X

X{[y(xm_„ Xm_2, ... , X2, 0, 1) VXi]-[y(x„_1, xm-2, ... ,X2, 1, 1)VX!] vxo}.

Теперь, используя формулу (2.3), обозначим составляющие,

заключенные в первых фигурных скобках последней формулы,

следующим образом:

y(xm_i, хш_2, ... , х2, 0, 0) vX| = а;

у(х„_ь хт_2, ... , х2, 1, 0) vx, = Ь;

Хо = С,

а во вторых фигурных скобках —

у(хт-ь хт-2, - , х2, 0, 1) v х, = а;

y(xm_i, хт_2, ... , х2, I, 1) vx, = Ь',

х0 = с.

После чего получим следующее выражение:

?(*«-!, Хт_2, ... , Х2, X,, Х0) =

= [у(*т-ь хт-2,... , х2, 0, 0) V X] V х0]-[у(хт_1, Х„_2, ... , Х2, 1, 0) VX, vxq]x

xLyUn-b хт-2, ... , х2, 0, 1) VXJ vx0]-[y(^ffl-b Х„_2, ... , х2, 1, 1) vx, vx0].

Раскрывая таким образом последовательно все остальные аргу-

менты, получим окончательное выражение функции в СКНФ:

у(х„_1, хт_2, ... , х2, Xi, х0) = д [Ух v Mxj],

где ух — значение функции в наборе аргументов X; Мх^- — мак-

стерм, т.е. дизъюнкция всех аргументов функции, причем аргу-

2 Нарышкин

33

мент в прямой форме (х,), если в данном наборе Xон равен нулю,

и в инверсной форме (х,) — если он равен единице.

Теперь посмотрим, какими свойствами обладают макстермы.

Для этого составим их таблицу истинности (табл. 2.9).

Обратите внимание на то, что каждый макстерм становится

равным нулю только в одном из наборов, а именно в том, кото-

рому соответствует его номер. Это наблюдение позволяет сделать

вывод о взаимосвязи минтермов и макстермов: Mn^= Мх*-.

2.4. Представление функций с не полностью заданными

аргументами в дизъюнктивной нормальной форме

Бывают случаи, когда логическая функция представлена со-

кращенной таблицей истинности, и поэтому в некоторых ее стро-

ках отдельные аргументы оказываются заданными факультативно.

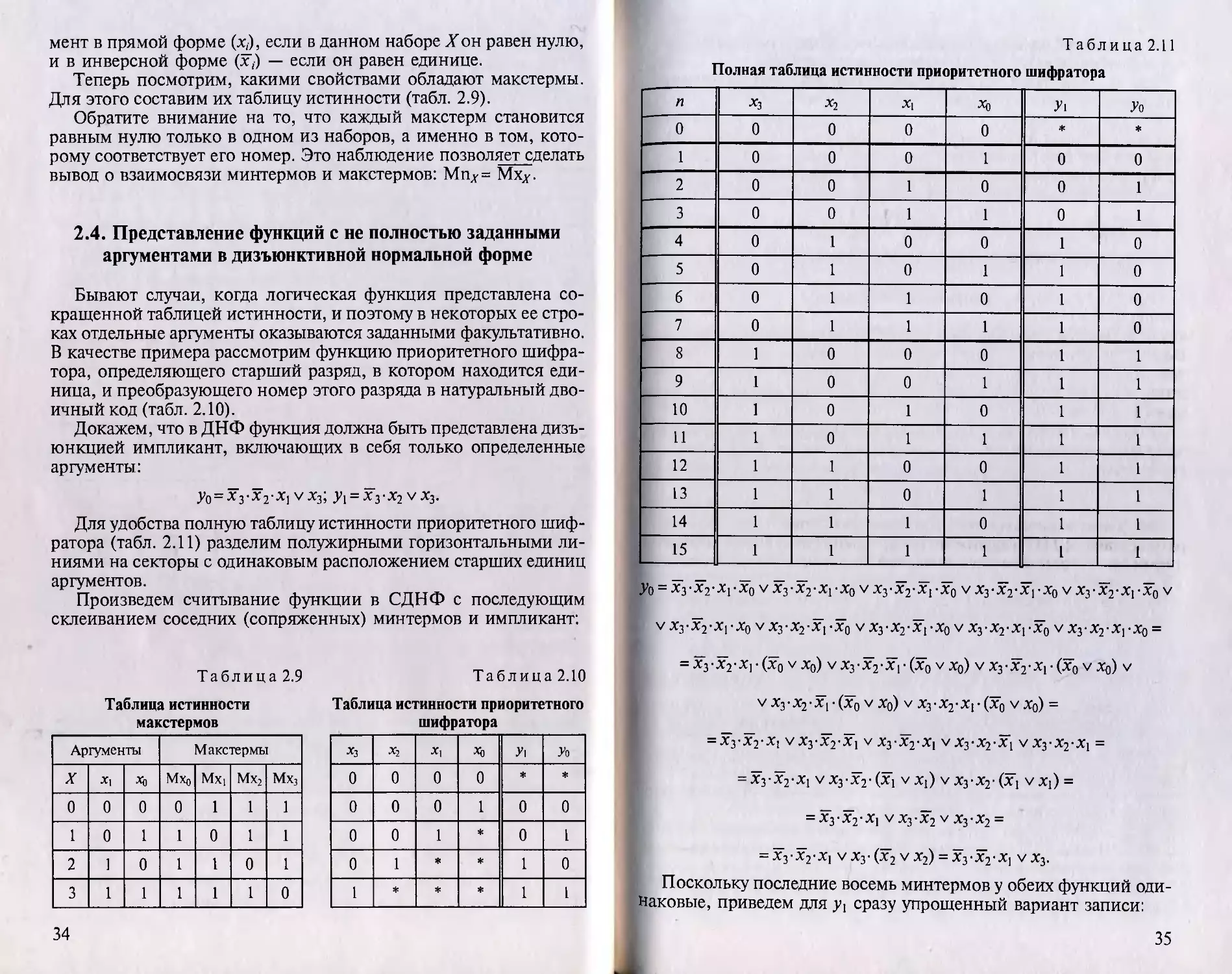

В качестве примера рассмотрим функцию приоритетного шифра-

тора, определяющего старший разряд, в котором находится еди-

ница, и преобразующего номер этого разряда в натуральный дво-

ичный код (табл. 2.10).

Докажем, что в ДНФ функция должна быть представлена дизъ-

юнкцией импликант, включающих в себя только определенные

аргументы:

Уо = Хз-х2-х1 vx3; У1 = Х3-Х? vx3.

Для удобства полную таблицу истинности приоритетного шиф-

ратора (табл. 2.11) разделим полужирными горизонтальными ли-

ниями на секторы с одинаковым расположением старших единиц

аргументов.

Произведем считывание функции в СДНФ с последующим

склеиванием соседних (сопряженных) минтермов и импликант:

Таблица 2.9

Таблица истинности

макстермов

Аргументы Макстермы

X *1 Мхо Мх, Мх2 Мх3

0 0 0 0 1 1 1

1 0 1 1 0 1 1

2 1 0 1 1 0 1

3 1 1 1 1 1 0

Таблица 2.10

Таблица истинности приоритетного

шифратора

*3 хг Х1 Уо

0 0 0 0 * *

0 0 0 1 0 0

0 0 1 * 0 1

0 1 * * 1 0

1 * * * 1 1

34

Таблица 2.11

Полная таблица истинности приоритетного шифратора

Л х3 х2 Х| Хз У1 Jo

0 0 0 0 0 * *

1 0 0 0 1 0 0

2 0 0 1 0 0 1

3 0 0 1 1 0 1

4 0 1 0 0 1 0

5 0 1 0 1 1 0

6 0 1 1 0 1 0

7 0 1 1 1 1 0

8 1 0 0 0 1 1

9 1 0 0 1 1 1

10 1 0 1 0 1 1

11 1 0 1 1 1 1

12 1 1 0 0 1 1

13 1 1 0 1 1 1

14 1 1 1 0 1 1

15 1 1 1 1 1 1

Уо = ХуХуХуХ0 V Ху Ху Ху Хо V ХуХуХуХц V ХуХуХ\-Хо V ХуХуХ[ -Хо v

VX3-X2-X|-X0 VX3-X2-X1-X0 VX3-X2-X1-X0 V Ху Ху Xy Xo vx3-x2-X|-x0 =

= XyXyXy(x0V Xo) VXyX2-Xy(X0V Xq) V XyXyXy (x0V Xo) V

VX3-X2-X|-(XO v Xq) V XyXyXy(X0 V Xo) =

= XyXyX{ VXj'XjXi V X3X2-Xi VX3-X2-Xi VX3-X2-X1 =

= X3-X2-Xj VX3-X2-(X] VX]) VX3-X2’(X| VX|) =

= XyXyX} VX3-X2 v X3'X2 =

= X3X2-X, vx3-(x2 VX2) = X3-X2’X| VXj.

Поскольку последние восемь минтермов у обеих функций оди-

наковые, приведем для у, сразу упрощенный вариант записи:

35

J1) = Х3-Х2-Х|-Хо V X3-X2-X|-Xq VX3-X2’XfX0 v Х3'Х2-Х|-ХО vx3 =

= X3-X2-Xt • (x0 V x0) V X3-X2-X| • (x0 V Xo) V x3 =

= XyX2 X\ VX3-X2-X1 V X3 =X3-X2-(X| V X|) vx3 = x3-x2 vx3.

Это и требовалось доказать.

Полученные выражения можно еще более упростить, если ис-

пользовать рассмотренный в гл. 1 прием:

ava-b = a-(\vb)vab = av a- bv a-b = av (a v а) -Ь = ач Ь.

Окончательно находим: у0 = х3 v х2-х,; J! = х3 v х2.

Контрольные вопросы

1. Что такое минтерм и каковы его свойства?

2. Как выражается логическая функция в СДНФ?

3. Что такое соседние минтермы?

4. Что такое импликанты и как они получаются?

5. Из каких этапов состоит процедура минимизации логических фун-

кций?

6. Как минимизировать функцию преобразователя кода «1 из 4» в на-

туральный двоичный код?

7. Сформулируйте и докажите теорему Шеннона о представлении ло-

гических функций дизъюнкцией двух конъюнкций.

8. Докажите теорему о представлении логических функций в СДНФ.

9. Составьте таблицу истинности для кода «1 из 4».

10. Составьте таблицу истинности для шифратора — преобразователя

кода «1 из 4» в натуральный двоичный код.

11. Запишите в СДНФ логическую функцию, соответствующую дизъ-

юнкции двух переменных.

12. Что называется сокращенной ДНФ?

13. Какая форма ДНФ называется тупиковой?

14. Какая ДНФ логической функции называется минимальной?

15. Составьте таблицу истинности кода Грея.

16. Запишите в СДНФ и минимизируйте разрядные функции кода

Грея.

17. Какая из четырех приведенных функций является минтермом:

1) х0 • X! v х2'Х3; 2) х0 v X| vx2v х3; 3) xo-xi-x2-x3; 4) хо v X] v х2 v х3?

18. Как влияет на сложность минимизированной функции наличие

запрещенных комбинаций (не влияет; упрощает; усложняет)?

19. Сформулируйте и докажите теорему о представлении логических

функций конъюнкцией двух дизъюнкций.

20. Докажите теорему о представлении логических функций в СКНФ.

21. Запишите в СКНФ логическую функцию, соответствующую конъ-

юнкции двух переменных.

22. Выведите функции для четырехразрядного преобразователя нату-

рального двоичного кода в код Грея.

36

23. По какому правилу можно представлять логическую функцию в

ДНФ, если в некоторых строках сокращенной таблицы истинности от-

дельные аргументы точно не заданы?

24. Выведите функции для четырехразрядного приоритетного шифра-

тора.

ГЛАВА 3

МИНИМИЗАЦИЯ ЛОГИЧЕСКИХ ФУНКЦИОНАЛОВ

С ПОМОЩЬЮ ЭВМ

3.1. Структура программы минимизации логического

функционала

Пусть требуется представить логический функционал Y(X), со-

стоящий из N логических функций yj (X), в минимальной дизъ-

юнктивно нормальной форме, с тем чтобы его было проще реа-

лизовать в виде устройства. Задача минимизации сводится в ко-

нечном счете к представлению функционала минимальным чис-

лом наиболее простых конъюнкций — импликант.

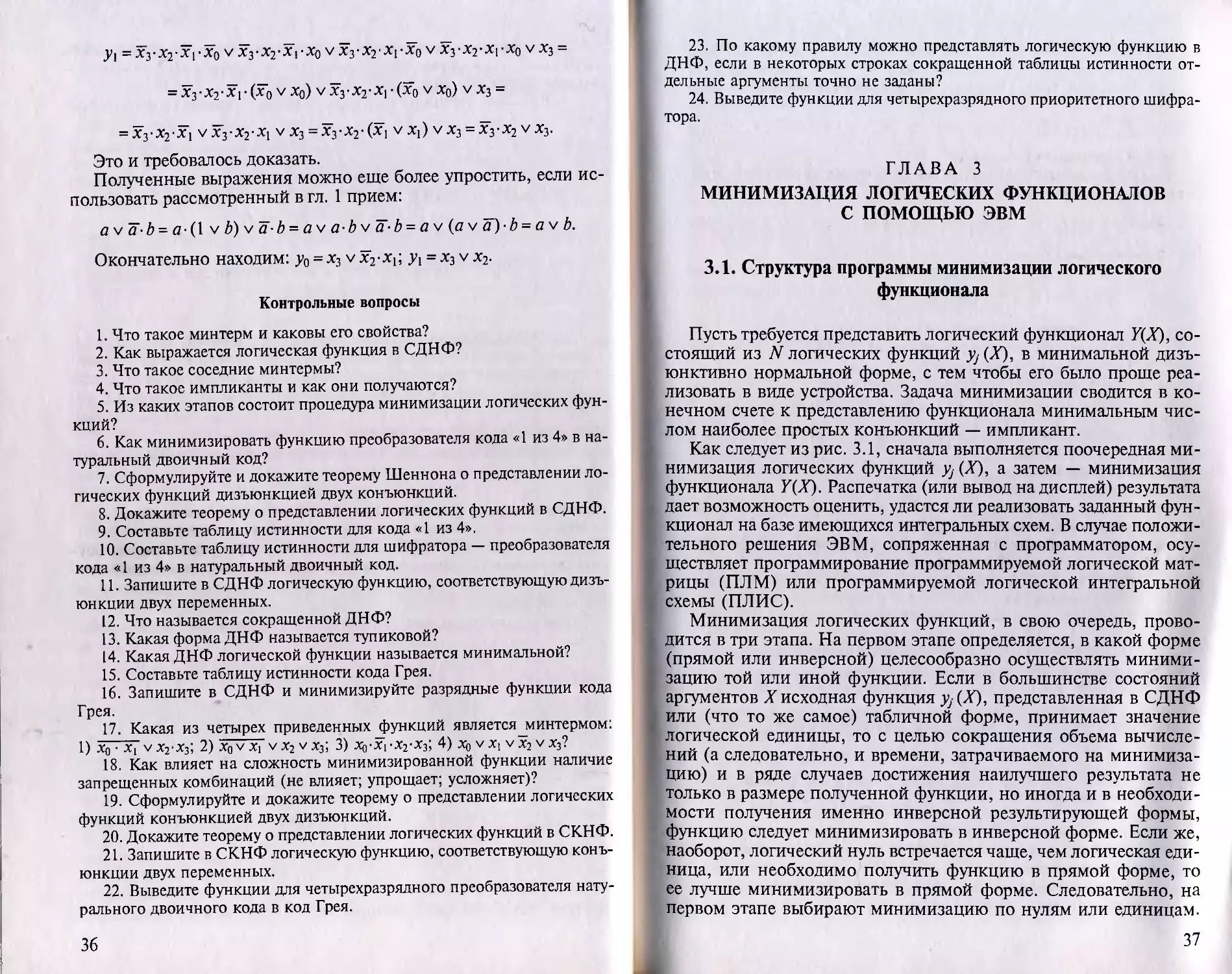

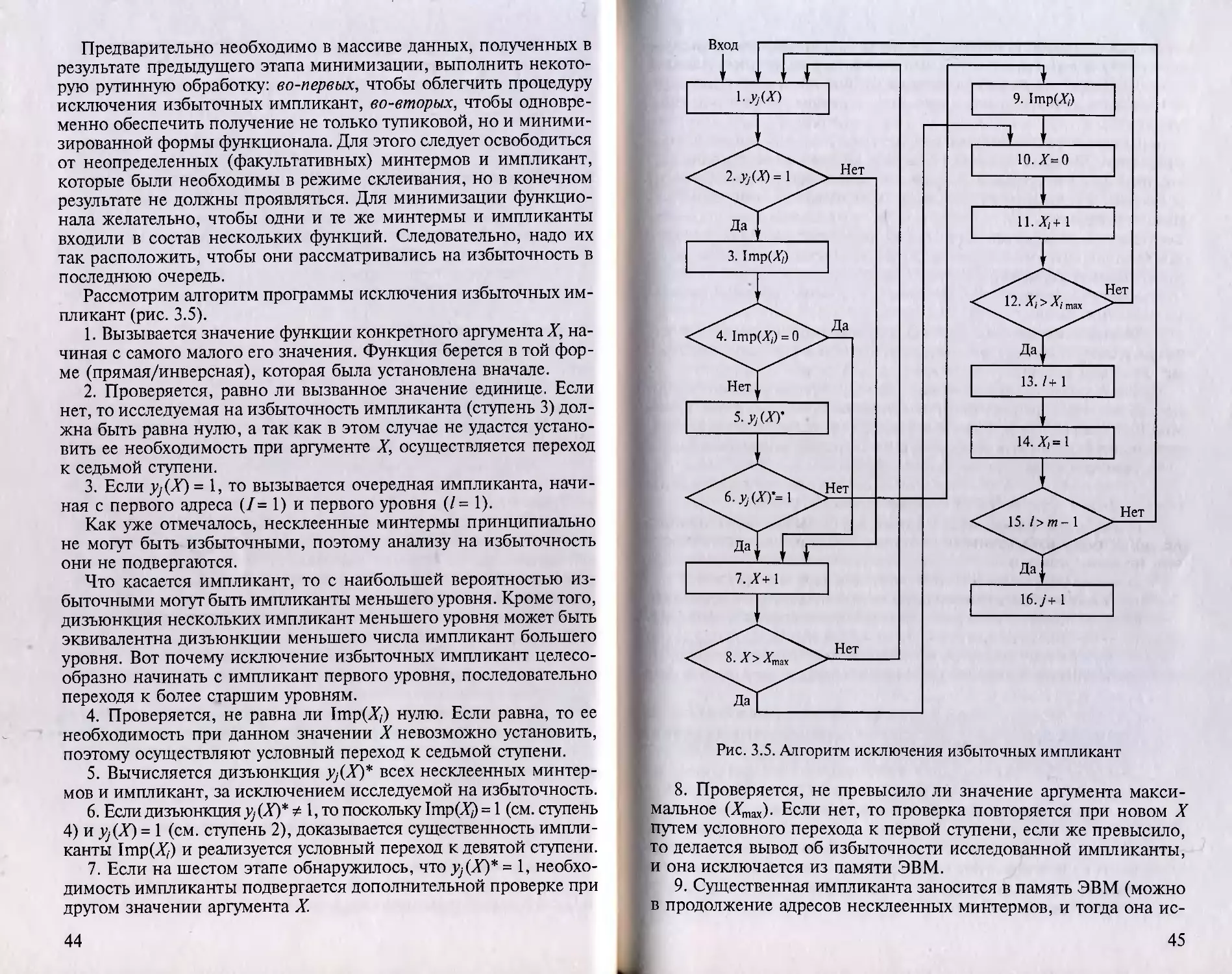

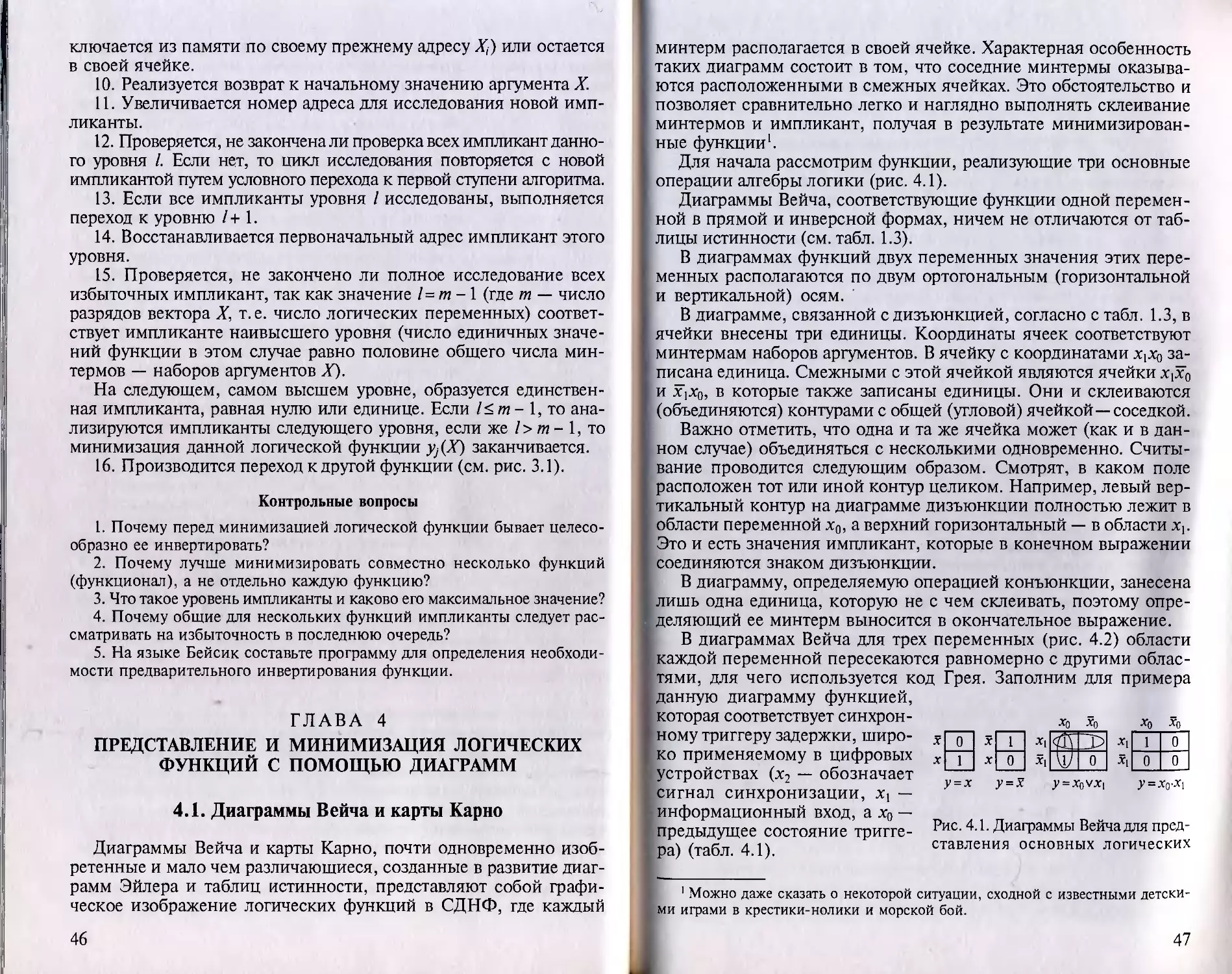

Как следует из рис. 3.1, сначала выполняется поочередная ми-

нимизация логических функций (X), а затем — минимизация

функционала Y(X). Распечатка (или вывод на дисплей) результата

дает возможность оценить, удастся ли реализовать заданный фун-

кционал на базе имеющихся интегральных схем. В случае положи-

тельного решения ЭВМ, сопряженная с программатором, осу-

ществляет программирование программируемой логической мат-

рицы (ПЛМ) или программируемой логической интегральной

схемы (ПЛИС).

Минимизация логических функций, в свою очередь, прово-

дится в три этапа. На первом этапе определяется, в какой форме

(прямой или инверсной) целесообразно осуществлять миними-

зацию той или иной функции. Если в большинстве состояний

аргументов X исходная функция у,(Х), представленная в СДНФ

или (что то же самое) табличной форме, принимает значение

логической единицы, то с целью сокращения объема вычисле-

ний (а следовательно, и времени, затрачиваемого на минимиза-

цию) и в ряде случаев достижения наилучшего результата не

только в размере полученной функции, но иногда и в необходи-

мости получения именно инверсной результирующей формы,

функцию следует минимизировать в инверсной форме. Если же,

наоборот, логический нуль встречается чаще, чем логическая еди-

ница, или необходимо получить функцию в прямой форме, то

ее лучше минимизировать в прямой форме. Следовательно, на

первом этапе выбирают минимизацию по нулям или единицам.

37

Вызов yj

Минимизация

7+1

Минимизация

функционала

Представление

результата

Принятие

решения

Программирование

Рис. 3.1. Блок-схема ал-

горитма автоматическо-

го программирования

ПЛМ и ПЛИС с пред-

варительной минимиза-

цией логического функ-

ционала

Рис. 3.2. Этапы минимизации логического

функционала

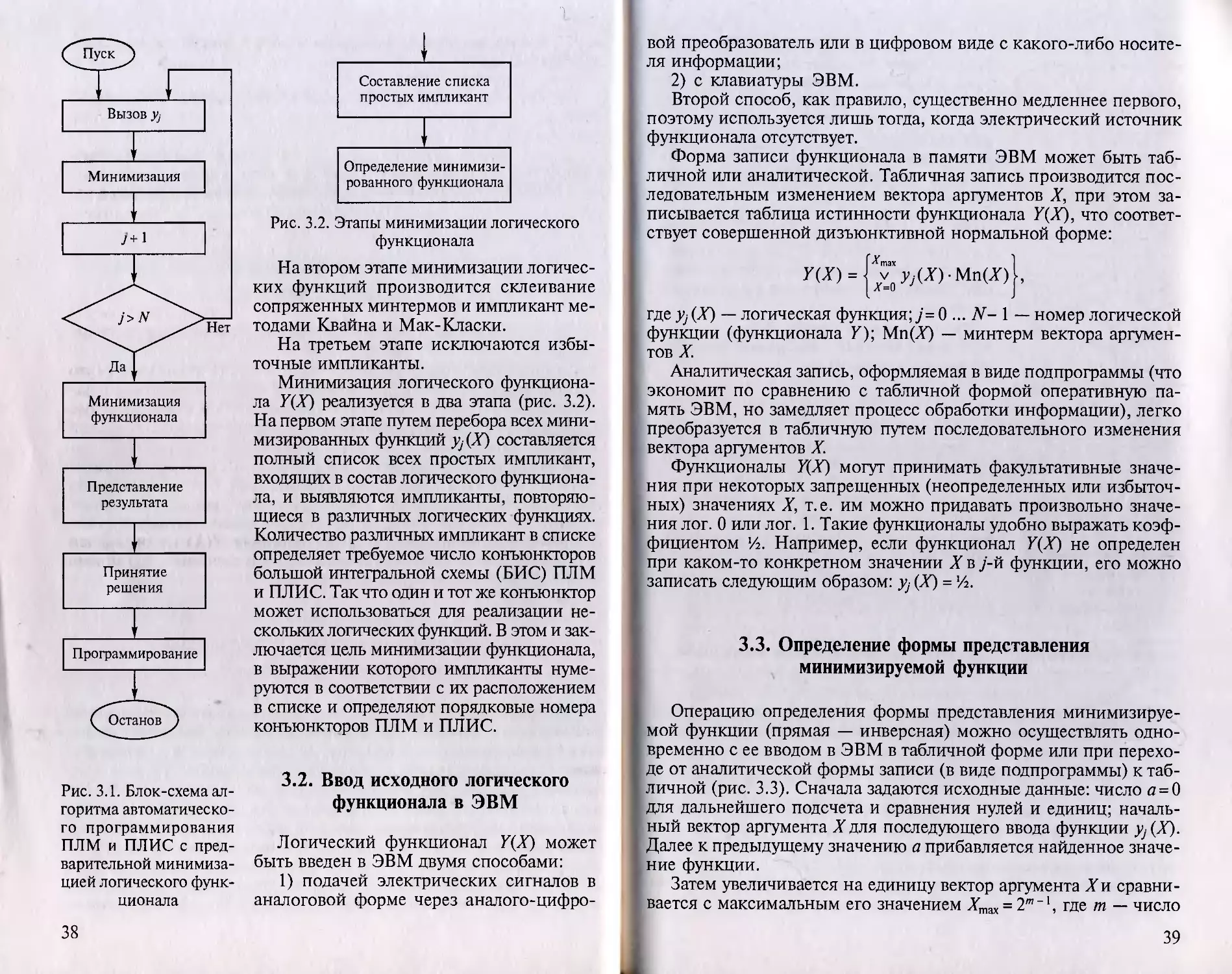

На втором этапе минимизации логичес-

ких функций производится склеивание

сопряженных минтермов и импликант ме-

тодами Квайна и Мак-Класки.

На третьем этапе исключаются избы-

точные импликанты.

Минимизация логического функциона-

ла Y(X) реализуется в два этапа (рис. 3.2).

На первом этапе путем перебора всех мини-

мизированных функций yj(X) составляется

полный список всех простых импликант,

входящих в состав логического функциона-

ла, и выявляются импликанты, повторяю-

щиеся в различных логических функциях.

Количество различных импликант в списке

определяет требуемое число конъюнкгоров

большой интегральной схемы (БИС) ПЛМ

и ПЛИС. Так что один и тот же конъюнктор

может использоваться для реализации не-

скольких логических функций. В этом и зак-

лючается цель минимизации функционала,

в выражении которого импликанты нуме-

руются в соответствии с их расположением

в списке и определяют порядковые номера

конъюнкторов ПЛМ и ПЛИС.

3.2. Ввод исходного логического

функционала в ЭВМ

Логический функционал Y(X) может

быть введен в ЭВМ двумя способами:

1) подачей электрических сигналов в

аналоговой форме через аналого-цифро-

38

вой преобразователь или в цифровом виде с какого-либо носите-

ля информации;

2) с клавиатуры ЭВМ.

Второй способ, как правило, существенно медленнее первого,

поэтому используется лишь тогда, когда электрический источник

функционала отсутствует.

Форма записи функционала в памяти ЭВМ может быть таб-

личной или аналитической. Табличная запись производится пос-

ледовательным изменением вектора аргументов X, при этом за-

писывается таблица истинности функционала Y(X), что соответ-

ствует совершенной дизъюнктивной нормальной форме:

{^тах |

где у} (X) — логическая функция; j= 0 ... N- 1 — номер логической

функции (функционала У); Мп (У) — минтерм вектора аргумен-

тов X.

Аналитическая запись, оформляемая в виде подпрограммы (что

экономит по сравнению с табличной формой оперативную па-

мять ЭВМ, но замедляет процесс обработки информации), легко

преобразуется в табличную путем последовательного изменения

вектора аргументов X.

Функционалы Y(X) могут принимать факультативные значе-

ния при некоторых запрещенных (неопределенных или избыточ-

ных) значениях X, т.е. им можно придавать произвольно значе-

ния лог. О или лог. 1. Такие функционалы удобно выражать коэф-

фициентом !4. Например, если функционал Y(X) не определен

при каком-то конкретном значении X в у-й функции, его можно

записать следующим образом: уу- (JQ = !4.

3.3. Определение формы представления

минимизируемой функции

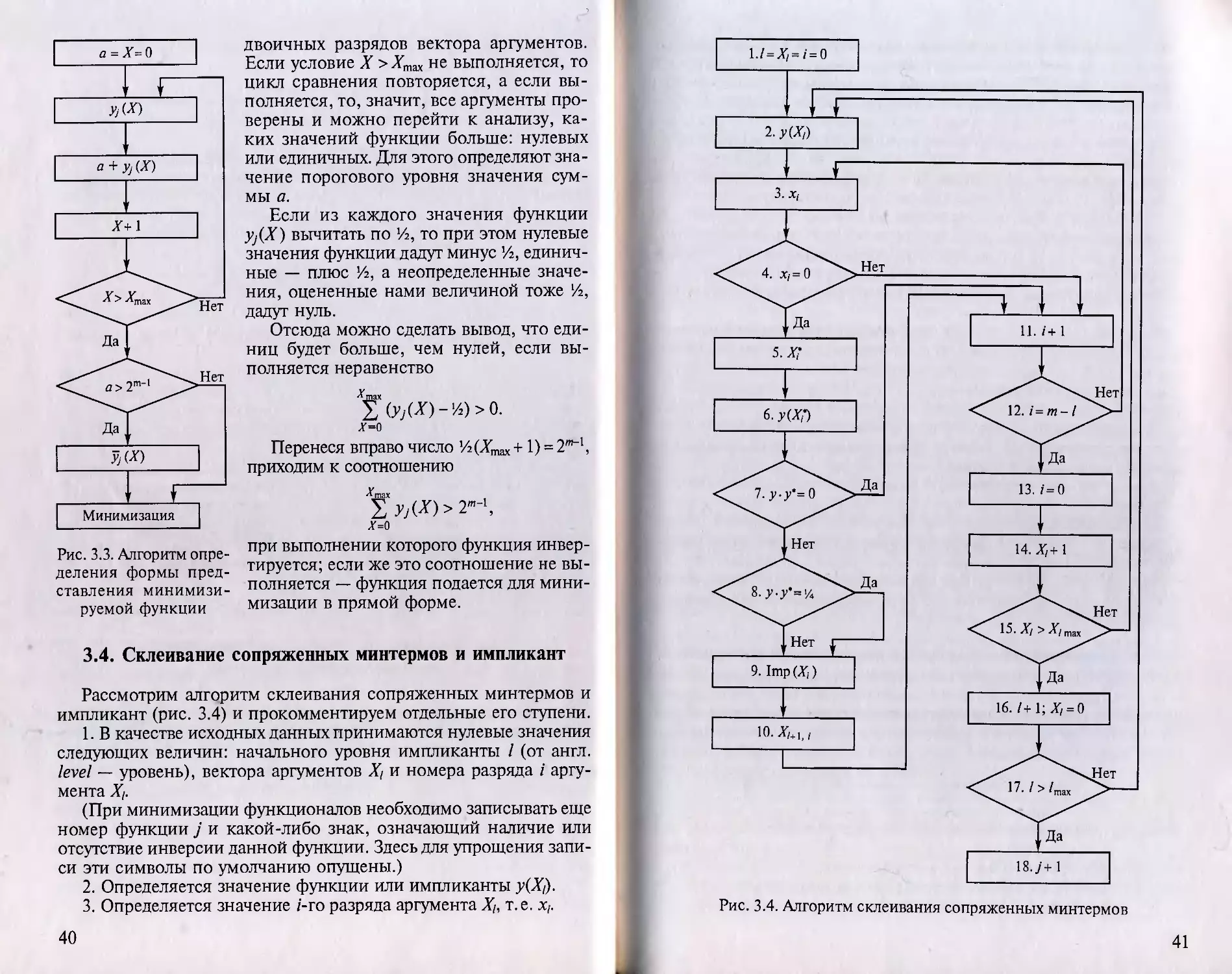

Операцию определения формы представления минимизируе-

мой функции (прямая — инверсная) можно осуществлять одно-

временно с ее вводом в ЭВМ в табличной форме или при перехо-

де от аналитической формы записи (в виде подпрограммы) к таб-

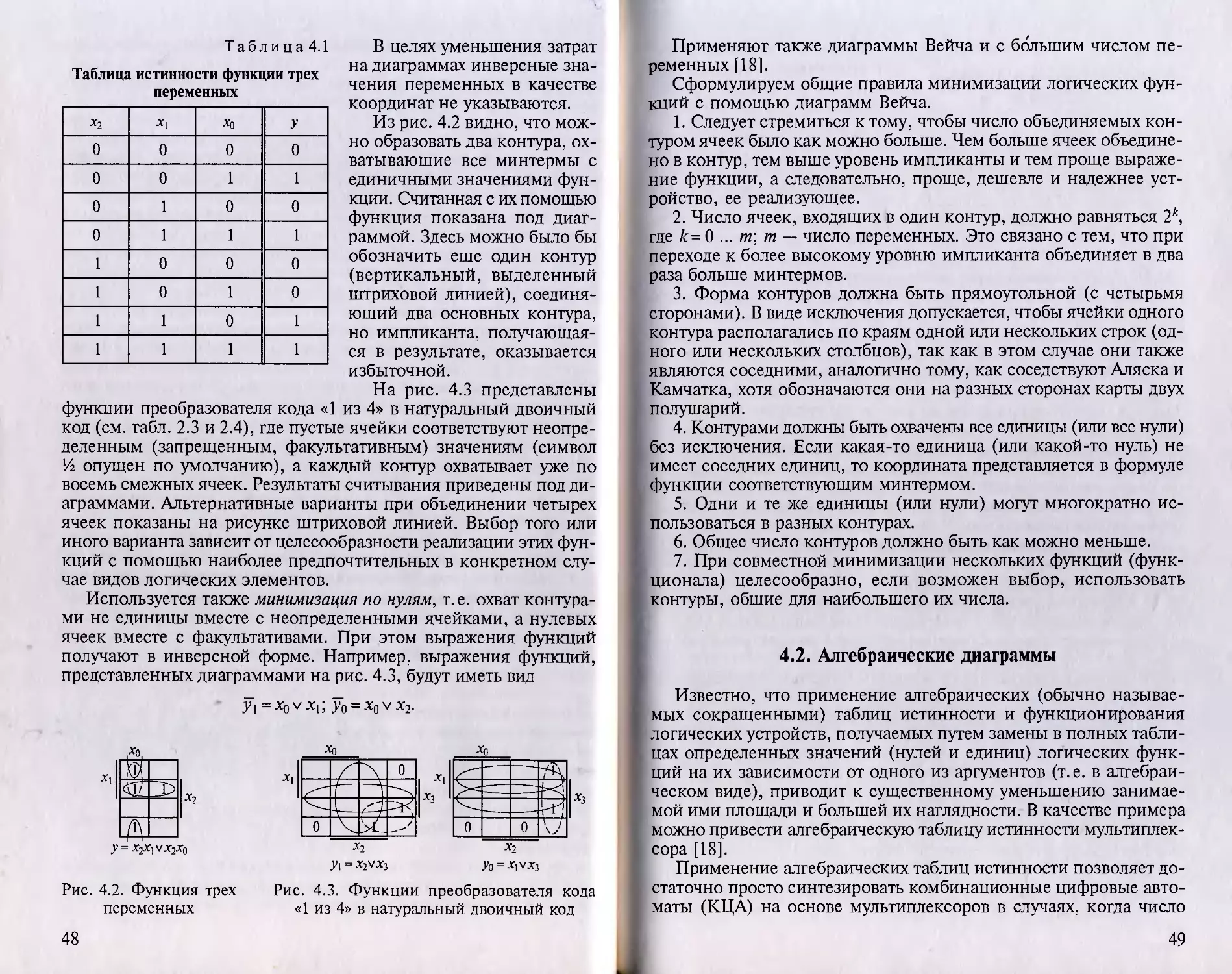

личной (рис. 3.3). Сначала задаются исходные данные: число а = 0

для дальнейшего подсчета и сравнения нулей и единиц; началь-

ный вектор аргумента А'для последующего ввода функции у;(Х).

Далее к предыдущему значению а прибавляется найденное значе-

ние функции.

Затем увеличивается на единицу вектор аргумента Xи сравни-

вается с максимальным его значением Хтзх = 2т~', где т — число

39

Рис. 3.3. Алгоритм опре-

деления формы пред-

ставления минимизи-

руемой функции

двоичных разрядов вектора аргументов.

Если условие X > Хтах не выполняется, то

цикл сравнения повторяется, а если вы-

полняется, то, значит, все аргументы про-

верены и можно перейти к анализу, ка-

ких значений функции больше: нулевых

или единичных. Для этого определяют зна-

чение порогового уровня значения сум-

мы а.

Если из каждого значения функции

y/JV) вычитать по !4, то при этом нулевые

значения функции дадут минус ’Л, единич-

ные — плюс ’/г, а неопределенные значе-

ния, оцененные нами величиной тоже ‘Л,

дадут нуль.

Отсюда можно сделать вывод, что еди-

ниц будет больше, чем нулей, если вы-

полняется неравенство

^тах

Х(у7(^)-Ю>0.

х=о

Перенеся вправо число }А(Хтах^ l) = 2m"1,

приходим к соотношению

^тах

S Уу(Х)> 2—1,

лг=о

при выполнении которого функция инвер-

тируется; если же это соотношение не вы-

полняется — функция подается для мини-

мизации в прямой форме.

3.4. Склеивание сопряженных минтермов и импликант

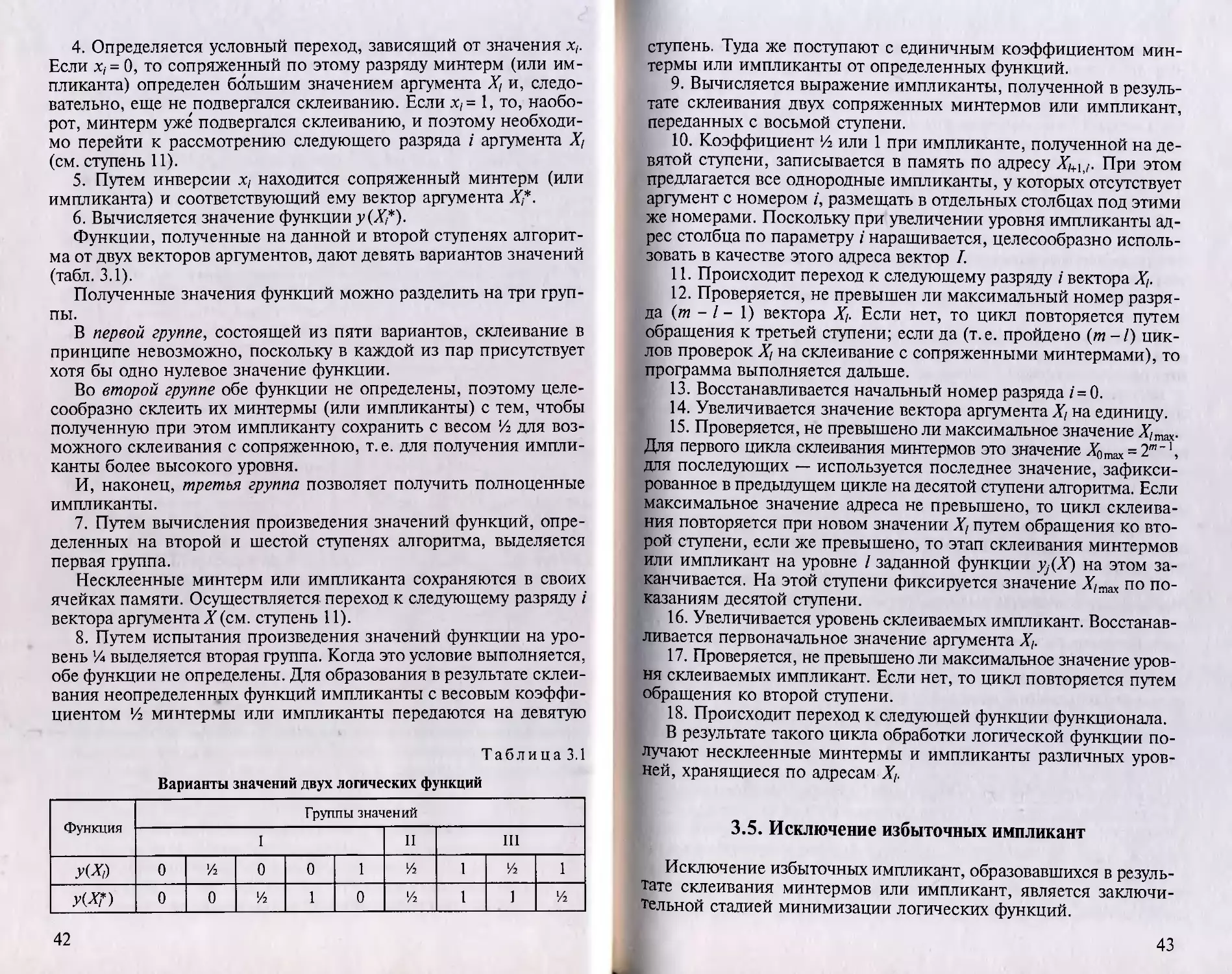

Рассмотрим алгоритм склеивания сопряженных минтермов и

импликант (рис. 3.4) и прокомментируем отдельные его ступени.

1. В качестве исходных данных принимаются нулевые значения

следующих величин: начального уровня импликанты / (от англ.

level — уровень), вектора аргументов Xt и номера разряда i аргу-

мента Xt.

(При минимизации функционалов необходимо записывать еще

номер функции j и какой-либо знак, означающий наличие или

отсутствие инверсии данной функции. Здесь для упрощения запи-

си эти символы по умолчанию опущены.)

2. Определяется значение функции или импликанты у(А)).

3. Определяется значение z-го разряда аргумента Xt, т.е. х,.

40

l.Z=A7= Z= О

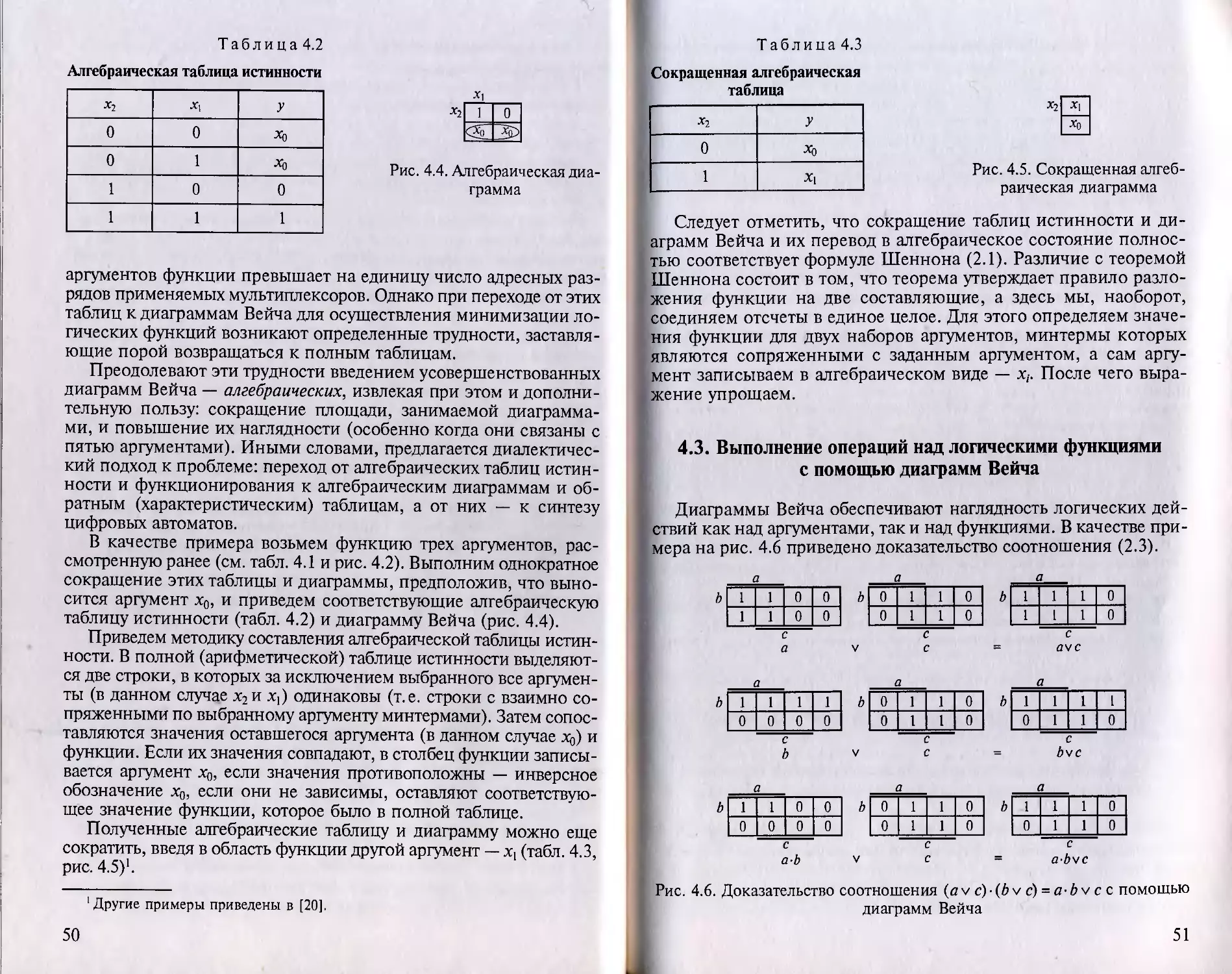

Рис. 3.4. Алгоритм склеивания сопряженных минтермов

41

4. Определяется условный переход, зависящий от значения х,.

Если х, = 0, то сопряженный по этому разряду минтерм (или им-

пликанта) определен большим значением аргумента X/ и, следо-

вательно, еще не подвергался склеиванию. Если х, = 1, то, наобо-

рот, минтерм уже подвергался склеиванию, и поэтому необходи-

мо перейти к рассмотрению следующего разряда i аргумента А)

(см. ступень 11).

5. Путем инверсии х, находится сопряженный минтерм (или

импликанта) и соответствующий ему вектор аргумента X*.

6. Вычисляется значение функции у (XX)

Функции, полученные на данной и второй ступенях алгорит-

ма от двух векторов аргументов, дают девять вариантов значений

(табл. 3.1).

Полученные значения функций можно разделить на три груп-

пы.

В первой группе, состоящей из пяти вариантов, склеивание в

принципе невозможно, поскольку в каждой из пар присутствует

хотя бы одно нулевое значение функции.

Во второй группе обе функции не определены, поэтому целе-

сообразно склеить их минтермы (или импликанты) с тем, чтобы

полученную при этом импликанту сохранить с весом !4 для воз-

можного склеивания с сопряженною, т. е. для получения импли-

канты более высокого уровня.

И, наконец, третья группа позволяет получить полноценные

импликанты.

7. Путем вычисления произведения значений функций, опре-

деленных на второй и шестой ступенях алгоритма, выделяется

первая группа.

Несклеенные минтерм или импликанта сохраняются в своих

ячейках памяти. Осуществляется переход к следующему разряду z

вектора аргумента X (см. ступень 11).

8. Путем испытания произведения значений функции на уро-

вень % выделяется вторая группа. Когда это условие выполняется,

обе функции не определены. Для образования в результате склеи-

вания неопределенных функций импликанты с весовым коэффи-

циентом ‘/г минтермы или импликанты передаются на девятую

Таблица 3.1

Варианты значений двух логических функций

Функция Группы значений

I II III

У(Х/) 0 */2 0 0 1 !6 1 ‘/2 1

у(хп 0 0 ‘/2 1 0 ‘/2 1 1 ‘/2

42

ступень. Туда же поступают с единичным коэффициентом мин-

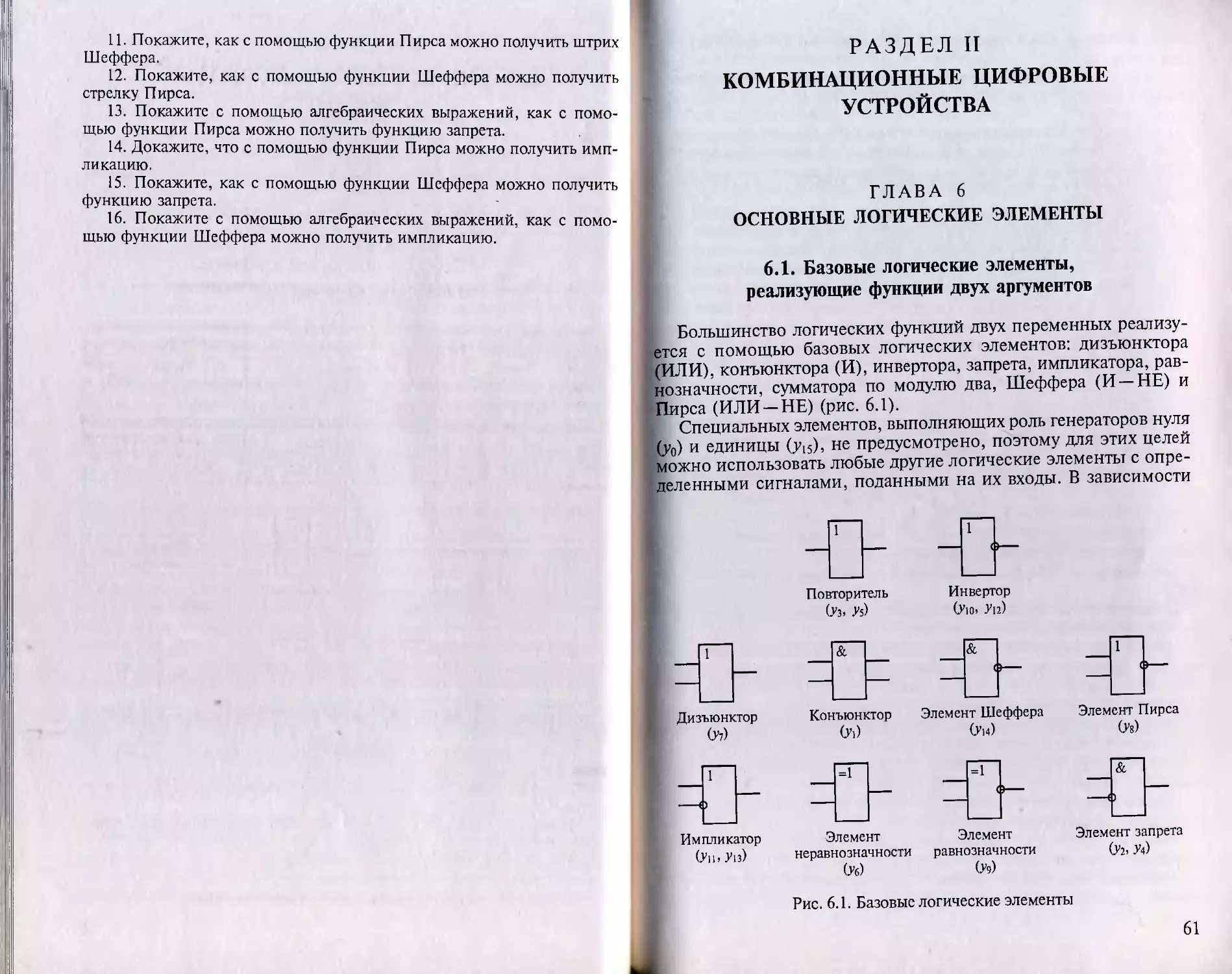

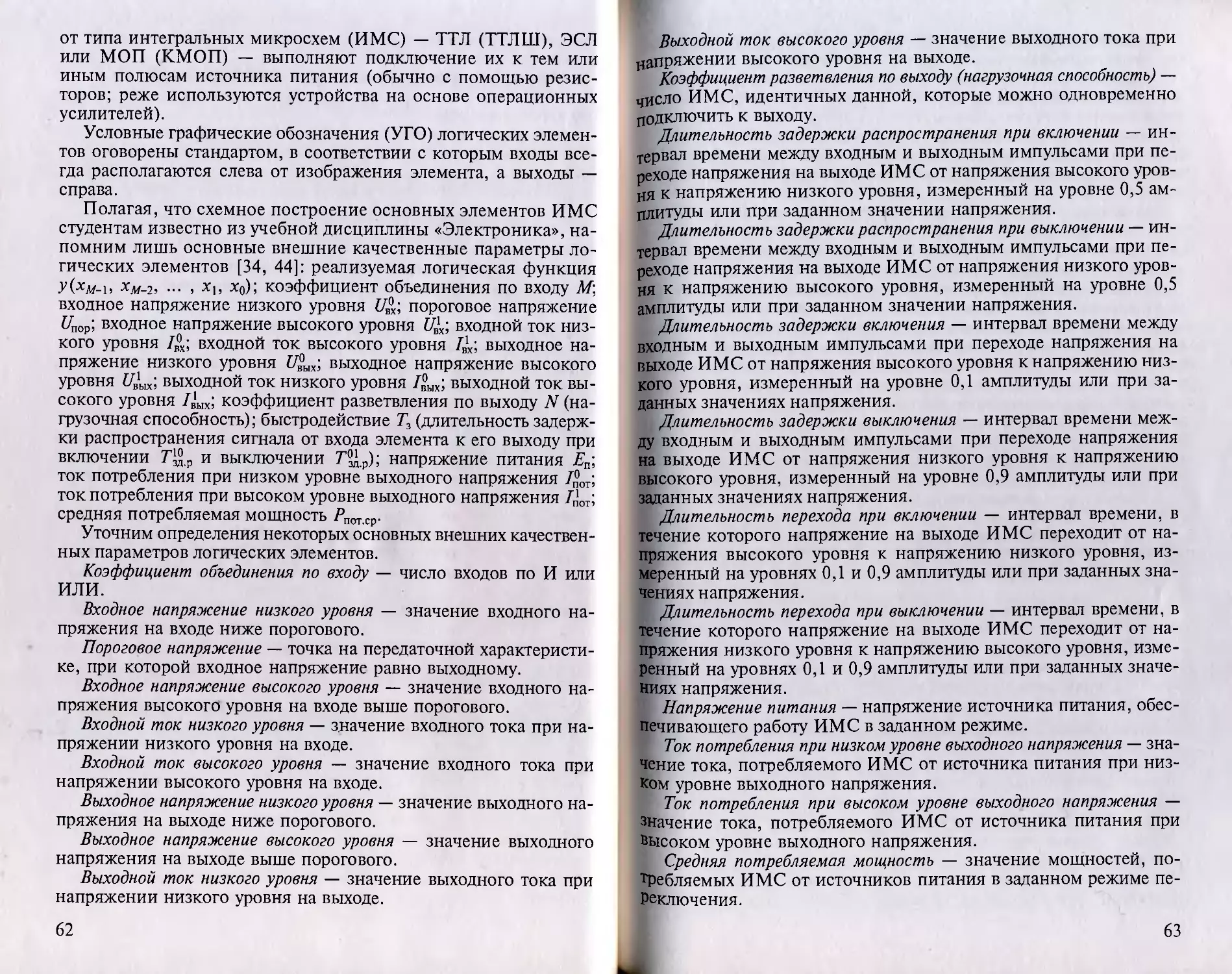

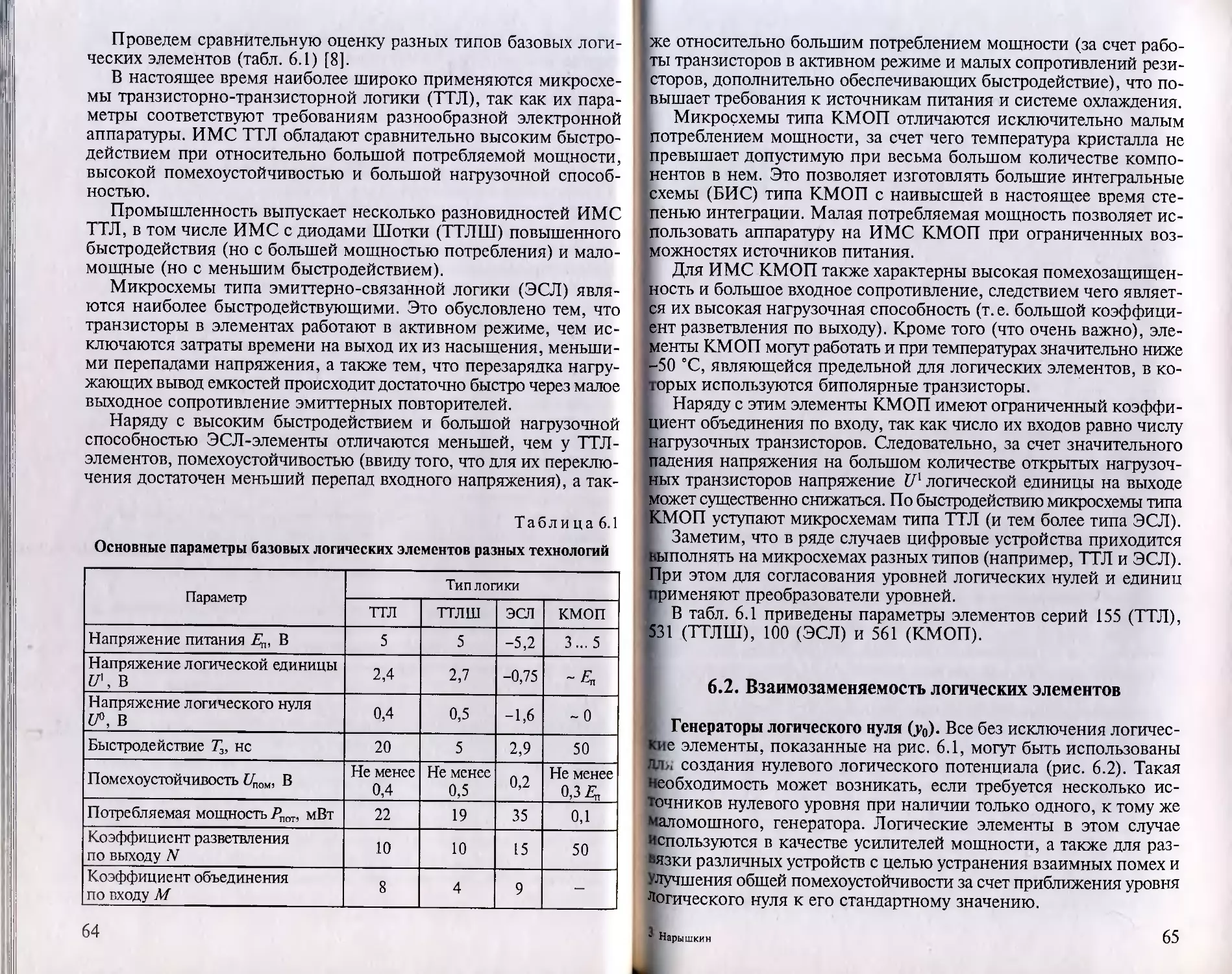

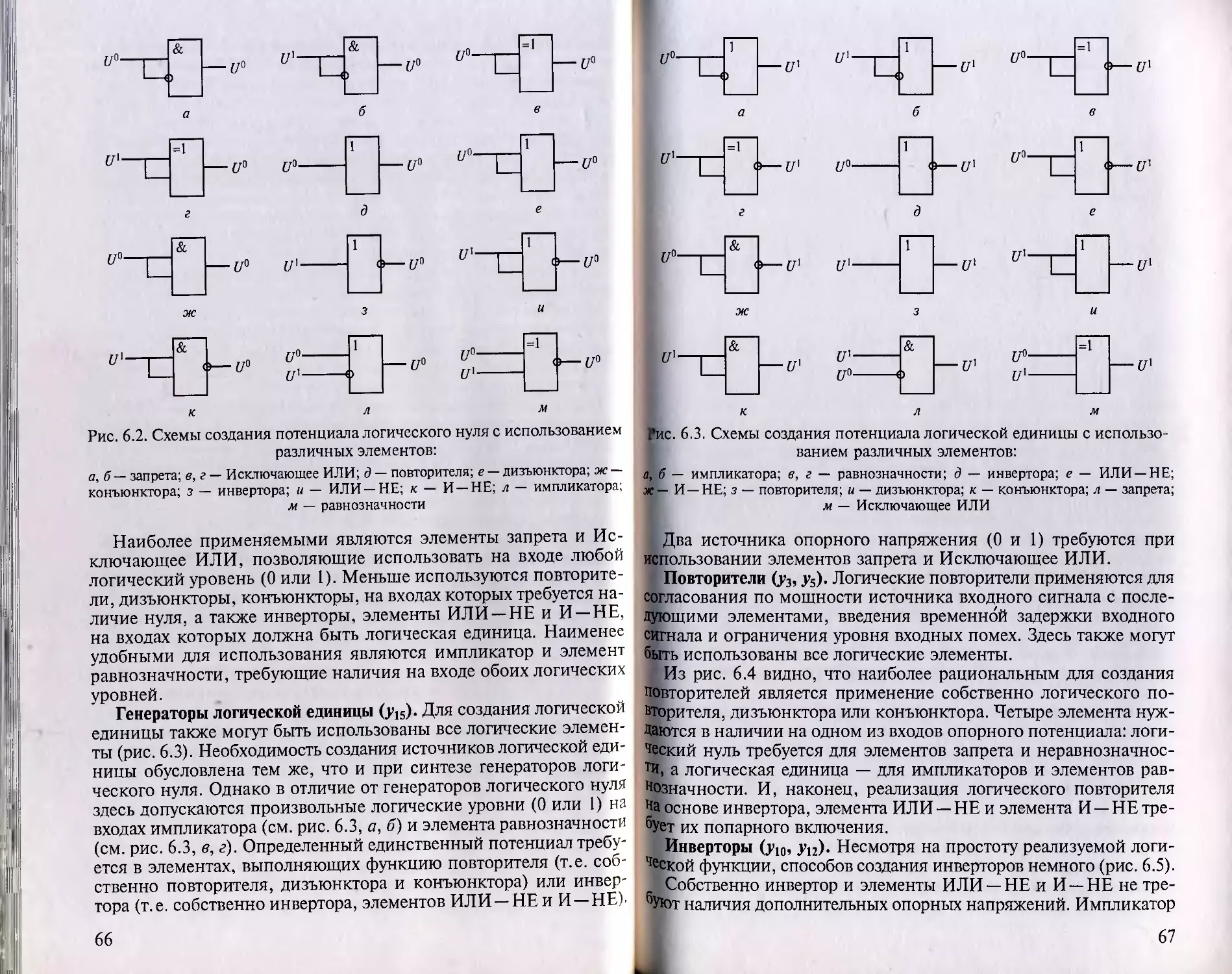

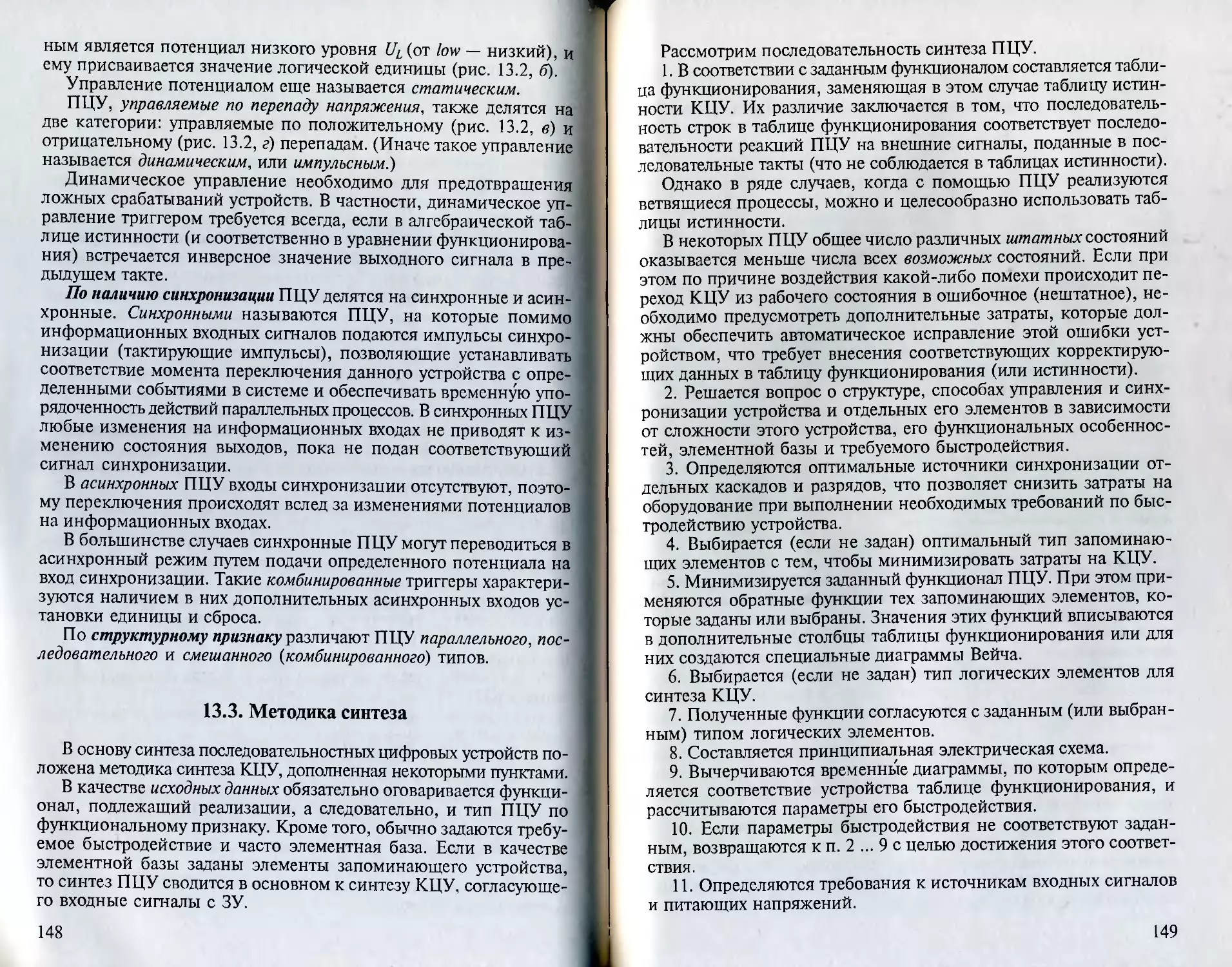

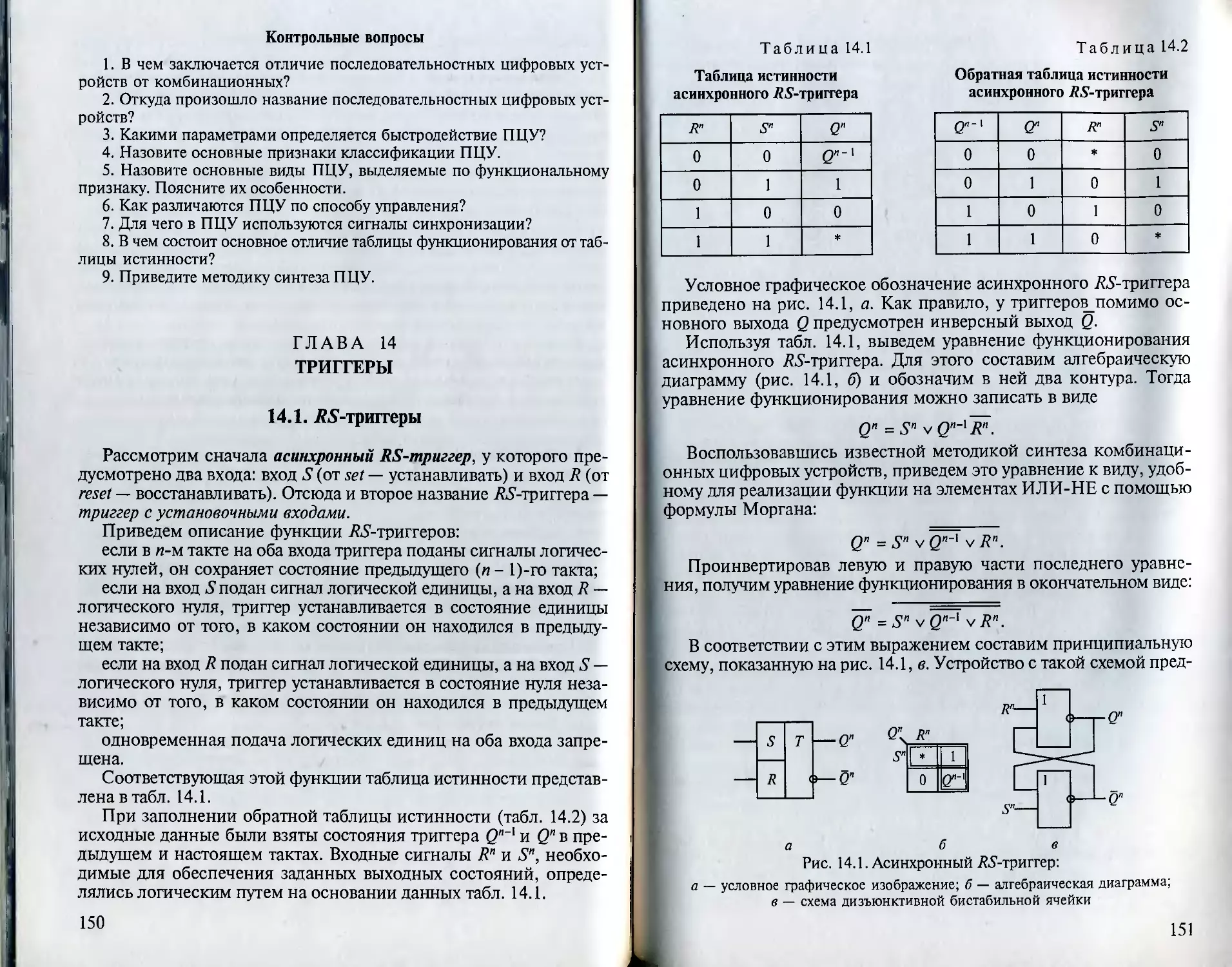

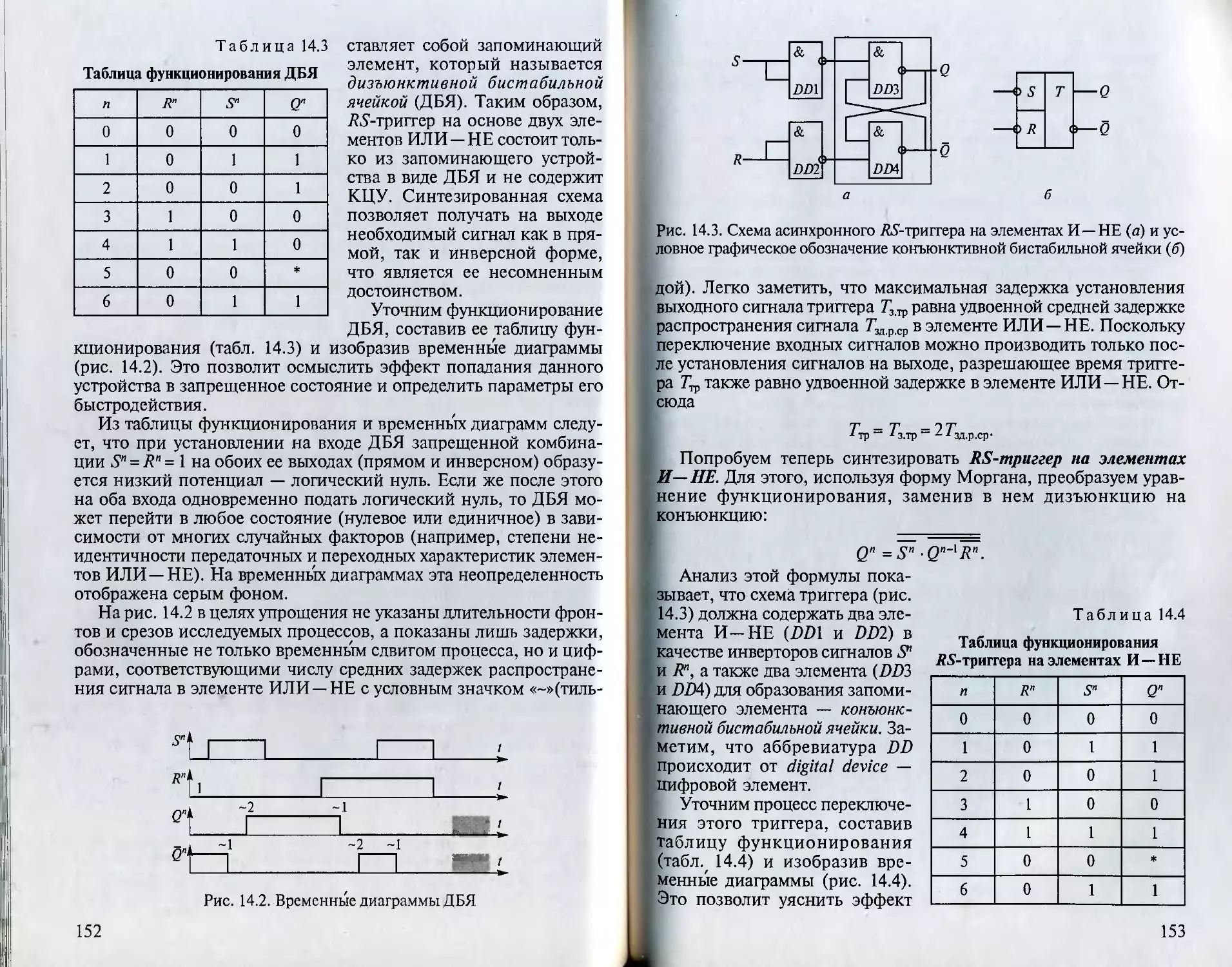

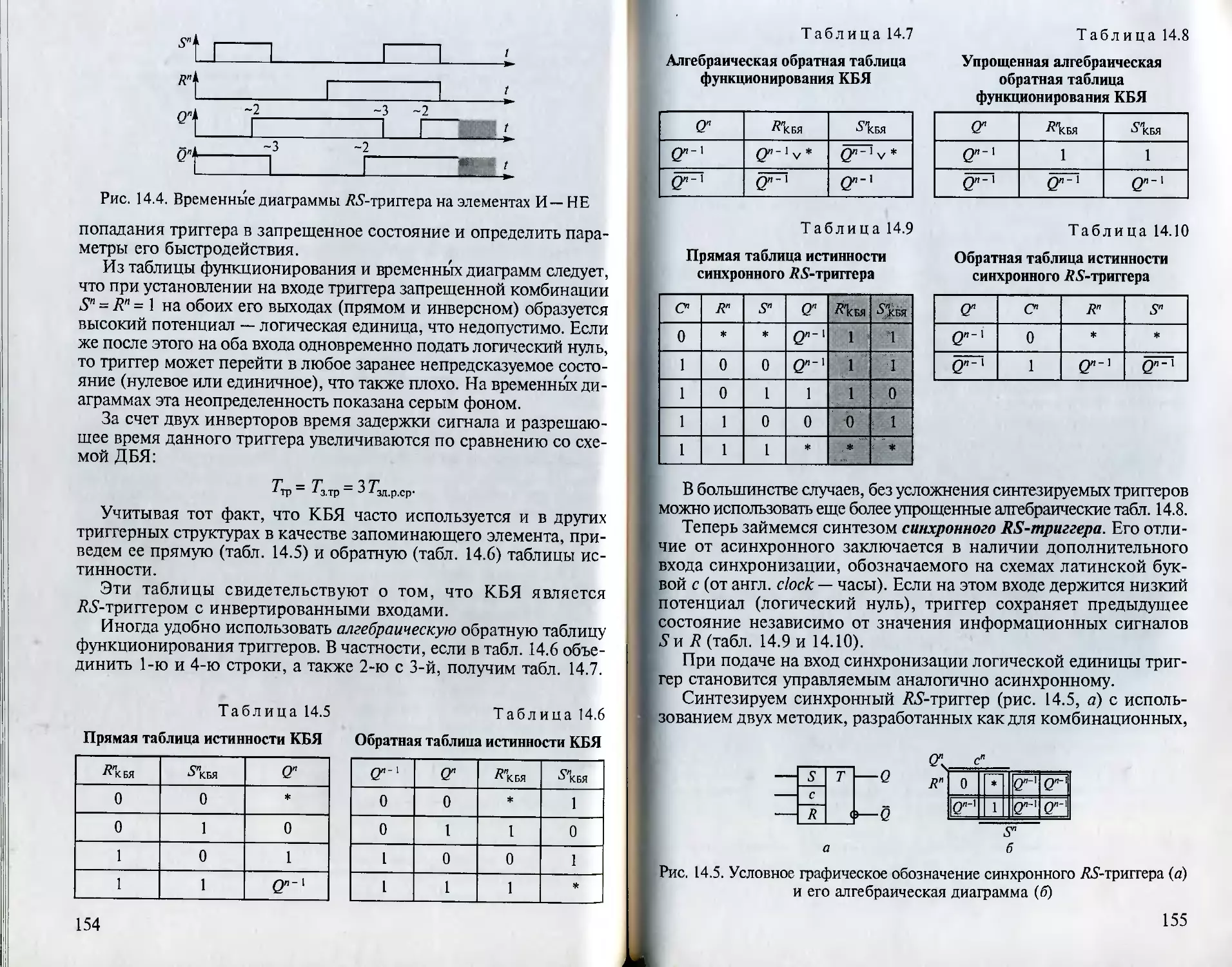

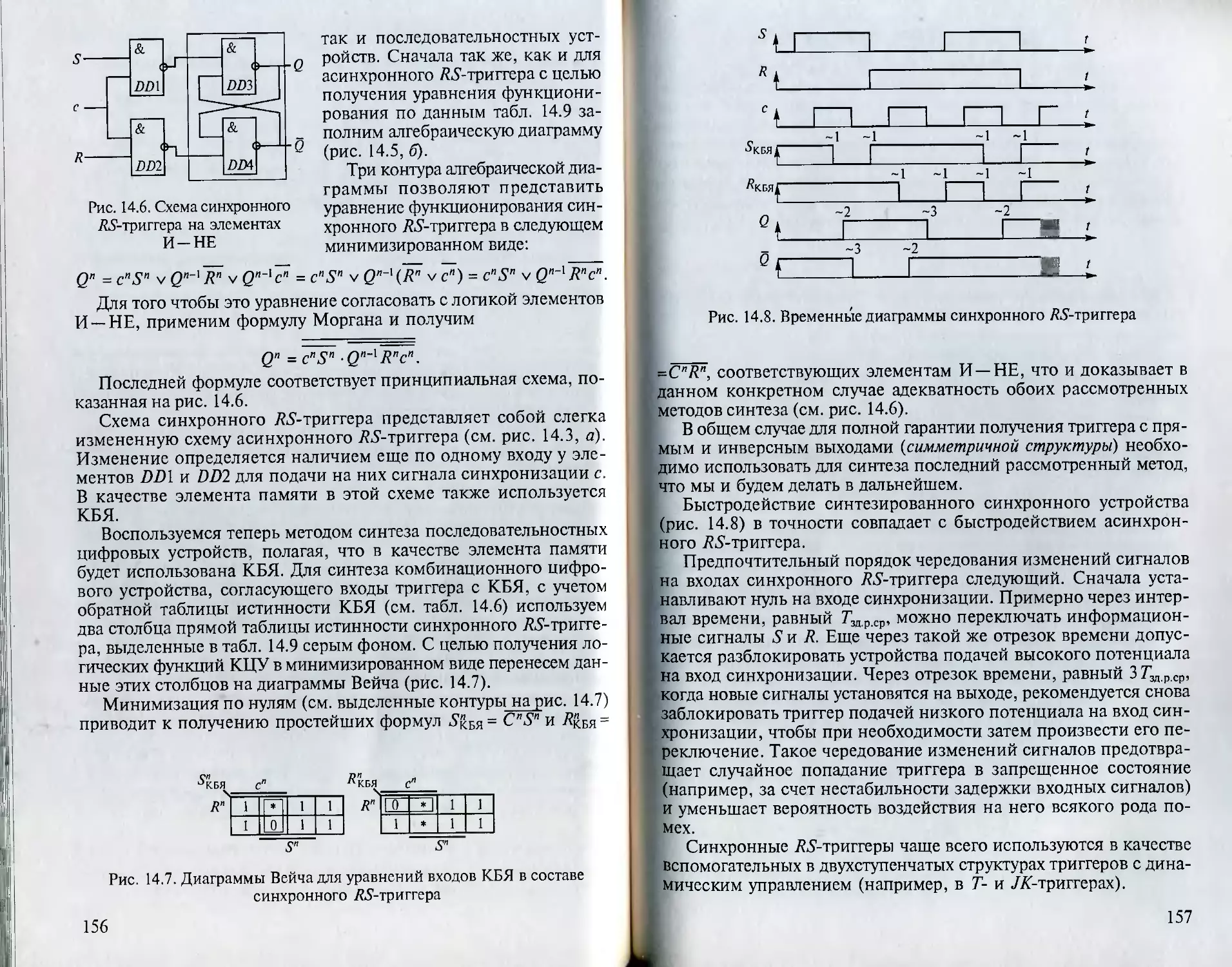

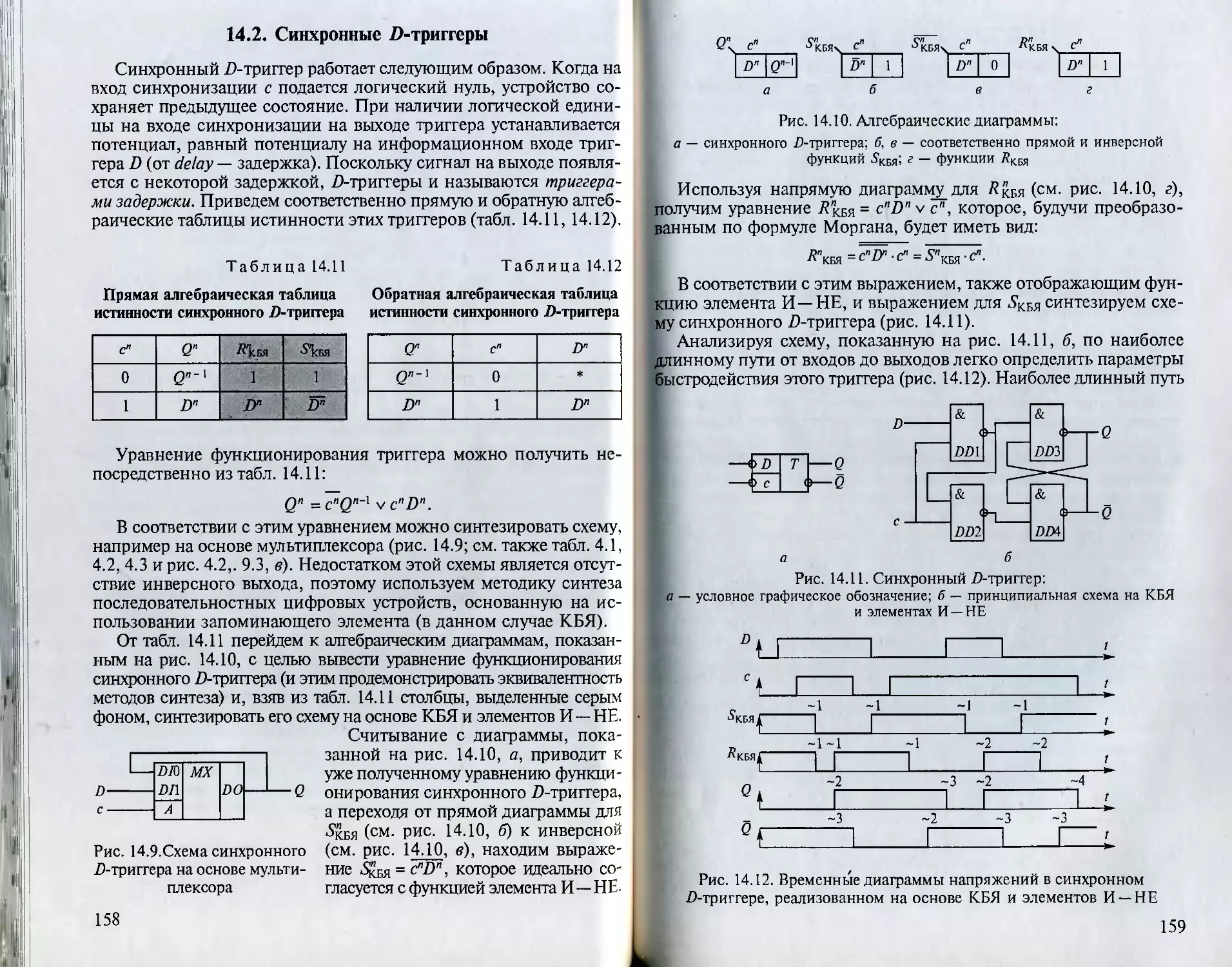

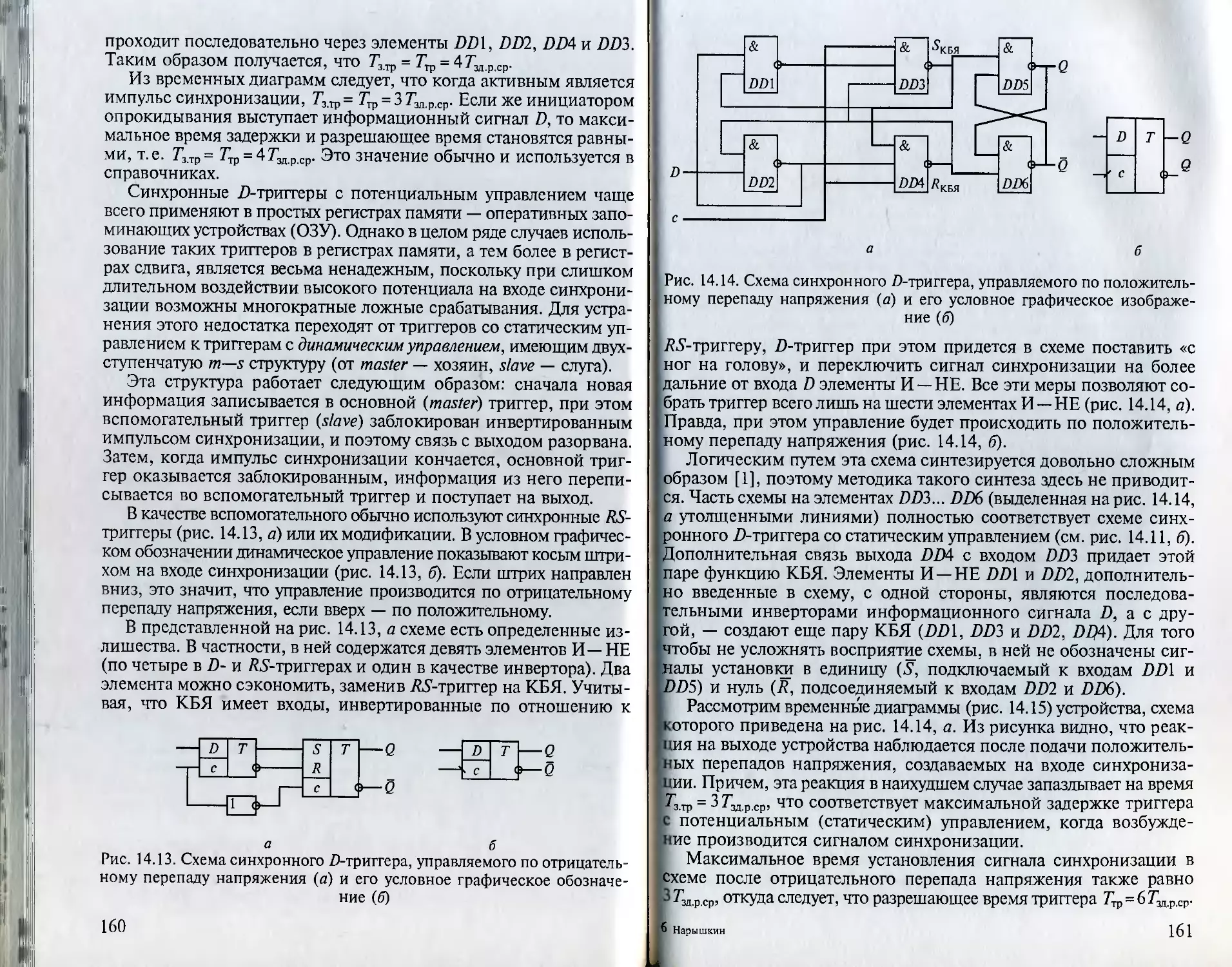

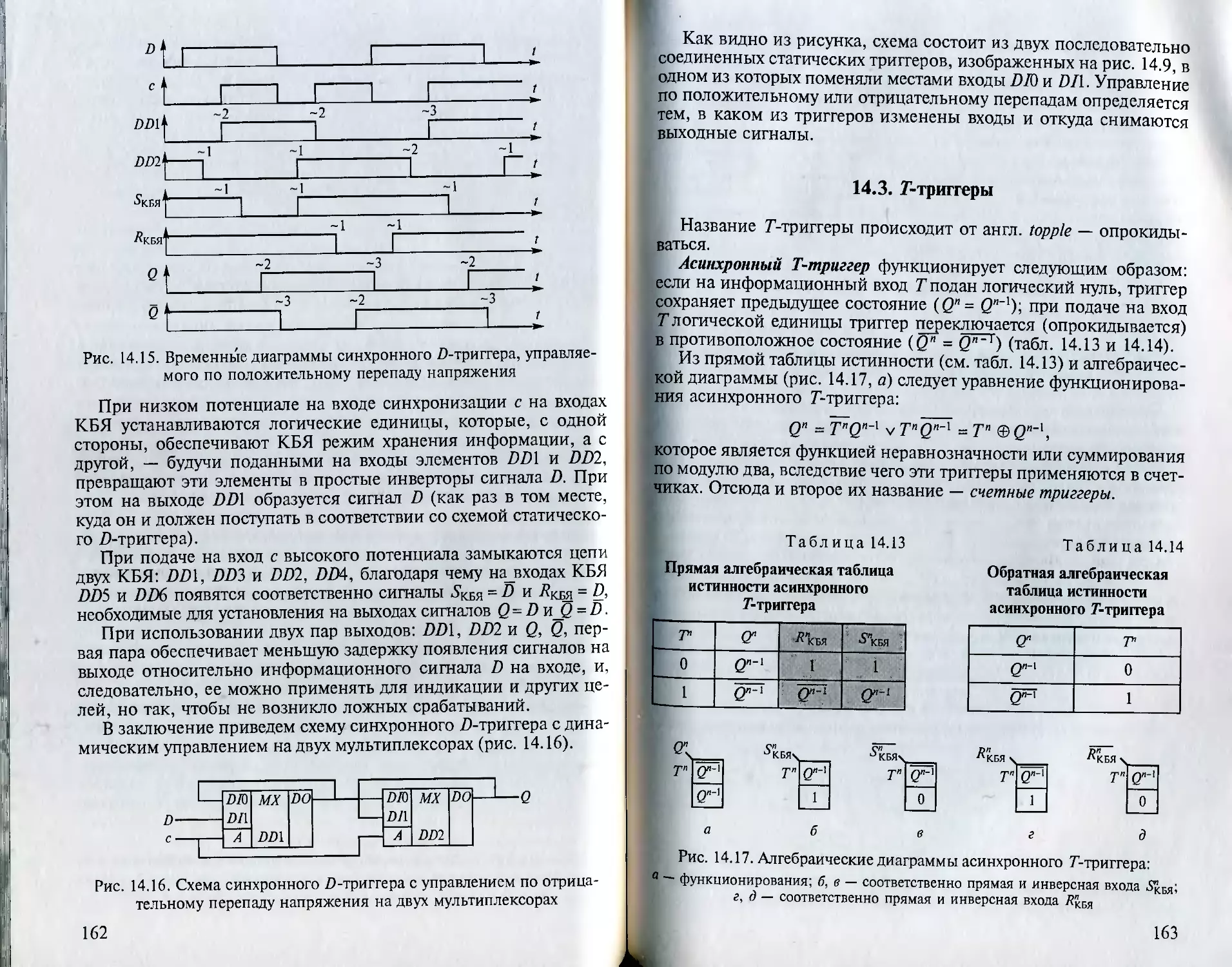

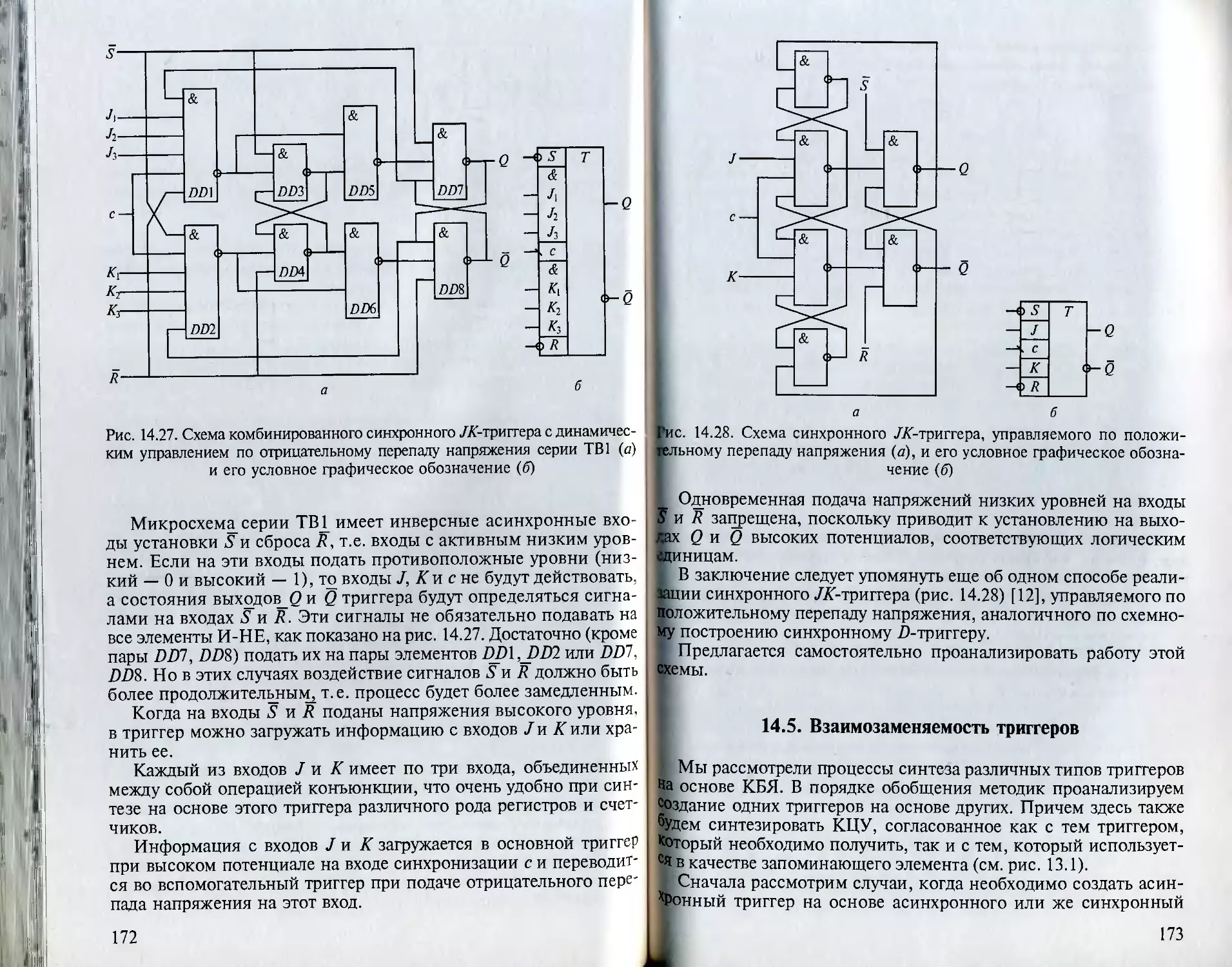

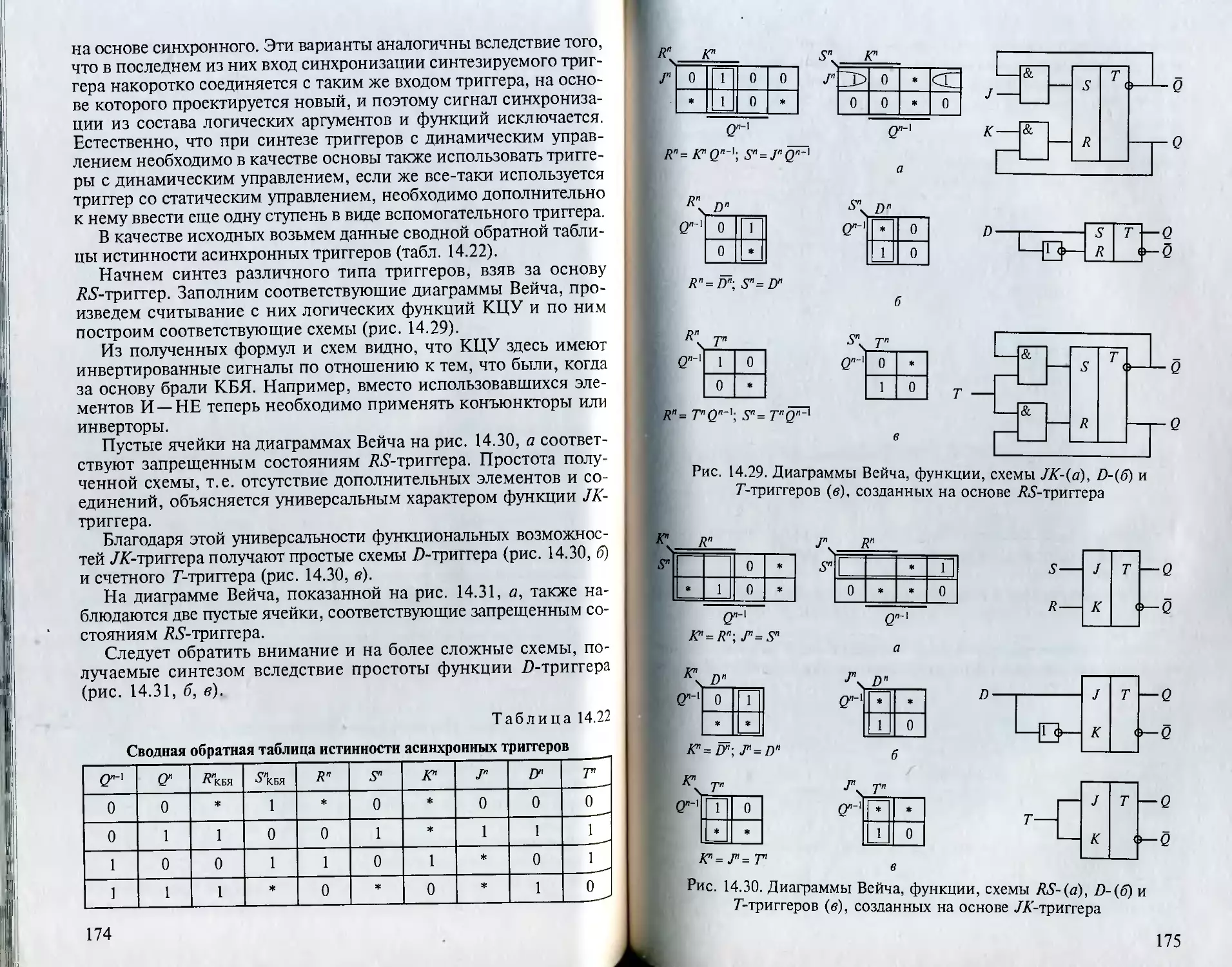

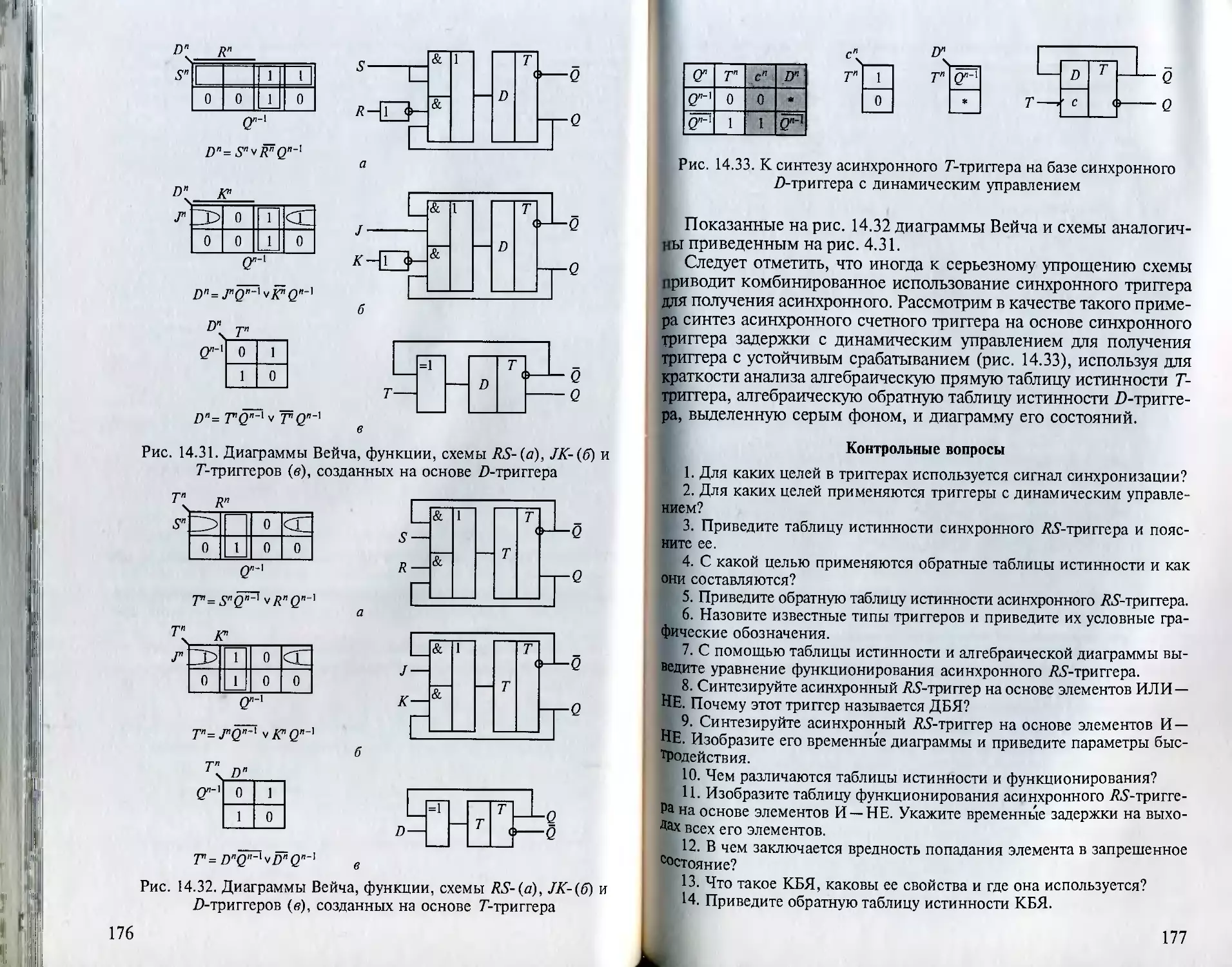

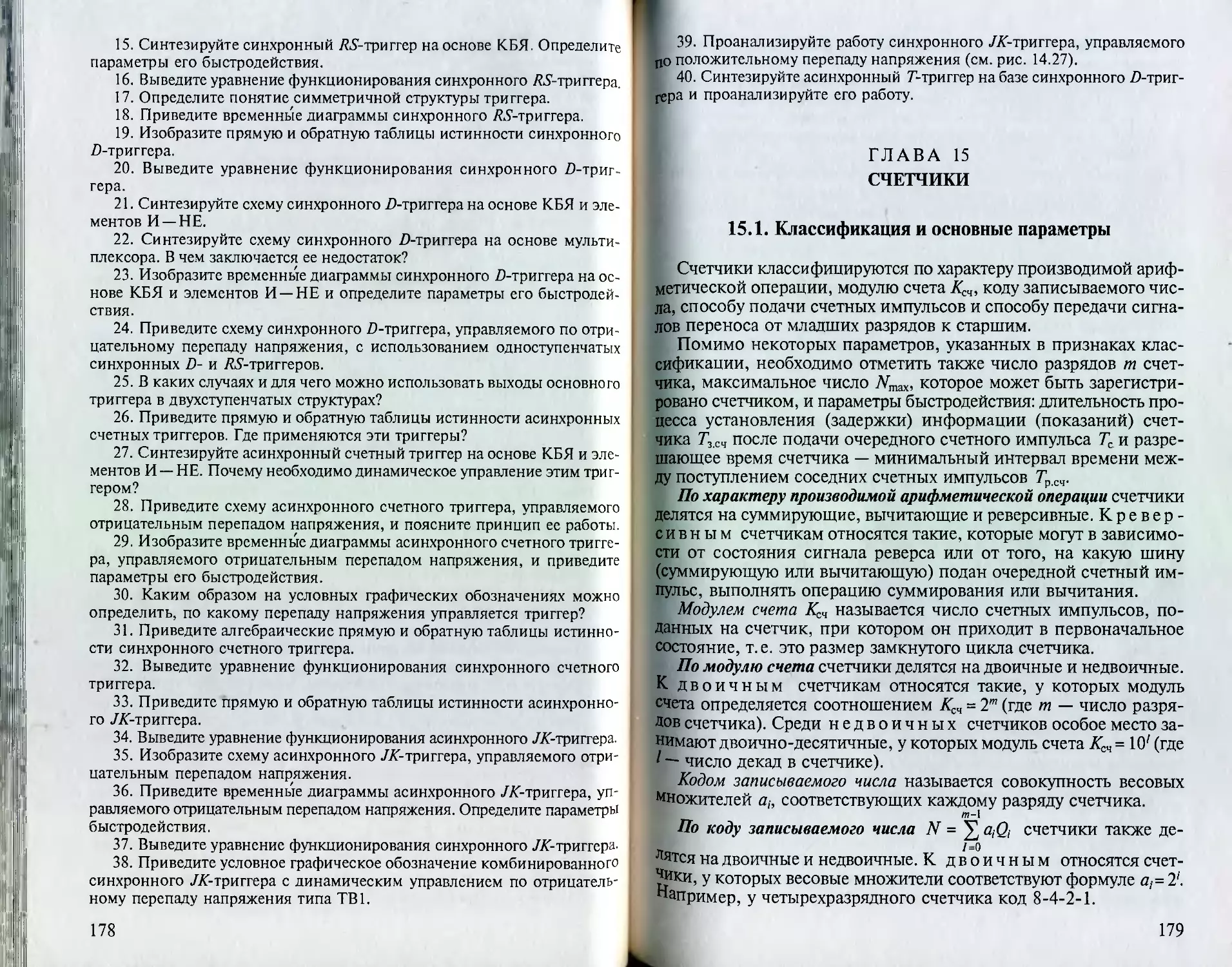

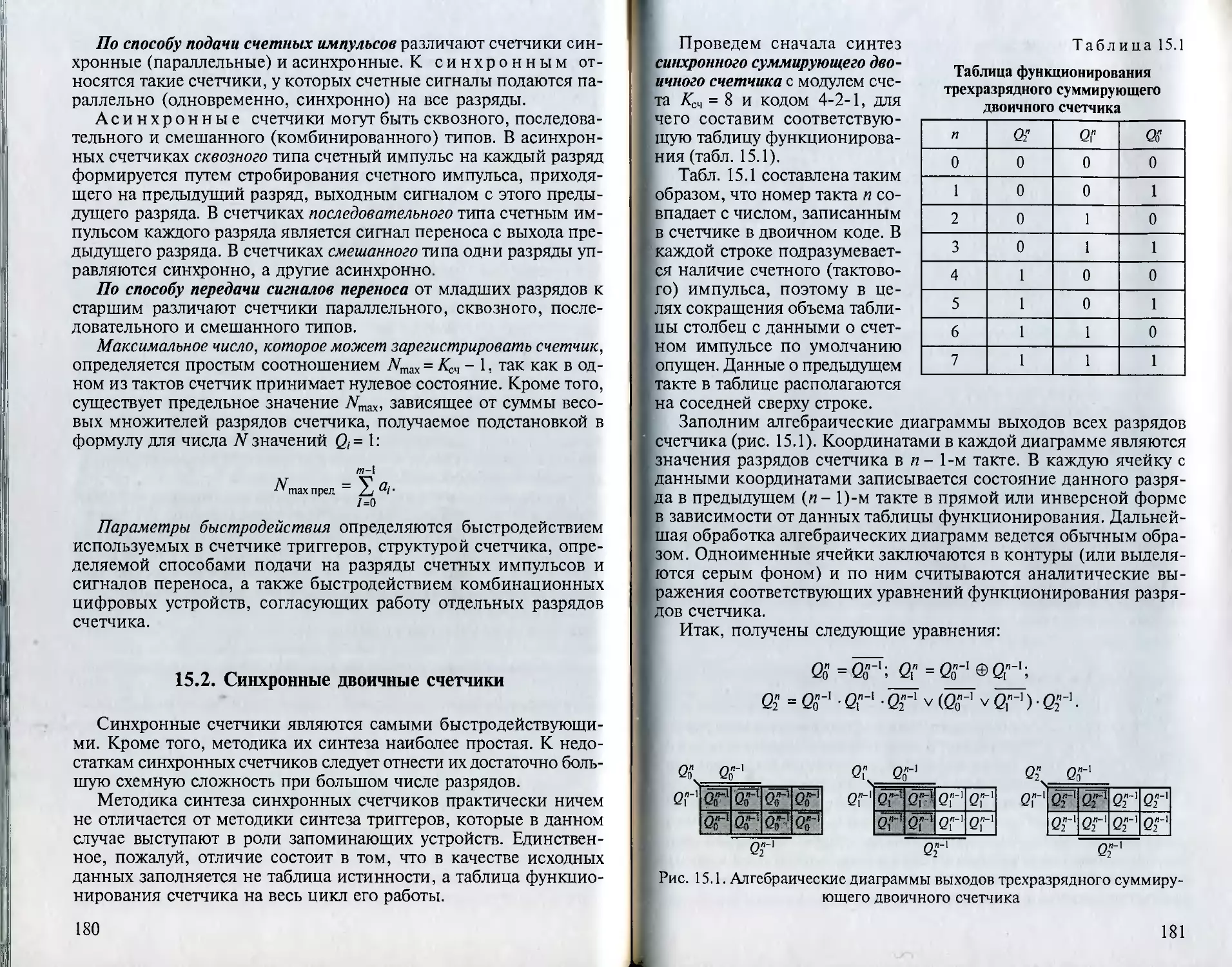

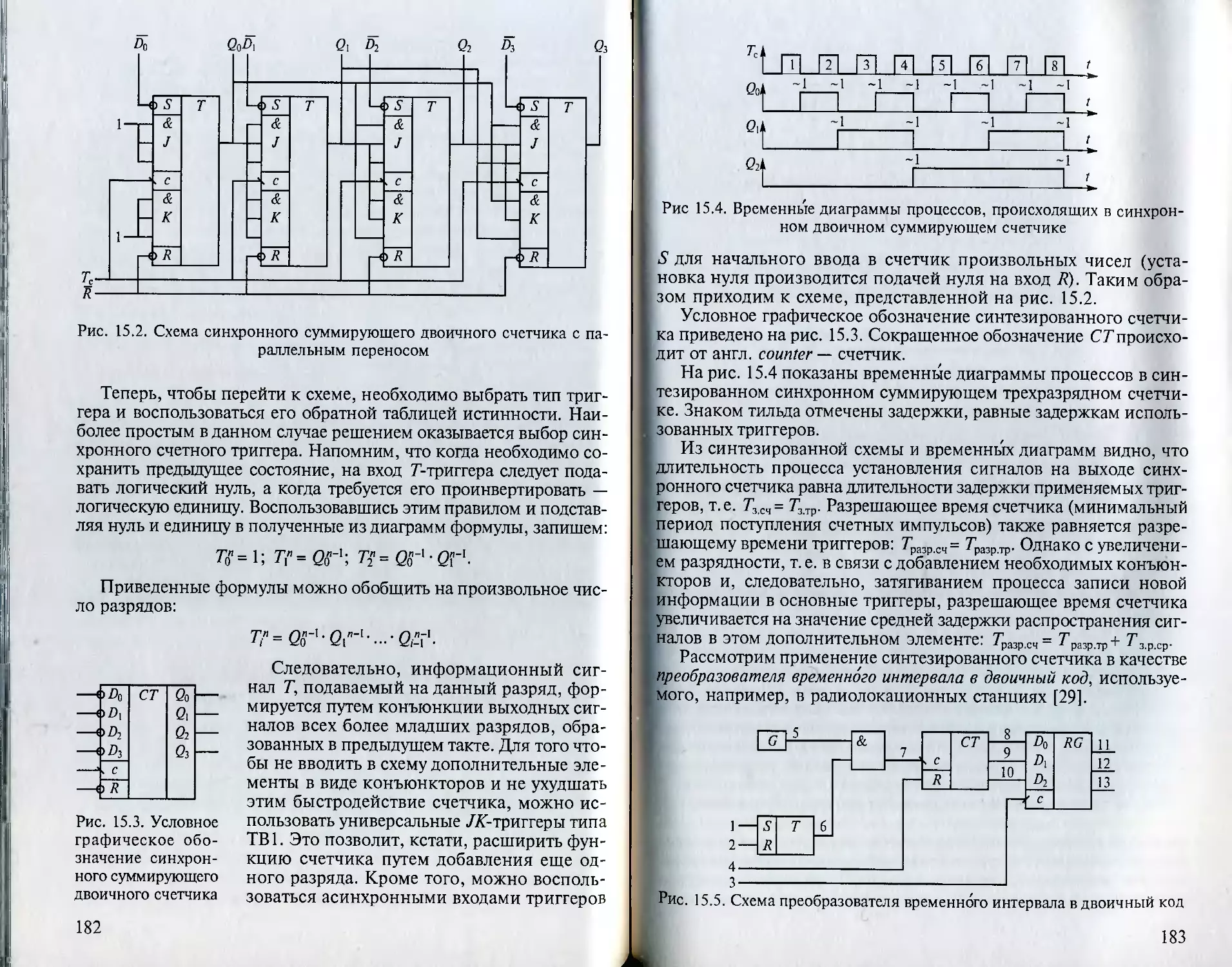

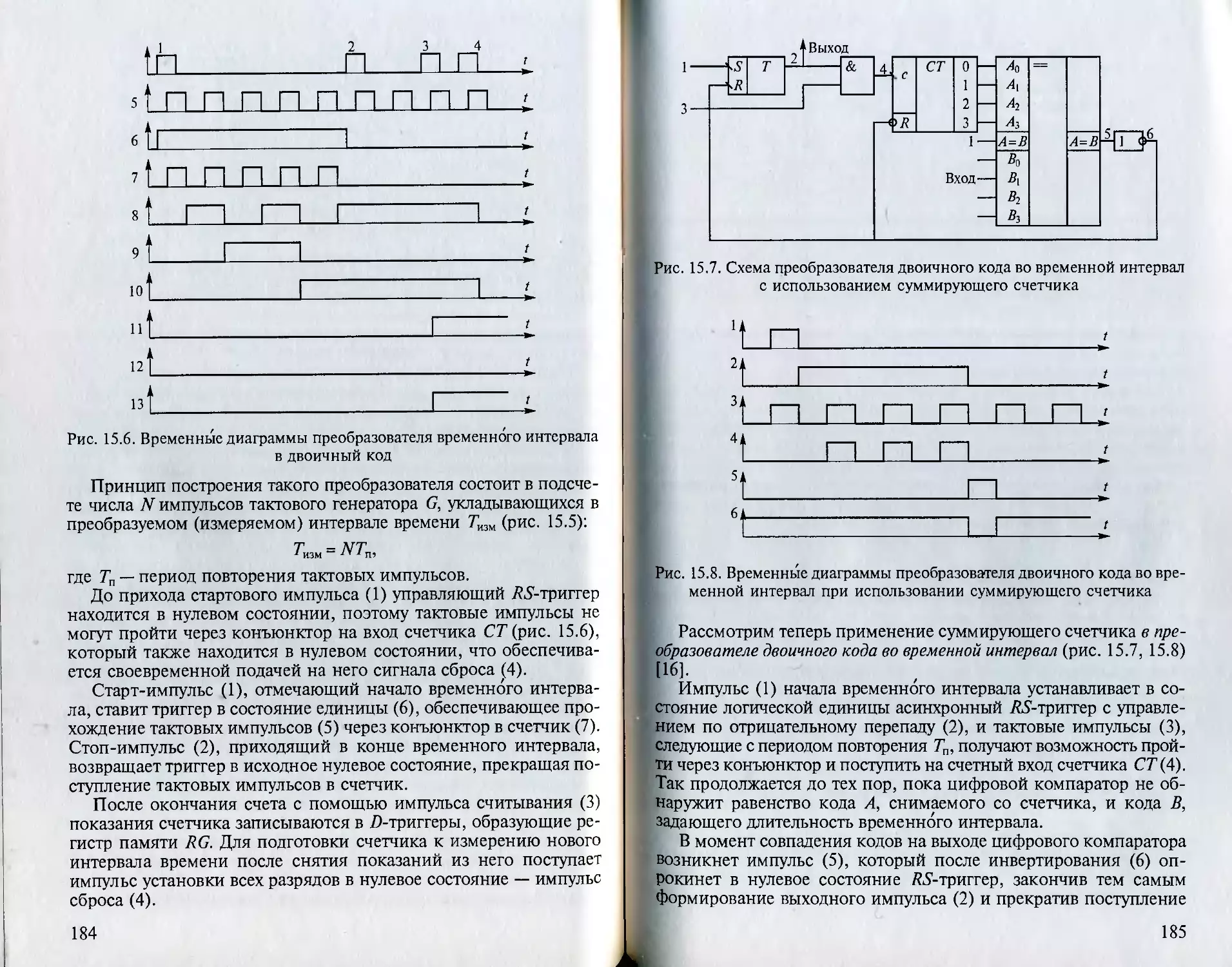

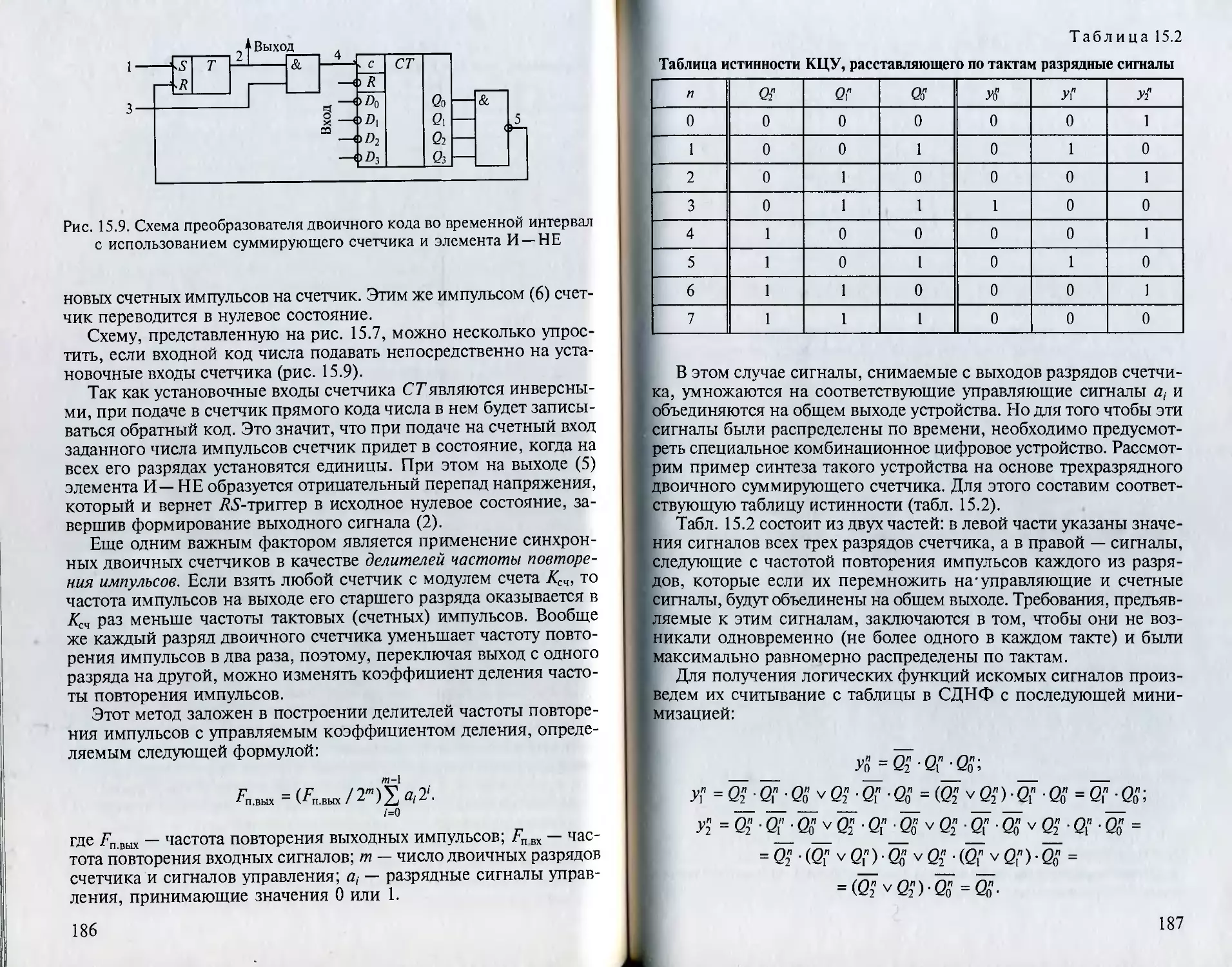

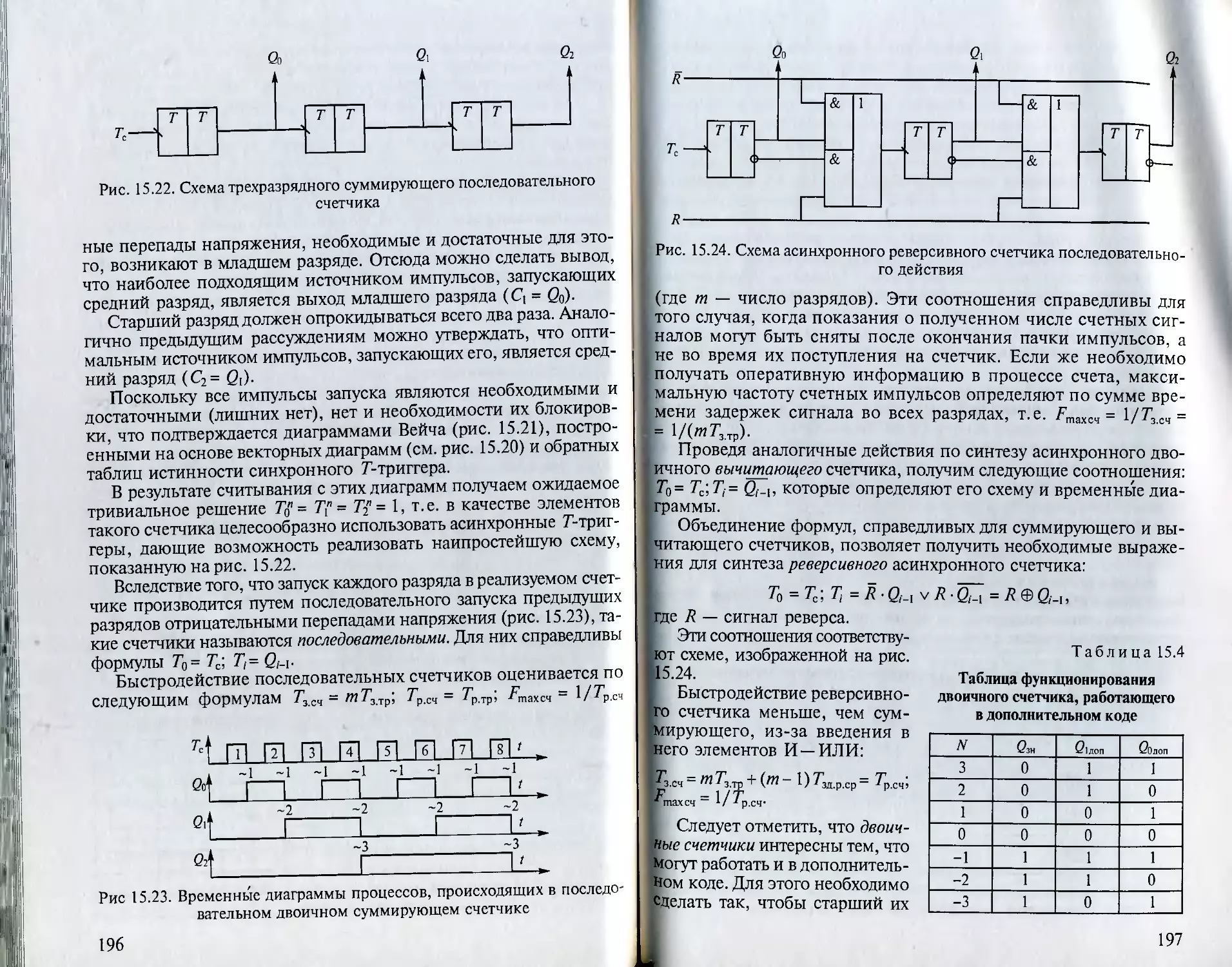

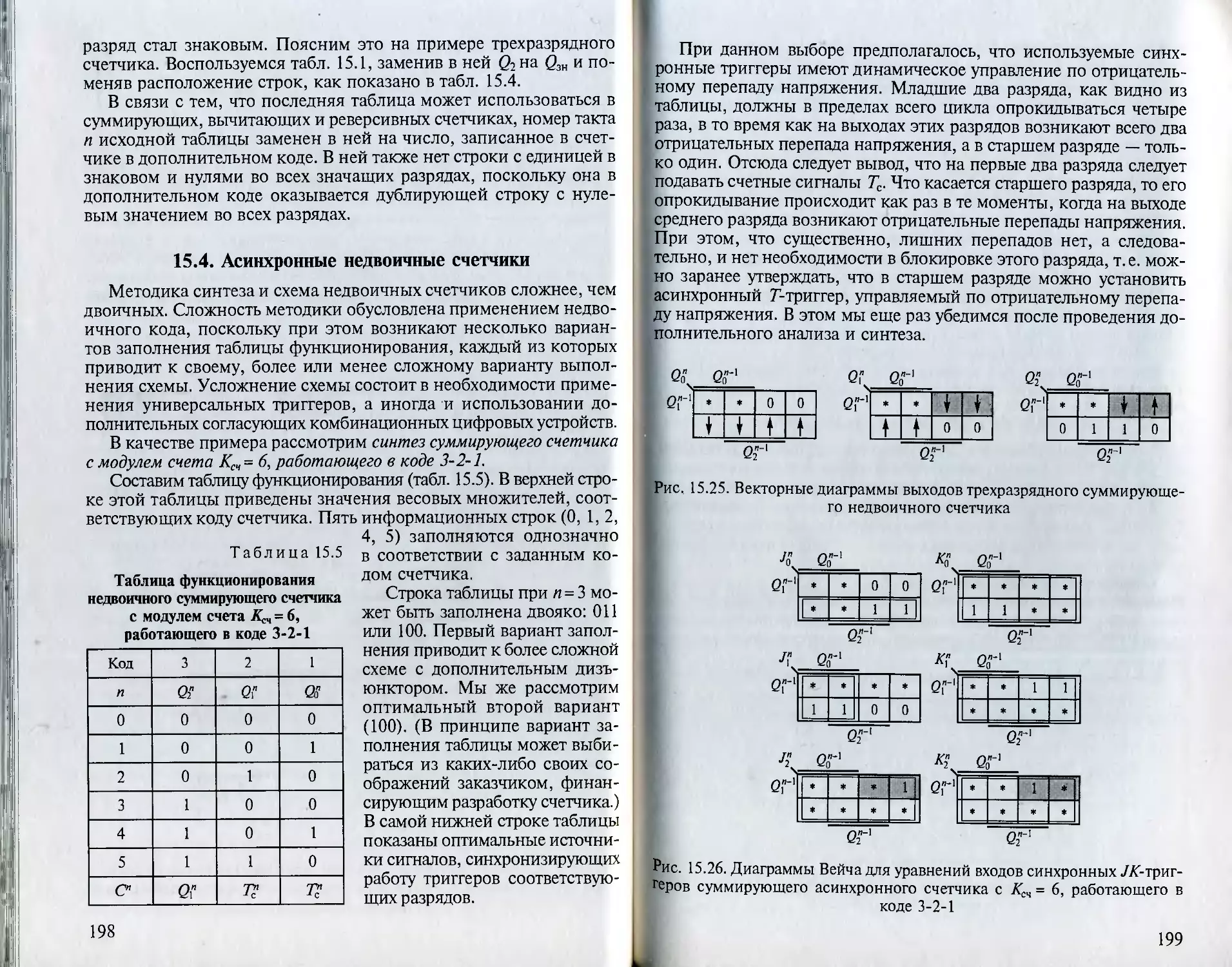

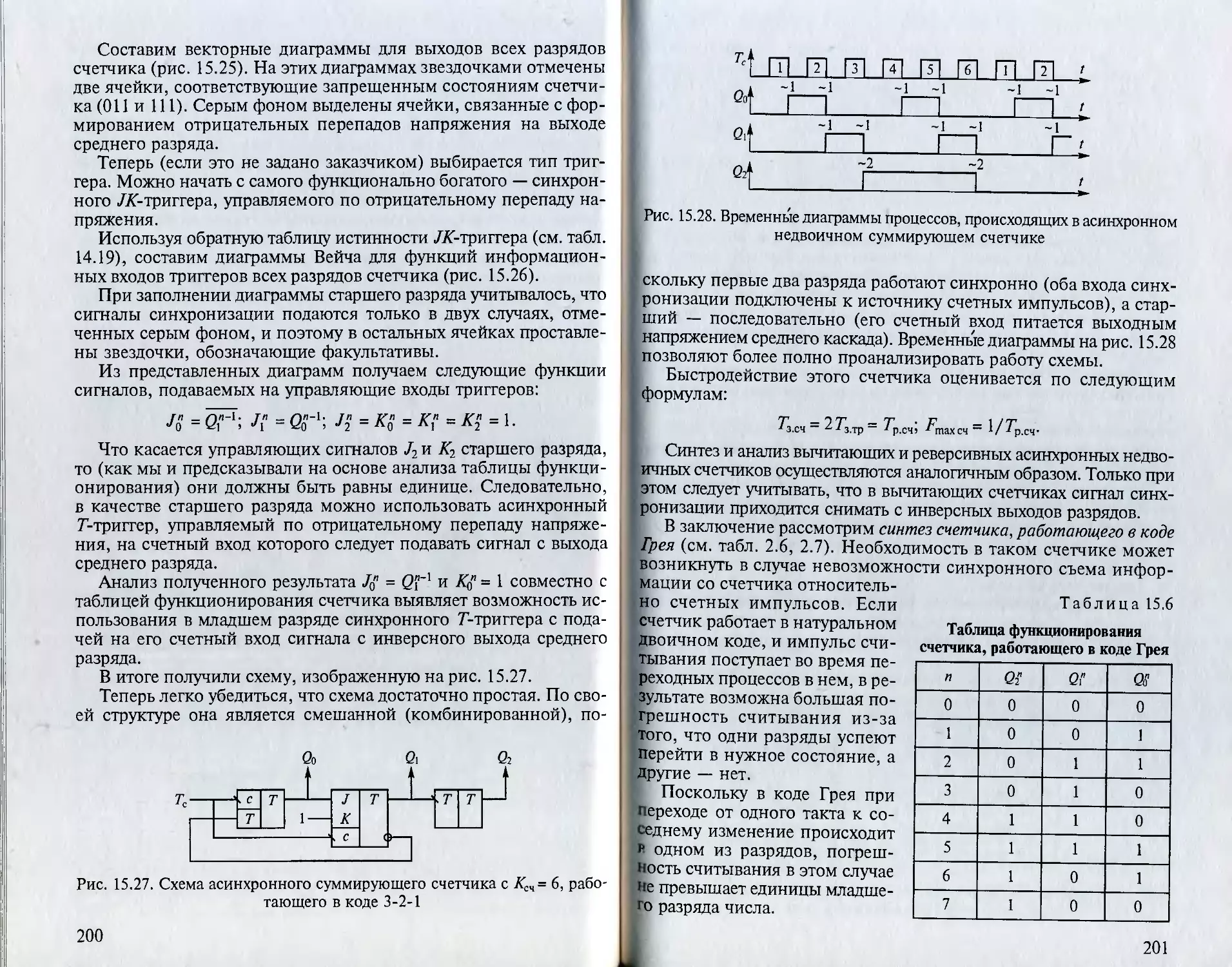

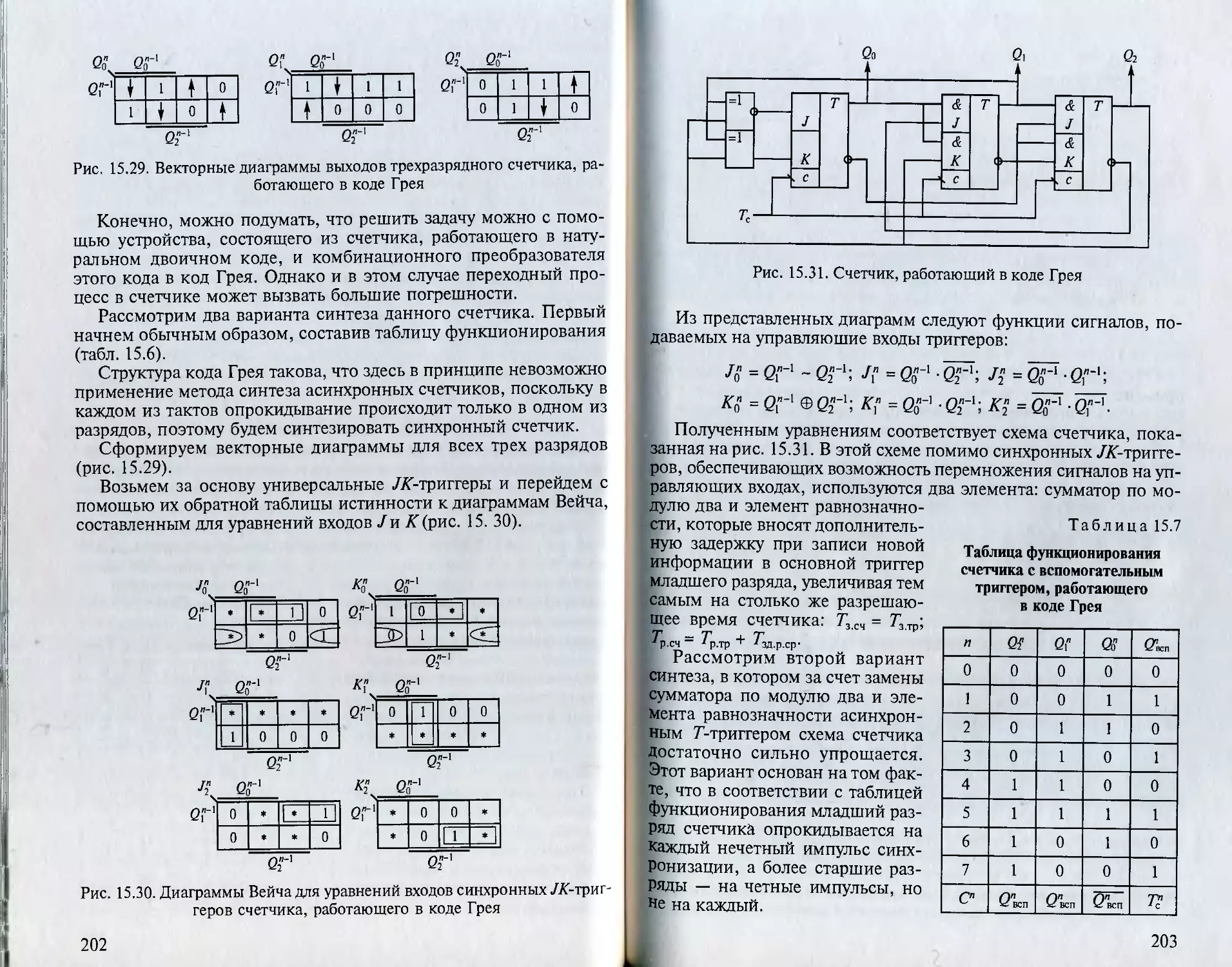

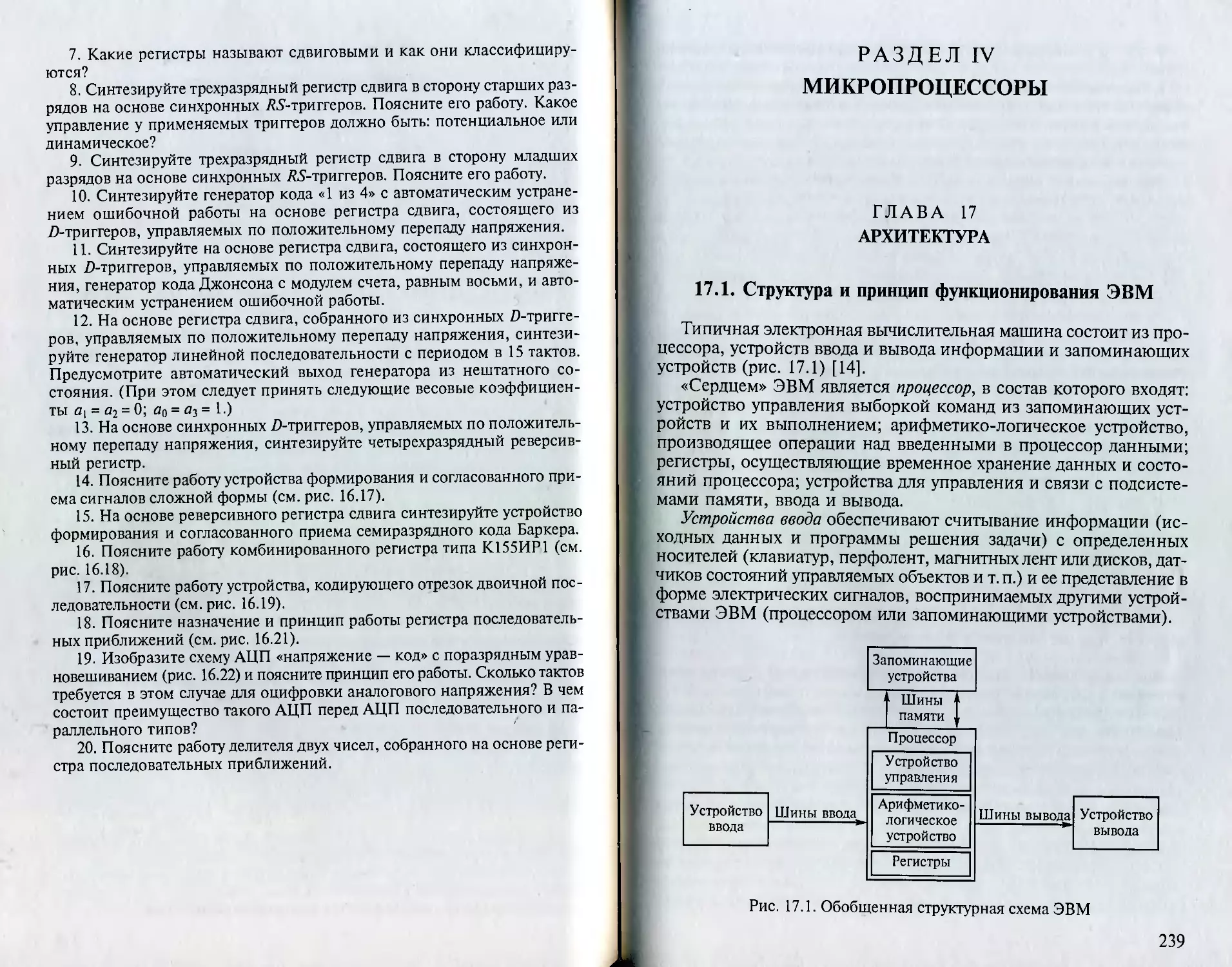

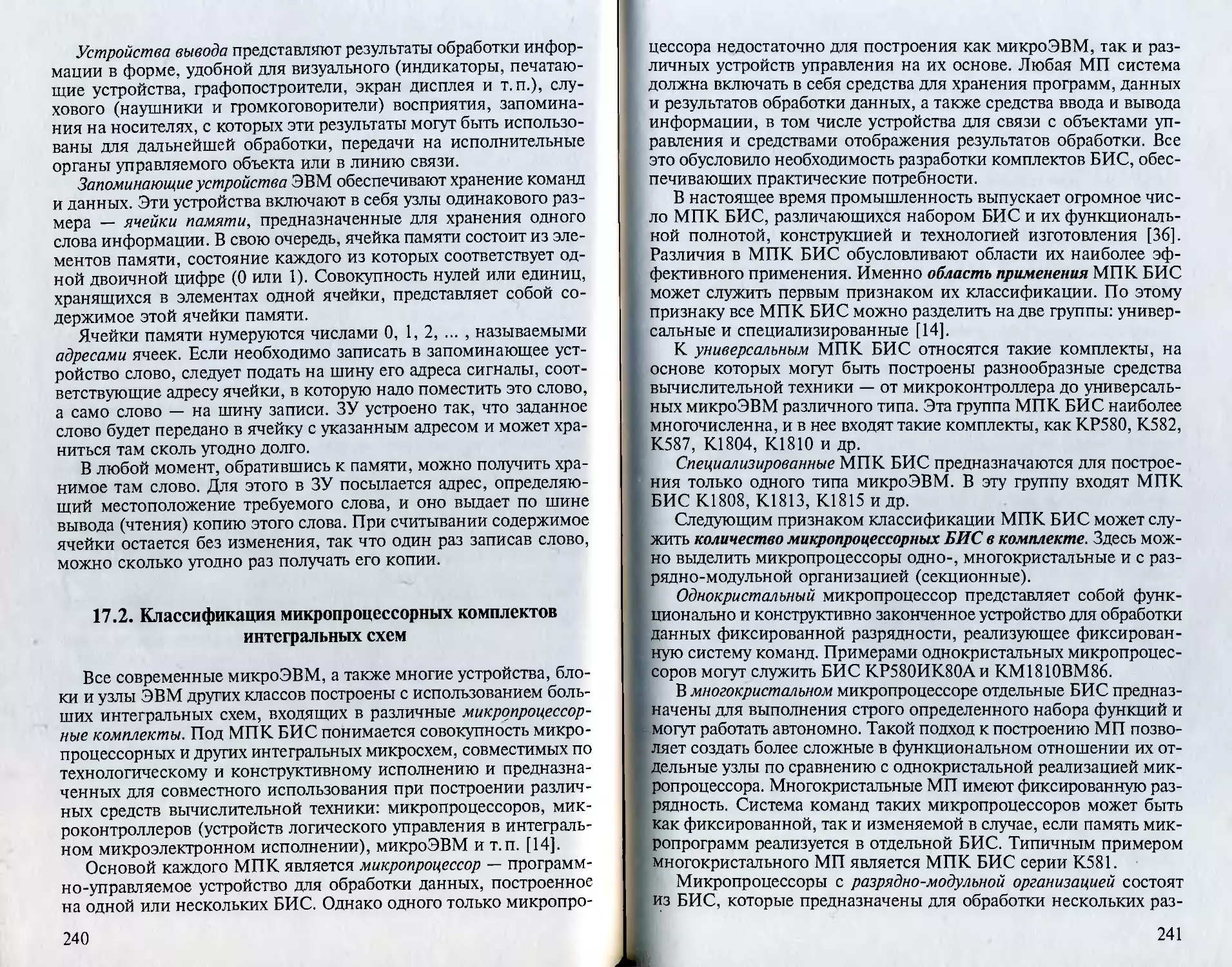

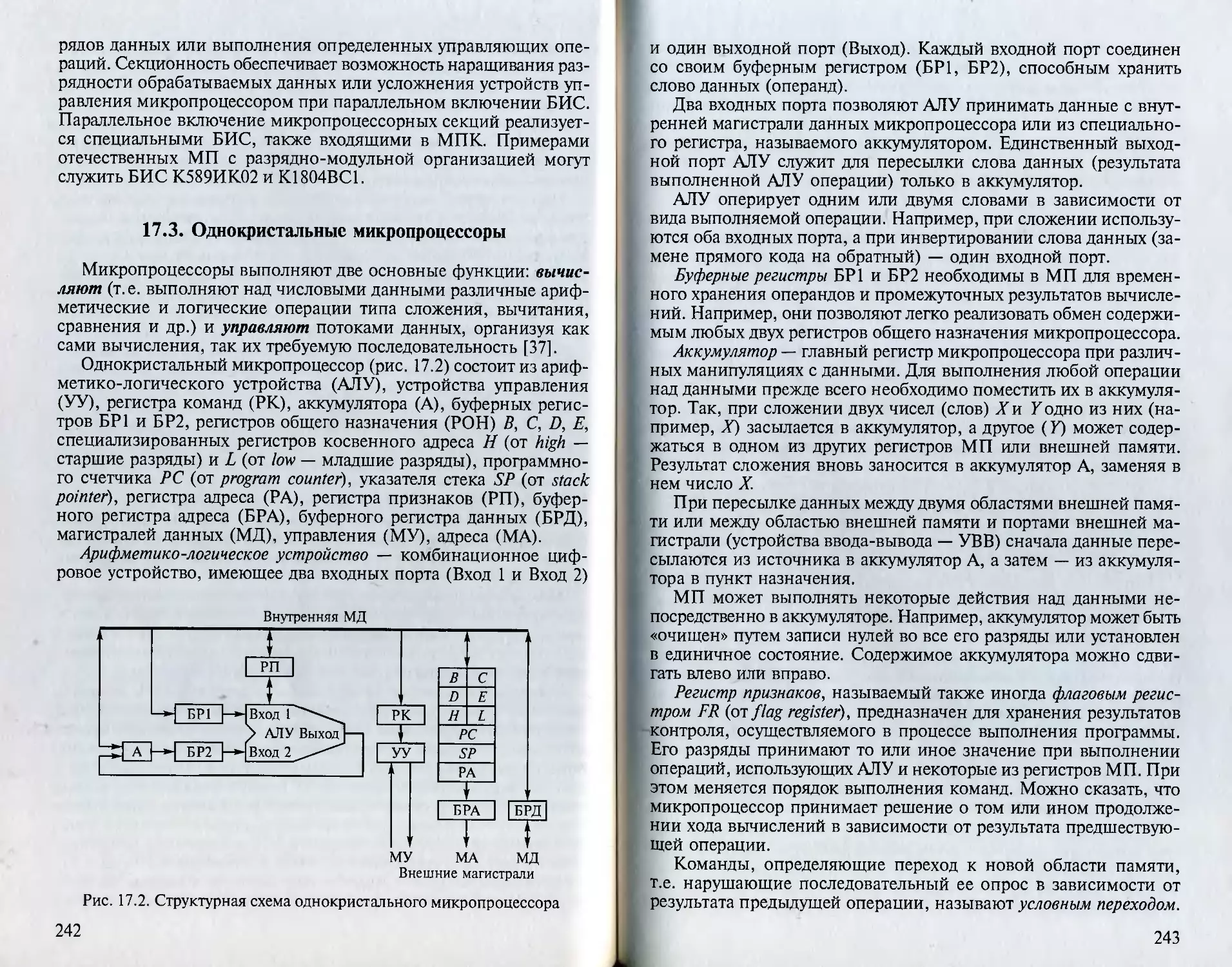

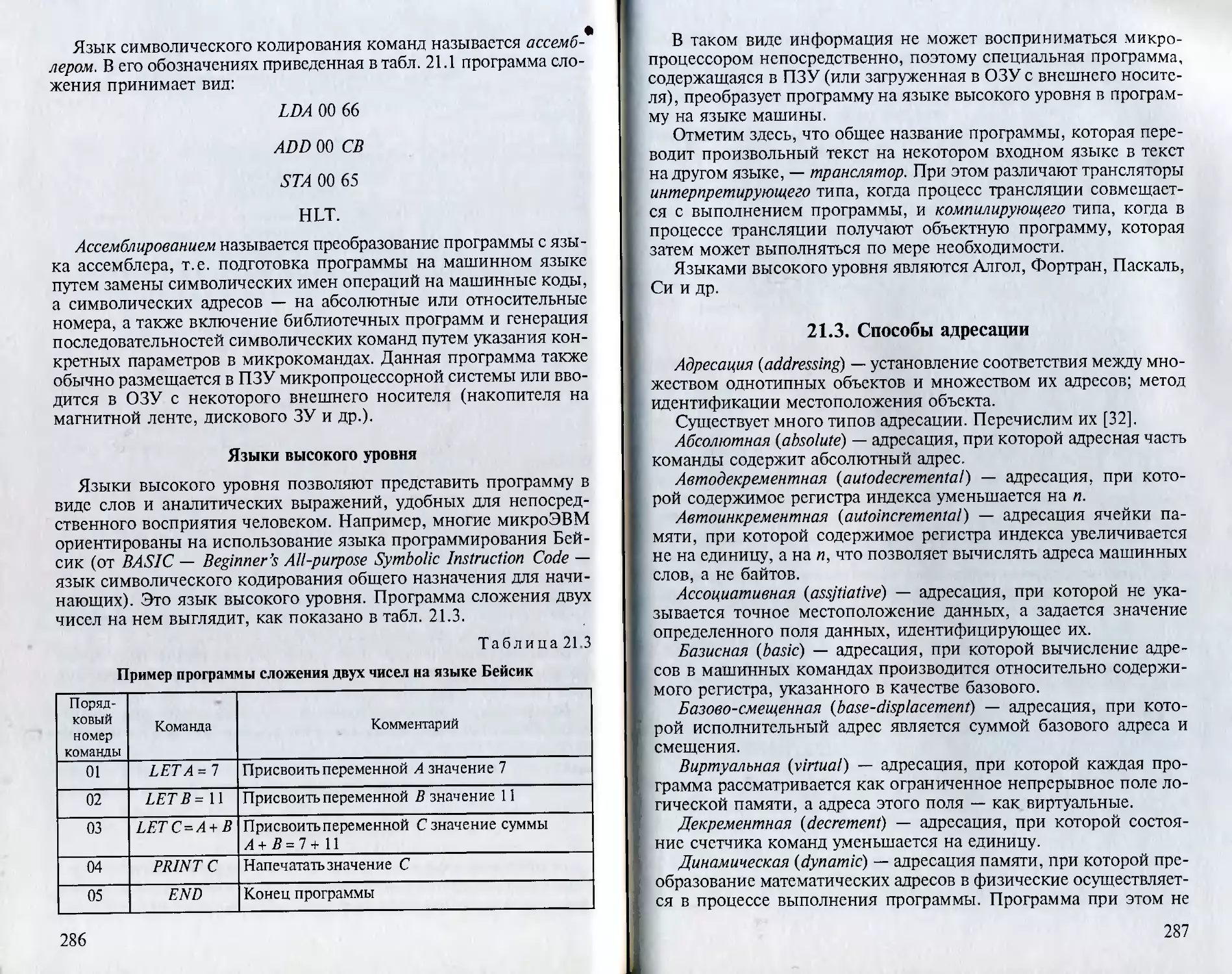

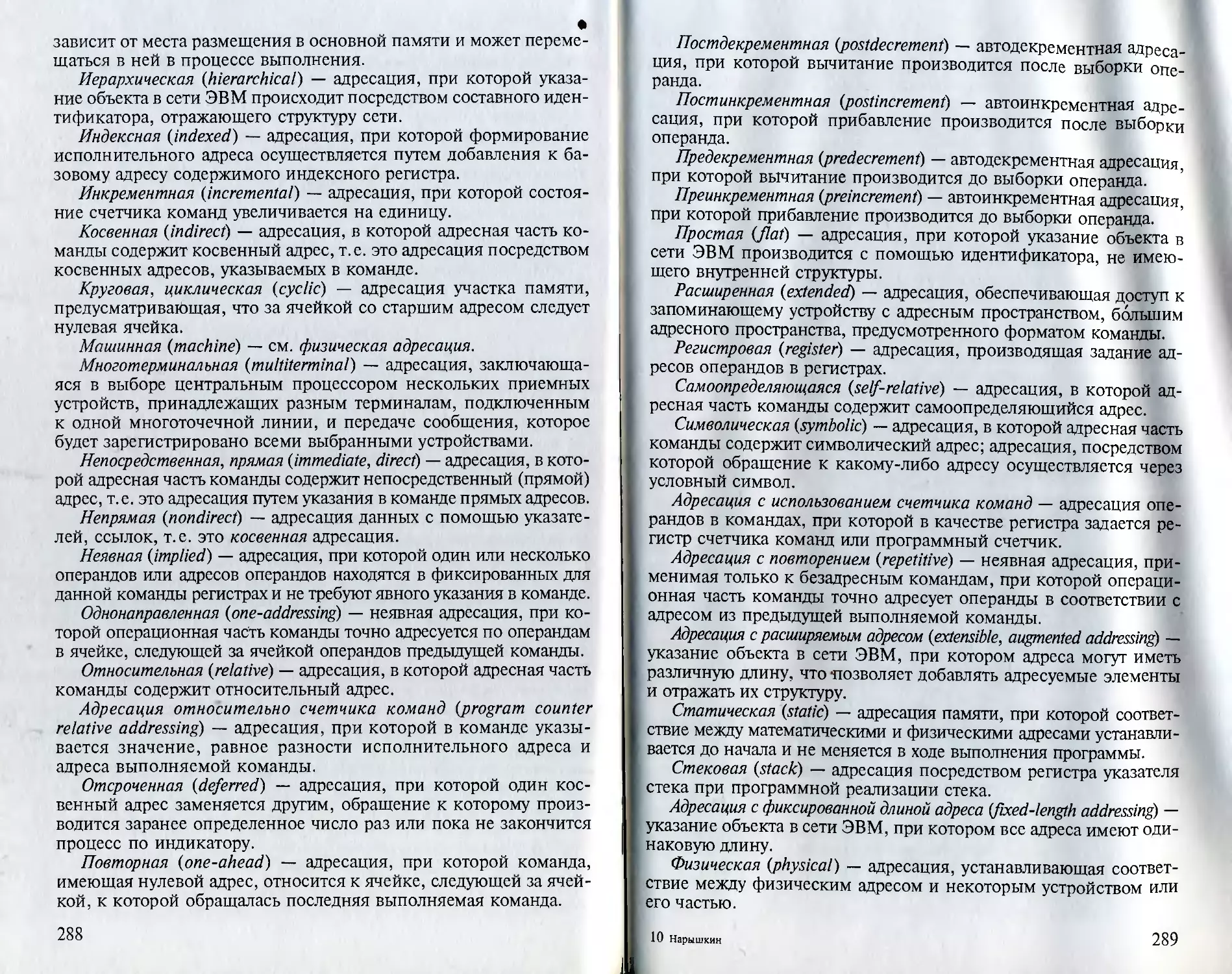

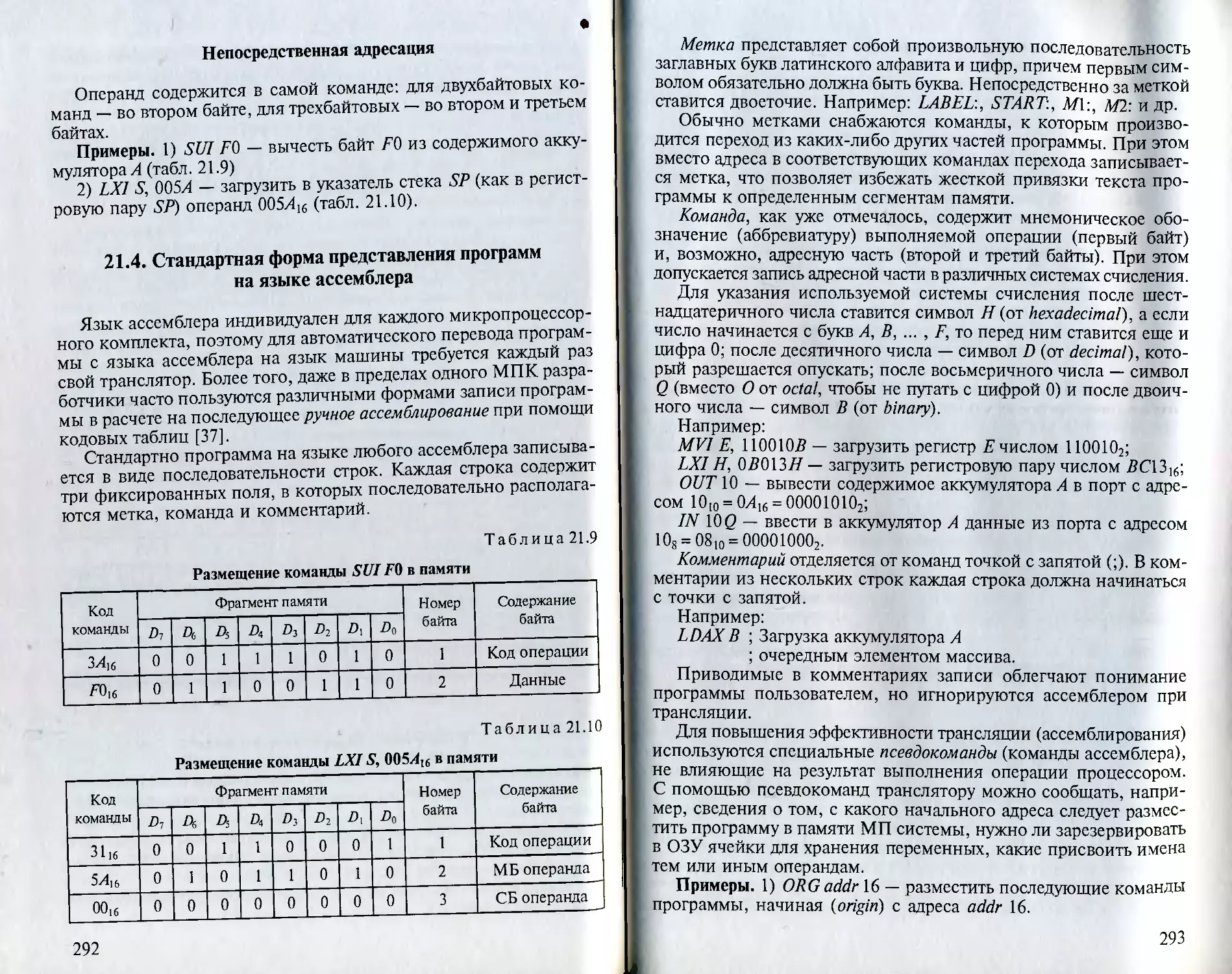

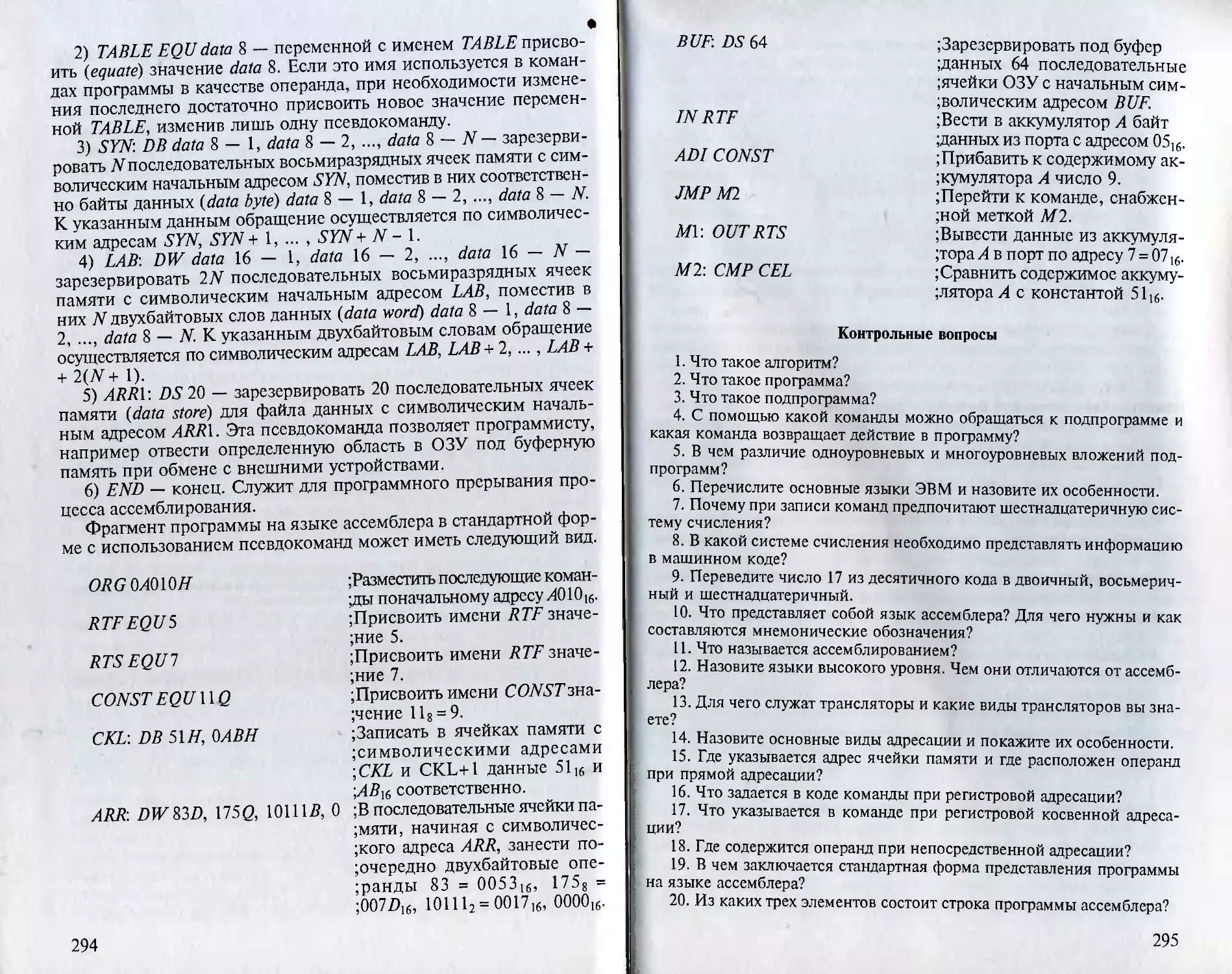

термы или импликанты от определенных функций.