Author: Бабич Н.П. Жуков И. А

Tags: блоки обработки данных процессоры вычислительная техника компьютерные технологии

ISBN: 966-96415-2-7

Year: 2004

Text

МКПрссс МММВЦНМс

Н. П. Бабич, И. А. Жуков

МЕТОДЫ ПОСТРОЕНИЯ И ПРОЕКТИРОВАНИЯ

“МК-Пресс” Киев, 2004

Рецензенты: член-корреспондент НАН Украины, профессор В.Ф. Евдокимов — директор Института проблем моделирования в энергетике НАН Украины; доктор технических наук, профессор Г.М. Луцкий — заведующий кафедрой "Вычислительная техника" НТУУ “КПИ''.

Бабич Н. П., Жуков И. А.

Б125 Компьютерная схемотехника. Методы построения и проектирования: Учебное пособие. — К,: “МК-Пресс”, 2004. — 576 с., ил.

ISBN 966-96415-2-7

В этом учебном пособии систематизировано изложены информационные, арифметические и логические основы микроэлектронных схем современных компьютеров. Рассмотрены принципы построения и функционирования логических и запоминающих элементов, типовых функциональных узлов, аналого-цифровых и цифро-аналоговых преобразователей, электронной памяти, арифметико-логических и управляющих устройств, микропроцессоров, интерфейсных контроллеров, а также представлены технологии производства печатных плат. Особое внимание уделено правилам составления конструкторской и программной документации, а также требованиям оформления схем и иллюстративных документов.

Рассчитано на студентов инженерно-технических специальностей высших учебных заведений.

ББК з973.2-04я73-5

BN 966-96415-2-7

© Бабич Н.П., Жуков И.А., текст, иллюстрации, 2004 © "МК-Пресс ’, оформление, дизайн обложки, 2004

Содержание 3

Содержание

Введение

Перечень используемых сокращений

Глава 1. Основы теории компьютерной схемотехники

1 1 Информационные основы компьютерной схемотехники

1 2 Арифметические основы компьютерной схемотехники

1 3 Логические основы компьютерной схемотехники

1 4 Основные хаоактеристики цифровых микросхем

Глава 2. Элементы компьютерной схемотехники

2 1 Логические элементы — диодные, транзисторные, ИИЛ и ДТЛ

2 2 Транзисторно-транзисторные логические элементы

2 3 Логические элементы эмиттерно-связной логики

2 4 Логические элементы на МОП-транзисторах

2 5 Импульсная и потенциально-импульсная системы элементов

2 6 Магнитная схемотехника

2 7 Асинхронные и синхронные RS-триггеры

2 8 Триггеры типов JK, Т D и DV

Глава 3. Последовательностные (накапливающие) узлы компьютерной схемотехники

3 1 Регистры

3 2 Счетчики

Глава 4. Комбинационные функциональные узлы компьютерной схемотехники

4 1 Дешифраторы

4 2 Шифраторы

4 3 Мультиплексоры и демультиплексоры

4 4 Схемы сравнения и контроля

4 5 Преобразователи кодов

4 6 Двоичные сумматоры

4 7 Двоично-десятичные сумматоры

Глава 5. Цифро-аналоговые и аналого-цифровые преобразователи

5 1 Цифро-аналоговые преобразователи

5 2 Аналого-цифровые преобразователи

Глава 6. Основы компьютерной техники

6 1 Общая характеристика компьютерной техники и короткая история ее развития

6 2 Архитектура и структура компьютеров

6 3 Принцип программного управления

6 4 Основные характеристики компьютеров

6 5 Поколения компьютеров

6

7 10

10

18 40

51 65

65 73

83

86

S3 97 103 110

119 119 128

141

141 147

151 157

166 173 186

190

190 196

202

202 203

207 208 209

4 Введение

Глава 7. Память компьютеров 213

7 1 Общая характеристика памяти 213

7 2 Основные структуры полупроводниковой памяти 219

7 3 Кэш-память 223

7 4 Постоянная память 227

7 5 Флэш-память 235

7 6 Статические запоминающие устройства 240

7 7 Динамическая память 243

Глава 8. Арифметико-логические устройства и устройства управления 254

8 1 Классификация арифметико-логических устройств 254

8 2 Языки описания операционных устройств 256

8 3 Устройства управления 258

8 4 Управляющие автоматы со схемной логикой 261

8 5 Структурный синтез управляющего автомата со схемной логикой 264

8 6 Синтез микропрограммного автомата с программируемой логикой 267

8 7 Центральное устройство управления 273

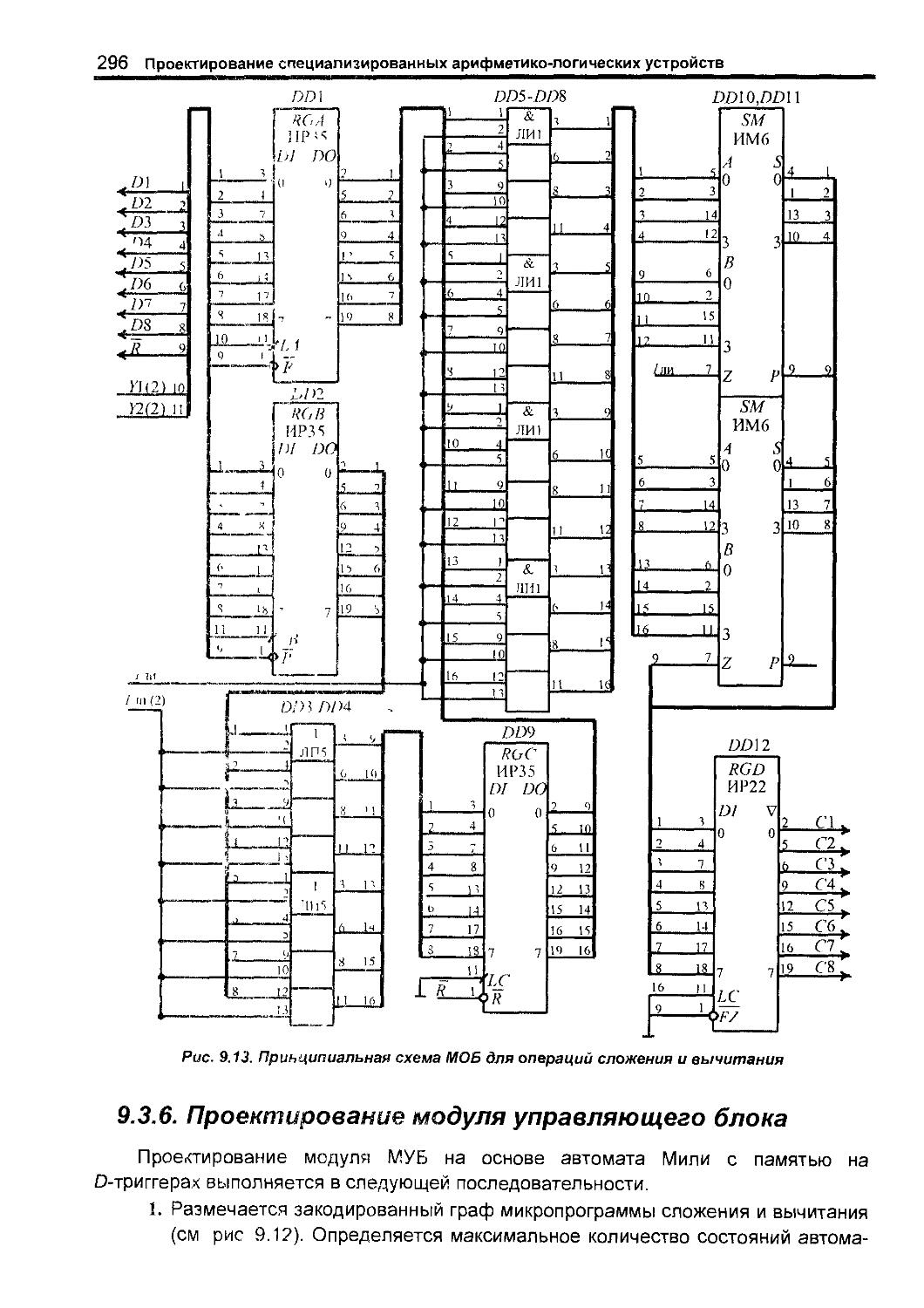

Глава 9. Проектирование специализированных арифметико-логических устройств 277

9 1 Реализация операции сложения 277

9 2 Реализация операции вычитания 285

9 3 Реализация операций сложения и вычитания 291

9 4 Реализация операции умножения 299

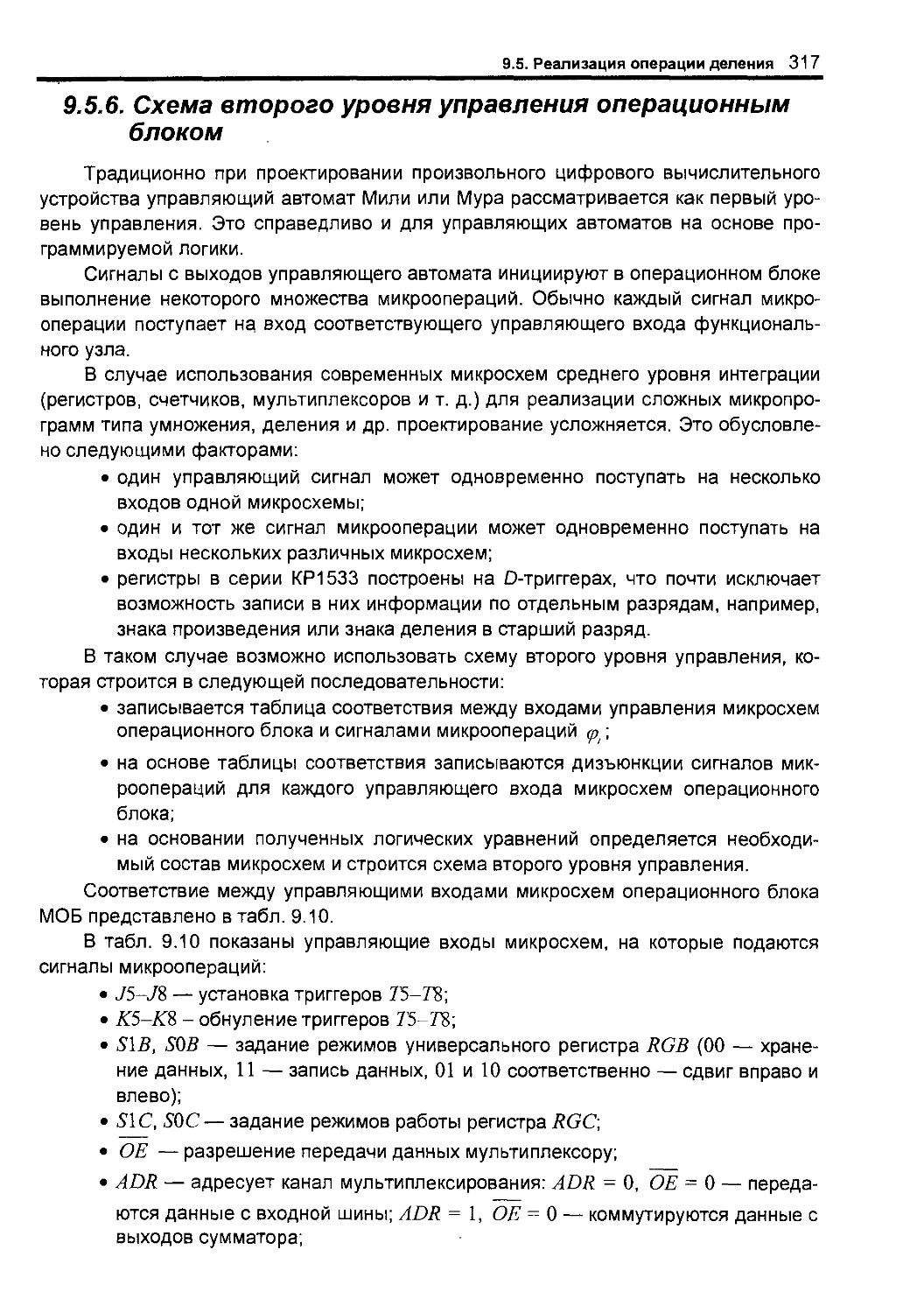

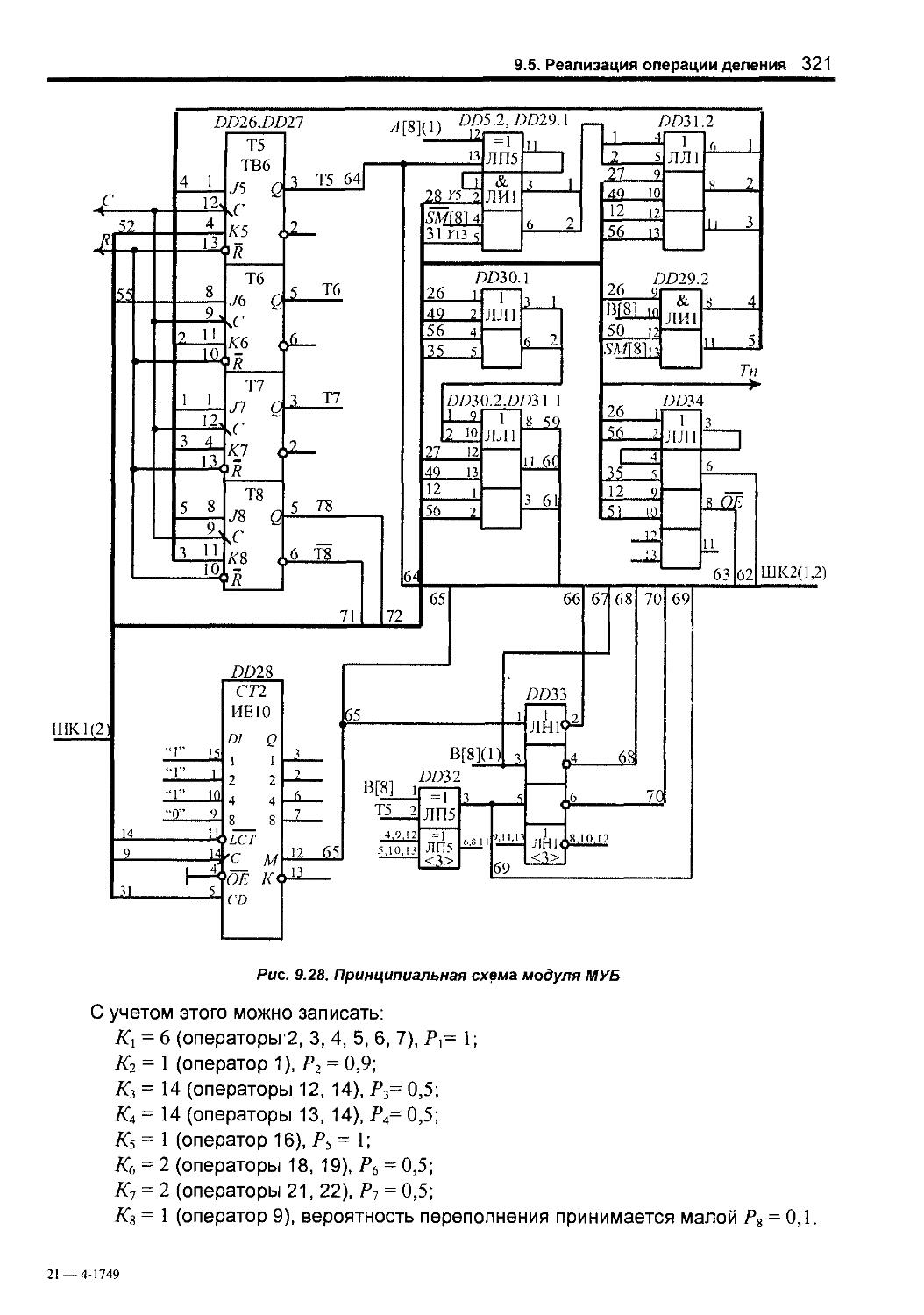

9 5 Реализация операции деления 308

Глава 10. Микропроцессоры 323

10 1 Общая характеристика процессоров и микропроцессоров 323

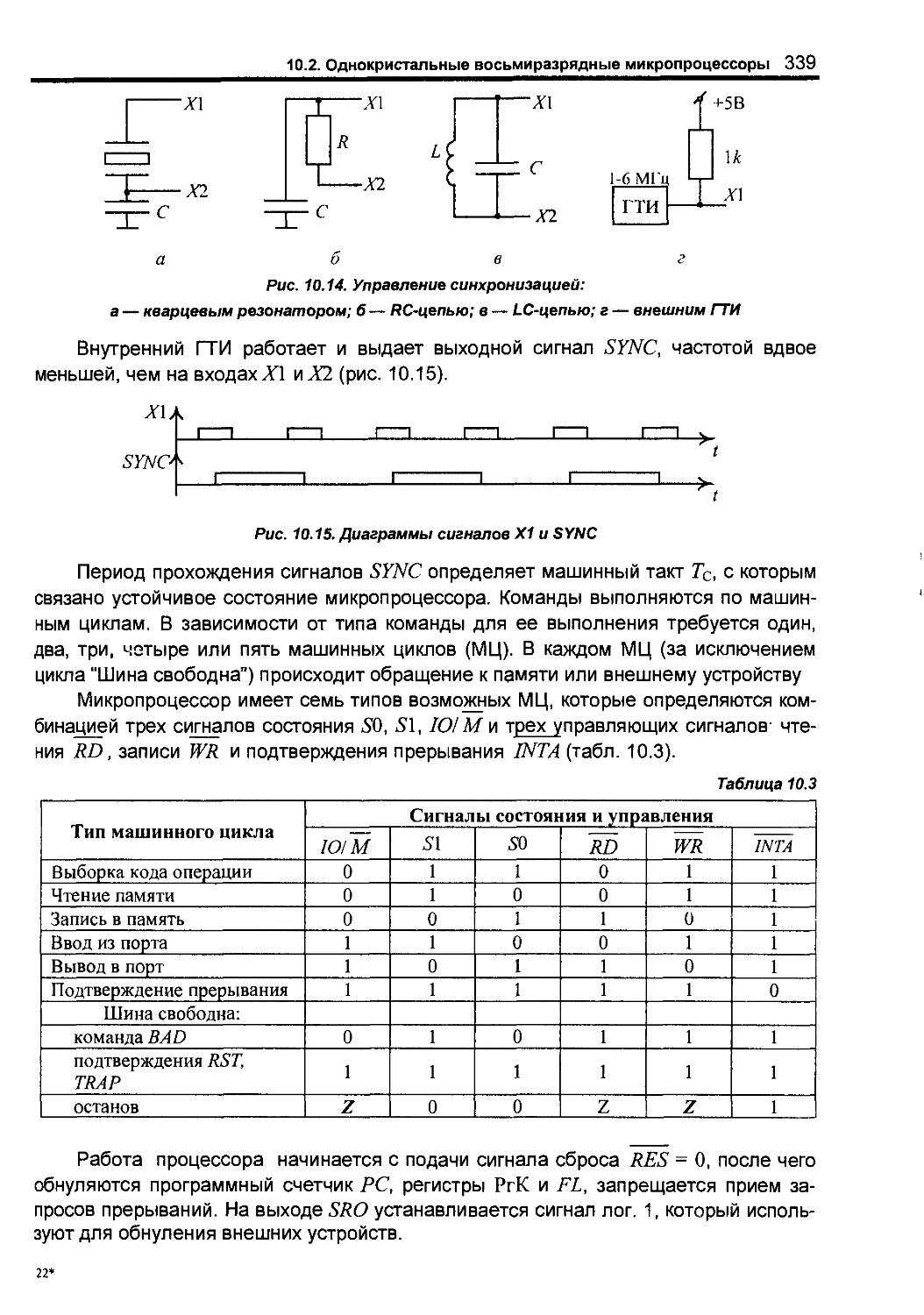

10 2 Однокристальные восьмиразрядные микропроцессоры 335

10 3 Однокристальные шестнадцатиразрядные микропроцессоры 368

10 4 Арифметические сопроцессоры 376

10 5 Суперскалярные 32-разрядные микропроцессоры с C/SC-архитектурой 378

10 6 Суперскалярные микропроцессоры с R/SC-архитектурой 390

Глава 11. Интерфейсы микропроцессорных систем 395

111 Общая характеристика микропроцессорных систем 395

112 Общая характеристика интерфейсов 401

113 Интерфейсные микросхемы 406

114 Программируемые интерфейсные контроллеры 417

Глава 12. Проектирование печатных плат 434

12 1 Основные определения 434

12 2 Виды печатных плат и кабелей 434

12 3 Материалы для печатных плат 436

12 4 Входной контроль и механическая обработка печатных плат 437

12 5 Чертеж печатной платы 439

12 6 Изготовление оригиналов и фотошаблонов 446

Содержание 5

12.7. Типовые процессы изготовления печатных плат.............452

12.8. Последовательность технологических процессов изготовления печатных плат................................454

Глава 13. Конструкторская документация............................457

13.1. Виды конструкторской документации....................... 457

13.2. Общие требования к оформлению проектов..................458

13.3. Обозначение стандартов ЕСКД.............................458

13.4. Обозначение конструкторских документов..................459

13.5. Форматы.................................................460

13.6. Основные надписи и порядок их заполнения................461

13.7. Конструкторские изделия.................................464

13.8. Стадии разработки конструкторской документации..........467

13.9. Правила оформления пояснительной записки................468

Глава 14. Требования к выполнению схем и иллюстративных документов.........................................480

14.1. Понятие схем и общие требования к их выполнению.........480

14.2. Правила выполнения схем цифровой вычислительной техники.488

14.3. Условные графические обозначения элементов цифровой техники в схемах...........................496

14.4. Требования к выполнению иллюстративных документов.......510

Глава 15. Программная документация 518

15.1. Программное обеспечение систем обработки информации.....518

15.2. Единая система программной документации..................521

15.3. Обозначение программных документов.......................523

15.4. Виды программ и программной документации................524

15.5. Стадии разработки программ и программной документации...524

15.6. Требования к содержанию и оформлению....................525

15.7. Символы в схемах алгоритмов, программ, данных и систем...530

Список литературы..................................................542

Приложения.........................................................546

А. Образцы форм документов проекта.............................545

Б. Соотношения размеров условных графических обозначений на модульной сетке...........................................552

В. Обозначения функций элементов, меток выводов...............553

Г. Примеры чертежей печатной платы............................559

Д. Условные графические обозначения элементов цифровой техники.562

Е. Перечень стандартов........................................567

Ж. Словарь общих терминов.....................................569

6 Введение

Введение

Компьютерная схемотехника — это научно-техническая дисциплина, которая изучает теоретические методы анализа и синтеза схем компьютеров (электронных вычислительных машин) и способы их технической реализации. Развитие компьютерной схемотехники является основой усовершенствования архитектуры компьютеров, качественного повышения их производительности и надежности, существенного уменьшения весогабаритных показателей. Компьютеры широко используются в различных отраслях народного хозяйства.

Цель применения компьютеров заключается в информатизации общества — обеспечении повсеместного использования автоматизированных методов сбора, передачи, обработки и хранения информации. Решение проблемы информатизации обеспечивает выход страны на новый уровень цивилизации.

Данное учебное пособие предназначено для студентов, которые обучаются по специальностям “Компьютерные системы и сети", “Информационные управляющие системы и технологии”, "Программное обеспечение автоматизированных систем”. Здесь нашли отражение результаты методологических исследований по оптимизации учебного процесса, полученные на кафедре вычислительной техники Института компьютерных технологий Национального авиационного университета Украины.

В пособии изложены информационные, арифметические, логические и схемотехнические основы компьютерной схемотехники. Рассмотрены элементы и типовые функциональные узлы, а также основные устройства компьютеров: электронная память, арифметико-логические, управления и системы ввода/вывода информации. В сжатой форме представлены характеристики процессоров, микропроцессоров и компьютеров, даны определения, классификация, основные области их применения. Рассмотрен также процесс проектирования печатных плат. Особое внимание уделено правилам разработки конструкторской и программной документации, а также требованиям к выполнению схем и иллюстративных документов.

Авторы благодарны рецензентам — директору Института проблем моделирования в энергетике НАН Украины, члену-корреспонденту НАН Украины, профессору В. Ф. Евдокимову и заведующему кафедры “Вычислительная техника” НТУУ “КПИ”, доктору технических наук, профессору Г. М. Луцкому за ценные замечания.

Авторы выражают благодарность кандидату технических наук А. А. Бабич за помощь в подготовке книги к изданию, а также ответственному редактору издательства “МК-Пресс” Юрию Шпаку, выполнившему всю работу по обработке авторского материала.

Перечень используемых сокращений 7

Перечень используемых сокращений

А аккумулятор

АК арифметический канал

АЛБ арифметико-логический блок

АЛУ арифметико-логическое устройство

АЦП аналого-цифровой преобразователь

АШ арбитр шины

БАД буфер адреса данных

БМУ блок местного управления

БИС большая интегральная схема

БИФ блок интерфейса

ВЗУ внешнее ЗУ

ГПК гибкий печатный кабель

ГПП гибкая печатная плата

ГТИ генератор тактовых импульсов

ДПП двусторонняя печатная плата

ЕСКД единая система конструкторской документации

ЕСПД единая система программной документации

ЗГ задающий генератор

ЗУ запоминающее устройство

И2Л интегральная инжекционная логика

ИМС интегральная микросхема

КВВ канал ввода-вывода

КМОП комплементарная МОП-структура

КОП код операции

КПДП контроллер ПДП

КПР контроллер прерываний

КПТО комплекс программ технического обслуживания

KLLI контроллер шины

МЕП структура “металл-полупроводник"

МИС малая интегральная схема

МК микрокоманда

МНОП структура "металл-нитрид-оксид-полупроводник”

МОП структура “металл-оксид-полупроводник”

МП микропроцессор

МПА микропрограммный автомат

МПК микропроцессорный комплект

8 Введение

мпп многослойная печатная плата

МПС микропроцессорная система

мц мэт машинный цикл многоэмиттерный транзистор

СБИС сверхбольшая интегральная схема

НГМД НЖМД НМЛ накопитель на гибких магнитных дисках накопитель на жестких магнитных дисках накопитель на магнитных лентах

НОД ОА накопитель на оптических дисках операционный автомат

ОЗУ оперативное ЗУ

ок открытый коллектор

оп ОПП оперативная память односторонняя печатная плата

ОС операционная система

ОУ операционный усилитель

ПД пдп ПЗУ переключатель Джозефсона прямой доступ к памяти постоянное ЗУ

пмк память микрокоманд

ПУ периферийное (внешнее) устройство

ППА ППЗУ программируемый параллельный адаптер программируемое ПЗУ

ппи ппп программируемый последовательный интерфейс пакеты прикладных программ

пт программируемый таймер

ПЭВМ персональная ЭВМ

РОН РПЗУ-ЭС РПЗУ-УФ регистр общего назначения репрограммируемое ПЗУ с электрическим стиранием репрограммируемое ПЗУ со стиранием данных ультрафиолетовым лучом

рт распределитель тактов

СДНФ СКНФ совершенная дизъюнктивная нормальная форма совершенная конъюнктивная нормальная форма

сис средняя интегральная схема

сои СУП сш система обработки информации схема ускоренного переноса системная шина

Перечень используемых сокращений 9

тз техническое задание

тл транзисторная логика

ТТЛ транзисторно-транзисторная логика

ттлш транзисторно-транзисторная логика с диодами Шотки

УА управляющий автомат

УВВ устройство ввода-вывода информации

УВв устройство ввода информации

УВыв УГО УУ устройство вывода информации условное графическое обозначение устройство управления

ФАМК формирователь адреса МК

ЦАП ЦП ЦУУ ША цифро-аналоговый преобразователь центральный процессор центральное устройство управления шина адреса

ШВВ шина ввода-вывода

ШД ШУ ЭВМ шина данных шина управления электронная вычислительная машина

эп эсл элемент памяти; эмиттерный повторитель эмиттерно-связная логика

10 Основы теории компьютерной схемотехники

Глава 1

Основы теории компьютерной схемотехники

1.1. Информационные основы компьютерной схемотехники

1.1.1. Информатика, информация, сигналы и их представление

Широкое применение компьютеров способствует научно-техническому развитию страны. Сфера использования компьютеров охватывает практически все виды человеческой деятельности.

Компьютер — это программно управляемая физическая система, предназначенная для алгоритмической обработки информации, представленной сигналами.

В широком смысле слова информация является отражением реального мира. Информация — это единственный неубывающий ресурс жизнеобеспечения. Более того: ее объем в настоящее время удваивается ежегодно. Информация, подготовленная для обработки на компьютерах, называется данными.

Информационный процесс включает в себя такие этапы:

I . сбор информации от различных источников и представление ее в форме, необходимой для ввода в компьютер;

2 . передачу (пересылку) информации от источника к приемнику;

3 . хранение — процесс передачи информации во времени;

4 . обработку — систематическое выполнение операций над данными;

5 . выдачу результата обработки пользователю.

На всех этих этапах используют средства компьютерной схемотехники. К информации предъявляют следующие требования:

• корректность (однозначность восприятия);

• ценность (полезность) и оперативность (актуальность);

• точность, достоверность и устойчивость (способность реагировать на изменения исходных данных);

• достаточность (полнота) — наличие минимально необходимого объема информации для принятия правильного решения.

Структуру и общие свойства информационных процессов изучают в информатике, которая включает:

• теорию информации;

• алгоритмические, программные и компьютерные средства обработки информации;

1.1. Информационные основы компьютерной схемотехники 11

• архитектуру компьютеров, системы искусственного интеллекта, вычислительные сети и т.д.

В теории информации изучают процессы передачи, преобразования и хранения информации, в том числе:

• методы определения количества информации в сообщении;

• рациональные способы представления информации с помощью различных символов (букв, цифр и т.д.);

• способы формирования, обнаружения и оценки параметров информационных процессов.

Упорядоченную последовательность символов (букв, цифр, математических знаков, предназначенных для передачи информации), закодированную в материальной форме, называют сообщением.

Информационное сообщение всегда связано с источником и приемником информации, соединенных каналом передачи (рис. 1.1).

Рис. 1.1. Информационная модель канала передачи

Источником и приемником информации могут быть как люди, так и технические устройства (компьютеры, датчики, индикаторы и др.). Каналом передачи (связи) называется совокупность устройств, имеющих один вход и один выход, предназначенных для передачи информации на расстояния. Сообщения'могут иметь различные формы: звука, текста, изображения, электрического напряжения от датчиков (например, от термопар).

Информационные сообщения размещают на машинных носителях информации. Носитель информации — это любая запоминающая предметная среда, предназначенная для записи и хранения информации с целью ее непосредственного ввода в компьютер. Носитель информации является промежуточным звеном между компьютером и первичным документом, содержащим числовые данные, текстовые материалы, схемы, графики, различные измерения.

Хранение сообщений — это, как правило, три вида операций: запись, собственно хранение и считывание. Информация записывается в носитель посредством изменения физических или механических свойств запоминающей среды. Данные считываются посредством преобразования их в электрические сигналы. Считают, что в носителе информации сигнал хранится в закодированной форме.

Носители информации различаются по следующим признакам:

• средой накопления: непрерывные (магнитные ленты и диски) и дискретные, где каждой хранимой единице данных отводится свой дискретный участок или элемент (ферритовые сердечники, перфокарты, перфоленты, триггеры, криотроны и т.д );

• типом материала: бумага с текстом или рисунком; бумажные перфоленты, перфокарты; магнитные ппенки, магнитные ленты и диски; полупроводниковые схемы памяти;

12 Основы теории компьютерной схемотехники

• способом считывания данных: механические, оптические, магнитные, электрические;

• конструктивным исполнением: ленточные, дисковые, электронные и др.

Для передачи информации от источника к приемнику сообщение преобразовывают в сигналы. Согласно ДСТУ 2938-94 “сигнал — это изменение физической величины, используемой для передачи данных”. Таким образом, сигнал образуется на основе некоторой физической величины (электромагнитные или акустические колебания, электрическое напряжение и др.), традиционно называемой энергетическим носителем, и изменения одного или нескольких ее параметров (амплитуды, частоты, фазы, длительности и др.) по закону передаваемой информации. Считают, что сигнал — это материально-энергетическое воплощение сообщения. Посредством совокупности сигналов можно представить любое сложное сообщение. Сигнал может преобразовываться без изменения смысла информации из одной физической величины в другую, более удобную для передачи по каналу связи и обработки в схемах компьютера. Изменение параметров физической величины по закону передаваемого сообщения называют модуляцией, а изменяемые параметры — информативными

Сигналы классифицируют по таким признакам:

• степени определенности ожидаемых значений — случайные и детерминированные;

• структуре временного изменения — непрерывные и дискретные;

• роли переданной информации в компьютеры — адреса, данные и управления;

• особенностям спектрального представления — низкочастотные и высокочастотные, узкополосные и широкополосные;

• способу преобразования — кодированные, декодированные, усиленные, дискретизированные и т.д.;

• принадлежности к виду связи — телеграфные, телефонные, радиолокационные, междумашинные и внутримашинные;

• характеру изменения кодированных сигналов в синхронизированные моменты времени-— потенциальные и импульсные.

В процессе передачи сигналов от источника к приемнику физические величины и способы их модуляции могут многократно изменяться, но содержание сообщения остается неизменным, поскольку оно определяется только законом модуляции.

Для информационного обмена используют знаки различного ранга:

• первый ранг — символы. Символ — это элементарная единица сообщения. Если число различных символов ограничено, то их совокупность называют алфавитом (например, буквы латинского алфавита, двоичные символы 0 и 1 — в технических устройствах);

• второй ранг — слова (группы символов), из которых строятся фразы и выражения.

В общем случае способ формализованного описания различных сигналов (и соответственно сообщений) называется представлением информации. В теории информации рассматривают не физическое, а математическое представление сиг

1.1. Информационные основы компьютерной схемотехники 13

налов, то есть их описание с помощью различных функций, формул, графиков, законов распределения вероятностей.

Наиболее распространенными способами представления сигналов являются временной, спектральный, статистический. Во многих случаях информация о протекании некоторого физического процесса поступает от соответствующих датчиков в виде электрических сигналов, которые непрерывно изменяются во времени. Различают следующие разновидности сигналов, описываемых временной функцией y(f).

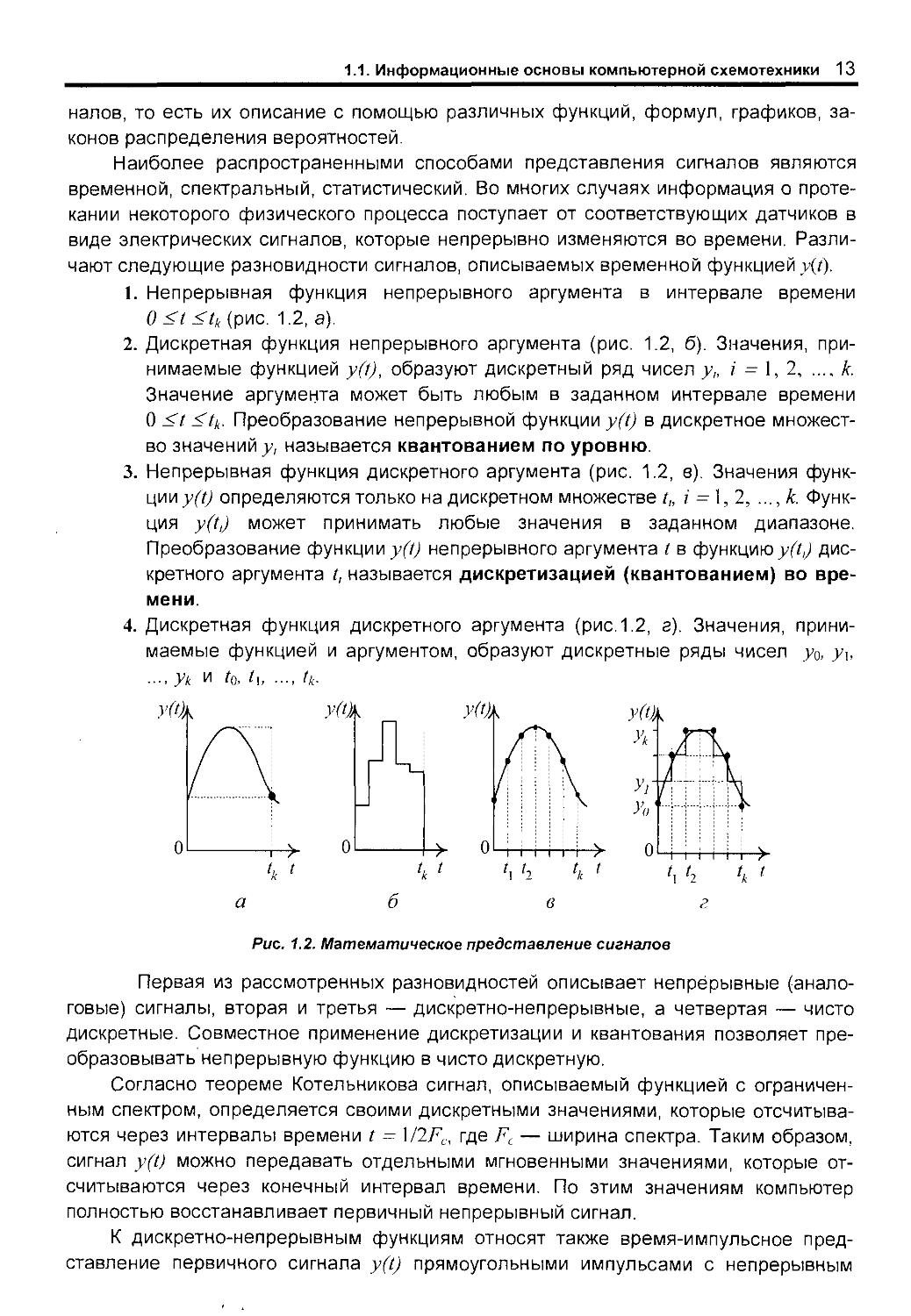

1. Непрерывная функция непрерывного аргумента в интервале времени О <t <tk (рис. 1.2, а).

2. Дискретная функция непрерывного аргумента (рис. 1.2, б). Значения, принимаемые функцией y(t), образуют дискретный ряд чисел i = 1, 2, .... к. Значение аргумента может быть любым в заданном интервале времени О <t <tk. Преобразование непрерывной функции y(t) в дискретное множество значений)/, называется квантованием по уровню.

3. Непрерывная функция дискретного аргумента (рис. 1.2, в). Значения функции y(t) определяются только на дискретном множестве th i = 1,2, ..., к. Функция y(tt) может принимать любые значения в заданном диапазоне. Преобразование функции y(t) непрерывного аргумента t в функциюy(t,) дискретного аргумента t, называется дискретизацией (квантованием) во времени.

4. Дискретная функция дискретного аргумента (рис. 1.2, г). Значения, принимаемые функцией и аргументом, образуют дискретные ряды чисел у0, уь , у к и to, t\, ..., tk.

Рис. 1.2. Математическое представление сигналов

Первая из рассмотренных разновидностей описывает непрерывные (аналоговые) сигналы, вторая и третья — дискретно-непрерывные, а четвертая — чисто дискретные. Совместное применение дискретизации и квантования позволяет преобразовывать непрерывную функцию в чисто дискретную.

Согласно теореме Котельникова сигнал, описываемый функцией с ограниченным спектром, определяется своими дискретными значениями, которые отсчитываются через интервалы времени t = \/2Fc, где Fc — ширина спектра. Таким образом, сигнал y(t) можно передавать отдельными мгновенными значениями, которые отсчитываются через конечный интервал времени. По этим значениям компьютер полностью восстанавливает первичный непрерывный сигнал.

К дискретно-непрерывным функциям относят также время-импульсное представление первичного сигнала y(t) прямоугольными импульсами с непрерывным

14 Основы теории компьютерной схемотехники

информативным параметром (,/Т. где /, — длительность импульсов, пропорциональная значению сигнала; Т — период повторения импульсов (рис. 1.3, а).

Рис. 1.3. Представление сигналов:

а — время-импульсное; 6 — число-импульсное; в — импульсно-кодовое

При число-импульсном представлении (рис. 1.3, б) информативным параметром является количество импульсов за период. В телеграфной связи используют импульсно-кодовое представление символов. Например, в коде Бодо передачу символов реализуют последовательной посылкой во времени пяти импульсов разной полярности, как показано на рис. 1.3, е для букв А и Б.

В компьютерной схемотехнике используют разрядно-цифровое (или просто цифровое) кодирование, в котором первичный сигнал представляется группой символов, отображайэщих значения цифр 0 и 1 двоичной системы счисления электрическими сигналами, например, импульсами. Наличие импульса соответствует цифре 1, отсутствие— 0. Разряды двоичного числа характеризуются весом, кратным степени двойки — 1, 2, 4, 8, ... (в направлении от младших к старшим разрядам), например. для четырехразрядного двоичного числа имеем:

.х - ,т3 л:2 • Л', • т0 = То • 21 -г х2 • Т + л', 21 т ,у() 2° =

= л'з -8 <- х2 • 4 т л', 2 + л'о • I

Если двоичное число х2 -- 1 101, то получим следующий десятичный эквивалент:

Хю == 1-8+ 1-4+ 0-2+ 1-1 = 13

Цифровой код передают последовательно во времени (последовательный код) с помощью одного канала передачи (рис. 1.4. а) или одновременно (параллельный код) с помощью многоканальной передачи (рис.1.4, б).

На практике последовательный код используют при передаче информации на большие расстояния (например, между компьютерами), а параллельный код — при передаче информации на малые расстояния (например, внутримашинные).

Рис. 1.4. Передача информации: а — последовательным кодом; б — параллельным кодом

1.1. Информационные основы компьютерной схемотехники 15

1.1.2. Информационные меры

В теории передачи и преобразования информации установлены информационные меры количества и качества информации — семантические, структурные, статистические.

Семантический подход позволят выделить полезность или ценность информационного сообщения. В структурном аспекте рассматривают строение массивов информации и их измерение простым подсчетом информационных элементов или комбинаторным методом. Структурный подход используют для оценки возможностей информационных систем вне зависимости от условий их применения. При использовании структурных мер информации учитывают только дискретное строение сообщения, количество содержащихся в нем информационных элементов, связей между ними. При структурном подходе различают геометрическую, комбинаторную и аддитивную меры информации.

Геометрическая мера определяет параметры геометрической модели информационного сообщения (длина, площадь, объем) в дискретных единицах. Эту меру применяют как для оценки информационной емкости всей модели, так и для оценки количества информации в одном сообщении.

В комбинаторной мере количество информации 1 определяют количеством комбинаций элементов (символов), которые совпадают с числом:

• сочетаний из q элементов по п:

1 = -^--, п\(q - п)!

например, для множества цифр 1, 2, 3, 4 можно составить шесть сочетаний по две цифры: 12, 13, 14, 23, 24, 34;

• перестановок I = q!, например, для множества букв а, в, с можно получить шесть перестановок: аве, асе, вас, вса, сав, сва\

• размещений с повторениями из q элементов по it.

I = q".

Например, для q = 0, 1 и а = 3 имеем: ООО, 001, 010, 01 1, 100, 101, 110, 111.

Широкое распространение получила аддитивная мера. Пусть N — число равновероятных сообщений, а — их длина, q — число букв алфавита, используемого для передачи информации. Количество возможных сообщений длины п равняется числу размещений с повторениями

N-~-q. (1.1)

Эту меру наделяют свойством аддитивности, чтобы она была пропорциональна длине сообщения и позволяла складывать количество информации ряда источников. Для этого Хартли предложил логарифмическую функцию как меру количества информации:

I = log N = п log q. (1.2)

Количество информации, которое приходится на один элемент сообщения, называется энтропией:

H = - = log(/. (1.3)

п

16 Основы теории компьютерной схемотехники

Основание логарифма зависит от выбора единицы количества информации. Если для алфавита используют двоичные цифры 0 и 1, то за основание логарифма принимают q = 2, в результате чего I = п log2 2 = п. При длине п = 1 получают Z = 1 и это количество информации называют битом.

Передача сообщения длиной п = 1 эквивалентна выбору одного из двух возможных равновероятных сообщений — одно из них равно единице, другое — нулю. Двоичное сообщение длины п содержит п битов информации. Если основание логарифма равно 10, то количество информации измеряется в десятичных единицах — дитах, причем 1 дит = 3,32 бита. Например, текст составлен из 32 букв алфавита и передается последовательно по телетайпу в двоичном коде. При этом количество информации I = log2jV = log232 = 5 битов. Далее используются логарифмы с основанием два.

В общем случае сообщения появляются с разной вероятностью. Статистическая мера использует вероятностный подход к оценке количества информации. Согласно Шеннону каждое сообщение характеризуется вероятностью появления, и чем она меньше, тем больше в сообщении информации. Вероятность конкретных типов сообщений устанавливают на основе статистического анализа.

Пусть сообщения образуются последовательной передачей букв некоторого алфавита xj... х„ xq с вероятностью появления каждой буквы р(х\) = р},

р(х) = р„ р(х:1) = рч, при этом выполняется условие:р< + ... +р, + ... + рч = 1.

Множество с известным распределением элементов называют ансамблем. Согласно Шеннону количество информации, которое содержится в сообщении х„ рассчитывают по формуле

/(*,) = log—• (1.4)

Р,

Для абсолютно достоверных сообщений р, = 1, количество информации 1(х) = 0; при уменьшении значенияр, количество информации увеличивается.

Пусть в ансамбле все букры алфавита хь ..., х„ ... , хч — равновероятны, то есть р\ = р2 = ... = pq = \/q, и статистически независимы. Тогда количество информации в сообщении длиной п букв с учетом выражения (1.4)

” ”11 1

/ = УЛх,) = У log—= log—+ ...+ log— = n\ogq, Zf P, P-. A

что совпадает с мерой Хартли в соответствии с выражениями (1.1) и (1.2).

Согласно Шеннону информация — это снятие неопределенности, что понимают следующим образом. До опыта событие (например, появление буквы х,) характеризуют малой начальной вероятностью рн, которой соответствует большая неопределенность. После опыта неопределенность уменьшается, поскольку конечная вероятность рк > рн. Уменьшение неопределенности рассчитывают как разность между начальным 7Н и конечным 1К значениями количества информации. Например, для рн = 0,1 и рк = 1 получим:

А/ = IH -1к = log —— log — = log 10 - log 1 - 3,32 бит.

Рн Рк

1.1. Информационные основы компьютерной схемотехники 17

Пусть сложное сообщение характеризуется алфавитом из букв хь х2, ..., xq, их вероятностями р\, р2, ..., рч и частотой появления каждой буквы т,, т2, .... mq. Все сообщения статистически независимы, при этом + т2 + ... + mq = т. Общее количество информации для всех q типов сообщений с учетом выражения (1.4)

я 1

h = У-Jog- м Р,

Среднее значение количества информации на одно сообщение (энтропия) согласно формуле Шеннона

гг Л: V"1 mi 1 1 V"1 1 1

^= —= у—log—= XAlog—, (1.5)

- ,=i - А ,=1 А

где при большом значении т отношение mjm характеризует вероятность р, каждой буквы. Выражение logl//>, рассматривают как частную энтропию, которая характеризует информативность буквы х,, а энтропию Н— как среднее значение частных энтропий. При малых значениях р, частная энтропия велика, а с приближением р. к единице она приближается к нулю (рис. 1.5, а).

Функция г| = (pj = р, logl/p, отражает вклад буквы х, в энтропию Н. Как видим, при р, = I эта функция равна нулю, затем возрастает до своего максимума и при уменьшении р, приближается к нулю. Функция q(p) при значении р, = 0,37 имеет максимум 0,531.

Интерес представляют сообщения с использованием двухбуквенного алфавита Х| и х2 (например, цифры 0 и 1). Поскольку при q = 2 вероятность букв алфавита Р\ + Pi = 1, то можно положить, чтор\ = р и р2 = 1 -р. Тогда энтропию определяют соотношением

Н = ?7() + 7(Рг) = Р log - + (1 - р) log 1 , р О-/’)

график которой показан на рис. 1.5, б. Он образуется суммированием двух графиков, определяющих энтропию каждой из двух букв. Из графиков видно, что при р = 0 или р = 1 энтропия равна нулю и неопределенность полностью снимается. Это означает, что с вероятностью, равной единице, можно знать, каким будет следующее сообщение.

Рис. 1.5. Гоафики функции Н: а — для частной энтропии; б — для двоичных сообщений

2 — 4-1749

0,2 0,4 0,6 0,8 1,0 Р

18 Основы теории компьютерной схемотехники

Энтропия двухбуквенных сообщений достигает максимального значения, равного 1 биту, при р = 0,5, и ее график симметричен относительно этого значения. Это тот случай, когда наиболее трудно предугадать, какое сообщение будет следующим, — то есть ситуация наиболее неопределенная.

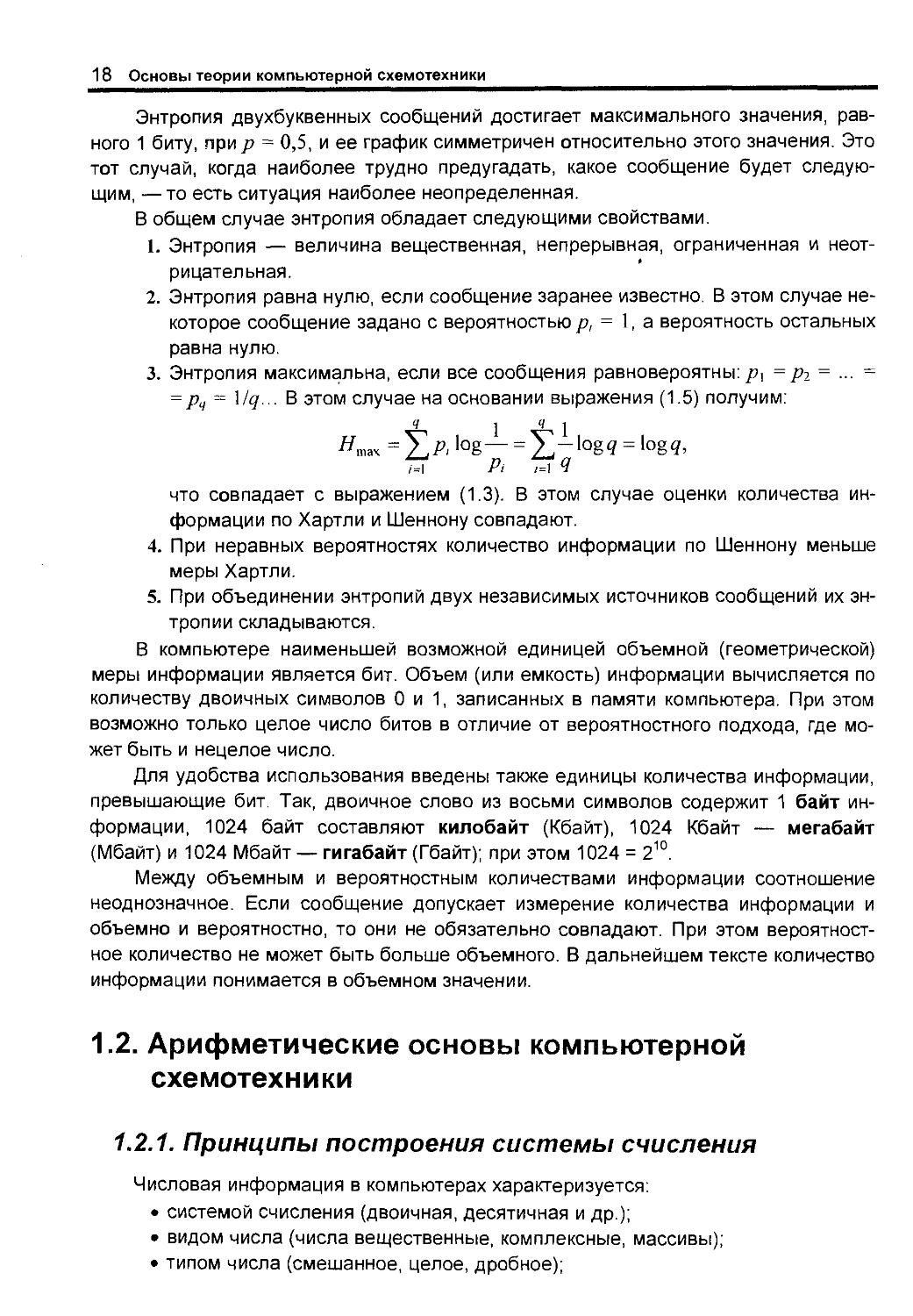

В общем случае энтропия обладает следующими свойствами.

1. Энтропия — величина вещественная, непрерывная, ограниченная и неотрицательная.

2. Энтропия равна нулю, если сообщение заранее известно. В этом случае некоторое сообщение задано с вероятностью р, = 1, а вероятность остальных равна нулю.

3. Энтропия максимальна, если все сообщения равновероятны: рх = р2 = ... = = рч = \lq... В этом случае на основании выражения (1.5) получим:

ч 1 4 1

•Og—= X-1Qg9 = log^

Pi 7^ Я

что совпадает с выражением (1.3). В этом случае оценки количества информации по Хартли и Шеннону совпадают.

4. При неравных вероятностях количество информации по Шеннону меньше меры Хартли.

5. При объединении энтропий двух независимых источников сообщений их энтропии складываются.

В компьютере наименьшей возможной единицей объемной (геометрической) меры информации является бит. Объем (или емкость) информации вычисляется по количеству двоичных символов 0 и 1, записанных в памяти компьютера. При этом возможно только целое число битов в отличие от вероятностного подхода, где может быть и нецелое число.

Для удобства использования введены также единицы количества информации, превышающие бит. Так, двоичное слово из восьми символов содержит 1 байт информации, 1024 байт составляют килобайт (Кбайт), 1024 Кбайт — мегабайт (Мбайт) и 1024 Мбайт — гигабайт (Гбайт); при этом 1024 = 210.

Между объемным и вероятностным количествами информации соотношение неоднозначное. Если сообщение допускает измерение количества информации и объемно и вероятностно, то они не обязательно совпадают. При этом вероятностное количество не может быть больше объемного. В дальнейшем тексте количество информации понимается в объемном значении.

1.2. Арифметические основы компьютерной схемотехники

1.2.1. Принципы построения системы счисления

Числовая информация в компьютерах характеризуется:

• системой счисления (двоичная, десятичная и др.);

• видом числа (числа вещественные, комплексные, массивы);

• типом числа (смешанное, целое, дробное);

1.2. Арифметические основы компьютерной схемотехники 19

• формой представления числа (место запятой) — с природной (переменной), фиксированной, плавающей запятой;

• разрядной сеткой и форматом числа;

• диапазоном и точностью представления чисел;

• способом кодирования отрицательных чисел — прямым, обратным и дополнительным кодами;

• алгоритмами выполнения арифметических операций.

Системой счисления называется совокупность цифр и правил для записи чисел. Запись числа в некоторой системе счисления называется его кодом. Все системы счисления делятся на позиционные и непозиционные. Для записи чисел в позиционной системе счисления используют определенное количество графических знаков (цифр и букв), которые отличаются один от другого. Число таких знаков q называют основанием позиционной системы счисления. В компьютерах используют позиционные системы с разным основанием.

Система счисления с основанием два (цифры 0 и 1) называется двоичной, система счисления с основанием три (цифры 0, 1,2) — троичной и т.д. В системах счисления с основанием меньше десяти используют десятичные цифры, а для основания больше десяти добавляют буквы латинского алфавита — А, В, С, D, Е, F. Далее в обозначениях в случае необходимости пишут десятичный индекс, равный применяемому основанию системы счисления (табл. 1.1).

Таблица 1.1

Основание q Система счисления Знаки

2 Двоичная 0, 1

3 Троичная 0, 1,2

5 Пятеричная 0, 1,2, 3,4

8 Восьмеричная 0, 1,2, 3,4,5, 6,7

10 Десятичная 0, 1,2, 3,4, 5, 6, 7, 8,9

16 Шестнадцатеричная 0, 1,2, 3,4, 5, 6, 7, 8, 9, А, В, С, D, Е, F

В позиционных системах счисления значение каждой цифры определяется ее изображением и позицией в числе. Отдельные позиции в записи числа называют разрядами, а номер позиции — номером разряда. Число разрядов в записи числа называется его разрядностью и совпадает с длиной числа.

В непозиционных системах счисления значение каждой цифры не зависит от ее позиции. Самой известной непозиционной системой является римская, в которой используются семь знаков — I, V, X, L, С, D, М, соответствующих таким значениям:

I

1

V X L С D М

5 10 50 100 500 1000

Например: III — 3; LIX — 59; DLV — 555.

Недостатком непозиционной системы является отсутствие нуля и формальных правил записи чисел и соответственно арифметических действий с ними (хотя по традиции римскими числами часто пользуются при нумерации глав в книгах, веков в истории и др.). Система счисления должна обеспечивать:

• возможность представления любого числа в заданном диапазоне;

2*

20 Основы теории компьютерной схемотехники

• однозначность, сжатость записи числа и простоту выполнения арифметических операций;

• достижение высокого быстродействия машины в процессе обработки информации.

Число в позиционной системе можно представить полиномом:

к

Aq = ak-qk + а^_, -qk 1 +...+а0 -q' +а_, -q 1 + -q т = -q , (1.6)

i=-m

где q — основание системы счисления; q‘ — вес позиции; а, е {0, 1, - 1)} —

цифры в позициях числа; 0, 1, ..., к — номера разрядов целой части числа; -1, -2, ..., -т — номера разрядов дробной части числа.

Позиционные системы с одинаковым основанием в каждом разряде называют однородными. Поскольку на значение q нет никаких ограничений, то теоретически возможно бесконечное множество позиционных систем счисления.

На практике применяют сокращенную запись полинома (1.6) в виде последовательности цифр со знаком в зависимости от типа числа:

• для смешанного числа

Aq - +ак ак-] ... а\ а0, а_\ ... С1-т, (1.6, а)

• для целого числа Aq = +ак Я*-| Щ а0; (1.6,6)

• для правильной дроби Aq = ± 0, ... (2 _т . (1.6, в)

\ Пример 1.1

Иллюстрация записи чисел в виде последовательности цифр (1.6) и соответствующего полинома (1.5):

• двоичная система: q = 2; cq е {0, 1}:

А2 = 111,01 = 1-22 + 1-2' + 1-2°+ 0-2*' + 1 -2 2 = 7,2510;

• восьмеричная система: q = 8; а,- е {0, 1, 2, ..., 7}:

Л8 = 45,21 =4-8' + 5-8° + 2-81 + 1-8“2 = 37,26510;

• десятичная система: q = 10; а, е {0, 1, 2, ..., 9}:

А10 = 135,64 = 1 -102 + 3-101 + 5-10° + 6 10“' + 4-10“2

• шестнадцатеричная система: q = 16; cq= {0, 1, ..., F}\

Al6 = DEAB = D-161 -ь^-160 + 1-16"' + 5-16“2 = = 13-16' + 14-16° + 1-16"' + 11-16 2 = 222,10510.

Рассмотренные записи чисел показывают один из способов перевода недесятичных чисел в десятичные. При одинаковой разрядности в системах счисления с большим основанием можно записать больше разных чисел.

1.2. Арифметические основы компьютерной схемотехники 21

Достоинством двоичной системы является: простота выполнения арифметических операций; наличие надежных микроэлектронных схем с двумя устойчивыми состояниями (триггеров), предназначенных для хранения значений двоичного разряда— цифр 0 или 1. Двоичные цифры называют также битами. В двоичнодесятичной системе счисления каждая десятичная цифра записывается четырьмя двоичными разрядами (тетрадами).

Пример 1.2

Запись десятичного числа в двоично-десятичной системе:

8 7 3 2 5

Aw = 873,25 = 1000 01110011,0010 0101.

1.2.2. Перевод чисел из одной системы в другую

Для перевода целого числа из одной системы счисления в другую необходимо разделить переводимое число на новое основание по правилам исходной системы. Полученный первый остаток является значением младшего разряда в новой системе, а первое частное необходимо снова разделить. Этот процесс продолжается вплоть до получения неделимого частного. Результат записывают в порядке, обратном их получению в виде формулы (1.6, б).

Для перевода правильной дроби из одной системы счисления в другую необходимо, действуя по правилам исходной системы, умножить переводимое число на основание новой системы; от результата отделить целую часть, а оставшуюся дробную часть снова умножить на это основание. Процесс такого умножения повторяется до получения заданного числа цифр. Результат записывают как целые части произведения в порядке их получения, располагаемых в виде формулы (1.6, в).

22 Основы теории компьютерной схемотехники

Пример 1.4

Перевод правильной десяти стью до четвертого знака: 0, 1 0 1 0 Результат: А = 0,62510 = 0,10 чной дроби А = 0,625 в двоичное число с точно- 625 2_ 0; 250 2_ a-i = 1; 500 2 а_2=0; 000 2_ а-з=1; 000 <7-4 = 0. 102.

Для перевода смешанных чисел в двоичную систему требуется отдельно переводить их целую и дробную части. В записи результата целая часть перевода отделяется от дробной в соответствии с формулой (1.6, а).

Г Пример 1.5

Перевод смешанного десятичного числа А = 118,62510 в двоичное. Используя результаты перевода целого числа 118 в примере 1.3 и дробного числа в примере 1.4, запишем результат:

________________________А= 118,62510 = 1110110,10102._______________________

В восьмеричных и шестнадцатеричных числах основание системы счисления кратно степени двойки: 23 = 8; 24 = 16. По этой причине перевод этих чисел в двоичные реализуется очень просто: каждую цифру записывают тремя двоичными цифрами (триадами) для восьмеричных чисел и четырьмя двоичными цифрами (тетрадами) для шестнадцатеричного числа в направлении влево и вправо от запятой. При этом крайние незначащие нули опускаются.

Пример 1.6

Иллюстрация перевода восьмеричных и шестнадцатеричных чисел в двоичные:

Г-°-, Г-'-, Г-Л-,

А = 305,428 = 011000101,100 0102’

л—। ,_Х_, ,-5—, ^-3-^ ,-3—,

А = 1AB,EFX6 = 011110101011,111011112-

Для перевода двоичного числа в восьмеричное исходное число разбивают на триады влево от запятой; отсутствующие крайние цифры дополняют нулями. Затем каждую триаду записывают восьмеричной цифрой. Аналогично осуществляется перевод двоичного числа в шестнадцатеричное, при этом выделяют тетрады, заменяемые шестнадцатеричными цифрами.

1.2. Арифметические основы компьютерной схемотехники 23

Пример 1.7

Иллюстрация перевода двоичных чисел в восьмеричные и шестнадцатеричные:

Д-, Д_,

А = 110011,1000102 = 110011,1000102 = 63,428;

А = 110011,1000102 = 00110011,100010002 = 33,88]6

Рассмотрим правила, облегчающие расчеты с двоичными числами.

1. Необходимо знать представление десятичных чисел от нуля до 15 в системах счисления с основанием q = 2, 8, 16 и 2-10 (табл. 1.2).

Таблица 1.2

q = 10 гч II О" QO II О" q = 16 q = 2-10

0 0 0 0 0000

1 1 1 1 0001

2 10 2 2 0010

3 и 3 3 ООП

4 100 4 4 0100

5 101 5 5 0101

6 по 6 6 оно

7 111 7 7 0111

8 1000 10 8 1000

9 1001 11 9 1001

10 1010 12 А 0001 0000

11 1011 13 В 0001 0001

12 1100 14 С 0001 0010

13 1101 15 D 0001 ООП

14 1110 16 Е 0001 0101

15 1111 17 F 0001 0101

2. Необходимо знать десятичные значения чисел 2к от к = 0 до к = Ю

(табл. 1.3).

Таблица 1.3

к 0 1 2 3 4 5 6 7 8 9 10

2к 1 2 4 8 16 32 64 128 256 512 1024

3. Полезно знать следующие соотношения для двоичных целых и дробных чисел:

А = Ю0...00 = 2к, например , А = 1000 2 = 23 = 8|0; к

А = 11... 11 = 2к -1, например , А = 111112 = 25 -1 = 31|0; к

А = 0,11...И = 1-2”*, например, Л = 0,1111 = 1-2”4=| — |

'—Г' 2 Ы10

24 Основы теории компьютерной схемотехники

А ~ 0,00...01 = 2“‘, например, А = 0,00001 2 = 2-5 = — •

Двоичные дробные числа в десятичном виде записываются так: к разрядов справа от запятой определяют целое положительное число в числителе, а в знаменателе — число 2а. Например, А = 0,10112 = (11/24)10 = (11/16)10, что читается как “одиннадцать шестнадцатых”.

1.2.3. Специальные системы счисления

Рассмотренные позиционные системы счисления относят к классическим. Кроме них, в компьютерах используют ряд специальных позиционных двоичных систем, в том числе:

• систему с использованием символов 0, -1, или_1, -Г, для удобства символ -1 обозначают как 1 ; систему с символами 1 и 1 называют системой счисления (1, 1);

• системы с отрицательным основанием q < -1 и символами 0, 1, ...,(<?- 1); систему с основанием q = -2 и символами 0, 1 называют минус-двоичной;

• избыточную систему с основанием q и количеством символов больше q, например, при q = 2 используют символы (1,0, 1), такую систему называют также симметричной знакоразрядной.

Преимуществом специальных систем счисления является упрощение и ускорение выполнения ряда арифметических операций (сложение, вычитание, умножение, деление) и представление единым кодом положительных и отрицательных чисел без дополнительного знакового разряда. Недостатком специальных систем является сложность правил перевода их в классические системы счисления и наоборот, а также неоднозначное представление ряда чисел.

Если в формуле (1.6) учесть, что символы а, принимают значение 1 или 1, то для основания q = 2 число А = 99|0 будет иметь вид 1111111. В системе чисел (1,1) отсутствует символ “нуль”, поэтому некоторые целые и дробные числа в ней не могут быть представлены конечным множеством символов. Например, десятичное чис-ло_ А =_20|0 в системе чисел (1,1) записывается как^ бесконечное число 11111,111 ..., что обуславливает погрешность в системе (1, 1). В то же время есть числа, которые не имеют единого изображения.

В минус-двоичной системе может быть представлено любое положительное или отрицательное число. Например, для q = -2, п = 4 с учетом формулы (1.6): А = 5ю = 0101 (_2); А = -5ю =1111(_2). Некоторые числа представлены неоднозначно и только бесконечными дробями: А = 1/3 = 0,010101... или А = 1,101010...

Избыточная двоичная система связана с обычной соотношением:

2= £ 2' = 2* -1 = 100...01. к '=0 к

На основании выражения (1.6) осуществляется переход от обычной двоичной системы к избыточной с символами 1,0, 1 и наоборот. Избыточная система имеет следующие свойства:

1.2. Арифметические основы компьютерной схемотехники 25

• одно и то же число не имеет единой записи: А = 12ю = 011002 — 10 1 00, = = 11100;

• положительные и отрицательные числа изображаются без_использования дополнительного знакового разряда: А = 13|0 = 011012 = 10101; А = -1310 = = -011012= 10101 (при смене знака достаточно заменить в записи числа 1 на 1 и наоборот);

• возможно уменьшение количества единиц в записи числа, что позволяет упростить и ускорить выполнение арифметических операций, особенно сложение и вычитание.

Преобразование двоичных чисел в избыточную систему с минимальным числом единиц в разрядах осуществляют так. На первом этапе все комбинации в записи числа вида 01. ..11 заменяют равнозначной комбинацией вида_10...01 с тем же числом разрядов; затем выполняют замену сочетаний 11 на 01 и 11 на 0 1, например:

А = 10 0111 0 01Н0И012 = 10100101 ООП 011 =10100101000101. 1 1 з

Количество единиц в записи числа уменьшилось с десяти до четырех.

1.2.4. Выбор системы счисления

В компьютерах в основном используют однородные позиционные системы счисления. При выборе основы q этих систем учитывают такие показатели.

1. Наличие физических элементов для изображения цифр системы в виде одного из q состояний, например, разницы напряжений. Уменьшение числа состояний упрощает физический элемент, поэтому наиболее приемлемой является двоичная система.

2. Экономичность системы счисления. Система с большим основанием q обеспечивает представление определенного числа меньшим количеством разрядов. Однако при этом усложняется построение физического элемента с большим числом состояний.

Эффективность системы счисления с основанием оценивается количеством цифровых разрядов D„ необходимых для изображения определенного числа с длиной то есть D, = qrn,. При этом учитывается, что уменьшение значения D, приводит к уменьшению электронных схем для представления чисел в компьютерах.

Для представления любого десятичного числа длиной, например, «ю = 6 используют Di0 = (fio’Hio = Ю-6 = 60 цифроразрядов. В двоичной системе для представления того же числа (с учетом соотношения п2 = З-ию) требуется иметь D2 - q2-3-n]0 = 2-3-6 = 36 цифровых разрядов.

Наиболее экономичной является система с основанием q = 2,73 ... « 3. Двоичная система по экономичности уступает троичной на 5,8%, однако имеет более надежные физические элементы. Кроме того, для запоминания цифр троичной системы 0, 1, 2 используют два двоичных физических элемента. Из этого следует, что самой эффективной является двоичная система счисления.

26 Основы теории компьютерной схемотехники

3. Трудоемкость и быстродействие выполнения арифметических операций. Чем меньше основание q, тем меньше цифр принимают участие в вычислении данных и тем выше быстродействие компьютера. Например, быстродействие машины в двоичной системе превышает быстродействие в троичной на 26,2%, а в десятичной — в 2,7 раза.

4. Наличие формального математического аппарата для анализа и синтеза цифровых схем. Таким аппаратом для двоичных элементов является булева алгебра.

Таким образом, из перечисленных показателей видно, что самой приемлемой для применения в компьютерах является однородная позиционная двоичная система счисления. Двоичные системы счисления используют в больших и средних компьютерах, предназначенных для решения научно-технических задач с большим объемом вычислений и сравнительно малым количеством исходных данных.

Двоично-десятичную систему применяют для решения экономических задач, которые характеризуются большим объемом входных и выходных данных в сравнении с малым объемом вычислений.

Двоично-десятичная система имеет следующие достоинства:

• не требуется перевод исходных данных из одной системы в другую;

• удобство контроля результатов изображением их на экране дисплея;

• удобство автоматического контроля через наличие избыточных кодов в изображении цифр: 1010, 1011, .... 1111.

1.2.5. Формы, диапазон и точность представления чисел

Двоичные числа в компьютерах размещаются в ячейках памяти или в регистрах, которые состоят из запоминающих элементов — триггеров. В ячейке или триггере хранится значение одного двоичного разряда — бит информации. Разрядной сеткой компьютера называется совокупность запоминающих элементов для размещения одного двоичного числа. Для разных классов компьютеров длина разрядной сетки составляет 8, 16, 32, 64 и больше разрядов. Форматом называется способ размещения компонентов числа в разрядной сетке, то есть последовательность и позиции знака, мантиссы, порядка и др.

В компьютерах используются две формы представления числа:

• с фиксированной запятой перед старшим разрядом числа (для правильной дроби) или после младшего (для целого числа);

• с плавающей запятой, место положения которой задается порядком числа.

Место запятой в обоих форматах понимается неявно, без использования дополнительных разрядов. По традиции нумерация разрядов в больших машинах осуществляется слева направо, а в мини- и микрокомпьютерах и микропроцессорах — справа налево.

В числах со знаком выделяют дополнительный знаковый разряд (обычно, крайний слева). В нем для знака плюс записывают цифру 0, а для знака минус — цифру 1. В числах без знака все разряды числа определяют модуль. Форматы двоичных дробных и целых чисел со знаком, с нумерацией разрядов справа налево и значением их веса показаны на рис. 1.6.

1.2. Арифметические основы компьютерной схемотехники 27

6 5 4 3 2 1 0

2’1 2'2 2‘3 2’4 2'5 2-б 2'7

Рис. 1.6. Формат байта: а — для правильной дроби; б — для целого числа

Числа в разрядную сетку записывают в соответствии с весом позиций. Не занятые разряды заполняют нулями, как это показано на рис. 1.7 для чисел +0,725ю = = .+0,101112 и-4710 =-1011112.

7 6 5 4 3 2 1 0

0.

1 0 1 1 1 0 0

А

7 6 5 4 3 2 1 0

1 0 1 0 1 1 1 1

Рис. 1.7. Запись чисел: а — дроби +0,101112; б — целого числа -1011112

Интервал числовой оси, заключенный симметрично между максимальным и минимальным значением числа, называется диапазоном представления. Абсолютное значение целого числа Л изменяется в пределах:

Amin IА | < Лтах; Лт|П = 1; Атах = 2 — 1, (1.7)

где к— количество разрядов цифровой части числа.

Из выражения (1.7) следует, что числа, по абсолютному значению меньше единицы, воспринимаются как “машинный нуль”; числа, больше Л,пах, вызывают переполнение разрядной сетки. Диапазон представления целых чисел с учетом симметрии относительно нуля числовой оси

Д>я=2Лтах = 2(2*-1)«2* ’. (1.8)

Пример 1.8

Рассчитать максимальное значение и диапазон представления целого числа со знаком в 16-разрядной сетке. На основе выражений (1.7) и (1.8) для к = 15 получаем:

Лтах = 215 - 1 = 32767; D = 2Лтах = 65534.

Абсолютное значение правильной дроби В изменяется в пределах:

. Д„,п < IВ | < Bmax; Bmin = Тк; Втт = 1-2* (1.9)

Правильная дробь, по модулю меньше 2”*, воспринимается как “машинный нуль”; числа, больше единицы, вызывают переполнение разрядной сетки. Диапазон представления правильной дроби

DB = 2Дпах = 2(1- 2 *) « 2, так как 1 » 2"*.

Точность представления чисел в компьютере определяется абсолютной и относительной погрешностью. Абсолютная погрешность представления чисел в компьютере составляет:

для целых чисел

АЛ = 1/2 = 2"';

(1.10)

28 Основы теории компьютерной схемотехники

для правильной дроби

АВ = 2 к/2 =2"(А+,). (1.11)

Из выражения (1.10) следует, что абсолютная погрешность представления целых чисел в форме с фиксированной запятой равна половине младшего разряда и не зависит от длины разрядной сетки. Из выражения (1.11) видно, что абсолютная погрешность представления правильной дроби в форме с фиксированной запятой уменьшается при увеличении длины разрядной сетки.

Относительная погрешность 8 представления числа задается отношением абсолютной погрешности к текущему значению числа и находится в пределах

8min — 8 Зщах.

Для целых чисел в форме с фиксированной запятой минимальное и максимальное значения относительной погрешности

Зл,™ = ЛА/Лтах = 2~7(2*- 1) « 2-(И|);

8Лтах = Жш = 2’71 = 0,5.

Такими же формулами определяются минимальное и максимальное значения относительной погрешности для правильной дроби с фиксированной запятой. Относительная погрешность представления чисел в форме с фиксированной запятой существенно зависит от значения числа и значительно возрастает для малых чисел.

В форме с плавающей запятой числа представляются в виде произведений:

С = qn -М = ХМ, (1.12)

где q — основание системы счисления (обычно целая степень числа 2); П — порядок числа длиной £+1 (целое число со знаком); М— мантисса числа длиной г+1 (правильная дробь со знаком); X — характеристика числа. Знак всего числа определяется знаком мантиссы. Для мини-компьютеров основания порядка и мантиссы совпадают (далее предполагается этот случай), а для больших машин — они различны. Представление числа формулой (1.12) называют также полулогарифмическим, потому что только часть числа — характеристика — представляется в логарифмической форме.

Мантисса называется нормализованной, если ее значение определяется неравенством вида

\/q<\M\<1, (1.13)

то есть в старшем разряде модуля мантиссы должна быть записана единица. Так, для основания q = 2 имеем: 2'1 < М< 1.

Пример 1.9

Иллюстрация записи числа в форме с плавающей запятой:

Л2 = 2'110,111 = 22-1 1,01 11 - 24-0,1 1011 1.

Значение порядка указывает на количество позиций, на которые “плавает" запятая.

Формат числа с плавающей запятой в 16-разрядной сетке показан на рис. 1.8. Тут для модулей порядка и мантиссы отведено соответственно пять и девять разря

1.2. Арифметические основы компьютерной схемотехники 29

дов. Запятая в порядке размещена (условно) после младшего разряда, а в мантиссе— перед старшим. Знаки порядка и мантиссы размещены перед их старшими разрядами.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 О

± Порядок ± Мантисса

Рис. 1.8. Формат чисел в форме с плавающей запятой

Абсолютное значение числа С в форме с плавающей запятой с учетом формул (1.7), (1.9) и (1.13) изменяется в пределах

Ainin Akinin “ Cmjn < | С* | < C*max — -Aqnax Л/1Пах, (1.14)

где Xmnl = 2 n- ; Af,nill = 2~’; Xmax = 2+n- ; Mmax = 1 -2~‘; Птах = T - 1;

г л к— разрядность модулей порядка и мантиссы.

Диапазон представления чисел в форме с плавающей запятой

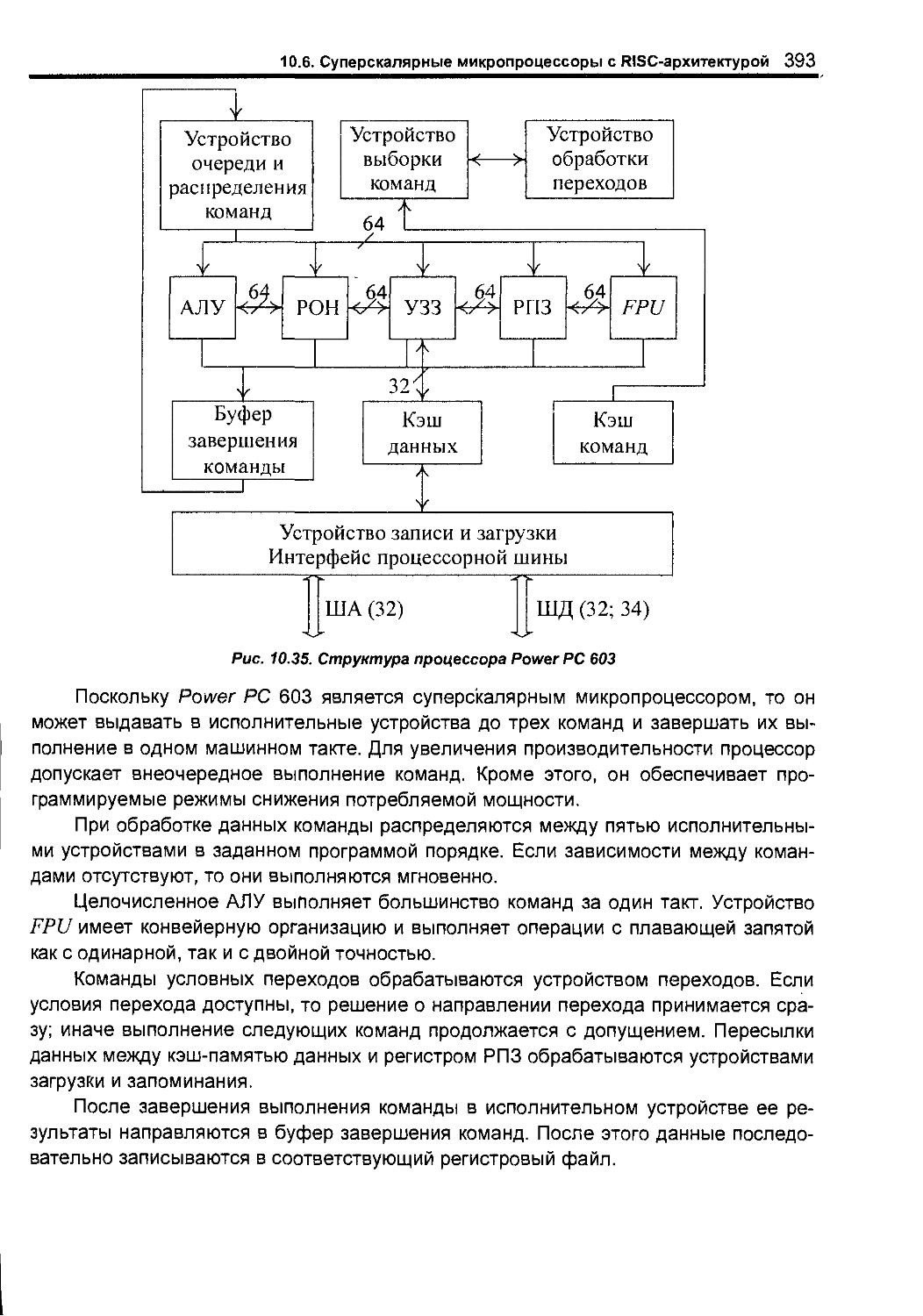

Dc =2Cmax = 2-2+n"M>(l-2~*)«2+n”"'+1. (1.15)

Пример 1.10 I

Рассчитать значение диапазона Dc для числа С при г = 5, к = 9. С учетом \ выражения (1.15) получаем:

П,„ах = 2/<- 1 = 25 - 1 - 31; Dc = 23|+|= 232,

что приблизительно соответствует десятичному числу 1О320’3 ~ 109. Диапазон представления чисел с плавающей запятой приблизительно больше в Птах раз диапазона представления чисел в форме с фиксированной запятой.

—-----—-----------------------------------------------__----,-----,----.-

Абсолютная погрешность представления чисел в форме с плавающей запятой зависит от погрешности мантиссы и порядка числа:

АС = АЛ/-2±П; АЛ/ = 2(Ж), (1.16)

где АЛ/— погрешность представления мантиссы.

Минимальная и максимальная относительные погрешности представления чисел в форме с плавающей запятой не зависят от характеристики (она записывается в числителе и знаменателе выражения и потому сокращается). С учетом формул (1.14) и (1.16) относительные погрешности рассчитывают из соотношений:

=

Ш 2~(t+l)

“ ~ 2“’

(1.17)

Из выражений (1.17) следует, что относительные погрешности представления чисел в форме с плавающей запятой практически постоянны во всем диапазоне чисел.

30 Основы теории компьютерной схемотехники

1.2.6. Представление информации в микропроцессорах класса Pentium

Рассмотрим представления операндов в 32-разрядных микропроцессорах класса Pentium. В них используются такие типы данных: целые числа, вещественные числа, двоично-десятичные числа и строки битов, байтов и слов. Целые числа представляются со знаком и без знака в форматах байта, слова, двойного и учетверенного слова длиной соответственно 8, 16, 32 и 64 бит (рис. 1.9).

7 0 7 0 15 8 7 0 15 8 7 0

l± I Байт | | Байт | Слово | | Слово I

a б в г

31 16 15 0 31 16 15 0

|± | Двойное слово | I Двойное слово

д е

61 0

l± I Учетверенное слово I

Рис. 1.9. Форматы целых чисел: а, в, д, ж— со знаком; б, г, е— без знака

Над числами в этих форматах выполняются операции сложения, вычитания, умножения, деления и др. Диапазоны представления знаковых и беззнаковых значений в данных форматах представлены в табл. 1.4.

Таблица 1.4

Формат числа Диапазон представления чисел

без знака со знаком

Байт 0...255 “128... + 127

Слово 0...65535 -32768...+32767

Двойное слово 0...4-Ю9 -2-1О9...+2-1О9

Учетверенное слово 0...5-1019 -2,51019. ..+2,5Ю19

Вещественные числа представлены в формате с плавающей запятой в коротком (32 бит), длинном (64 бит) и расширенном (80 бит) форматах (рис. 1.10). Числа с плавающей запятой длиной 32 и 64 бит, которые используются во многих компьютерах, например, в ЕС ЭВМ, СМ ЭВМ, обычно называют числами с одинарной и двойной точностью. Расширенный формат характерен только для процессоров класса Pentium.

31 30 27 26 0

| Порядок 1 Мантисса |

63 62 a 52 51 0

1 ± 1 Порядок 1 Мантисса 1

79 78 б 64 63 0

Ь L Порядок 1 Мантисса

в

Рис. 1.10. Форматы чисел с плавающей запятой: а — короткий; б — длинный; в — расширенный

1.2. Арифметические основы компьютерной схемотехники 31

В данных форматах чисел с плавающей запятой используются смещенные по-

рядки Псм ’

П + 127 для г = 8;

Псм = П + АП = П +2г-'~

1 = •! П + 1023 для г = 11;

П + 16383 для г = 15,

где П — значение истинного порядка; АП = 2'1 - 1 — смещение; г — длина порядка, которая равна 8, 11 или 15 бит соответственно для короткого, длинного и расширенного формата. Значение ПСм всегда положительное, поэтому знаковый разряд не нужен. Представление порядка со смещением упрощает операции сравнения чисел с плавающей запятой, что особенно важно для алгоритмов сортировки.

Значение числа с плавающей запятой и смещенным порядком определяется по формуле

где 5— знак числа; п — число, которое для разных форматов равно 23, 52 или 63.

В машине мантисса представлена в нормализованной форме, которая состоит из целой части Fo = 1 и дроби в таком виде:

М — 1, F, F2, .... Fi, ...,Fn.

В коротком и длинном форматах бит Fo при передаче чисел и хранении их в памяти не фигурирует. Это — скрытый (неявный) бит, который в нормализованном числе всегда равен единице.

Пример 1.11

Представить десятичное число -247,375 в коротком формате. Двоичный код этого числа равен -11110111,011; истинный порядок будет +7 (запятая сдвигается влево на семь разрядов), а смещение достигнет значения Псм = 127 + 7 = 134. С учетом скрытого бита Fo = 1 имеем:

Знак Порядок Мантисса

1 1000 0110 ,1110 1110 1100 0000 0000 0000.

Параметры форматов вещественных чисел представлены в табл. 1.5.

Таблица 1.5

Параметры Формат

короткий ДЛИННЫЙ расширенный

Длина формата, бит 32 64 80

Длина мантиссы, бит 24 53 64

Длина порядка, бит 8 П 15

Смещение порядка + 127 + 1023 +16383

Диапазон Ю±з8 1О±308 10±4932

Числа в коротком и длинном форматах существуют только в памяти. При загрузке чисел в одном из этих форматов в микропроцессор они автоматически преобразуются в 80-битный формат, который используется только для внутренних one-

32 Основы теории компьютерной схемотехники

раций. Аналогично данные из процессора преобразуются в короткий или длинный формат для хранения в памяти.

Точность вычислений чисел с плавающей запятой возрастает с увеличением длины мантиссы. Диапазон представления чисел с плавающей запятой зависит от длины порядка и основания счисления q. В машинах ЕС ЭВМ значение q = 16. В процессорах Pentium диапазон представления чисел в коротком формате для q = 2 находится в пределах 10±38. Если же для этого формата взять основание q = 16, то получим значение диапазона в пределах 10±152.

В микропроцессорах Pentium используются двоично-десятичные цифры в таких форматах:

• восьмиразрядные упакованные, которые содержат в одном байте две десятичные цифры в коде 8421, например, 3910 = 0011 Ю012_10;

• восьмиразрядные неупакованные, которые содержат одну десятичную цифру в байте (младшая тетрада) вместе с признаком (зоной) 00112 в международном коде ASCII, например, 3910 = 0011 0011 0011 Ю012_10.

Представление десятичного числа 136492 в неупакованном и упакованном форматах показано на рис. 1.11;

7______0 7_______0 7______0 7______0 7_______0 7______0

|00П 0001 |0011 ООП |0011 0П0|00П 0100|00П 100110011 оою|

а

7______0 7_______0 7______0

[0001 ООП |0П0 0100 |1001 0010 I

б

Рис. 1.11. Представление десятичных цифр в форматах: а — неупакованном; б — упакованном

• 80-разрядные упакованные, в которые записываются 19 десятичных цифр, и в старшую тетраду записывается знак числа.

1.2.7. Кодирование отрицательных чисел

Для записи знака числа, замены операции вычитания чисел сложением их кодов, а также для определения переполнения разрядной сетки используют прямой, обратный и дополнительный коды, где для представления знака числа отводится знаковый разряд, который располагается слева от числа и отделяется запятой. В знаковый разряд записывают нуль (для положительного числа) или единицу (для отрицательного). Запятая в машине в явном виде не изображается, а только подразумевается.

Числа, представленные в прямом, обратном и дополнительном кодах, называют машинными изображениями. Они состоят из знакового разряда и цифровой части (модуля числа). Положительные числа во всех кодах записываются одинаково. Если обозначить машинные изображения числа А в прямом коде [Л]Пр, в обратном коде [Л]0Б, в дополнительном коде [Л]д, то для положительных чисел имеем:

[Л]пр = [Л]об = И]д.

1.2. Арифметические основы компьютерной схемотехники 33

Для отрицательных чисел с длинной мантиссы к битов коды определяют по таким правилам:

прямой код:

Г1 + |Л| -для дроби;

МпР = ] А. I I

2 + -для целого числа;

обратный код:

[2-|л|-2“а' -для дроби;

И]оБ=1 л+| | |

2 -Л -для целого числа;

дополнительный код:

[2-|л| -для дроби;

Ид Н А.+| I , 12 - |Л| - для целого числа;

Пример 1.12 ]

Запись двоичных чисел А = 10102 и В = —10102 в прямых кодах:

[Л]Пр = 0,1010; [5]пр= 1,1010. |

Обратный код отрицательного числа образуется из его прямого кода после инвертирования значений разрядов цифровой части, то есть заменой нуля на единицу и единицы — на нуль; значение знакового разряда не изменяется. Дополнительный код отрицательного двоичного числа образуется из его обратного кода путем добавления единицы к младшему разряду.

Пример 1.13

Представление в обратном и дополнительном кодах двоичных чисел: целого А =-10012 и дробного В = —10012:

И]0Б= 1,0110; №=1,0111;

[5]об= 1,0110; [5]д= 1,0111.

Из этих примеров видно, что обратный и дополнительный коды целых и дробных чисел по виду записи совпадают; расхождения между ними отражены в алгоритмах обработки информации.

В модифицированных кодах знак числа дублируется в двух знаковых разрядах.

Пример 1.14

Представление в модифицированных кодах чисел А = 11012 и В = -11012: №р=№б=№ = 00,1101;

[5]пр= 11,1101; Моб = 11,0010; [5]д = 11,0011.

Для перехода от обратного кода отрицательного числа к прямому коду требуется инвертировать значения разрядов цифровой части, не изменяя значения знакового разряда. Для перехода от дополнительного кода отрицательного числа к прямому сначала получают его обратный код, а затем добавляют единицу к младшему разряду. 3-4-1749

34 Основы теории компьютерной схемотехники

1.2.8. Арифметические операции сложения и вычитания

Все операции в компьютере выполняются в арифметико-логическом устройстве (АЛУ). Числа, которые участвуют в операциях, называются операндами. Основной операцией в АЛУ является сложение. Операция вычитания заменяется сложением операндов в обратном или дополнительном кодах. Операции умножения и деления сводятся к многократным сложениям и сдвигам.

Правила выполнения операций сложения, вычитания, умножения и сложения по модулю 2 в двоичной арифметике представлены в табл. 1.6. При сложении двух единиц возникает перенос в старший разряд; при вычитании из нуля единицы требуется заем из старшего разряда.

Таблица 1.6

Сложение Вычитание Умножение Модуль 2

0+0 = 0 0-0 = 0 00 = 0 0+0 = 0

0+1 = 1 1-0=1 01 =0 0+1 = 1

1+0 = 1 1-1=0 1-0 = 0 1+0=1

1 + 1 = 10 т Перенос 0-1 = 11 t Заем 11 = 1 1 + 1=0

Операция сложения в АЛУ выполняется типовым функциональным узлом — сумматором. Он состоит из отдельных логических схем, называемых одноразрядными сумматорами. Связь между отдельными одноразрядными сумматорами реализуется с помощью цепей переноса в направлении от младших разрядов к старшим.

Операнды А и В поступают с выходов регистров операндов. Комбинационный сумматор строится на логических элементах и не обладает свойством запоминания информации, поэтому результат сложения записывается в регистр результата.

Во всех компьютерах имеются команды сложения и вычитания чисел. Однако в сумматорах реализуются только операции сложения условно положительных машинных изображений. Машинные изображения положительных операндов во всех кодах совпадают. Машинные изображения отрицательных операндов получают по правилам представления чисел в обратном и дополнительном кодах. В операциях вычитания знак второго операнда (вычитаемого) автоматически изменяется на противоположный и после этого получают его машинное изображение. Поэтому в последующих примерах рассматриваются только операции сложения.

В машинных изображениях (для обратного и дополнительного кодов) знаковый разряд и цифровая часть числа рассматриваются как одно целое. Они одинаково участвуют в операции сложения. При сложении в обратных кодах перенос из старшего знакового разряда результата поступает на вход переноса младшего разряда (циклический перенос). При сложении в дополнительных кодах перенос из старшего знакового разряда результата не учитывается, поэтому в сумматоре цепь циклического переноса разрывается. Знак результата при сложении машинных изображений образуется автоматически.

При сложении двоичных л-разрядных чисел А = а,„ ..., а, и В = Ь„, ..., Z>„ ...,

Ьх результат в каждом разряде определяют по формулам:

1.2. Арифметические основы компьютерной схемотехники 35

а, + bj +Zi — Si + 2P,+l,

f 0 при а, + Ь, < 1;

/+l [1 при at + bi > 2;

где а„ bj — значения z-x разрядов; Z, — перенос из младшего разряда; S, — результат; Р1+, — перенос в старший разряд.

Пример 1.15

Сложить двоичные числа А = 1010 и В = 0011 в обратном коде:

[Л]Об = 0,1010

+ [^]ОБ = 0,0011

[С]об = 0,1101; С= 11012 = 1310.

Пример 1.16

Сложить двоичные числа А = -1010 и В = ном кодах: [Л]Об = 1,0101 + [^]об = 1,1100 -0011 в обратном и дополнитель- [Л]д= 1,0110 + [5]д= 1,1101

1,0001 | +1 [С]Об = 1,0010; С = -11012 =-1310. [С]д= 1,0011; С =-11012 =-1310.

При сложении чисел одного знака возможно переполнение разрядной сетки, признаком чего является несовпадение знака результата со знаками операндов. В АЛУ имеются специальные логические схемы, которые автоматически формируют признак переполнения.

Пример 1.17

Сложить двоичные числа А = 1011 и В = 0111 в обратном и дополнительном

кодах:

[Л]об = 0,1011 [Л]д = 0,1011

+ [5]об = 0,0111 + [5]д = 0,0111

[Qoe# 1,0010; [С]д# 1,0010.

В этом примере сложение положительных чисел привело к положительному переполнению: операнды — положительные, результат — отрицательный.

Пример 1.18

Сложить двоичные числа А = -1011 и В = -0111 в обратном и дополнительном кодах:

|/4]об — 1,0100 + [5]об= 1,1000 [Л]д= 1,0101 + [Я]д= 1,1001

[С]об # 0,1101; [С]д # 0,1110.

з*

36 Основы теории компьютерной схемотехники

В этом примере сложение отрицательных чисел привело к отрицательному переполнению; операнды — отрицательные, результат — положительный.

Для упрощения обнаружения переполнения разрядной сетки используются модифицированные коды, для которых знаковый разряд в сумматоре дублируется. Положительному переполнению в знаковых разрядах соответствуют цифры 01, а отрицательному — 10. Значение знаковых разрядов 00 соответствует правильному положительному результату, а цифры 11 — отрицательному.

Пример 1.19

\ Сложить двоичные числа А = -1010 и В = 1100 в обратном и дополнительном

\ модифицированных кодах:

I [Л]МОБ= 11,0101 [Л]мд= 11,0110

I +[^]МОБ = 00,1100 + [£]мд = 00,1100

I ’ 100,0001” [С]мд = 00,0010;

I I* +1

I 1-----►

[С]Моб = 00,0010; С = 00102 = 2|О. С = 00102 = 2|О.

Пример 1.20

Сложение чисел А = -1101 и В = фицированных кодах: -1010 в обратном и дополнительном моди-

[Л]МОБ = 11,0010 [Л]мд= 11,0011

+ [£]МОБ= 11,0101 + [£]мд= 11,0110

[С]МОБ^ 10,1000; [С]мд^ 10,1001.

В этих примерах произошло отрицательное переполнение в результате.

1.2.9. Арифметические операции умножения и деления

Операция умножения чисел состоит из к циклов, где к — число цифровых разрядов множителя. Результат умножения z-го разряда множителя на множимое называется частичным произведением, а их последовательное сложение — суммой частичных произведений (СЧП). В каждом цикле анализируется следующая цифра множителя: если это 1, то к СЧП прибавляется множимое, если 0, то сложение не выполняется. Цикл завершается сдвигом на один разряд множимого относительно СЧП или сдвигом СЧП относительно неподвижного множителя. Множимое и множитель размещаются в разрядной сетке на основе специальных схем-регистров, а СЧП — в сумматоре-регистре.

Умножение можно выполнять одним из четырех способов:

• с младших разрядов множителя со сдвигом его и СЧП вправо при неподвижном множимом (рис. 1.12, а). Старшие разряды произведения находятся в сумматоре, а младшие — в регистре множителя;

• с младших разрядов множителя при сдвиге множимого и неподвижной СЧП;

• со старших разрядов множителя при сдвиге СЧП влево и неподвижном множимом;

1.2. Арифметические основы компьютерной схемотехники 37

• со старших разрядов множителя при сдвиге его и СЧП влево (рис. 1.12, б).

Если хотя бы один из сомножителей равен нулю, то произведению сразу присваивается нулевое значение.

п 1

а б

Рис. 1.12. Способы умножения: a — первый; б — четвертый

Алгоритм умножения целых чисел, представленных в прямом коде, на основе первого способа реализуется в такой последовательности:

1. взять модули сомножителей и обнулить исходное значение СЧП;

2. если младшая цифра множителя равна 1, то к СЧП прибавляется множимое; если это 0, то сложение не происходит;

3. сдвиг вправо на один разряд СЧП и множителя;

4. пп. 2 и 3 последовательно выполняются к раз, после чего произведению присваивается знак, определяемый сложением по модулю 2 знаков сомножителей.

Пример 1.21

Перемножить первым способом числа А = 13 )0 = 11012 и В = 1110 = 10112,

представленные прямыми кодами.

1101 — модуль множимого

1011 — модуль множителя

0000 — исходная СЧП

+1101 — первое частичное произведение (ЧП)

1101 — первая СЧП

01101 — сдвиг вправо СЧП на 1 разряд

+ 1101 — второе ЧП

100111 — вторая СЧП

0100111 — сдвиг вправо СЧП на 1 разряд

+0000 — третье ЧП

100111 — третья СЧП

0100111 — сдвиг вправо СЧП на 1 разряд

+1101 — четвертое ЧП

10001111 • — четвертая СЧП

10001111 — сдвиг вправо СЧП на 1 разряд.

Произведение С = А В = 100011112= 143,0-

38 Основы теории компьютерной схемотехники

Разработаны также методы ускоренного умножения и умножения в дополнительных кодах.

Операция деления числа С = А / В обычно сводится к последовательности вычитаний делителя В сначала из делимого А, а затем из создаваемых в процессе деления остатков Числа А и В поступают в прямом коде. В зависимости от способа вычитания делителя различают два алгоритма деления: без восстановления остатка и с восстановлением.

Для обоих алгоритмов общим является следующее:

• деление осуществляется над модулями чисел А и В (при делении целых чисел в машинах длина делимого А вдвое больше длины делителя В)-,

• знак частного определяется сложением по модулю 2 знаков Л и В;

• перед делением анализируются числа А и В на равенство нулю: если А = О, то частному присваивается значение 0 и операция завершается; при В = О выполнение программы прерывается;

• умножение частного на два осуществляется сдвигом его влево на один разряд, а операция вычитания делителя В заменяется его сложением в дополнительном коде;

• первый остаток R} определяет по формуле

R} =2-\А\-В = 2-\А\+[-В]а,

причем, если 7?| < 0, то деление возможно, если R} > 0, то возникает переполнение разрядной сетки;

• цифры частного определяются, начиная со старших разрядов:

при R, < 0;

при R, > 0,

i - 1,2, ..., к, где к — заданное количество цифр частного. Обычно первый разряд С,- отводится для записи знака.

Алгоритм деления без восстановления остатка определяют по следующему ре-курентному соотношению:

' 2Rt +15

2R, + [б 1ц

при R,< 0; при R, >0.

Алгоритм деления с восстановлением остатка определяют по следующему ре-курентному соотношению:

47?,-, + [- 5]д при Ri < 0; 2Rj + В]д при Rj > 0.

при R, > 0.

[ Пример 1.22

Разделить числа А = 49|0 и В - -7]0 на основе алгоритма без восстановления остатка. Прямой код операндов: [Л]Пр = 0,0110001, [В]Пр = 1,111; [-5]д = = 1,001:

1.2. Арифметические основы компьютерной схемотехники 39

Пример 1.22. Продолжение

[Л]Пр = 0,0110001 + [5]ПР= 1,111

2 |Л = 0,1100010 + [-В]д= 1,001

7?, = 1,1110010 < 27?, = 1,1100100 + \В\ =0,111 0 С, =0

Т?2 = 0,1010100 > 27?2= 1,0101000 + [-7?]д= 1,001 0 С2 = 1;

7?з = 0,0111000 > 27?3 = 0,1110000 + Н?]д= 1,001 0 С3 = 1; частное [С]пр = 1,111; С = -111 = -7)0; остаток равен нулю.

Т?4 = 0,0000000 > 0 С4 = 1; Знак частного А[7] Ф В[7] = 0 Ф 1 = 1.

Пример 1.23

Разделить числа А остатков: [Л]пр = 0,0110001 + [5]ПР= 1,111 = 49ю и В = -710 на основе алгоритма с восстановлением

2|Л| = 0,1100010 + [-7?]п= 1,001

7?! = 1,1110010 < 47?0= 1,1000100 + [-7?]д= 1,001 0 С, = 0

Т?2 = 0,1010100 > 27?2 = 1,0101000 + [-7?]д= 1,001 0 С2 = 1;

7?з = 0,0111000 > 27?3 = 0,1110000 + [-Д]д= 1,001 0 С3 = 1; частное [Л]ПР = 1,111; С = -111 = -710.

Т?4 = 0,0000000 > 0 С4 = 1;

40 Основы теории компьютерной схемотехники

Описанные способы выполнения арифметических операций над числами с фиксированной запятой применяют также для выполнения их над мантиссами чисел с плавающей запятой. Сложение и вычитание чисел А и В с плавающей запятой может осуществляться только при равенстве их порядков Пл и Пя. Для этого они предварительно выравниваются сдвигом одного из них. При умножении или делении чисел А и В с плавающей запятой порядок результата ПР равен соответственно сумме или разности порядков этих чисел, то есть ПР = ПА± Пй.

1.3. Логические основы компьютерной схемотехники

1.3.1. Булева алгебра

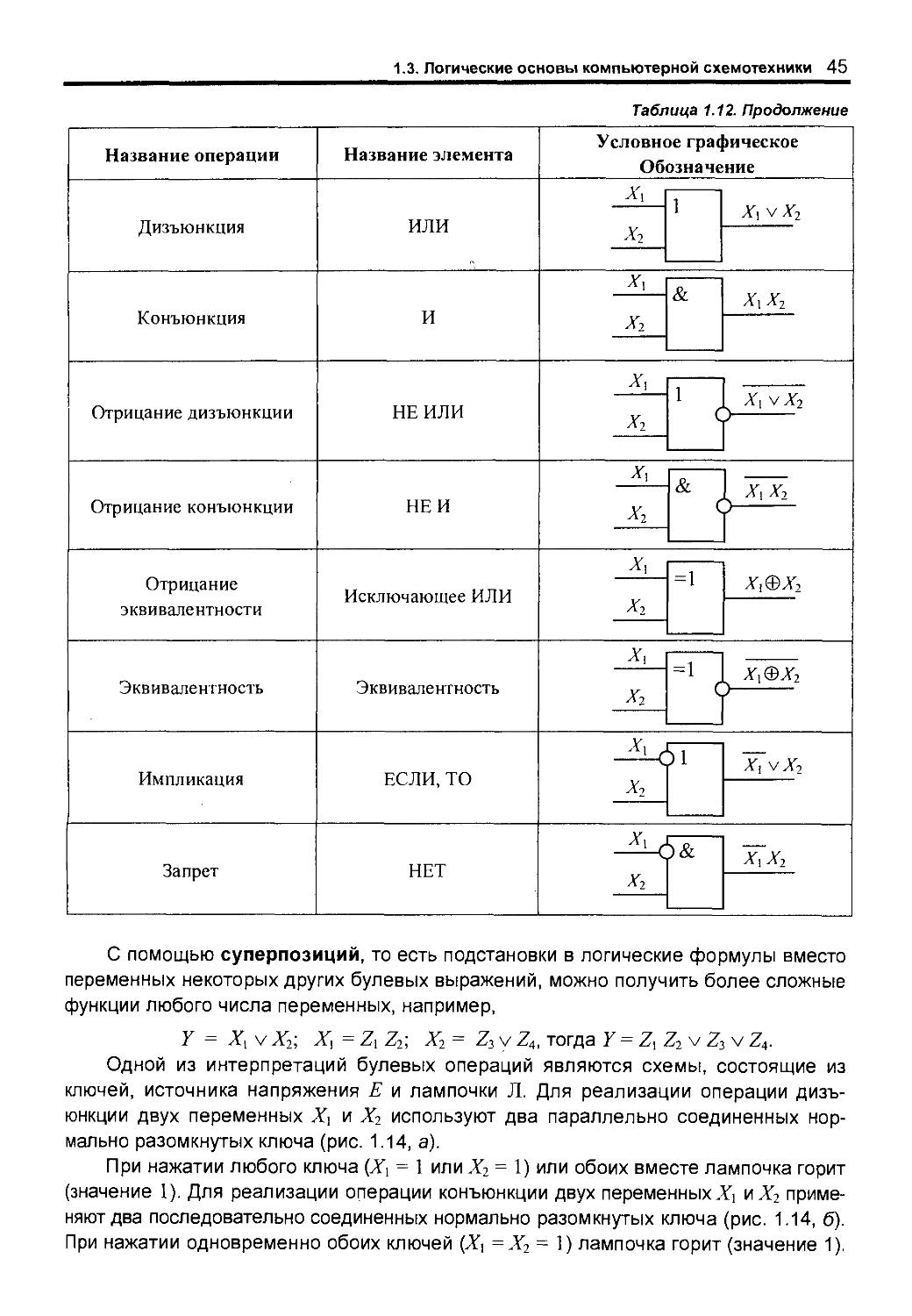

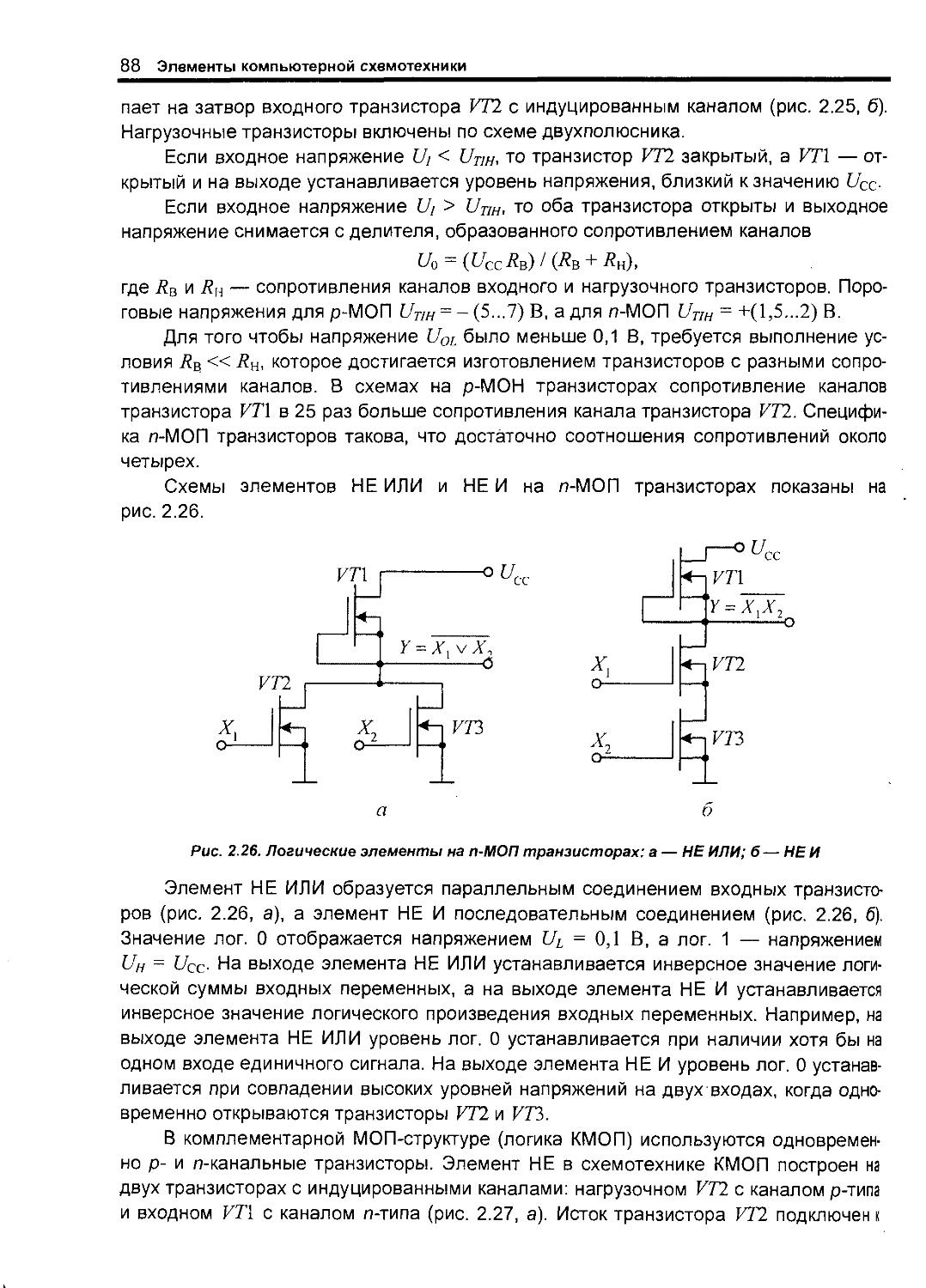

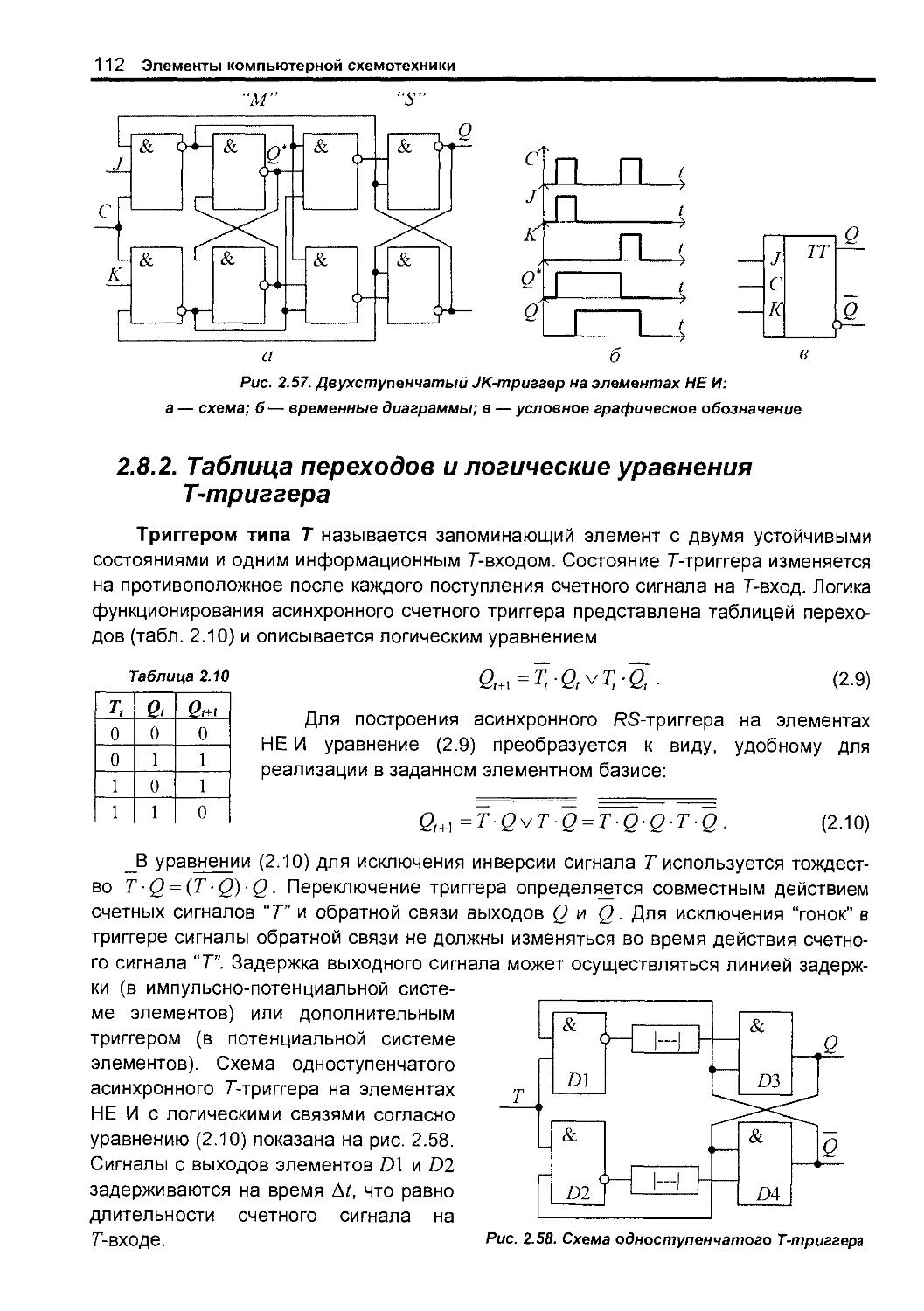

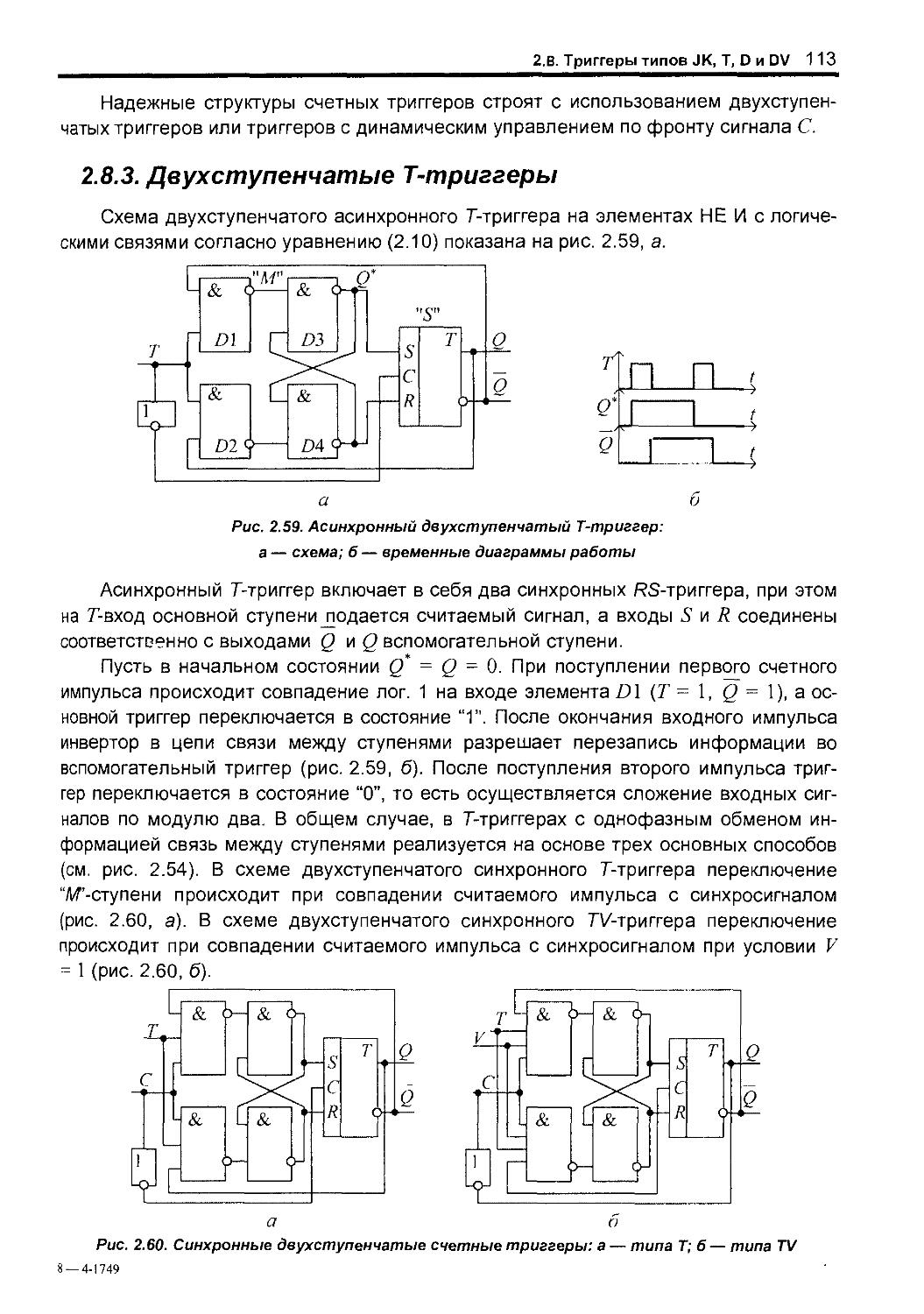

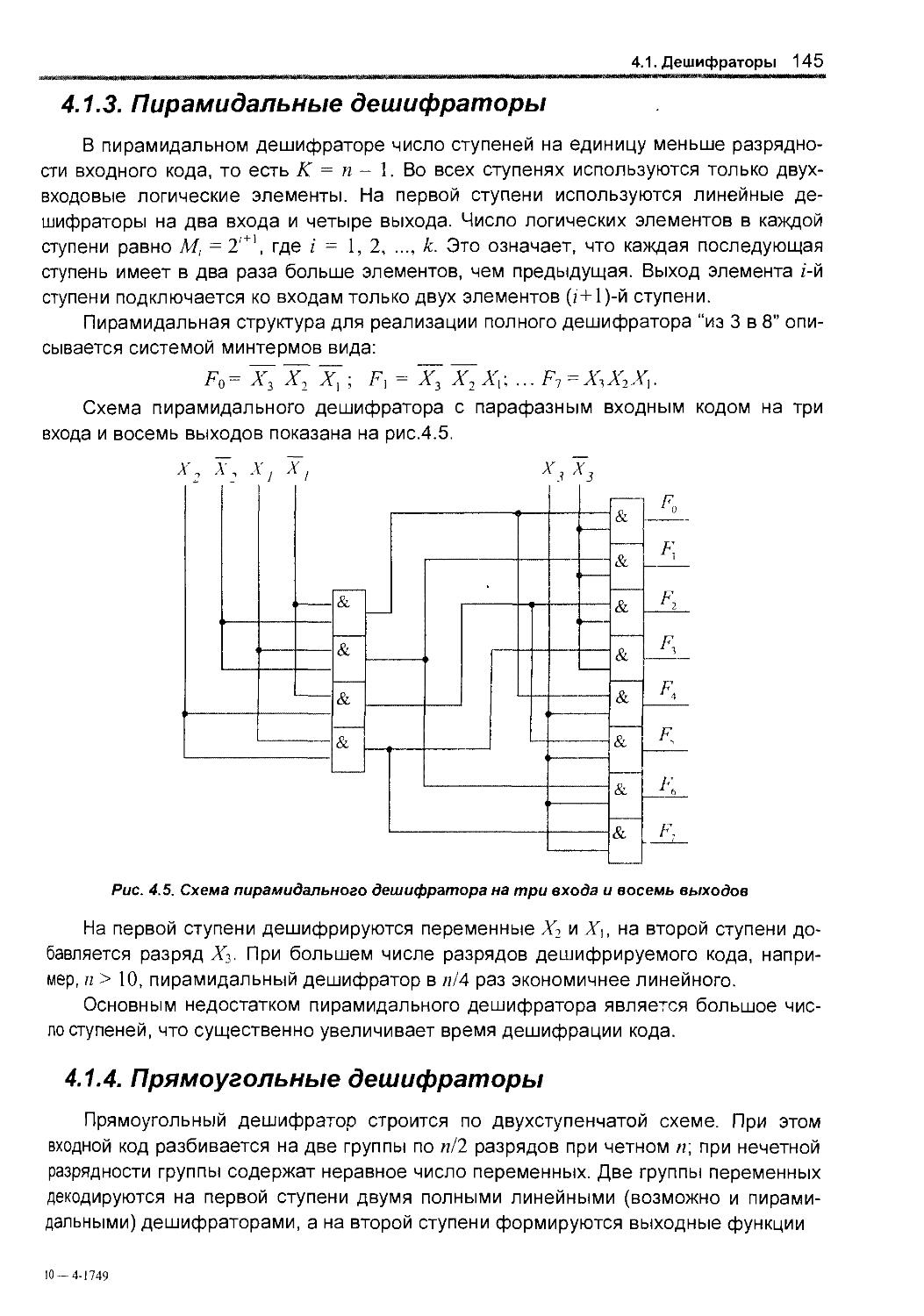

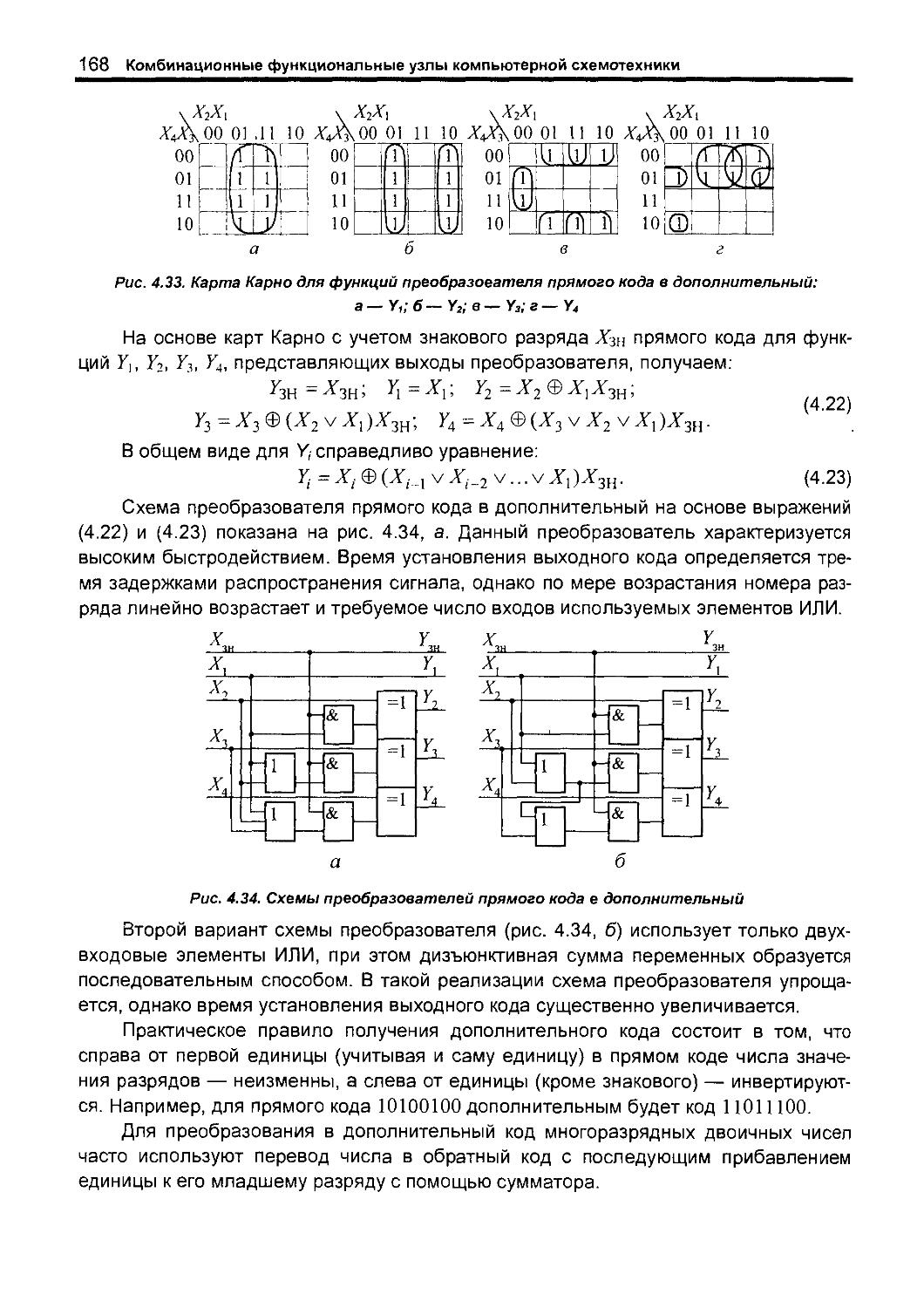

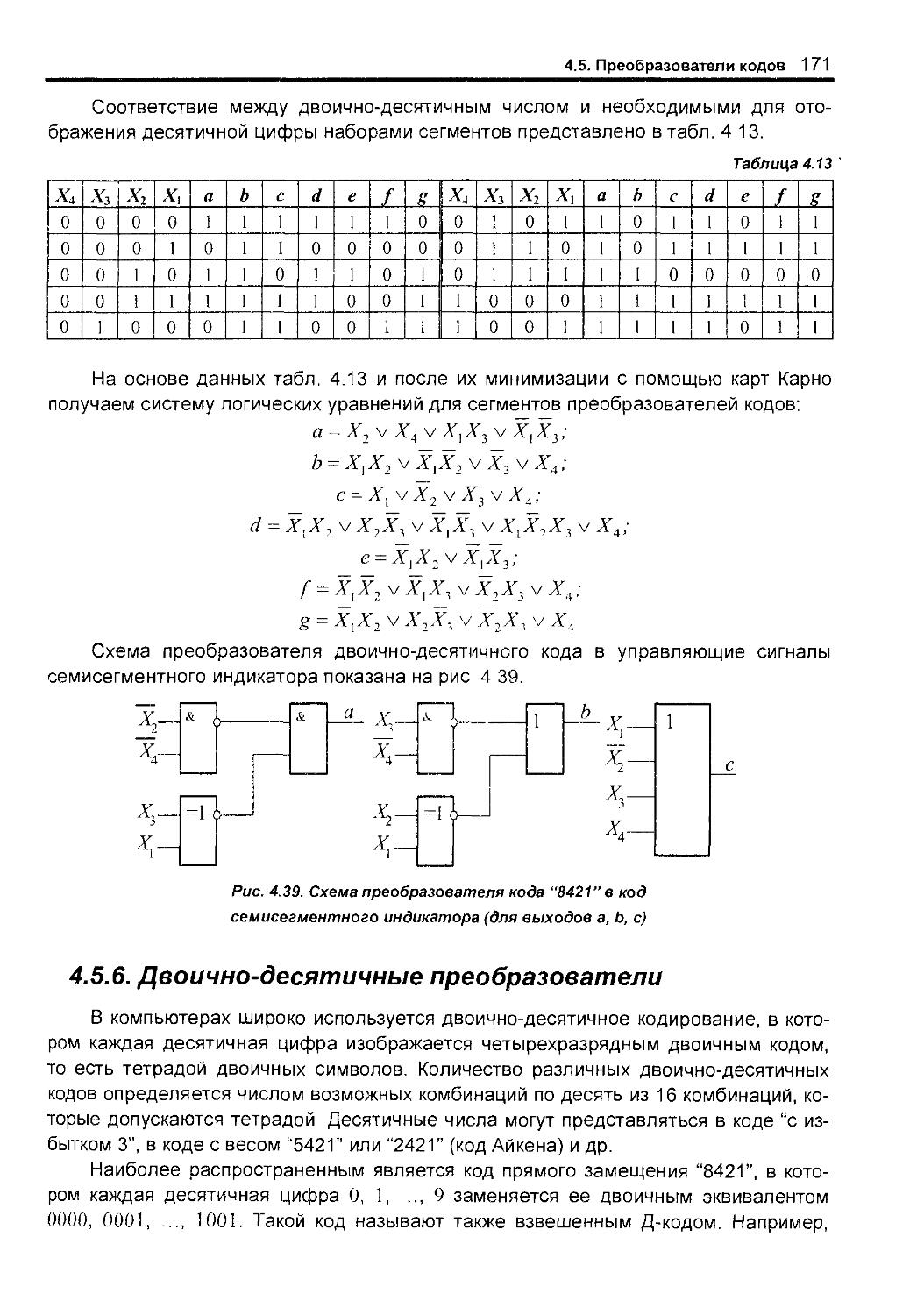

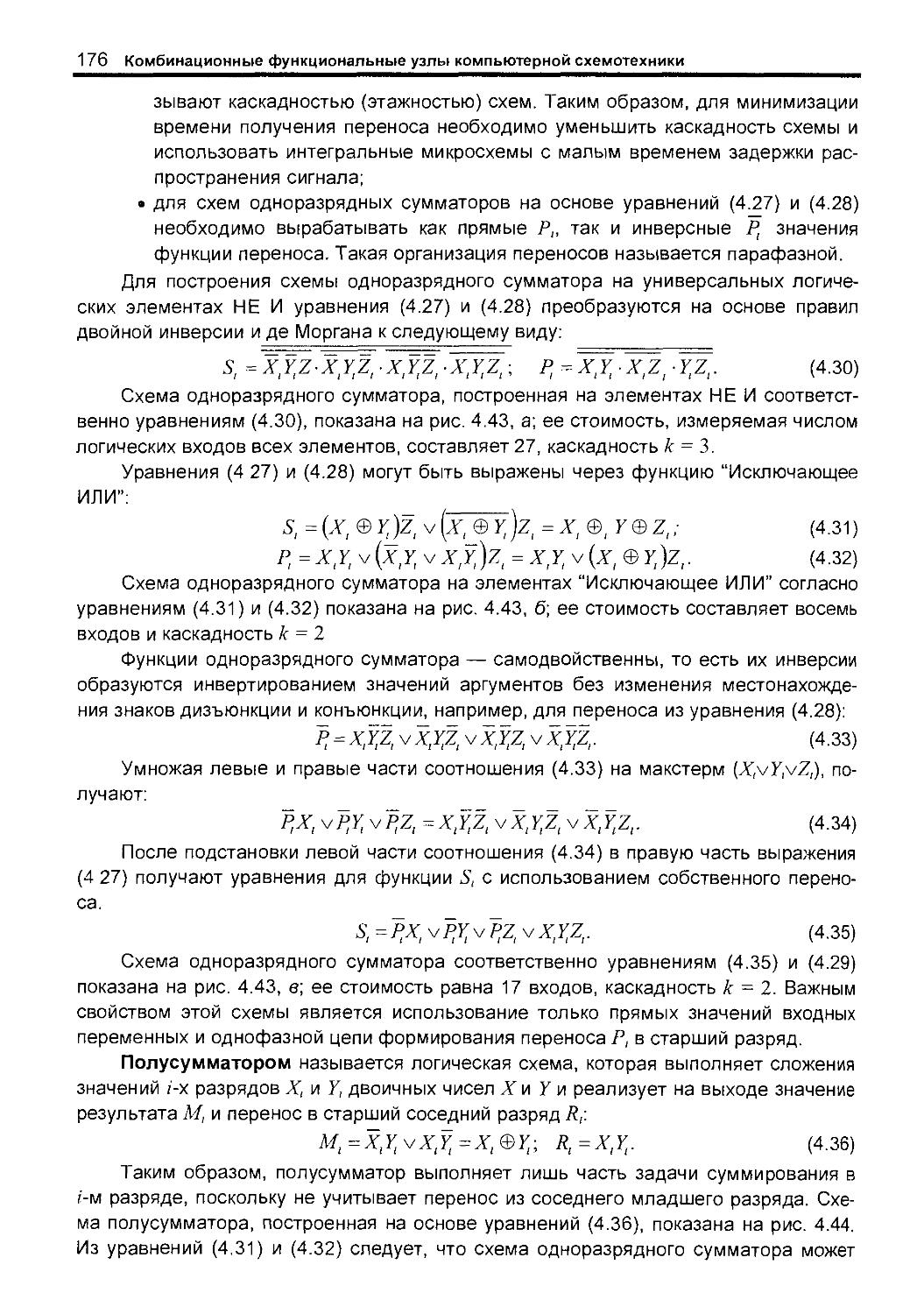

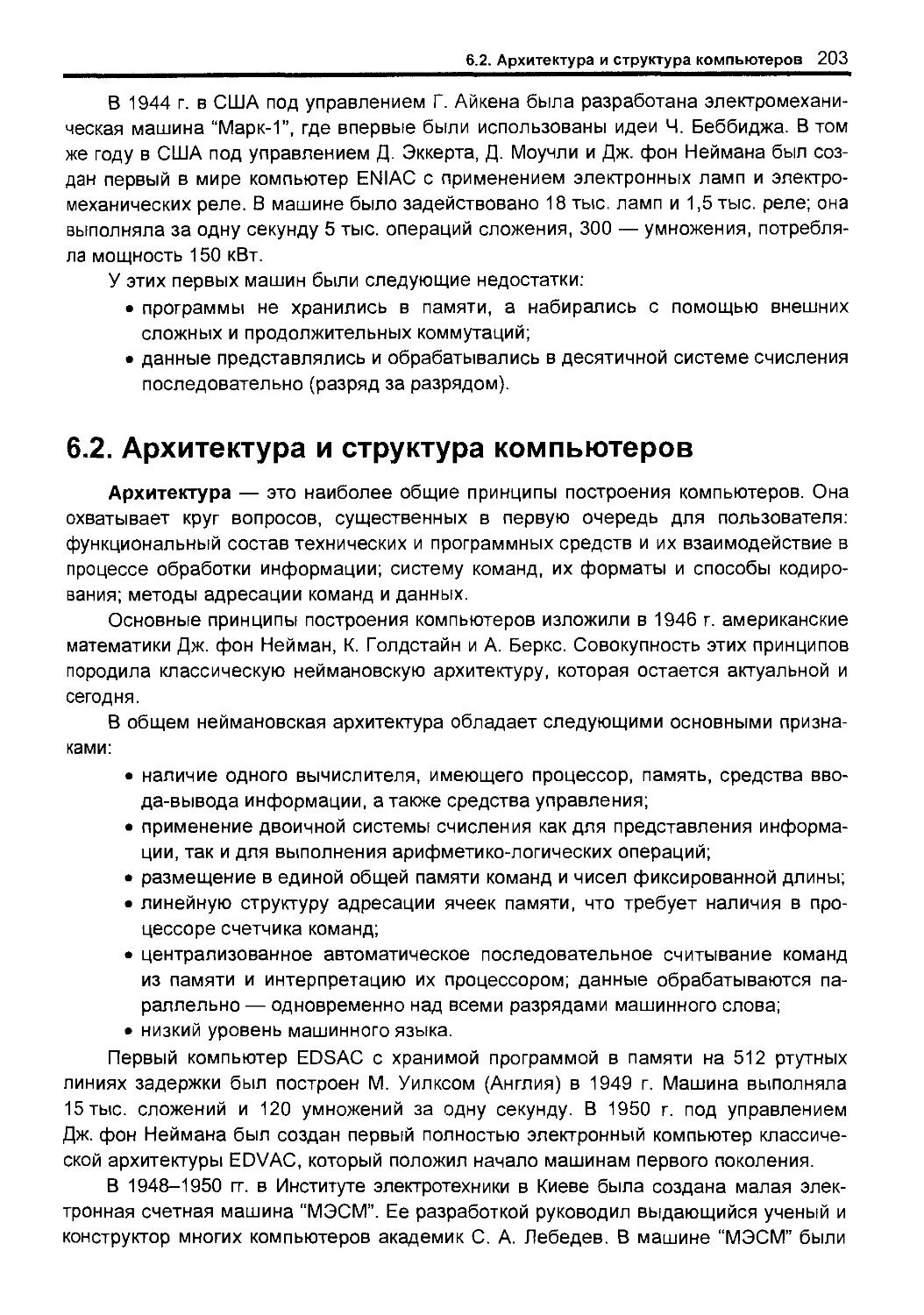

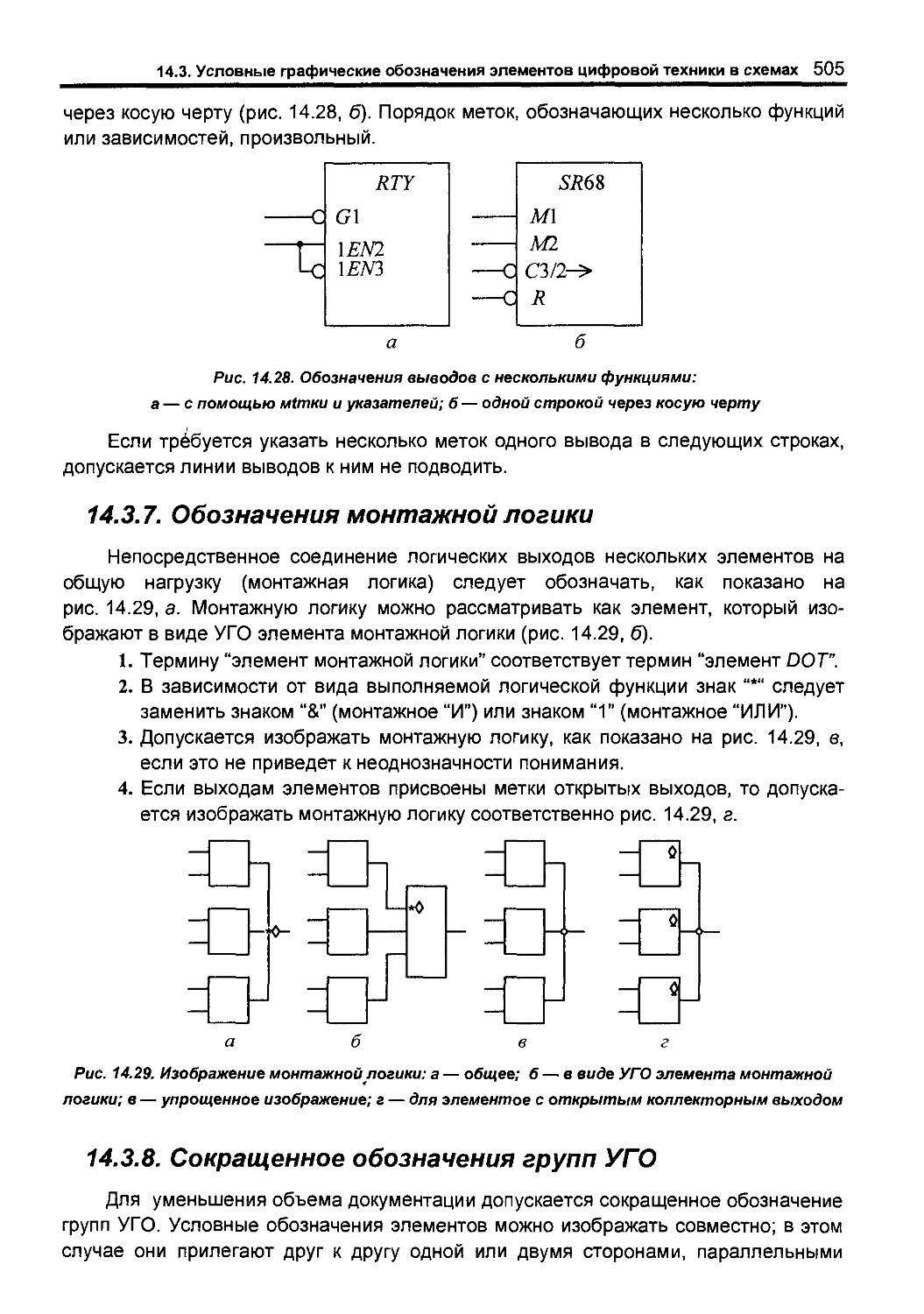

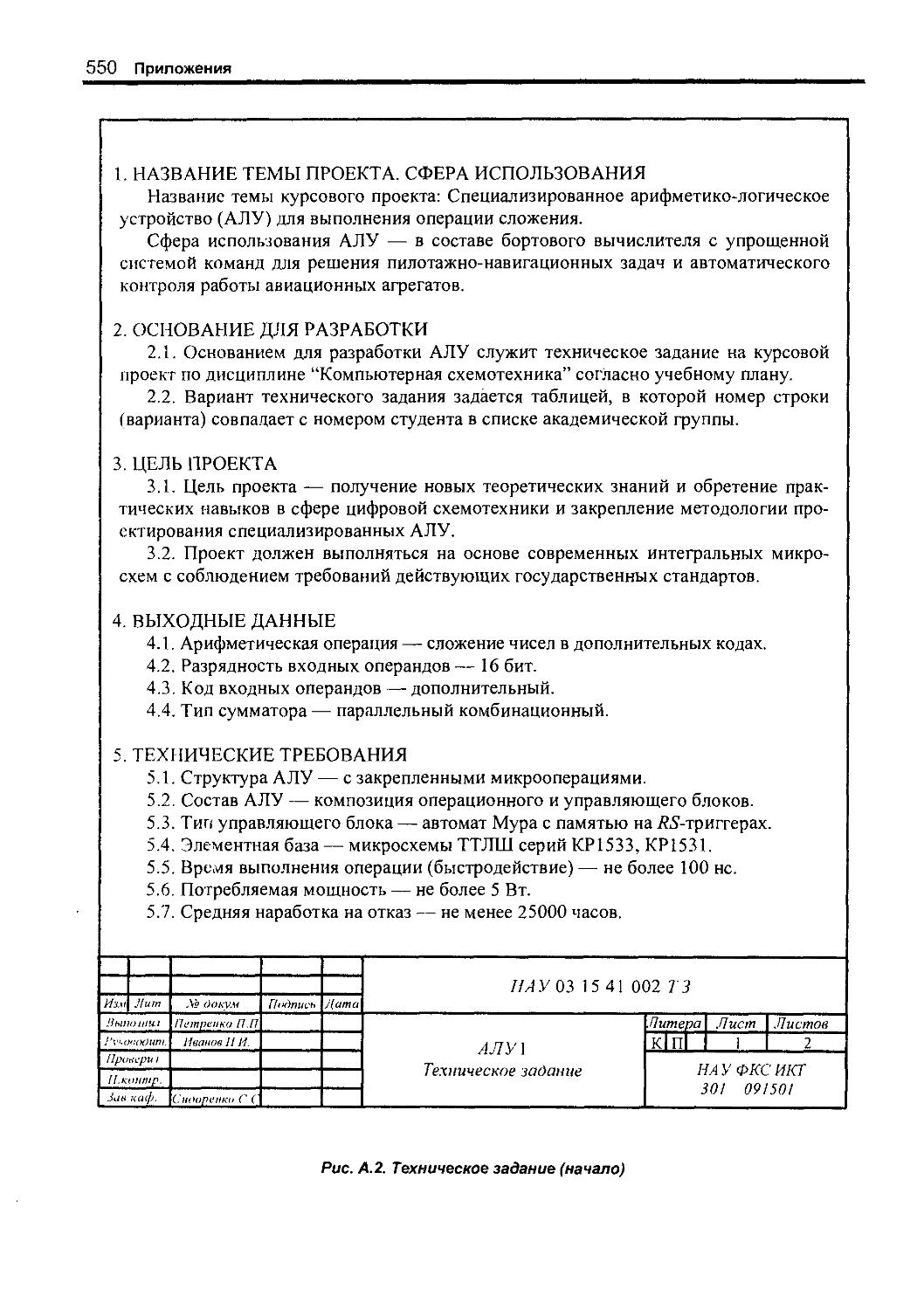

Теоретической основой компьютерной схемотехники является алгебра логики — наука, которая использует математические методы для решения логических задач. Алгебру логики называют булевой в честь английского математика Дж. Буля, внесшего наибольший вклад в развитие этой науки.