Author: Понтов Б.Н.

Tags: общее машиностроение машиноведение электроника летательные аппараты цифровые устройства издательство маи-принт

ISBN: 978-5-7035-1945-5

Year: 2008

Text

ЦИФРОВЫЕ УСТРОЙСТВА

СИСТЕМ ПРИВОДОВ

ЛЕТАТЕЛЬНЫХ АППАРАТОВ

ФЕДЕРАЛЬНОЕ АГЕНТСТВО ПО ОБРАЗОВАНИЮ

МОСКОВСКИЙ АВИАЦИОННЫЙ ИНСТИТУТ

(государственный технический университет)

Б.Н. ПОПОВ

ЦИФРОВЫЕ УСТРОЙСТВА

СИСТЕМ ПРИВОДОВ

ЛЕТАТЕЛЬНЫХ АППАРАТОВ

Допущено Учебно-методическим объединением высших

учебных заведений Российской Федерации по образова¬

нию в области авиации, ракетостроения и космоса в

качестве учебного пособия для студентов высших

учебных заведений РФ, обучающихся

по направлению подготовки дипломированного

специалиста 160600

«Интегрированные системы летательных аппаратов»

и специальности 160603

«Системы приводов летательных аппаратов»

Москва

Издательство МАИ-ПРИНТ

2008

ББК 34.447

П 58

П58 Попов Б.Н. Цифровые устройства систем приводов летатель¬

ных аппаратов: Учебное пособие. — М.: Изд-во МАИ-ПРИНТ,

2008. — 124 с.: ил.

ISBN 978-5-7035-1945-5

Изложены основы теории цифровых устройств и методы их про¬

ектирования. Рассмотрены комбинационные и последовательностные

цифровые устройства, преобразователи информации, применяемые в

системах автоматики. Большое внимание уделено вопросу минимиза¬

ции логических функций. Приведены примеры цифровых устройств,

используемых в системах приводов ЛА, в том числе устройства управ¬

ления двигателями.

Предназначено для студентов авиационных вузов, обучающихся

по специальности «Системы приводов летательных аппаратов» и смеж¬

ным специальностям.

Рецензенты:

кафедра «Системы автоматического управления» Тульского госу¬

дарственного университета (зав. каф. д-р техн, наук, проф. О.В. Горя¬

чев)-,

канд. техн, наук В.П. Андреев

ISBN 978-5-7035-1945-5 © Московский авиационный институт

(государственный технический университет), 2008

© Попов Б.Н., 2008

1. ВВЕДЕНИЕ В ЦИФРОВУЮ ЭЛЕКТРОНИКУ

1.1. Место и назначение цифровых устройств

в следящих приводах

В состав современных систем приводов ЛА входят разнообраз¬

ные цифровые либо микропроцессорные устройства. Такие приво¬

ды называют цифровыми следящими приводами (ЦСП).

Блок-схема современного автономного ЦСП представлена на

рис. 1.1, где приняты следующие обозначения: ЦУМ — цифровая

управляющая машина; СМВ — специализированный микропроцес¬

сорный вычислитель; ЦАП — цифроаналоговый преобразователь;

АЦП — аналого-цифровой преобразователь; ИУ — исполнительное

устройство, состоящее из усилителя мощности, исполнительного

двигателя и механической передачи; ЦЭУПУ — цифровое электрон¬

но-усилительное преобразовательное устройство.

ЦУМ реализует требуемый закон движения выходного звена

привода и передает его в виде двоичного «-разрядного кода Кв на

вход привода.

СМВ получает «-разрядные коды Кв и К,-, вычисляет код ошиб¬

ки: Кд= Кв — Кс и далее — код управления Ку. СМВ обеспечивает

реализацию требуемых динамических свойств привода, т.е. реали-

Место цифровых устройств

Рис. 1.1. Блок-схема ЦСП

3

зует цифровую коррекцию, экстраполяцию, пересчет координат,

обработку информации с первичных датчиков, алгоритмы встроен¬

ного контроля.

ЦАП преобразует код управления в маломощный электричес¬

кий аналоговый сигнал.

ИУ — это электро- (пневмо-, гидро-) механический преобразо¬

ватель, который преобразует маломощный электрический сигнал в

перемещение (угловое либо линейное).

АЦП преобразует механическое перемещение в «-разрядный

двоичный код Кс.

ЦЭУПУ представляет собой управляющий информационный

канал следящего привода.

1.2. Условные обозначения цифровых интегральных

микросхем

Основные определения, используемые в цифровой электрони¬

ке, приведены в ГОСТ 17021-88.

Интегральная микросхема (ИС) — микроэлектронное изделие,

выполняющее определенную функцию преобразования и обработки

сигналов. ИС состоит из элементов (транзистор, конденсатор, ре¬

зистор, диод). Совокупность элементов реализуется в технологичес¬

ком процессе. В состав ИС могут входить компоненты — самосто¬

ятельные микроэлектронные изделия (например, бескорпусной тран¬

зистор), в этом случае ИС называют гибридной. ИС бывают аналого¬

вые и цифровые. В данном пособии рассматриваются преимуществен¬

но цифровые ИС.

ИС разрабатываются и выпускаются предприятиями в виде се¬

рий. К серии относят совокупность ИС, которые выполняют различ¬

ные функции, но имеют единое конструктивное и технологическое

исполнение. Таким образом, у всех ИС одной серии одинаковый вид

корпуса. Корпус — часть конструкции ИС, предназначенная для

защиты микросхемы от внешних воздействующих факторов и для

соединения с внешними электрическими цепями с помощью выво¬

дов.

По конструктивно-технологическому исполнению все серии ИС

делятся на три группы: полупроводниковые, гибридные, прочие.

Этим группам в системе условных обозначений присвоены цифры:

4

1, 5, 6, 7 — полупроводниковые ИС; 2, 4, 8 — гибридные ИС; 3 —

прочие ИС.

По функциональному признаку ИС делятся на подгруппы (на¬

пример, логические элементы, триггеры, преобразователи, схемы

арифметических и дискретных устройств).

Обозначение ИС состоит из четырех обязательных полей.

Первое поле — цифра, определяющая конструктивно-техноло¬

гическую группу.

Второе поле — две или три цифры, характеризующие порядко¬

вый номер серии внутри данной технологической группы. Таким

образом, первые два поля составляют три или четыре цифры и оп¬

ределяют полный номер серии ИС.

Третье поле — две буквы, соответствующие подгруппе и виду

ИС. Подгруппа определяет функциональное назначение ИС (логи¬

ческие элементы — Л, триггеры — Т, схемы цифровых устройств —

И и т.д.). Вид конкретизирует функциональное назначение ИС внут¬

ри подгрупп (триггеры: универсальные — В, счетные — Т, с задер¬

жкой — Ми т.д.).

Четвертое поле — порядковый номер разработки ИС серии внут¬

ри в данного вида, может состоять из одной или двух цифр.

Впереди обозначения могут быть одна или две буквы. Если буква

одна, то это условия изготовления на заводе (номер приемки мик¬

росхемы).

После четвертого поля также может стоять буква (А, Б, В, Г),

характеризующая электрический разброс параметров.

В качестве примера рассмотрим ИС КМ555ЛАЗ (рис. 1.2).

п

К М 5 55 Л АЗ

1Т Номер разработки ИС данного вида

Вид (по функциональному признаку)

Подгруппа (по функциональному назначению)

Порядковый номер данной серии

Группа (по конструктивно-технологическому исполнению)

Особенности конструктивного исполнения

Условие приемки на заводе-изготовителе

Рис. 1.2. Обозначение интегральной схемы

5

По степени интеграции (число элементов на кристалле) микро¬

схемы делятся на простые интегральные схемы (до 100), средней сте¬

пени интеграции (до 1000), большие интегральные схемы (до 10000)

и сверхбольшие ИС (свыше 10000).

1.3. Параметры цифровых интегральных микросхем

Базовым элементом любой цифровой микросхемы является

транзистор, работающий в режиме переключения и обеспечивающий

представление двоичной информацйи. В зависимости от типа ис¬

пользуемых транзисторов различают биполярные и МДП (металл

— диэлектрик — полупроводник) микросхемы. По способу представ¬

ления двоичной информации (0 и 1) цифровые микросхемы делят¬

ся на потенциальные и импульсные. Для ИС потенциального типа

уровни напряжения, соответствующие логическим нулю и единице

при стандартном пятивольтовом напряжении питания, показаны на

рис. 1.3.

Параметры цифровых микросхем разделяют на электрические

и динамические. К первым относят:

U® — уровень напряжения, соответствующий логическому нулю.

ТТЛ

Уровень

логического

НУЛЯ

Уровень

логической

единицы

Рис. 1.3. Уровни напряжения для ИС потенциального типа

6

Ul — уровень напряжения, соответствующий логической еди¬

нице.

/«х > — входной ток, соответствующий логическим нулю и

единице.

N— коэффициент разветвления по выходу (нагрузочная спо¬

собность).

М — коэффициент объединения по входу (число логических

входов элемента).

Р — потребляемая мощность.

t/n — напряжение питания.

К динамическим параметрам относят коэффициенты задержки

<°).

В настоящее время существует устойчивая тенденция к перехо¬

ду на пониженное напряжение питания ИС. Ряд микросхем уже сей¬

час имеет напряжение питания 3,3 В и 1,8 В. Это автоматически при¬

водит к изменению уровней напряжения, соответствующих логичес¬

ким нулю и единице.

1.4. Условные графические обозначения цифровых устройств

на принципиальных электрических схемах

По виду элементов, входящих в состав изделия, связей между

ними и назначению схемы подразделяют на виды и типы по ГОСТ

2.701-84 (табл. 1.1).

Таблица 1.1

Вид схемы

Обозначение

Тип схемы

Обозначение

Электрическая

Э

Структурная

1

Гидравлическая

Г

Функциональная

2

Пневматическая

П

Принципиальная

3

Кинематическая

К

Монтажная

4

Оптическая

Л

(соединений)

Комбинированная

С

Подключения

5

Энергетическая

Р

Общая

6

Расположения

7

Совмещенная

0

7

На схеме электрической принципиальной (ЭЗ) указывают все

элементы, необходимые для построения цифрового устройства, связи

между элементами и элементы, которые заканчивают входные и

выходные цепи.

Правила построения условных графических обозначений (УГО)

элементов и устройств цифровой техники устанавливает ГОСТ 2.743-

91, согласно которому элементы схемы — УГО изделия или части

изделия, реализующие функцию или систему функций алгебры ло¬

гики, например, микросхема интегральная, микросборка, набор эле¬

ментов, их части и совокупности.

К элементам цифровой техники относят ряд аналоговых элемен¬

тов и устройств (например: конденсатор, операционный усилитель,

резистор), используемых совместно с цифровыми элементами.

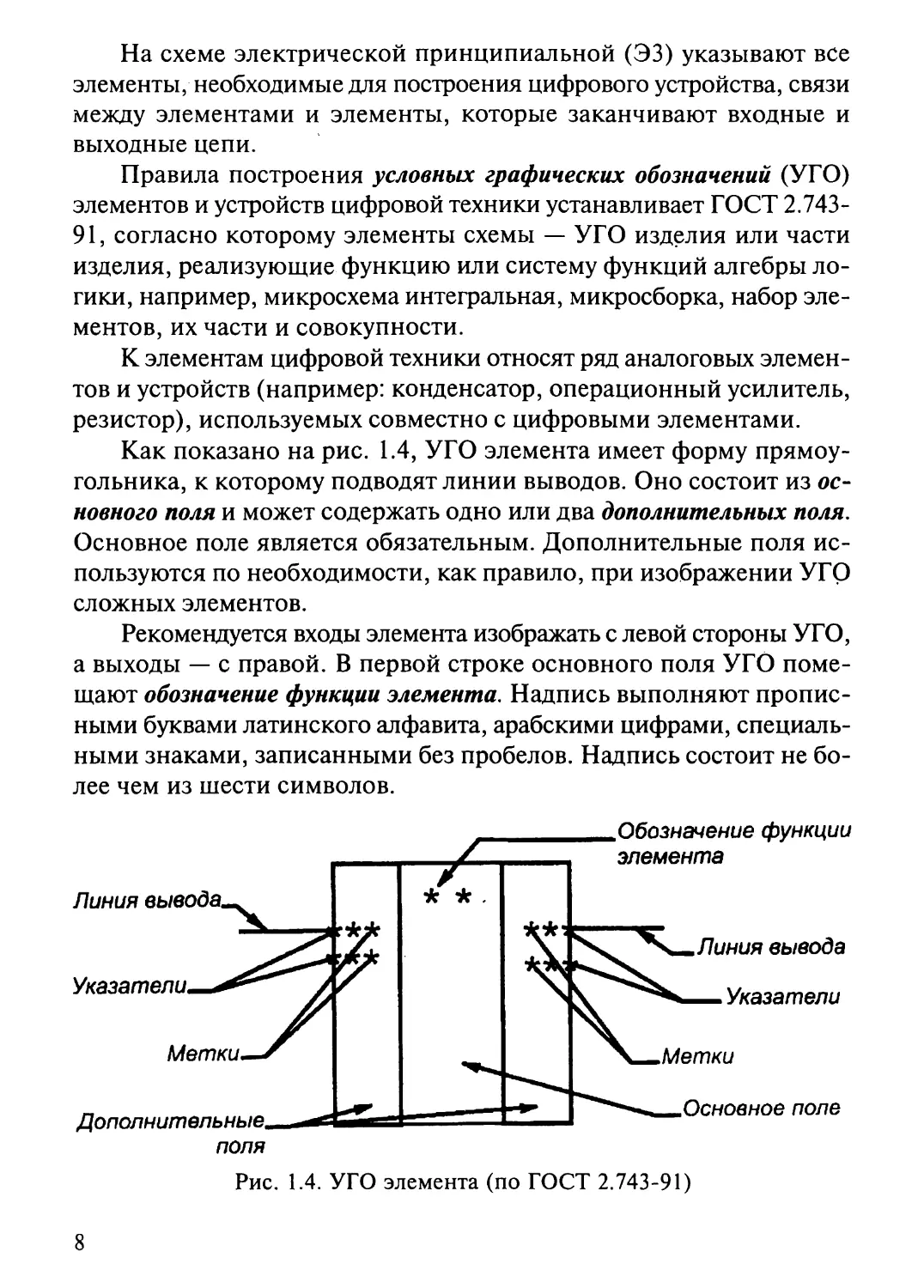

Как показано на рис. 1.4, УГО элемента имеет форму прямоу¬

гольника, к которому подводят линии выводов. Оно состоит из ос¬

новного поля и может содержать одно или два дополнительных поля.

Основное поле является обязательным. Дополнительные поля ис¬

пользуются по необходимости, как правило, при изображении УГО

сложных элементов.

Рекомендуется входы элемента изображать с левой стороны УГО,

а выходы — с правой. В первой строке основного поля УГО поме¬

щают обозначение функции элемента. Надпись выполняют пропис¬

ными буквами латинского алфавита, арабскими цифрами, специаль¬

ными знаками, записанными без пробелов. Надпись состоит не бо¬

лее чем из шести символов.

Рис. 1.4. УГО элемента (по ГОСТ 2.743-91)

8

Все выводы имеют указатели и могут иметь метки.

Указатели определяют тип поступающего сигнала и его актив¬

ное состояние.

Метка — функциональное обозначение вывода, помещается в

дополнительном поле напротив соответствующего вывода и также

содержит не более чем шесть символов. Функционально подобные

метки выводов с помощью горизонтальных линий объединяют в зоны.

Наиболее часто используемые варианты указателей выводов, ре¬

комендуемые ГОСТом, показаны на рис. 1.5, где а — прямые стати¬

ческие; б — инверсные статические; в — прямые динамические; г —

инверсные динамические; д — не несущие логической информации.

Размер УГО схемы по горизонтали определяется наличием или

отсутствием дополнительных полей. Рекомендуется, чтобы сумма

ширины двух дополнительных полей была равна ширине основного

поля. Размер УГО по вертикали определяется количеством выводов

с той стороны, где их больше, и параметром С (рис. 1.6).

4 Ф 4?

О- О- 4} 4~

а) б) г) д)

Рис. 1.5. Условное обозначение указателей выводов

9

При изготовлении принципиальных электрических схем реко¬

мендованная ширина основного поля составляет 10 мм, дополни¬

тельного — 5 мм, высота строки (размер Q — 5 мм.

Наиболее часто встречающиеся формы УГО цифровых элемен¬

тов приведены на рис. 1.6. Элементы на принципиальных электри¬

ческих схемах имеют сплошную нумерацию, проставляемую сверху

графического обозначения элемента. При этом цифровые ИС реко¬

мендуется обозначать DD, аналоговые — DA. Если элементы, при¬

надлежащие одной ИС, расположены в разных местах принципи¬

альной схемы, они обозначаются как DD1.1, DD1.2, DD1.3.

Соединение цифровых элементов между собой в более сложные

устройства осуществляют с помощью проводников (в том числе

печатных), кабелей и шин. Их изображения на принципиальных

электрических схемах определяются в ГОСТ 2.755-87.

Для уменьшения числа проводников (соединительных линий)

на принципиальных электрических схемах применяются шины. Шина

— это соединительная линия утроенной толщины, использующая

внутреннюю адресацию.

Для соединения двух и более цифровых блоков между собой

используют разъемы. В основном применяют разъемы двух типов:

круглые и плоские. На принципиальных электрических схемах разъе¬

мы обозначаются в виде таблиц, имеющих две колонки: большая

часть называется «цепь», меньшая — «контакт» (К). В колонке «цепь»

указывают функциональное назначение сигнала. Вто¬

Цепь

К

АО

1

А 1

2

А2

3

АЗ

4

D13

10

D 14

11

D 15

12

рая колонка предназначена для указания порядкового

номера контакта (рис. 1.7). Для круглых разъемов ис¬

пользуется цифровая нумерация, для плоских (мно¬

горядных) — буквенно-цифровая: каждый ряд обо¬

значается буквой, внутри ряда — цифрой.

Для разработки цифровых устройств используют¬

ся многочисленные пакеты автоматизированного

проектирования, которые основаны на западных

стандартах УГО цифровых ИС. В табл. 1.2 даны не¬

которые сравнительные изображения отечественных

и импортных УГО.

Рис. 1.7. УГО

разъема

10

Таблица 1.2

Тип элемента

Российский стандарт

(ГОСТ 2.743-91)

Западный стандарт

(MIL/ANSI)

НЕ

1

>

И

&

о

НЕ-И

&

=г>

ИЛИ

1

о

СУММА

ПО МОДУЛЮ 2

=1

э >

D-триггер

D

>

тт

Q

■ D Q

CLR

Т

2. КОМБИНАЦИОННЫЕ ЛОГИЧЕСКИЕ СХЕМЫ

2.1. Основные определения

Логической переменной называют электрический (гидравличес¬

кий, пневматический и т.д.) сигнал, принимающий два существен¬

но различных значения, известные как состояния ИСТИНА (TRUE)

и ЛОЖЬ (FALSE). В практике истинное и ложное состояния часто

обозначают терминами: «высокий-низкий уровни», «логическая 1 —

11

логический 0». Обозначение логической переменной в виде 1 и О

является наиболее удобным.

Логической схемой называют такую схему, которая выполняет

логические операции над одной или несколькими логическими пе¬

ременными.

Комбинационной логической схемой называют такую схему, вы¬

ходное состояние которой определяется только комбинацией вход¬

ных логических переменных в данный момент времени.

Раздел математики, посвященный исследованию свойств пере¬

менных величин, принимающих только два значения, называется

алгеброй логики или булевой алгеброй — по имени английского мате¬

матика Джорджа Буля (1815—1864). Булева алгебра применяется при

формальном описании и синтезе цифровых блоков, устройств и

систем. По аналогии с заданием любых математических функций,

задание логических функций означает определение правила (зако¬

на, алгоритма), согласно которому всем возможным значениям ар¬

гумента ставится в соответствие значение функции. Особенностью

логических функций является то, что аргументы (переменные) и сами

функции могут принимать лишь два значения: 1 и 0. Функции, не

зависящие ни от каких переменных, называются константами. Оче¬

видно, что в булевой алгебре имеются две константы: 1 и 0.

2.2. Логические функции одной переменной

Логические функции удобно задавать таблично. Рассмотрим

логическую функцию одной переменной, заданную таблично

(табл. 2.1, где i — номер набора логической переменной; X— логи¬

ческая переменная (аргумент); Fo ... F3 — логические функции).

Таким образом, как следует из табл. 2.1, существуют четыре

функции одной логической переменной. Функции Fo и F3 не зави¬

сят от значения аргумента и соответственно называются КОНСТАН¬

ТА 0 и КОНСТАНТА 1. Значение функции Fj повторяет значение

Таблица 2.1

i

X

Fo

F,

F2

F3

0

0

0

0

1

1

1

1

0

1

0

1

12

аргумента X F2 s X. Эта функция применяется достаточно редко.

Наибольший интерес для теории и практики представляет функция

F которая очень часто используется и называется ИНВЕРСИЯ (ОТ¬

РИЦАНИЕ, НЕ). Она обозначается верхним подчеркиванием аргу¬

мента, F2 — X (читается F2 равно не X). Логический элемент (схе¬

ма), реализующий функцию ИНВЕРСИЯ, называется инвертором.

На рис.2.1 показаны принципиальная схема простейшего инвер¬

тора (с) и его условное графическое обозначение на электрических

принципиальных схемах (б).

Рис. 2.1. Принципиальная схема (а) и УГО (б) инвертора

2.3. Логические функции двух переменных

Задать логическую функцию нескольких переменных — значит

определить ее значения 0 или 1 на всех возможных наборах (комби¬

нациях) значений этих переменных, причем две логические функ¬

ции считаются различными, если их значения не совпадают хотя бы

на одном наборе значения переменных. Рассмотрим логические

функции двух переменных, заданные таблично (табл. 2.2).

Из табл. 2.2 следует, что существует 16 логических функций двух

переменных. Функции, симметрично расположенные относительно

линии, разделяющей F7m Fs, взаимно инверсны.

Функции Fo и FJS по аналогии с логическими функциями одной

переменной называются КОНСТАНТА 0 и КОНСТАНТА 1. Функ¬

ция Fj называется КОНЪЮНКЦИЯ (ЛОГИЧЕСКОЕ УМНОЖЕ¬

НИЕ, И). Функция Fj (рис. 2.2,а) принимает значение логической

1 только тогда, когда оба аргумента принимают значения логичес-

13

Таблица 2.2

i

X,

х0

Fo

F,

Р2

F3

F<

Fs

F6

F7

Fs

F9

Fl0

F„

F,2

Fl3

F„

FIS

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

0

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

2

1

0

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

3

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

а) б)

в) г)

кой 1. Симметричная ей функция

F14 (рис. 2.2,6) - ОТРИЦАНИЕ

КОНЪЮНКЦИИ (НЕ-И). Функ¬

ция F7 (рис. 2.2,в) называется

ДИЗЪЮНКЦИЯ (ЛОГИЧЕСКОЕ

СЛОЖЕНИЕ, ИЛИ) и принимает

значение логической 1 только тог¬

да, когда хотя бы одна логическая

Рис. 2.2. УГО элементов,

реализующие простейшие

логические функции

переменная принимает значение ло¬

гической 1. Симметричная ей фун¬

кция 7>(рис. 2.2,г) - ОТРИЦАНИЕ

ДИЗЪЮНКЦИИ (НЕ-ИЛИ).

Одной из наиболее часто ис¬

пользуемых в цифровых устройствах

следящих приводов логических фун¬

кций является F6 (рис. 2.2,6) —

СУММА ПО МОДУЛЮ 2. Инверс¬

ная ей функция F9 называется РАВ¬

НОЗНАЧНОСТЬ (рис. 2.2,е). При¬

ведем ряд форм записи элементарных функций двух переменных:

14

2.4. Основные соотношения булевой алгебры

Булева алгебра, как и другие разделы математики, основывает¬

ся на ряде постулатов, из которых следует ряд соотношений, наибо¬

лее часто используемых на практике.

Двойное отрицание (отрицание отрицания) переменной равно

самой переменной:

Х = Х.

Остальные 20 соотношений можно получить из табл. 2.2:

Avl = l;

AvO = A;

AvA = A;

AvA = l;

X 1 = А; X 0 = 0;

X Х = Х;

X А = 0;

Avl = 0;

AvO = A;

XvX = X;

AvA = 0;

X -1 = А; X 0 = 1;

X х = х,

АА = 1;

А®1 = А; А®0 = А;

х®х=о-

АФА = 1.

(2.1)

Первая строка соответствует функции F7, вторая — третья —

Fs, четвертая — FJ4 и пятая — F6. Все соотношения получены из

табл. 2.2 при условии, что Xj=X При этом для первого столбца спра¬

ведливо: Хд — 1; для второго — Хд= 0; для третьего — Хо = X; для

четвертого — Хо = X .

Основные соотношения булевой алгебры можно распространить

на функции п переменных. Например, выражение Av 1=1 для фун¬

кции трех переменных имеет вид

A2vA2vA7v 1 = 1 или AjXjXjV 1 = 1.

2.5. Формулы де Моргана

Формулы де Моргана определяют законы двойственности, со¬

гласно которым устанавливается связь между функциями конъюнк¬

ции и дизъюнкции:

A2vA; = A2A/;

(2.3)

Х2^Х^Х2-Х^,

15

(2.4)

Х2 -Х^Х^Х,,

Х2Х}=Х~2^1. (2.5)

На примере выражения (2.2) покажем справедливость формул

де Моргана. Для этого методом перебора докажем, что тождество

верно для всех наборов переменных Х2 и Х2 (табл. 2.3).

Таблица 2.3

/

Х2

X,

X2vXj

*2

X,

х2 Xi

0

0

0

0

1

1

1

1

1

0

1

1

0

1

0

0

2

1

0

1

0

0

1

0

3

1

1

1

0

0

0

0

Из табл. 2.3 следует, что функции, стоящие в левой и правой

части выражения (2.2), принимают одинаковые значения на каж¬

дом из возможных наборов переменных.

Формулы де Моргана можно распространить на функции п пе¬

ременных. Например, выражение (2.3) для функции четырех пере¬

менных имеет вид:

Х4 v Х2 v Х2 v Xj = Х4 • Хз ■ Х2 • Xi.

Формулы де Моргана позволяют выражать дизъюнкции через

конъюнкции и отрицания (или конъюнкции через дизъюнкции и

отрицания).

2.6. Основные свойства логических функций

Рассмотрим три наиболее часто используемых свойства логичес¬

ких функций и проиллюстрируем их на примере функций двух пе¬

ременных. При этом отметим, что эти свойства можно распростра¬

нить на логические функции п переменных.

1. Свойство коммутативности', порядок переменных при вы¬

полнении операции не влияет на результат этой операции:

16

X,vX2=X2v Xj,

X1x2=x2x1-, (26)

XjX2=X2-Xj.

2. Свойство ассоциативности', переменные можно группировать

в любом порядке, например для операций И и ИЛИ:

Xj v Х2 v Х3 = (Xj v Х2) vX3=XjV (Х2 v Х3);

Х1Х2Х3^(Х1Х2)Х3=Х1(Х2Х3). (2-7)

3. Свойство дистрибутивности', общие части конъюнкций (дизъ¬

юнкций) можно выносить за скобки, если они объединены знаком

дизъюнкции (конъюнкции). В случае необходимости можно раскры¬

вать скобочные выражения:

Xj- Х2 V Xj • Х3 = Xj • (v Х3); (2.8)

(XjvX2)(XjvX3)^XjvX2-Х3. (2.9)

Докажем тождество (2.9):

(Xj vX2)(XjvX3) = Xj-XjvXj-X3vXj-X2vX2-X3.

Согласно основным соотношениям (2.1):

Xj-Xj=Xj,

тогда

XjXjvXjX3vXj-X2vX2X3=Xj vXj-X3vXj-X2 vx2-x3.

Согласно свойству дистрибутивности (2.8), общие части конъ¬

юнкций можно вынести за скобку, тогда:

XjvXj-X3 vXj-X2vX2-X3=Xj(lvX3 vl2)v Х2-Х3.

Выражение в скобках в соответствии с (2.1) равно единице, а

конъюнкция любой переменной с логической единицей дает логи¬

ческую переменную. Выражение (2.9), таким образом, доказано.

17

Практический интерес представляют два следствия из свойства

дистрибутивности. Пусть в выражении (2.9)

Xt=A - Х2 = Л, Х3 = В ;

(2.Ю)

тогда, подставляя (2.10) в (2.9), получим

(AvA)(AvB) = AvA-B.

Очевидно, что выражение в первых скобках равно единице, откуда

окончательно следует:

Av А-В = Av В.

Аналогично (2.11) можно показать, что:

Av Л В = Av В.

(2.11)

(2.12)

Выражения (2.11, 2.12) используются для минимизации логических

функций.

2.7. Совершенная дизъюнктивная нормальная форма

Для перехода от табличного представления логических функций

к алгебраическому каждому набору переменных ставится в соответ¬

ствие минтерм — конъюнкция всех переменных, которые входят

либо в прямом виде, если значение данной переменной на наборе

равно 1, либо в инверсном виде, если значение переменной на на¬

боре равно 0. Для к переменных составляются q = 2к минтермов: т0,

mq_j.

Значение функции Fj, соответствующее f-му набору перемен¬

ных, будем обозначать f...

Совершенной дизъюнктивной нормальной формой (СДНФ) будем

называть алгебраическое представление функции Fj как логической

суммы минтермов, для которых f.. =1.

В общем случае произвольную логическую функцию можно

определить как

Выражение (2.13) и называется СДНФ.

18

В качестве примера приведем все минтермы для функций двух

переменных (табл. 2.4) и найдем СДНФ для функции F9.

Таблица 2.4

i

х,

Хо

F,

Минтермы

0

0

0

1

т0 = Xi Хо

1

0

1

0

nil — X1 Xq

" 2

1

0

0

т2 = Хг Хо

3

1

1

1

т3 = 1 ' *0

Как следует из табл. 2.4 и выражения (2.13), СДНФ функции F9

есть логическая сумма минтермов, соответствующих наборам пере¬

менных, для которых f9i =1:

F9 = f90m0 v f91ml V ff2m2 V f93m3 =^<X1X0)v

vO ■ (Yj xg) v 0 • (x, • то) v I - (Xj x0)=x~, • Yo v xt • x0.

По СДНФ просто построить схему любого логического устрой¬

ства, реализующего заданную функцию. Но СДНФ не является

минимальной формой записи логической функции для ее реализа¬

ции. Она часто служит исходной формой логической функции для

ее последующей минимизации.

2.8. Полные системы логических функций

Так как любую логическую функцию можно представить в виде

СДНФ, а сама СДНФ записывается с помощью трех элементарных

функций КОНЪЮНКЦИЯ, ДИЗЪЮНКЦИЯ и ОТРИЦАНИЕ, то

это означает, что эти три функции представляют полную систему

логических функций или базис. Минимальным базисом называют

такую полную систему логических функций, удаление из которой

хотя бы одной функции превращает ее в неполную систему.

Базис КОНЪЮНКЦИЯ, ДИЗЪЮНКЦИЯ и ОТРИЦАНИЕ не

является минимальным. Это следует из того, что в соответствии с

формулами де Моргана ДИЗЪЮНКЦИЮ можно выразить через

19

КОНЪЮНКЦИЮ и ОТРИЦАНИЕ, поэтому система логических

функций КОНЪЮНКЦИЯ и ОТРИЦАНИЕ также является бази¬

сом, и при том минимальным. Аналогично минимальным базисом

является система логических функций ДИЗЪЮНКЦИЯ и ОТРИ¬

ЦАНИЕ, поскольку КОНЪЮНКЦИЯ по формуле де Моргана мо¬

жет быть выражена через ДИЗЪЮНКЦИЮ и ОТРИЦАНИЕ. Ми¬

нимальным базисом являются также логические функции НЕ-И и

HE-ИЛИ. Отсюда следует один очень важный практический вывод:

любую, сколь угодно сложную логическую функцию или цифровое ус¬

тройство можно реализовать с помощью ИС одного типа — двух¬

входовых элементов НЕ-И (HE-ИЛИ). В качестве примера приве¬

дем реализацию функции Fk (СУММА ПО МОДУЛЮ 2) в трех ба¬

зисах И, ИЛИ, НЕ (рис. 2.3,а), НЕ-И (рис. 2.3,6), НЕ-ИЛИ

(рис. 2.3,в). Для второго и третьего случаев сформулируем правило:

Если необходимо реализовать некоторую логическую фун¬

кцию, заданную в виде СДНФ, с помощью элементов НЕ-И

(HE-ИЛИ), предварительно следует с помощью формул де

Моргана привести функцию к виду, в котором исключена

ДИЗЪЮНКЦИЯ (КОНЪЮНКЦИЯ).

2.9. Минимизация логических функций

Минимизация логических функций позволяет решить задачу

уменьшения веса, габаритов, потребляемой мощности и стоимости

изделий электронной техники.

Большинство известных методов минимизации основано на

применении следующих трех операций.

1. Операция склеивания. Назовем соседними две такие конъюнк¬

ции, которые имеют одну длину (число переменных, объединенных

знаком конъюнкции) и отличаются знаком инверсии только одной

переменной. Например, конъюнкции

X5X4X3X2Xj и XsX4JT3X2Xj

отличаются знаком инверсии Х3. Для каждой конъюнкции п пере¬

менных существует п соседних конъюнкций.

20

Рис. 2.3. Реализация функции «Сумма по модулю 2» в трех базисах

Запишем дизъюнкцию этих соседних конъюнкций и преобразу¬

ем ее согласно свойству дистрибутивности:

Выражение в скобках согласно основным соотношениям буле¬

вой алгебры равно 1, алогическое умножение некоторого выраже¬

ния на 1 равно самому выражению и окончательно:

21

Таким образом, две соседние конъюнкции склеиваются, т.е.

вместо их дизъюнкции можно записать одну конъюнкцию, длина

которой на единицу меньше длины исходных конъюнкций, и в нее

не входит переменная, по которой исходные конъюнкции являются

соседними. Окончательно запишем:

Р XvP Х = Р,

где Р— произвольная конъюнкция.

2. Операция поглощения (в общем виде):

РХуР=Р.

Приведем доказательство этого выражения:

Р XvP = P XvP l = P(Xvl) = P 1 = Р.

3. Операция неполного склеивания:

Р XvP X = PvP XvP X.

Согласно операции склеивания левая часть этого тождества равна

Р. Докажем, используя операцию поглощения, что и правая часть

тождества равна Р.

PvP XvPX = (PvP X)vP X = PvP X = P.

Можно показать также, что

Р XvP X = PvP X;

Р XvP X = PvP X.

Из операции неполного склеивания следует, что каждая из скле¬

иваемых конъюнкций может быть использована для склеивания с

другими соседними конъюнкциями.

Рассмотрим пример минимизации логической функции. Пусть

некоторая функция четырех переменных задана таблично (табл. 2.5).

22

Таблица 2.5

i

Х3

Х2

X,

Хв

F

0

0

0

0

0

0

1

0

0

0

1

1

2

0

0

1

0

0

3

0

0

1

1

0

4

0

1

0

0

1

5

0

1

0

1

1

6

0

1

1

0

0

7

0

1

1

1

0

8

1

0

0

0

0

9

1

0

0

1

1

10

1

0

1

0

0

11

1

0

1

1

0

12

1

1

0

0

0

13

1

1

0

1

1

14

1

1

1

0

0

15

1

1

1

1

0

Запишем СДНФ логической функции:

F = Xз • Х2 • Xi • Хд v Xз • Х2 • Xi Хо v

^Хз ■ Х2 Xi Хд vХ3 -Х2 -Хз Хд v

vX3 -Х2 -Xj -Хд.

Попарно соседними конъюнкциями являются конъюнкции с

номерами 1 и 5, 4 и 5, 9 и 13. Проведя операции склеивания для пар

соседних конъюнкций, получим:

F = Хз ■ Xi • Хо v Хз ■ Х2 • Xi v Х3 • Xi ■ Хо.

Очевидно, что в данном выражении первая и третья конъюнкции

являются соседними по переменной Х3 и могут быть склеены:

F = Х1Х0чХзХ2Х1. (2.14)

Так как дальнейшее применение операций склеивания и погло¬

щения невозможно, то последнее выражение для минимизируемой

функции называют тупиковой дизъюнктивной нормальной формой

(ТДНФ).

23

При склеивании могут получится несколько различных ТДНФ.

Самая простая из всех возможных ТДНФ называется минимальной

дизъюнктивной нормальной формой (МДНФ).

2.10. Карты Карно (Диаграммы Вейча)

2.10.1. Общие понятия

Карты Карно реализуют графоаналитический метод представ¬

ления и упрощения булевых выражений.

Карта Карно — это таблица специального вида, имеющая 2я

клеток, где п — число логических переменных. Каждой клетке кар¬

ты Карно соответствует определенный минтерм. Карты Карно для

п = 2, 3, 4, 5, 6 показаны на рис. 2.4.

Переменные в карте Карно расположены так, что при переходе

от каждой клетки к соседней изменяется состояние только одной

переменной (рис. 2.4). В карте Карно п переменных имеется 2п зон,

из которых п — прямые зоны и ровно столько же инверсных зон.

Зоной будем называть часть карты Карно, в которую соответствую¬

щая переменная входит либо только без знака инверсии (Aj), либо

только со знаком инверсии (Xi).

Прямой зоной карты Карно назовем такую ее часть, в которую

переменная Xi входит без знака инверсии.

Инверсной зоной карты Карно назовем ту часть, в которую пере¬

менная Xt входит со знаком инверсии.

Линии, разделяющие карту Карно на зоны А^.и Xk, назовем ося¬

ми карты Карно (Ох,).

Каждая клетка карты Карно имеет уникальный номер (адрес),

который является десятичным эквивалентом соответствующего мин-

терма.

Существует несколько схем увеличения размерности карт Кар¬

но. В настоящее время наиболее часто используется ступенчатая

форма.

При ступенчатой схеме развертывания карт Карно выбирается

новая ось, совпадающая либо с нижней стороной карты Карно, если

исходная карта прямоугольная, либо с правой стороной карты, если

карта — квадрат. Далее, относительно этой оси зеркально отобра¬

жается исходная карта. Вся новая часть карты Карно считается но-

24

.0x0

Хо хо

Хо

0

1

5

4

2

3

7

6

10

11

15

14

8

9

13

12

0

1

5

4

20

21

17

16

2

3

7

6

22

23

19

18

.10

11

15

11

30

31

27

26

8

9

13

12

—Я

29

25

24

Хз

Хо Хо

0

1

5

4

20

21

17

16

2

3

7

6

22

23

19

18

10

11

15

14

30

31

27

26

8

9

13

12

28

29

25

24

40

41

45

44

60

61

57

56

42

43

47

46

62

63

59

58

34

35

39

38

$4

55

51

50

32

33

37

36

52

53

49

48

Хз

Х5

Х2

Х4

Рис. 2.4. Карты Карно для п = 2, 3, 4, 5, 6

вой зоной. Проводится нумерация клеток новой зоны, при этом

нумерация старых клеток не меняется.

Введем понятие покрытие единичных значений логической фун¬

кции в карте Карно как совокупность клеток карты, в которых про¬

ставлены единицы. При этом покрытие должно состоять из 2Г кле¬

ток, где г = 0,1, 2,..., (п — 1) называют рангом покрытия карты Карно

п переменных. Произвольная единичная клетка является покрыти¬

ем 0-го ранга.

25

Две единичные клетки составляют покрытие первого ранга (одна

ранее найденная и любая симметричная ей относительно какой-либо

оси карты).

Четыре единичные клетки образуют покрытие второго ранга

(одно ранее найденное покрытие первого ранга и любое симметрич¬

ное ему покрытие первого ранга относительно какой-либо оси кар¬

ты).

Восемь единичных клеток составляют покрытие третьего ранга

(одно ранее найденное покрытие второго ранга и любое симметрич¬

ное ему покрытие второго ранга относительно какой-либо оси кар¬

ты).

Каждому покрытию соответствует минтерм, причем, чем выше

ранг покрытия, тем меньшее число переменных в конъюнкции. На

рис. 2.5 и 2.6 приведены примеры покрытий первого и второго ран¬

гов для карт Карно трех и четырех переменных соответственно.

Основным достоинством карт Карно является то, что с их по¬

мощью можно быстро и просто отыскивать МДНФ. Отыскание

МДНФ по карте Карно состоит из двух этапов:

— покрытие всех единичных значений функции минимальным

числом покрытий максимально высокого ранга. При этом одна и та

же единичная клетка может входить в разные покрытия;

— объединение всех найденных покрытий (конъюнкций) зна¬

ком дизъюнкции.

Сформулируем два правила, согласно которым каждому макси¬

мальному покрытию ранга г можно поставить в соответствие конъ¬

юнкцию ТДНФ.

Хо

7

л 1 2)

7

1

(L

Рис. 2.5. Покрытия первого ранга

Х2

Рис. 2.6. Покрытия второго ранга

26

Рис. 2.7. Варианты соседних

клеток для карты Карно

при п = 4

1. Если покрытие пересекается осью Охр т.е. часть этого покры¬

тия лежит в зоне Xi, а часть — в зоне X., то переменная Xi в соот¬

ветствующую этому покрытию конъюнкцию не войдет.

2. Если покрытие целиком лежит

в зоне Xt( X.), то в соответствующую

этому покрытию конъюнкцию ТДНФ

войдет переменная Xi(Xi).

Каждой клетке карты Карно п пе¬

ременных соответствует п соседних

клеток. Все соседние клетки симмет¬

ричны относительно какой-либо оси

карты.

На рис. 2.7 для карты Карно четы¬

рех переменных показаны варианты

соседних клеток, которые используют¬

ся для отыскания максимальных по¬

крытий.

2,10.2, Минимизация полностью определенных

логических функций

Полностью определенной называют такую логическую функцию

п переменных, значения которой определены (0 или 1) на всех 2п

наборах переменных. Логическую функцию удобно задавать картой

Карно, поместив в клетке с номером i соответствующее значение (О

либо 1).

В качестве примера рассмотрим минимизацию логической фун¬

кции, заданной табл. 2.5, с помощью карты Карно.

Поставим в клетках карты Карно с номерами i соответствую¬

щие значения функции F(pHC. 2.8,я). В качестве исходного покры¬

тия 0-го ранга выберем единичную клетку с номером 1. Покрытие

1-го ранга можно получить, присоединяя к клетке 1 симметричную

ей относительно оси Ох2 единичную клетку с номером 5. Далее на¬

ходим симметричное найденному покрытию 1-го ранга относительно

оси Ох3 покрытие 1-го ранга, составленное единичными клетками с

номерами 9 и 13. Таким образом, четыре единичные клетки 1, 5, 9

и 13 образуют покрытие 2-го ранга. Увеличить ранг этого покрытия

27

I

I

Г I

Хо i

I

11

1

5

1

4

0

2

0

3

0

7

0

6

~ОхЗ

Хз

Xi

0

10

0

11

0

15

0

14

°в

19

1

0

12

I

I Х2

'0x2

Хо

0

<)

0

0

0

0

0

0

■о

0

0

'"■Г

Т

0

Х2

Хз

а) б)

Рис. 2.8. Минимизация полностью определенной логической функции

нельзя, так как в карте Карно отсутствуют четыре единичные клет¬

ки, симметричные ранее найденным (1, 5, 9, 13) относительно ка¬

кой-либо оси карты. В найденное покрытие не вошла единичная

клетка с номером 4, которую примем за новое исходное покрытие

0-го ранга. Увеличить ранг этого покрытия можно, присоединяя к

клетке 4 симметричную ей относительно оси Ох0 единичную клетку

с номером 5. Найденное покрытие (4, 5) является максимальным,

так как ранг этого покрытия увеличить нельзя. Таким образом, все

единичные клетки карты Карно для рассматриваемой функции «на¬

крываются» двумя максимальными покрытиями: 2-го ранга (1, 5, 9,

13) и 1-го ранга (4,5). Оба покрытия показаны на рис. 2.8,5. Объе¬

диняя конъюнкции, соответствующие найденным покрытиям зна¬

ком дизъюнкции, запишем МДНФ:

F = XiX0vX3X2Xi,

что полностью совпадает с выражением (2.14).

2.10.3. Минимизация не полностью определенных

логических функций

Не полностью определенной называют такую логическую функ¬

цию п переменных, значения которой определены не на всех 2" на¬

28

борах значений переменных. Неопределенность значения функции

обозначают символом «~», либо «х».

Если функция не определена на к наборах переменных, то су¬

ществует 2К вариантов доопределения, только один из которых при¬

ведет к МДНФ. Не полностью определенная логическая функция

должна быть доопределена таким образом, чтобы все единичные

значения функции накрывались минимальным числом покрытий

возможно более высокого ранга.

Пусть есть некоторая не полностью определенная логическая

функция Fn, заданная с помощью карты Карно (рис. 2.9,а).

Хо Хо

Рис. 2.9. Минимизация не полностью определенной

логической функции

После того как все единичные значения функции накрыты по¬

крытиями, во все остальные клетки проставляют нули.

После доопределения карта Карно примет вид, показанный на

рис. 2.9,6, при этом МДНФ функции:

Fn = Xi X0vXtX0vX3X2.

2.11. Мажоритарные логические схемы

Мажоритарной схемой называют такую логическую схему, зна¬

чение выходного сигнала которой равно большинству значений вход¬

ных сигналов.

Элемент, реализующий мажоритарную функцию, носит назва¬

ние кворум-элемент.

29

Все кворум-элементы имеют нечетное количество входов. На

практике используются схемы с тремя, пятью, реже — с семью вхо¬

дами.

Рассмотрим пример простейшей мажоритарной схемы выборки

2 из 3. Составим таблицу истинности (табл. 2.6).

Таблица 2.6

i

х2

х,

Хв '

0

0

0

0

0

1

0

0

1

0

2

0

1

0

0

3

0

1

1

1

4

1

0

0

0

5

1

0

1

1

6

1

1

0

1

7

1

1

1

1

По табл. 2.6 заполним карту Карно (рис. 2.10).

Как следует из рис. 2.10, единичные значения функции Т2 3 на¬

крываются тремя покрытиями первого ранга:

F2 3=X2X0^XjX0vX2Xr

Отметим, что логические функции,

описывающие мажоритарные схемы, име¬

ют конъюнкции одинаковой длины. Други¬

ми словами, в карте Карно все покрытия

должны быть одного ранга.

Функция мажоритарного элемента обо¬

значается как >п, где п — количество вы-

(2.15)

Рис. 2.11. УГО

микросхемы

К564ЛП13

Х1

Х2

ХЗ

>2

Y1

Х4

Х5

Х6

>2

Y2

Х7

Х8

Х9

>2

Y3

Хо

0

0

т

0

0

(<

7

0

Х2

Рис. 2.10. Карта Карно

для мажоритарной схемы

«2 из 3»

30

борок. В качестве примера приведем УГО микросхемы К564ЛП13

(рис. 2.11), которая содержит три элемента, каждый из которых ре¬

ализует функцию F2 3.

Отметим, что кворум-элементы широко используются для по¬

вышения надежности в системах встроенного контроля резервируе¬

мых рулевых приводных систем.

2.12. Коммутаторы (мультиплексоры и демультиплексоры)

Мультиплексором (рис. 2.12,о) называют устройство коммутации

нескольких источников данных на один приемник.

Демультиплексором (рис. 2.12,6) называют устройство коммута¬

ции одного источника на несколько приемников.

Разрядность управляющего сигнала /’определяется как

nF=\og2N, (2.16)

где N— количество источников (приемников).

В качестве примера рассмотрим четырехразрядный мультиплек¬

сор «2 в 1» (рис. 2.13,а), который реализует систему функций (2.17).

УГО реальной микросхемы К555КП11, реализующей (2.17), приве¬

ден на рис. 2.13,6, где вход SI? (эквивалентен F) управляет выбором

а) б)

Рис. 2.12. Функциональные схемы мультиплексора (а)

и демультиплексора (б)

31

А = <А1А2АЗА4>

В=<В1В2ВЗВ4>

а) б)

Рис. 2.13. Функциональная схема 4-разрядного мультиплексора «2 в 1»

(а) и УГО микросхемы К555КП11 (б)

каналов А или В. Дополнительный вход Е обеспечивает третье со¬

стояние на выходе:

т = А1 FvBl F;

D2 = A2FvB2F;

D3 = A3FvB3F;

D4 = A4FvB4F.

(2.17)

Мультиплексоры и демультиплексоры применяются в арифме-

тическо-логических и микропроцессорных устройствах для увели¬

чения числа источников и приемников в операциях.

2.13. Сумматоры

2.13,1. Общие понятия

Одной из основных операций при выполнении арифметических

действий в цифровых устройствах следящих приводов является сло¬

жение. Наиболее часто используется алгебраическое сложение. На¬

пример, к функционально-необходимым операциям в ЦСП отно-

32

сится формирование кода ошибки (рис. 2.14). На основе суммато¬

ров строятся более сложные арифметическо-логические устройства

и микропроцессоры. На базе сумматоров, кроме сложения и вычи¬

тания, реализуются операции умножения и деления.

а)

Рис. 2.14. Формирование кода ошибки (а) на основе сумматора (б)

Цифровые сумматоры используются во всех цифровых следящих

приводах либо самостоятельно, либо в составе микропроцессоров и

микроконтроллеров. Четвертъсумматором называют функцию СУМ¬

МА ПО МОДУЛЮ 2.

2.13.2. Полусумматор

Рассмотрим принцип сложения двух одноразрядных чисел.

Для одного разряда можно записать:

О

О

1 1

+

+

+

+

О

1

о

1

1 10

В последнем случае при сложении двух одноразрядных чисел

сумма оказалась двухразрядным числом. Если сумму обозначить S,

а перенос обозначить С (в соответствии с правилами двоичного сло¬

жения) и предположить, что суммировались не одноразрядные чис¬

ла, а разряды и «-разрядных чисел, то равный единице стар¬

ший разряд двухразрядной суммы является переносом в следующий

по старшинству разряд. Таким образом, схему суммирования для од¬

ного разряда можно представить в виде

33

Ниже приводится таблица истинности полусумматора (табл. 2.7).

Таблица 2.7

i

X>

Y

G

0

0

0

0

0

1

0

1

о.

1

2

1

0

0

1

3

1

1

1

0

Из табл. 2.7 следует, что:

(2.18)

Таким образом, полусумматор — устройство, реализующее сис¬

тему уравнений (2.18).

2.13.3. Полный одноразрядный сумматор

Общая схема суммирования для любого разряда может быть

записана как

Таким образом, каждый разряд полного одноразрядного сумма¬

тора (ПОС) должен иметь три входа: по одному входу для каждого

из разрядов складываемых чисел и один вход для сигнала переноса,

который может возникнуть в предыдущем разряде (рис. 2.15,я). За¬

пишем таблицу истинности ПОС (табл. 2.8).

Для получения аналитического выражения для воспользуем¬

ся картой Карно (рис. 2.15,6)

St vCi-iY.Xt vC^Xf =

^Ci-iiYiX^Y.XtyvC.^YiXi vFJ,.) =

= Ci-iZ.vCi_1Zi=Ci_I ®Yj ®Xr (2.19)

34

Таблица 2.8

i

с,.,

Y>

X

■ С;

X

0

0

0

0

0

0

1

0

0

1

0

1

2

0

1

0

0

1

3

0

1

1

1

0

4

1

0

0

0 '

1

5

1

0

1

1

0

6

1

1

0

1

0

7

1

1

1

1

1

0

а

0

а

а

0

а

0

в)

Рис. 2.15 Функциональная схема ПОС (а), карта Карно для функци

и Sj (б), схема реализации функции (в)

Таблица истинности для функции переноса Cz полностью совпа¬

дает с таблицей истинности мажоритарной схемы «2 из 3» — F2 3.

Поэтому, учитывая, C/w/~ Х2 , XI , Л>Х0, имеем

Y^C^ Х^-Х, (2.20)

Таким образом, система логических функций (2.19-2.20) опи¬

сывает работу ПОС. Схема реализации для ПОС с учетом того,

35

что и являются функциями СУММА ПО МОДУЛЮ 2 перемен¬

ных (X; и ) и ( и Cz_7) соответственно, показана на рис. 2.15,в.

2.13.4. Полный п-разрядный сумматор

На практике в цифровых устройствах систем приводов приме¬

няют многоразрядные сумматоры. Функциональная схема полного

л-разрядного сумматора показана на рис. 2.16.

Рис. 2.16. Полный л-разрядный сумматор

Рис. 2.17. УГО

К564ИМ1

Если суммирование осуществляется в

дополнительном коде, то на вход С 7 пода¬

ется «О» и разряд Cn_j теряется.

Если суммирование осуществляется в

обратном коде, то перенос из старшего раз¬

ряда Cn_j циклически соединяется с С_г

Суммирование в дополнительном коде

требует в два раза меньше времени, чем в

обратном. В качестве примера на рис. 2.17

приведено УГО четырехразрядного сумма¬

тора со схемой ускоренного переноса

К564ИМ1.

2.14. Шифраторы и дешифраторы

Шифратор (кодер) представляет собой преобразователь код-код.

Как правило, шифраторы преобразуют десятичный код в двоичный

либо в двоично-десятичный. При этом шифратор может иметь до

36

2п входов и п выходов. В любой момент времени в активном состо¬

янии находится только один разряд входного кода.

Таблица истинности (табл. 2.9) иллюстрирует работу двоично¬

десятичного шифратора К555ИВЗ, УГО которого показано на

рис. 2.18 (CD — coder: кодер или шифратор).

Таблица 2.9

19

18

17

16

15

14

13

12

п

А8

А4

А2

А1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1'

0

0

0

1

0

0

0

0

0

0

0

1

0

0

1

0

0

0

0

0

0

0

1

0

0

1

1

0

0

0

0

0

1

0

1

0

0

0

0

0

0

1

0

1

0

1

0

0

0

1

0

1

1

0

0

0

1

0

1

1

1

0

1

1

0

0

0

1

1

0

0

1

Частным случаем шифратора, используемого в преобразовате¬

лях напряжение-код по методу мгновенного кодирования, являют¬

ся приоритетные шифраторы, таблицы истинности которых отли¬

чаются тем, что вместо знака неопределенности (см. табл. 2.9) стоят

логические единицы.

Дешифратором (декодером) называют комбинационную схему,

имеющую п входов и в общем случае до 2" выходов. Выходные фун¬

кции Dj при этом имеют вид:

О0(Х)^Хп-1...ХзХ2‘Х1 Хо\

D1(X) = Xn-i...X3-X2XiX0',

<D2(X) = Xn^...X3X2X1X0;

(2.21)

D2„_,(X) = Xn_I...X3.X2X1-X0.

Дешифратор (ДШ), таким образом, преобразует л-разрядный

Двоичный код в 2л-разрядный код. При этом каждой комбинации

37

Рис. 2.18. УГО шифратора

К555ИВЗ

Рис. 2.19. УГО дешифратора

К155ИД1

переменных на входе ДШ соответствует активный сигнал только на

одном из выходов. Система функций D} (X) является совокупностью

всех возможных минтермов, которые можно образовать от л пере¬

менных. В качестве примера на рис. 2.19 (DC — decoder) показано

УГО двоично-десятичного дешифратора К155ИД1, которому соот¬

ветствует табл. 2.10.

Дешифраторы делятся на полные и неполные. Первые реализу¬

ют полную систему функций (2.21) для п разрядов, вторые — лишь

некоторые из функций Dj (X). Как правило, наиболее часто исполь¬

зуются неполные дешифраторы, к числу которых относится двоич¬

но-десятичный дешифратор.

Таблица 2.10

Входы

Выходы

J4

13

12

11

А9

А8

А7

А6

А5

А4

АЗ

А2

А1

АО

0

0

0

0

0

1

1

1

1

1

1

1

1

1

0

0

0

1

1

0

1

1

1

1

1

1

1

1

0

0

1

0

1

1

0

1

1

1

1

1

1

1

0

0

1

1

1

1

1

0

1

1

1

1

1

1

0

1

0

0

1

1

1

1

0

1

1

1

1

1

0

1

0

1

1

1

1

1

1

0

1

1

1

1

0

1

1

0

1

1

1

1

1

1

0

1

1

1

0

1

1

1

1

1

1

1

1

1

1

0

1

1

1

0

0

0

1

1

1

1

1

1

1

1

0

1

1

0

0

1

1

1

1

1

1

1

1

1

1

0

38

к числу широко использу¬

емых в практике принадлежит

дешифратор семисегментного

индикатора.

Семисегментные индика¬

торы на светодиодах являются

одним из наиболее распростра¬

ненных устройств отображения

десятичных чисел. На рис.

2.20,а показан общий вид од¬

ного индикатора, а на рис.

2.20,6 — все десять цифр, по¬

лучаемые с его помощью. Семь

сегментов индикатора обозна¬

чаются латинскими буквами от

Рис. 2.20. Семисегментный

индикатор

а до g.

Когда ключ замкнут, ток от источника (C/n = +5В) течет через

светодиод, вызывая его свечение. Последовательно включенный ре¬

зистор ограничивает ток до уровня = 20 мА. Без ограничивающего

резистора светодиод может выйти из строя. Обычно работой семи¬

сегментного индикатора управляют не механические, а электронные

ключи. На практике их роль реализуют семисегментные дешифра¬

торы — формирователи (табл. 2.11).

Таблица 2.11

АЗ

А2

А1

АО

Fa

Fb

Fc

Fd

Fe

Ff

Fg

0

0

0

0

1

1

1

1

1

1

0

0

0

0

1

0

1

1

0

0

0

0

0

0

1

0

1

1

0

1

1

0

1

0

0

1

1

1

1

1

1

0

0

1

0

1

0

0

0

1

1

0

0

1

1

0

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

0

1

1

1

1

1

0

1

1

1

1

1

1

0

0

0

0

1

0

0

0

1

1

1

1

1

1

1

1

0

0

1

1

1

1

1

0

1

1

39

2.15. Преобразователи кодов

В следящих приводах, а именно в цифровых датчиках (ЦД) об¬

ратной связи находят применение специальные непозиционные

коды. К числу наиболее часто используемых относятся код Грея и

код Джонсона. Так как ЦД являются подмножеством АЦП (см.

рис. 1.1) и сигнал с их выхода поступает в СМВ, который произво¬

дит вычисления в двоичном арифметическом коде, требуется пре¬

образование кодов.

2.15.1. Код Грея. Синтез преобразователя:

код Грея — двоичный арифметический код

Формирование кода Грея основывается на ряде положений.

1. Код Грея является кодом без избытка. Это означает, что для

кодирования некоторого числа состояний в коде Грея и в двоичном

арифметическом коде требуется одинаковое число разрядов.

2. Код Грея является помехозащищенным кодом. Это означает,

что каждая последующая комбинация отличается от предыдущей

значением только одного разряда.

3. Код Грея является циклическим кодом. Это означает, что пер¬

вая комбинация отличается от последней также значением только

одного разряда.

4. Собственно формирование кода Грея происходит со стороны

правых в сторону левых разрядов, причем введение каждого нового

разряда осуществляется только после того, как израсходованы все

возможные комбинации в предыдущих разрядах.

Рассмотрим задачу преобразования четырехразрядного кода Грея

в двоичный код (табл. 2.12).

При этом приняты следующие обозначения: — разряды кода

Грея (исходного кода); 2? — разряды двоичного арифметического

кода (искомого кода); iG — номер набора логических переменных

для кода Грея; iB — номер набора логических переменных для дво¬

ичного кода.

Табл. 2.12 иллюстрирует соответствие между кодом Грея и дво¬

ичным арифметическим кодом.

Синтез преобразователя кодов будем вести поразрядно с помо¬

щью карт Карно. При этом отметим два положения:

40

Таблица 2.12

Код Грея

Двоичный

арифметический код

G3

G2

G1

Go

*в

в3

в.

В,

Во

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

0

0

1

3

0

0

1

1

2

0

0

1

0

2

0

0

1

0

3

0

0

1

1

6

0

1

1

0

4

0

1

0

0

7

0

1

1

1

5

0

1

0

1

5

0

1

0

1

6

0

1

1

0

4

0

1

0

0

7

0

1

1

1

12

1

1

0

0

8

1

0

0

0

13

1

1

0

1

9

1

0

0

1

15

1

1

1

1

10

1

0

1

0

14

1

1

1

0

11

1

0

1

1

10

1

0

1

0

12

1

1

0

0

11

1

0

1

1

13

1

1

0

1

9

1

0

0

1

14

1

1

1

0

8

1

0

0

0

15

1

1

1

1

1) разрядность исходного кода определяет размерность карт

Карно;

2) разрядность искомого кода определяет число карт Карно.

На рис. 2.21 показаны заполненные в соответствии с табл. 2.12

карты Карно с покрытиями для логических функций: В3 (одно по¬

крытие третьего ранга), В2 (два покрытия второго ранга), В3 (четы¬

ре покрытия первого ранга), Во (восемь покрытий нулевого ранга).

Минимальные дизъюнктивные нормальные формы (МДНФ),

полученные по картам Карно, для В3... Во имеют вид:

В3 = G3, (2.22)

41

Go Вз

0

0

0

0

0

0

0

0

(L

1

1

1

1

1)

G2

Go Bi

0

0

г

"0

0

0

0

0

0

г

"D

0

0

G2

Go B2

G2

Рис. 2.21. Карты Карно для синтеза 4-разрядного преобразователя

код Грея — двоичный арифметический код

B2=G3 G2vG3 G2; (2.23)

В] = G3 G2 Gj v G3 • G2 • Gj v Gj • G2 • Gj v G3 • G2 • Gr, (2.24)

Bq — G3 • G2 -G] -Gq v G3 G2 • Gj • Go v G3 • G2 -Gj GqV

vG3 • Gj Gl • Go V Gj • G2 • Gj ’ Gq V Gj • G2 • Gi • Go V

V Gj • Gj • Gl • Gq V Gj ' Gj ' Gj • Go •

Подставим в (2.23) вместо G3 в соответствии с (2.22) В3, тогда:

В2=В3 G2vB3 G2 (2.26)

Преобразуем (2.24), используя свойства дистрибутивности и

ассоциативности логических функций и учитывая (2.22). Тогда

Bj = (В3 G2 vBj • G2) • Gi v(В3 G2 v В3 ♦ G2) Gj.

42

Учитывая (2.26) и то, что

В г = Вз G2 v Bj G2,

окончательно получим:

Bj=B2Gi vB2 Gr (2.27)

Преобразуем (2.25) с помощью свойства дистрибутивности и

ассоциативности логических функций:

Во = (вз G2^G3 G2) Gj Go v(G3 -G2vG3-G2)-Gj Go v

v((r3 '&2V &3 ' G2V G3 G1 ' G0-

С учетом (2.23) и (2.26) получим:

Bq = В 2 Gj Go^ B2 G^ Go v B2 - Gj Gq v B2 ■ Gi • Go.

Используя далее свойство дистрибутивности, учитывая (2.27) и

то, что

Bl - B2G1 V В2 Gj,

запишем:

Bq— BjGo v Bi Gq. (2.28)

Анализируя выражения (2.26), (2.27) и (2.28), можно сделать

вывод о том, что общая формула для /-го разряда преобразователя

код Грея — двоичный арифметический код имеет вид:

B^B.^GivBi+i-G.. (2.29)

Формула (2.29) верна и для старшего разряда, так как в этом

случае Bi+{ = 0 (то есть физически этот разряд отсутствует), тогда

(2.29) переходит в

5,. = Gp

что соответствует (2.22).

43

На рис. 2.22,а приведена принципиальная схема четырехразряд¬

ного преобразователя код Грея — двоичный арифметический код,

а на рис. 2.22,6 — УГО.

Рис. 2.22. Принципиальная схема (а) и УГО (б) 4-разрядного

преобразователя код Грея — двоичный арифметический код

G/B

G3

ВЗ

G2

В2

G1

В1

GO

ВО

Как следует из рис. 2.22 и выражения (2.29), преобразователь

код Грея — двоичный арифметический код имеет регулярную струк¬

туру и каждый дополнительный разряд добавляет всего один эле¬

мент СУММА ПО МОДУЛЮ 2 в схему преобразователя.

2.15.2. Код Джонсона. Синтез преобразователя:

код Джонсона — двоичный арифметический код

Формирование кода Джонсона основывается на ряде положений.

1. Код Джонсона является кодом с избытком. Это означает, что

для кодирования некоторого числа состояний в коде Джонсона тре¬

буется большее число разрядов (для числа разрядов больше 2), чем

в двоичном арифметическом коде. Число состояний = 2п^, где

«Дж — число разрядов в коде Джонсона.

2. Код Джонсона является помехозащищенным кодом. Это озна¬

чает, что каждая последующая комбинация отличается от предыду¬

щей значением только одного разряда.

3. Код Джонсона является циклическим кодом. Это означает, что

первая комбинация отличается от последней также значением толь¬

ко одного разряда.

44

4. Собственно формирование кода Джонсона происходит со сто¬

роны правых в сторону левых разрядов, причем введение каждого

нового разряда осуществляется до тех пор, пока все разряды не бу¬

дут заполнены единицами. После этого происходит в том же поряд¬

ке последовательное заполнение нулями до момента, когда в край¬

нем левом разряде находится единица, а в остальных — нули.

Рассмотрим задачу преобразования четырехразрядного кода

Джонсона в двоичный код (табл. 2.13).

При этом приняты следующие обозначения: Jf — разряды кода

Джонсона (исходного кода); Д, — разряды двоичного арифметичес¬

кого кода (искомого кода); ij — номер набора логических перемен¬

ных для кода Джонсона; iB — номер набора логических переменных

для арифметического кода.

Табл. 2.13 иллюстрирует соответствие между кодом Джонсона и

двоичным арифметическим кодом.

Как следует из табл. 2.13, код Джонсона, в отличие от кода Грея,

является кодом с избытком, т.е. для кодирования восьми состояний

необходимо четыре разряда, в то время, как при использовании

двоичного арифметического кода, как и кода Грея, — только три.

Синтез преобразователя кодов будем вести поразрядно с помо¬

щью карт Карно.

На рис. 2.23 показаны заполненные в соответствии с табл. 2.13

карты Карно с покрытиями для логических функций В2 (одно по-

Таблица 2.13

Код Джонсона

Двоичный

арифметический код

h

Л

//

Л

в2

в.

Во

0

0

0

0

0

0

0

0

0

1

0

0

0

1

1

0

0

1

3

0

0

1

1

2

0

1

0

7

0

1

1

1

3

0

1

1

15

1

1

1

1

4

1

0

0

14

1

1

1

0

5

1

0

1

12

1

1

0

0

6

1

1

0

8

1

0

0

0

7

1

1

1

45

0

0

-

-

-

0

0

1

к

-

-

0

0

*

(г

1

1

э

-

-

0

0

0

-

!)

Рис. 2.23. Карты Карно для синтеза 4-разрядного преобразователя

код Джонсона — двоичный арифметический код

крытие третьего ранга), В3 (два покрытия второго ранга), Во (четы¬

ре покрытия второго ранга).

Минимальные дизъюнктивные нормальные формы (МДНФ),

полученные по картам Карно, для В2...В0 имеют вид:

B2^J3, (2.30)

Bj=J3 Jiv73 Jj, (2.31)

Bo =JjJovJiJgvJ3J2 vJ3 J2 (2.32)

На рис. 2.24,а приведена принципиальная схема преобразова¬

теля 4-разрядного кода Джонсона в трехразрядный двоичный ариф¬

метический код, а на рис. 2.24,6 — УГО.

Рис. 2.24. Принципиальная схема (а) и УГО (б) 4-разрядного

преобразователя кода Джонсона в двоичный арифметический код

J3

J2

Л

JO

J/B

В2

В1

ВО

46

2.16. Схемы сравнения кодов (цифровые компараторы)

Цифровые компараторы предназначены для сравнения двух

двоичных чисел. Табл. 2.14 иллюстрирует связь между входами и

выходами компаратора при сравнении двух одноразрядных чисел а

и Ь, которые могут принимать значения 0 либо 1.

В качестве примера приведем схему сравнения двух 4-разряд-

ных чисел К555СП1 (рис. 2.25,а). Результатом сравнения является

обнаружение одного из трех возможных состояний: А < В, А = В,

А > В. Критерием равенства двух двоичных чисел является совпаде¬

ние их по всем разрядам. Выход схемы сравнения устанавливается

в высокое состояние, если два числа равны; в противном случае вы-

Таблица 2.14

Входы

Выходы

а

ь

Ра>ь

Fa=b

р

га<Ь

0

0

0

1

0

0

1

0

0

1

1

0

1

0

0

1

1

0

1

0

а) б)

Рис. 2.25. УГО (а) и схема реализации части (б) 4-разрядного

цифрового компаратора

47

ход находится в низком состоянии (рис. 2.25,6). Микросхема имеет

четыре сравниваемых входа чисел А=<А0,А 1 ,И2,ЛЗ > и

5=<50,51,52,53> и три дополнительных входа переноса А<В, А=В,

А>Вдля сравнения чисел большей разрядности путем последователь¬

ного соединения компараторов в каскад.

Схемы сравнения кодов используются в составе преобразовате¬

лей код-широтно-импульсный сигнал, применяемых в современных

ЦСП.

2.17. Буферные (промежуточные) логические схемы

Буферные (промежуточные) логические схемы используются в

сложных цифровых устройствах, где требуется согласование элект¬

рических параметров.

Существует два типа буферных схем:

1 — схемы с открытым коллектором,

2 — схемы с тремя состояниями.

2.17.1. Схемы с открытым коллектором

Если объединить выходы двух стандартных логических схем

(рис. 2.26,а), то всегда может возникнуть ситуация, когда на выходе

одной из логических схем формируется логическая единица, а на вы¬

ходе другой — логический нуль. В этом случае возникает электри-

а) б)

Рис. 2.26. Стандартные ИС (я) и ИС с открытым коллектором (6)

48

ческая цепь, которая приводит к избыточному току и выходу схемы

из строя.

Этого недостатка лишены схемы с открытым коллектором (ОК),

которые могут реализовать «монтажное ИЛИ» (рис. 2.26,6). Схемы

с ОК обеспечивают возможность регулирования выходного тока

благодаря выбору номиналов источников питания и номиналов со¬

гласующих резисторов.

2.17.2. Схемы с тремя состояниями

Выход таких схем имеет три различных состояния. Для управ¬

ления третьим состоянием имеется специальный вывод (ОЕ — Output

Enable). Когда на управляющий вход подан высокий потенциал,

логика работы схемы не отличается от обычной (например, TTL-

схемы). Третье состояние — Zхарактеризуется очень высоким вы¬

ходным сопротивлением и имеет место при подаче на управляющий

вход низкого потенциала. Перевод в третье состояние обеспечивает

логическое отключение выхода схемы от нагрузки.

Приведем таблицу истинности (табл. 2.15) тристабильного ин¬

вертора (рис. 2.27).

Схемы с тремя состояниями применяются в качестве интерфей¬

сных буферных схем (шинные формирователи).

Таблица 2.15

X (вход)

ОЕ

Y (выход)

0

0

Z

1

0

Z

0

1

1

1

1

0

Рис. 2.27. Инвертор

с тремя состояниями

3. ПОСЛЕДОВАТЕЛЬНОСТНЫЕ

ЛОГИЧЕСКИЕ СХЕМЫ

Последовательностной логической схемой называют такую схе¬

му, выходное значение которой зависит не только от комбинации

входных сигналов, но и от последовательности входных и выход¬

ных сигналов в предыдущие моменты времени. Поэтому говорят,

нто последовательностные схемы обладают памятью.

49

В основе всех последовательностных схем лежит устройство,

которое носит название триггер.

На базе триггеров строятся более сложные устройства — гене¬

раторы импульсов, регистры, счетчики.

3.1. Триггеры

Триггером называют устройство с двумя устойчивыми взаимо-

инверсными состояниями, которые устанавливаются при подаче на

вход управляющих сигналов и могут хранить это состояние в тече¬

ние бесконечно долгого времени после снятия этих сигналов.

Информационные

сигналы

ТТ

Q

75

Тактовый

сигнал

Рис. 3.1. УГО обобщенного

триггера, тактируемого по

переднему фронту

На рис. 3.1 показано условное

обозначение триггера. Триггер име¬

ет прямой — Q и инверсный — Q

выходы. Как правило, триггер имеет

один (или несколько) информаци¬

онный вход и может иметь синхро¬

низирующий (тактовый) вход. В за¬

висимости от того, используется

синхронизирующий сигнал или нет,

триггеры делятся на синхронные

(тактируемые) и асинхронные.

Говорят, что триггер установлен, если выполнено условие:

<2=ке=о).

При этом Q = О (Q = 1) — состояние сброса.

В практике наибольшее применение нашли следующие тригге¬

ры: R-S, D, J-K, Т

В основе всех типов триггеров лежит один и тот же базовый эле¬

мент — бистабильная ячейка (БЯ) или R-S -триггер.

3.1.1. Бистабильная ячейка

Рассмотрим принцип действия бистабильной ячейки, постро¬

енной, например, на основе элементов НЕ-И (рис. 3.2,л). Как сле¬

дует из рис. 3.2,я, БЯ представляет собой два элемента НЕ-И, объе-

50

Рис. 3.2. Бистабильная ячейка, построенная

г—

—>

0

0

0

0

б)

на двух элементах 2-И-НЕ (а) и соответствующая карта Карно (б)

диненные перекрестными положительными обратными связями.

Таблица истинности БЯ дана ниже (табл. 3.1).

Обратим внимание на два положения, которые важны при опи¬

сании работы последовательностных схем.

1. Перед началом объяснения принципа действия необходимо

задаться исходным состоянием схемы.

2. Описание работы следует начинать с входных сигналов, име¬

ющих уровень логического нуля.

Запрещенное состояние БЯ следует трактовать таким образом,

что при одновременной подаче на входы DD1.1 и DD1.2 (рис. 3.2,а)

сигналов логического нуля на выходах Q и Q устанавливается со-

Таблица 3.1

i

S"

R"

Q"

Qn+I

0

0

0

0

~(D

1

0

0

1

~(1)

2

0

1

0

1

3

0

1

1

1

4

1

0

0

0

5

1

0

1

0

6

1

1

0

0

7

1

1

1

1

51

стояние Q = Q. Это противоречит определению триггера как устрой¬

ства с двумя взаимно инверсными выходами.

Найдем уравнение, связывающее текущее состояние БЯ — Qn+l

с управляющими сигналами S", Rn и предыдущим состоянием Qn

Qn^ = f(Sn,Rn,Qn)

с помощью карты Карно (рис. 3.2,6), заполненной по табл. 3.1.

Как следует из рис. 3.2,6, уравнение БЯ имеет вид:

Qa+I =Sa vRttQa. (3.1)

Часто при описании триггерных устройств используют не пол¬

ные, а сокращенные таблицы. В этом случае из числа переменных

исключается Q" , что возможно исходя из анализа полных таблиц.

Действительно, как следует из табл. 3.1 для Qn+i строки: нуле¬

вая и первая, вторая и третья, четвертая и пятая, попарно дают один

и тот же результат. Шестая и седьмая строки повторяют значения

для Qn . Таким образом, сокращенная таблица для БЯ примет сле¬

дующий вид (табл. 3.2):

Таблица 3.2

i

s"

R"

Q"+/

0

0

0

~(D

1

0

1

1

2

1

0

0

3

1

1

Q"

Карта Карно для БЯ, заполненная по табл. 3.2, показана на

рис. 3.3.

В том случае, если в карте Карно наряду с единицами, нулями

и неопределенностями в некоторых клетках стоят логические пере¬

менные, процедура отыскания МДНФ состоит из двух этапов:

52

(-

0

.о]

Рис, 3.3. Карта

Карно для БЯ

1) покрытие всех единичных значений функ¬

ции (единичных клеток);

2) покрытие всех значений функции, равных

логическим переменным (клеток с логическими пе¬

ременными).

В обоих случаях необходимо, чтобы покрытия

были максимально возможного ранга, а их число

— минимальным. При этом для увеличения ранга

покрытия к единичной клетке не может быть присоединена клетка

с логической переменной, т.к. переменная может принимать значе¬

ния не только логической единицы, но и логического нуля.

Поскольку при отыскании МДНФ накрывают не только единич¬

ные клетки, но и клетки, в которых расположены логические пере¬

менные, для увеличения ранга покрытия к клетке с логической пе¬

ременной может быть присоединена как единичная клетка, так и

клетка с неопределенностью. Уравнение БЯ, полученное по карте

Карно (рис. 3.3), совпадает с уравнением (3.1).

Для определения минимального времени подачи входных сиг¬

налов следует учитывать задержку на один логический элемент

2-И-НЕ т = тах(т301,т31 °). Полное минимальное время для БЯ со¬

ставит 3 т.

Кроме таблиц состояний, карт Карно и уравнений для описа¬

ния последовательностных схем, и триггерных — в частности, ис¬

пользуют временные диаграммы. Эти диаграммы показывают уров¬

ни напряжений и временные интервалы между входными и выход¬

ными сигналами. По оси абсцисс откладывают время, по оси орди¬

нат — уровень напряжения или уровень логического сигнала.

Временные диаграммы позволяют показать все состояния ло¬