Author: Богданович М.И

Tags: электротехника микрорадиоэлектронная аппаратура микроэлектроника электроника

ISBN: 5-338-00501-8

Year: 1991

Text

ББК 32.844.1я2

Ц 75

УДК 621.382.049.77 (035.5)

Авторы: М. И. БОГДАНОВИЧ, И. Н. ГРЕЛЬ, В. А. ПРОХОРЕНКО,

В. В. ШЛЛИМО

Рецензент канд. техн. наук Н. И. ОВСЯННИКОВ

i

2302030700 — 138

Ц 68—90

М 301(03)—91

ISBN 5-338-00501-8

© Авторский коллектив, 1991

ПРЕДИСЛОВИЕ

Современный этап развития научно-технического прогресса

характеризуется широким применением электроники и

микроэлектроники во всех сферах жизни и деятельности человека.

Важную роль при этом сыграло появление и быстрое

совершенствование интегральных микросхем — основной элементной

базы современной электроники. Цифровые интегральные

микросхемы применяются в вычислительных машинах и

комплексах, в электронных устройствах автоматики, цифровых

измерительных приборах, аппаратуре связи и передачи данных,

медицинской и бытовой аппаратуре, в приборах и

оборудовании для научных исследований и т. д.

В настоящее время сведения о цифровых интегральных

схемах необходимы не только специалистам по

радиоэлектронике, но и радиолюбителям.

Цель настоящего справочника — ознакомить широкий круг

специалистов, студентов и радиолюбителей с основами

построения цифровых интегральных схем и с наиболее

распространенными их сериями малого и среднего уровня интеграции.

Книга будет полезна начинающим и опытным

радиолюбителям, студентам и молодым специалистам, а также

специалистам других отраслей народного хозяйства, у которых

возникает необходимость изучения нового оборудования и

аппаратуры, содержащих электронные узлы и блоки.

В первой главе справочника приведены общие сведения

о цифровых интегральных схемах и конструктивных

особенностях Во второй — интегральные схемы

транзисторно-транзисторной логики. В третьей описаны наиболее

распространенные цифровые интегральные схемы на основе КМДП-тран-

зисторов. Четвертая глава познакомит читателей с самыми

быстродействующими микросхемами на основе эмиттерно-свя-

занной логики.

Приведены основные параметры рассматриваемых

интегральных схем, которые сведены в таблицы по разделам. Для

более полного понимания работы микросхем среднего уровня

интеграции во многих случаях приводятся их структурные

схемы, а также принципиальные схемы основных элементов

3

ГЛАВА 1. Общие сведения

о цифровых микросхемах

1.1. Классификация и система

условных обозначений цифровых микросхем

Цифровые микросхемы предназначены для преобразования

и обработки сигналов, изменяющихся по законам дискретной

функции. Они применяются для построения ЦВМ, а также

цифровых узлов измерительных приборов, аппаратуры

автоматического управления, связи и т. д.

По конструктивно-технологическому исполнению все

цифровые ИС делятся на группы. По характеру выполняемых

функций в аппаратуре ИС подразделяются на подгруппы

(например, логические элементы, триггеры и т. д.) и виды

внутри подгрупп (например, триггеры с задержкой, триггеры

универсальные и т. д.). Разделение цифровых ИС на

подгруппы и виды по функциональному назначению приведены в

табл. 1.1.

Таблица 1.1.

Цифровые интегральные микросхемы

Подгруппа и вид ИС

I

Обозначение

2

Формирователи:

импульсов тока АА

импульсов прямоугольной формы АГ

импульсов специальной формы АФ

прочие АП

Схемы задержки БР

Схемы вычислительных средств:

сопряжение с магистралью ВА

синхронизации ВБ

управления вводом-выводом (схемы интерфейса) ВВ

контроллеры ВГ

микроЭВМ BE

специализированные ВЖ

времязадающие ВИ

комбинированные ВК

микропроцессоры ВМ

управление прерыванием ВН

прочие ВП

функциональные расширители (в том числе

расширители разрядных данных) ВР

микропроцессорные секции ВС

схемы управления памятью ВТ

схемы микропрограммного управления ВУ

функциональные преобразователи информации ВФ

4

Продолжение табл. 1.1

(арифметические, тригонометрические,

логарифмические, быстрого преобразования Фурье и др.)

Генераторы:

прямоугольных сигналов

сигналов специальной формы

Схемы арифметических и дискретных устройств:

арифметическо-логические устройства

шифраторы

дешифраторы

счетчики

комбинированные

полусумматоры

сумматоры

прочие

регистры

Коммутаторы и ключи:

напряжения

тока

прочие

Логические элементы:

И-НЕ

И-НЕ/ИЛИ-НЕ

расширители

ИЛИ-НЕ

И

И-ИЛИ-НЕ/И-ИЛИ

ИЛИ

ИЛИ-НЕ/ИЛИ

НЕ

прочие

И-ИЛИ-НЕ

И-ИЛИ

Преобразователи сигналов:

двоичного кода в семисегментиый код

уровня (согласователи)

код — код

Схемы запоминающих устройств (ЗУ):

ассоциативные ЗУ

матрицы постоянных ЗУ

постоянные ЗУ (масочные)

матрицы оперативных ЗУ

прочие

постоянные ЗУ с возможностью многократного

электрического перепрограммирования

оперативные ЗУ

постоянные ЗУ с ультрафиолетовым стиранием и

электрической записью информации

Схемы сравнения

Триггеры:

универсальные (типа J К)

ГГ

ГФ

ИА

ИВ

ид

ИЕ

ик

ИЛ

им

ип

ИР

кн

кт

кп

ЛА

Л Б

лд

ЛЕ

ЛИ

ЛК

ЛЛ

лм

лн

лп

ЛР

лс

пп

ПУ

ПР

РА

РВ

РЕ

РМ

РП

PT

РУ

РФ

СА

СП

ск

ТВ

Продолжение табл. 1.1

динамические ТД

комбинированные ТК.

Шмитта ТЛ

с задержкой (типа D) ТМ

прочие ТП

с раздельным запуском (типа RS) ТР

счетные (типа Т) ТТ

Усилители yj]

Многофункциональные схемы

цифровые ХЛ

комбинированные ХК.

цифровые матрицы ХМ

прочие ХП

Сведения о подгруппе и виде микросхемы содержатся в ее

условном обозначении.

В соответствии с ГОСТ 17021—75 обозначение цифровых

ИС должно состоять из четырех элементов. Первый из них —

цифра (1, 5, 7), обозначающая группу ИС. Она определяется

конструктивно-технологическим исполнением ИС. Второй

элемент—две или три цифры (от 00 до 99 либо от 000 до 999),

указывающие порядковый номер разработки серии ИС.

Третий элемент — две буквы, обозначающие подгруппу и вид

микросхемы, определяющие основные функциональные

назначения ИС (табл. 1.1). Четвертый элемент — число,

обозначающее порядковый помер разработки ИС по функциональному

признаку в данной серии.

Два первых элемента обозначают серию ИС. Под серией

понимают совокупность типов ИС, которые могут выполнять

различные функции, имеют единое

конструктивно-технологическое исполнение и предназначены для совместного приме

нения.

Пример условного обозначения интегральной

полупроводниковой логической микросхемы И-НЕ с порядковым номером

разработки серии — 1533, порядковым номером разработки

данной схемы в серии по функциональному признаку — 3

приведен ниже.

При необходимости разработчик ИС имеет право после

порядкового номера разработки ИС по функциональному

признаку в данной серии дополнительно поместить букву

(от А до Я), обозначающую отличие электрических

параметров ИС одного типа (например, 531ЛА1П). Конечная буква

при маркировке может быть заменена точкой. Цвет ее

указывается в технических условиях (ТУ) на ИС конкретных типов.

Для микросхем, используемых в устройствах широкого

применения, в начале обозначения добавляется буква К (на

Серия

1

533 Л А Л

Порядковый номер разработки И С в

данной серии па азункциопалбному

признана

Вид (по функциональному назначению)

Подгруппа

Порядковый номер разработки серии

Группа (по конструктивно-технологическому исполнению)

Условное обозначение микросхемы 1533ЛАЗ

пример, К1533ЛАЗ). Как правило, ИС с буквой К отличаются

от микросхем, не имеющих ее, условиями приемки на

заводе-изготовителе, т. е. отличаются не только диапазоном температур,

при которых они могут быть использованы, но и численными

значениями некоторых параметров.

В последнее время для некоторых ИС после буквы К

ставится дополнительная буква, указывающая особенность

конструктивного исполнения (например, КР, КМ, КФ).

Для бескорпусных ИС перед цифровым обозначением

серии добавляют букву Б, а после обозначения порядкового

номера разработки ИС по функциональному признаку в

данной серии (или после дополнительного буквенного

обозначения) через дефис указывают цифру, характеризующую

модификацию конструктивного исполнения (например, Б133ЛАЗ-1).

В табл. 1.2 приведены обозначения конструктивного

исполнения для различных модификаций бескорпусных ИС.

Таблица 1.2. Модификация конструктивного исполнения

бескорпусных интегральных микросхем

Характерна ика конструктивного исполнения микросхем

(модификация)

Обозначение

конструктивного

исполнения

С гибкими выводами

С ленточными (паучковыми) выводами

С жесткими выводами

На общей пластине (нераздельные)

Раздельные без потери ориентировки

С контактными площадками без выводов (кристалл)

Основные серии, тип логики, шифр 'корпуса и номер его

рисунка, а также назначение цифровых ИС приведены в табл 1.3.

1.2. Корпуса цифровым

интегральных микросхем

Для защиты ИС от внешних воздействий их помещают

в стандартизированные герметизированные корпуса. В

соответствии с ГОСТ 17467—79 «Микросхемы интегральные.

Основные размеры» они делятся на пять типов, отличающихся

по форме и расположению выводов.

Таблица 1.3. Основные серии, тип логики,

шифр и рисунок чертежа корпуса,

назначение цифровых интегральных микросхем

Серия

1

Тип

логики

2

Шифр корпуса

3

Рисунок

чертежа

корпуса

4

Назначение серии

микросхем

-

133 ТТЛ

HI 33 ТТЛ

КМ 133 ТТЛ

134 ТТЛ

401.14-1 (ТЛ2, ТЛЗ)

401.14-4

401.14-5 (ЛАП, ЛНЗ

ЛН5, ЛП8, ЛП9)

402.16-16 (ИД1, ИД4,

ИМЗ, ИМ4, КП2, КП7,

ЛА12, ЛЕ5, ЛЕ6, ПП4,

ТМ7, ИП4)

402.16-21 (АГЗ, ИДЮ,

ТВ15)

402.16-25 (ИВ1)

402.16-32 (ИЕ5, ИЕ8)

402.16-33 (ИД15,

ИД16)

405.24-1 (ИДЗ, ИР13)

405.24-2 (ИПЗ, ИР17,

КП1)

Н02.14-2В

Н04.16-2В (АГЗ, ИМЗ)

Н02.14-1В (ЛЕ1, ЛИ1,

ЛЛ1, ЛН1)

Н06.24-2В (ИР13)

4105.14-1 (КП5, ЛА1

ЛА4, ЛА6 ЛА8, ЛА15,

ЛД1, ЛДЗ, ЛП5, ЛР1,

ЛРЗ, ЛР4)

4105.14-02 (TBI,

4106.16-3 (ИД1,

4114.24-1 (ИДЗ)

401.14-3 (ЛА2,

ЛБ1, ЛБ2, ЛПЗ

ЛР2, ЛР4, TBI,

ТМ2, ХЛ2, ХЛЗ)

401.14-4 (ИЕ2,

П. 17 Предназначена

П. 17 для построения уз-

П. 19 лов ЦВМ и

устройств дискретной

П. 20 автоматики

П. 24

П.

п.

п.

п.

п.

24

24

24

25

25

П. 36

П. 27

ТМ2)

КП7)

ЛА8,

ЛР1,

ТВ14,

ИЕ5,

П.

П.

П.

П.

П.

27

28

30

18

17

Для построения

узлов ЦВМ и

устройств автоматики

малой

потребляемой мощности

Продолжение таб.1. 1.Я

ИМ5, ИП2, ИР1, ИР2,

ИР8, КП8...КП10, ЛБ1,

ЛБ2, ЛР1, ЛР2)

402.16-6 (ИД6, ИМ4, П. 20

ИП4)

402.16-11 (ИР5, СП1) П. 22

405.24-2 (ИДЗ, ИПЗ) П. 25

К134 ТТЛ 401.14-3 (ЛБ1, ЛБ2, П. 18

ЛР1, ЛР2, TBI, TB14)

401.14-4 (ИЕ5, ИР1, П. 17

КП8...КП10, ИР2)

402.16-6 (ИД6, ИМ4, П. 20

ИП4)

405.24-2 (ИПЗ) П. 25

КР134 ТТЛ 201.14-1 (ИП2, ЛА2, П. 1

ЛА8, ЛПЗ, ЛР4, ТМ2,

ХЛ2)

201.14-2 (ИЕ2, ИМ5, П. 1

ИР8)

238.16-2 (ИР5, СП1) П. 8

239.24-2 (ИДЗ) П. 9

155 ТТЛ 201.14-1 П. 1 То же, что и серия

201.14-2 (ИМ1, ТЛ2, П. 1 133

ТЛЗ)

238.16-1 (АГЗ, ИП4, П. 8

КП2, КП7, ИД1, ИД4,

ИДЮ, ТМ8)

238.16-2 (ИЕ6...ИЕ9, П. 8

ИМЗ, ПР6, ПР7, ТМ7,

ИВ1, ЛН6, ЛП10,

ЛПП)

239.24-1 (КП1) П. 9

239.24-2 (ИДЗ, ИПЗ, П. 9

ИР13, ИР17)

2101.8-1 (ЛИ5) П. 10

К155 ТТЛ 201.14-1 П. 1

201.14-2 (ЛА12, ЛА13, П. 1

ЛИ5, ЛП7, ТЛ2, ТЛЗ,

ЛЕ5, ЛЕ6, ЛНЗ, ЛН5,

ЛП8)

238.16-1 (АГЗ, ИД1, П. 8

ИД4, ИДЮ, ИП4, КП2,

ИД15, КП7, ТМ8, ЛЕ2,

ТВ15)

238.16-2 (ИЕ6...ИЕ9, П. 8

ИМЗ, ПР6, ПР7, ТМ7,

ИД11...ИД13, ИР15,

лнб, лрю; лпп,

ИР32)

239.24-1 (КП1) П. 9

239.24-2 (РПЗ, ИДЗ, П. 9

ИПЗ, ИР13, ИР17)

9

Продолжение табл. 1.3

К155

ТТЛ

169

ТТЛ

170

ТТЛ

КМ 170 ТТЛ

199 ТТЛ

КР508 ТТЛ

514 ТТЛ

КМ559

Р559

10

ТТЛ

ТТЛ

УЛ1

238.16-1

402.16-7 (ИР2)

402.16-33 (ИД4)

П. 10

П. 2

П. 2

П. 4

2101.8-1 (ЛА18, ЛЛ2)

201.14-8

201.14-9

201.16-5 (АГЗ, ИДИ..

ИД13, ИР15, КП2)

201.16-6 (ИД1, ИД4

ИЕ6...ИЕ8, КП7, ПР6

ПР7, ТМ7, ТМ8)

209.24-1 (ИД8, ИД9)

401.14-4 (АП1, УП1)

402.16-6 (УЛ1, УЛ2

УЛ4...УЛ7)

402.16-7 (АА1...АА4, П. 21

АА6, АП2, УП2, ХК1)

402.16-32 (УЛ8)

4112.16-3 (АА7)

201.14-1 (АП1

УЛ2, УЛ4, УП1)

201.14-2 (АА1...АА4

АА6)

238.16-2 (АП4)

2101.8-1 (АП2, АПЗ)

2106.16-1 (АА7)

201.14-9

401.14-4

П. 4

П. 7

П. 17 Предназначены

П. 20 для управления ЗУ

П.

п.

п.

п.

п.

п.

п.

п.

п.

24

29

1

1

8

10

12

2

17

П. 8

549

К549

559

КР559

М559

ТТЛ

ТТЛ

ТТЛ

ТТЛ

ТТЛ

401.14-3

402.16-18

238.16-2

2140Ю.20-2 (ВТ1, ИП8)

2104.18-1 (ВН1)

201.16-13 ИП1...ИПЗ)

П.

11.

П.

П.

П.

П.

18

23

8

16

11

6

2140Ю.20-2 (ВТ1, ИП8) П.

2104.18-1 (ВН1) П.

238.16-2 П.

Для построения

узлов ЦВМ и

устройств дискретной

автоматики

Для применения в

ОЗУ РЭА

Для применения в

устройствах

отображения

цифровой, знаковой и

буквенной

информации РЭА

Для управления

ЗУ

Для обмена

информацией между

устройствами и

блоками систем и

для передачи

данных на

периферийные устройства,

устройства

отображения и

индикации

Продолжение табл. 1.3

К599

1102

К1102

К1 119

ТТЛ

ТТЛ

ТТЛ

ТТЛ

530

ТТЛШ

КМ530 ТТЛШ

М530 ТТЛШ

Н530 ТТЛШ

К531 ТТЛШ

201.14-1

4112.16-3

201.14-2 (АП5, АП10)

238.16-2 (АП1...АПЗ)

2101.8-1 (АП4, АП6.

АП9, АП11...АП14)

402.16-34

401.14-5 (ИЕН, ИЕ15,

ЛА13, ЛИЗ, ИП5, ЛА1..

ЛА4, ЛА16, ЛА17 ЛА9,

ЛЕ1, ЛЛ1, ЛН1, ЛН2,

ЛП5, ЛР9, ЛР11, ТВ 10,

ТВ11, ТВ 10, TBU, ТМ2,

ТЛЗ)

402.16-25 (АП2, ГП,

ИД7, ИД14, ИЕ16,

ИЕ17, ИР11, ИР12,

КПП, КП14, КП15,

КП2, КП4, КП7, СП1,

ТВ9, ТМ8, ТМ9)

4118.24-3 (АПЗ, АП4,

ИР24, ИПЗ)

4552Ю.20-1 (ИР22,

ИР23)

201.14.10 (ЛА12)

201.14-10 (ЛА2...ЛА4,

ЛА12, ЛН1 ЛН2, ЛП5,

ЛР9, ТМ2, ЛР5, ЛИ1)

201.16-13 (ИР18...

ИР21, КПП, ТВ9)

2120.24-1 (ИК1)

Н02.14-2В (ЛАЗ, ЛА9,

ЛЕ1, ЛН1, ЛН2, ТВЮ,

ТМ2)

Н04.16-2В (ИД7, ИД14,

ТМ8, ТМ9)

201.14-1 (ЛА1 ЛА4,

ЛА7, ЛА9, ЛА13, ЛА17,

ЛЕ1, ЛЕ7, ЛИЗ, ЛЛ1,

ЛН1, ЛН2, ЛП5, ЛР9...

ЛР11.ТВ10, ТВ11, ТЛЗ,

ТМ2)

201 14-13 (ИЕН, ИЕ15,

П. 1 Для построения

узлов ЦВМ и

устройств дискретной

автоматики

П. 29 для работы в ка-

П. I честве быстродей-

П. 8 ствующих логиче-

П. 10 ских схем

управления в РЭА

П. 24 Для

преобразования уровня ИС

ТТЛ в уровни,

требуемые для

управления ИС с

зарядовой связью в

РЭА

П. 19 Для работы в

РЭА, в ЭВМ и

устройствах

автоматики

повышенной производи

тельности

П. 24

П. 31

П. 35

П. 3

П. 6

П. 13

П. 36

П. 36

П. 1 То же, что и се

рия 530

П 1

11

Продолжение табл. 1.3

ИП5, ЛА12, ЛА16,

ЛИ1)

201.16-12 (КП15, ЛА19,

ТВ9, ТМ8)

201.16-16 (АП2, ГГ1,

ИД7, ИД14, ИЕ16,

ИЕ17, ИП4, ИР11,

ИР12, ИР18...ИР21,

КПП, КП14, КП2, КП7,

СП1, ТМ9, ХЛ1)

239.24.7 (ИК1, ИК2,

ИПЗ)

2140Ю.20-1 (АПЗ, АП4,

ИР22...ИР24, ВГ1)

КМ531 ТТЛШ 201.14-9 (ЛА12, ЛИ1)

201.16-5 (ИР18...ИР21)

КР531 ТТЛШ 201.14-13 (ЛА12, ЛИ1)

201.16-12 (КП16, КП18)

238.16-2 (ИР18...ИР21)

201.16-16 (КП12, ИЕ10)

533 ТТЛШ 401.14-4 (ИМ5, ИП6,

ИП7, ЛА1...ЛАЗ, ЛА7,

ЛА9, ЛА12, ЛЕ1, ЛЕ4,

ЛИ1, ЛИЗ, ЛИ6, ЛЛ1,

ЛН1, ЛН2, ЛР4, ЛР11,

ЛР13, ТЛ2, ТМ2, ХЛ1)

401.14-5 (ИЕ5, ИП5,

ИР8, ИР16, ЛАЮ,

ЛА13, ЛА4, ЛА6, ЛИ2,

ЛПЗ, ЛП5, ЛП8, ТВ6)

402.16-18 (ИД7, ИЕ6,

ИЕ7, КП11...КП14,

КП16, КП2, КП7, СП-1)

402.16-32 (ИВ1, ИР11,

ТМ7, АГЗ, ИД 10, ИЕ9,

ИЕ10, ИП8, ИР9, ИР26,

ИР32, КП15, ТМ8, ТМ9,

ТР2)

402.16-33 (ИД5, ИД4,

ИМ6, ИП4, ИР25, ТВ9)

405.24-2 (ИР28, ИМ7,

ИПЗ)

4118.24-1 (ИДЗ, ИД19,

ИР22, ИР23, ИР27)

4119.28-1 (ВЖ1)

4152Ю20-1 (АПЗ...АП6)

Н533 ТТЛШ Н02.14-1В (ЛЕ4, ЛЛ1,

ЛЛ4, ТВ6)

555 ТТЛШ Н02.14-2В (ЛАЕ..ЛАЗ,

ЛА9, ЛИ1, ЛН1, ЛРП)

201.14-1 (ЛИЗ, ЛН2,

ЛП5, ТЛ2, ТР2)

П. 5-

П. 5

П. 9

П. 16

П. 2

П. 4

П. 1

П. 5

П. 8

П. 5

П. 17 Для построения

средств

вычислительной техники с

малой

потребляемой мощностью

П. 19

П. 23

П 24

П. 24

П. 25

П. 31

П. 32

П. 35

П. 36

П. 36

П. 1 Для применения в

ЭВМ, устройствах

Продолжение табл. 1.3

автоматики и свя

зи

К555 ТТЛШ 201.14-1 (ИМ5, ИП5, П. 1

ЛП8, ИЕ5, ИЕ2, ИЕ14,

ИЕ15, ИР16, ЛН1,

ЛА1...ЛА4, ЛА6, ЛА7,

ЛА9, ЛАЮ, ЛА13, ЛЕ1,

ЛЛ1, ЛЕ4, ЛИ1...ЛИЗ,

ЛИ6, ЛП12, ЛН2, ЛП5,

ЛР4, ЛРП, ЛР13, ТВ6

ТЛ2)

201.14-2 (ИП6, ИП7, П. 1

ЛА12, ЛИ4, ТМ2)

201.16-5 (ИВ1) П. 4

238.16-1 (ИВ1, ИВЗ, П. 8

ИД4, ИД5, ИД 10, ИМ6,

ИР11, ИР26, ТВ9, ТМ7)

238.16-2 (КП16, ИД32, П. 8

ИД7, ИД18, АГЗ, ИЕ10,

ИЕ6, ИЕ7, ИЕ8, ИП8,

ИР10, ИР15, ИРЗО,

ИР9, КП11...КШ5

КП2, КП7, СП1, ТМ8,

ТМ9, ТР2, ИП9)

239.24-1 (ИМ7, ИПЗ) П. 9

2140Ю.20-1 (АПЗ...АП6, П. 16

ИР22, ИР23. ИР27)

КМ555 ТТЛШ 201 14-8 (ИЕ19, ИП6, П. 2

ИП7, ИР8, ИР15, ЛА1..

ЛА4, ЛА9, ЛА12, ЛА13,

ЛЕ1, ЛЕ4, ЛИ1, ЛИЗ,

ЛИ4, ЛИ6, ЛЛ1, ЛН1,

ЛН2, ЛП12, ЛП15,

ЛРП, ЛР13, ТЛ2, ТМ2)

201.16-5 (ИД18, ИД10, П 4

ИД6, ИД4, АГЗ, ИЕ9,

ИЕ10, ИМ6, ИП4, ИРП,

ИР26, КШ5, ТМ7

ТМ9, ТР2)

201.16-6 (ИР32, ИР9 П. 4

ИР10)

КР559 ТТЛШ 238.16-2 (ИП4, СК2) П. 8 Для обмена ин-

М559 ТТЛШ 201.16-13 (ИП9, ИПЮ) П. 6 формацией между

2108.22-1 (ВВ1,'ВВ2) П. 12 устройствами и

блоками систем и

для передачи

данных иа

периферийные устройства,

устройства

отображения и

индикации

571 ТТЛШ 402.16-11 (ХЛ1...ХЛЗ) П 22 для постройки уз-

13

Продолжение табл. 1.3

КР571 ТТЛШ

580 ТТЛШ

КР580

585 ТТЛШ

589 ТТЛШ

К589 ТТЛШ

КМ589 ТТЛШ

КР1531 ТТЛШ

КР1533 ТТЛШ

1533 »

1802 ТТЛШ

KP180L »

Ml 804 ТТЛШ

КМ 180 4

Ml 804 »

К176 КМДП

4112.16-2 (ХЛ4, ХЛ5)

238.16-2 (ХЛ4, ХЛ5)

2140Ю.20-2 (ИР82,

ИР83)

201.16-13 (ГФ24)

201.16-12 (КР580,

ГФ24)

402.16-32 (АП16, АП26,

ХЛ4)

405.24-2 (ИК14, ИР12)

4119.28-1 (ИК02,

И КОЗ)

238.16-2 МП 16, АП26)

2121.28-1 (ИК02,

ИКОЗ)

2123.40-1 (ИК01)

239.24-2 (ИК14, ИР12)

238.16-2 (АП16, АП26,

ХЛ4)

239.24-2 (ИК14, ИР12)

2121.28-1 (ИК02,

ИКОЗ)

2123.40-1 (ИК01)

201.16-6 (АП16, АП26)

201.14-1

401.14-5 (остальные)

402.16-32 (КП11...КП15,

ИД4, СП1)

4118.24-1 (ИПЗ)

4119.28-1 (ИР31)

4153.20-1,01 (ИР22,

ИР23, ИРЗЗ, ИР37,

АП4, АП5)

201.14-1

4134.48-2 (ИМ1)

4118.24-1 (ИР1)

239.24-2 (ИР1)

2120.24-1 (ГГ1)

2108.22-1 (ИР2)

2121.28-6 (ИРЗ)

201.16-13 (ИР1)

201.14-1 (ИЕ1, ИЕЗ,

П. 29 лов и блоков ЦВМ

и РЭА

П. 8

П. 16 Генератор

тактовых сигналов 8-

П. 6 разрядный буфер-

П. 5 ный регистр

П. 24 Предназначены

для построения

П. 25 контроллеров

П. 32

П.

п.

п.

п.

п.

п.

п.

8

14

15

9

8

9

14

П. 15

П. 4

П. 1 Для работы в РЭА

широкого

применения

П. 19 Для построения

П. 24 различных

радиоэлектронных уст

П. 31 ройств

П. 32

П. 1

П. 34 Предназначены

П. 31 для построения

П. 9 контроллеров,

встроенных мини

ЭВМ, устройств

автоматики, си

стем обработки

данных

П. 13 То же, что и серия

1802

П. 12

П. 14

П. 6

П 1 Предназначены

14

Продолжение табл. 1.3

НСТЛМ ИЕ4, ИЕ5, ИРЗ,

ИР10, КТ1, ЛИ1, ЛП1,

ЛП4, ЛП11, ЛП12,

ЛС1, ПУ1, ТМ1)

238.16-1 (ИД1, ИД2,

ИДЗ, ИЕ2, ИЕ12, ИЕ13,

ИЕ18, ПУ2, ПУЗ, ПУ5)

П. 8

для построения

малогабаритных

устройств

цифровой автоматики и

вычислительной

техники

561

К561

КМДП

НСТЛМ

КМДП

НСТЛМ

564

КМДП

НСТЛМ

201.14-1 (ЛА7, ЛА8

ЛН2, ЛП13, ТМ2)

238.16-1 (ИЕ8, ИЕ16

ИМ1, ИР9)

201.14-1 (КТЗ, ЛА7

ЛА8, ЛА9, ЛЕ5, ЛЕ6

ЛЕЮ, ЛН2, ЛП2, ЛП13.

ТЛ1, ТМ2)

238.16-1 (ИД1, ИЕ8.

ИЕ9, ИЕ10, ИЕН.

ИЕН, ИЕ16, ИЕ19.

ИК1, ИМ1, ИП2, ИП5.

ИР2, ИР9, КП1, КП2,

ЛН1, ЛС2, ПУ4, СА1.

TBI,ТМЗ, ТР2)

405.24-7 (ИЕ15Б)

239.24-1 (ИР11,

ИР16)

402.16-33 (АГ1,

ИД5, ИЕ9, ИЕ10

ИП5, ЛН1, ПУ4

TBI, ТМЗ, ТР2,

402.16-23 (ГП,

ИЕН, ИЕ14,

Н564

КМДП

НСТЛМ

ИР12,

ИД4,

, ИП2,

, СА1,

УМ1)

ИД1,

ИЕ19,

ИК1, ИМ1, ИП4, ИР2,

ИР9, КП1, КП2, ПУ6,

ПР1)

4118.24-2 (ИЕ15, ИК2)

405.24-2 (ИПЗ, ИР6,

ИР11, ИР12, ИР13)

401.14-5 (ИП6, ИР1,

КТЗ, ЛА7, ЛА8, ЛА9,

ЛАЮ, ЛЕ5, ЛЕ6, ИЕ10,

ЛН2, ЛП2, ЛП13, ЛС1,

ПУ7, ПУ8, ТЛ1, ТМ2)

402.16-32 (ЛС2)

Н02.16-1В (ИД1, ИП2,

ЛН1, ЛС2, ПУ4, СА1,

TBI, ТМЗ, ТР2)

Н04.16-1В (ИЕ10,

ИЕН, ИК1, ИПЗ, ИП4,

ИР2, КП1, ИР9, КП2)

Комплекты

цифровых ИС // и 111

степени

интеграции для примене-

П 1 ния в аппаратуре

автоматики и

вычислительной

техники с жесткими

П. 8 требованиями по

быстродействию,

потребляемой

мощности,

габаритам,

помехоустойчивости.

Используются в широком

П. 26 диапазоне наиря-

П. 9 жения питания

П. 24

П. 24

П 31

П. 25

П 19

П. 24

П 36

П 36

15

Продолжение табл. 1.3

КР1561

120

КМДП

НСТЛМ

ЭСЛ

500

ЭСЛ

К500

ЭСЛ

Н06.24-1В (ИР6)

Н02.14-1В (КТЗ,

ЛА8, ЛА9, ЛЕ5,

ЛЕЮ, ЛН2, ЛП2,

(АП,

ИЕ20,

238.16-

ИД7,

ИР15)

201.14-

ЛА7,

ЛЕ6,

ТМ2)

ИД6,

ИЕ21,

ЛП115,

ЛП129,

ЛС119,

ПУ125,

ТМ131,

ТМ134,

239.24-2 (ИП181)

238.16-2 (ИВ 165

ИД161, ИД162, ИД164

ИЕ136, ИЕ137, ИЕ160

ИМ180, ИП179

ЛЕ106, ЛЕШ,

ЛКП7, ЛК121,

ЛЛ210, ЛМ101,

ЛМ105, ЛМ109,

ИР141

ЛЕ211

ЛЛ110

ЛМ102

ЛП107

ЛП128

ЛС118

ПУ125

ТМ131

ТМ134

ЛПЧ5, ЛП116,

ЛП129, ЛП216,

ИР400, ПУ124,

ТВ135, ТМ130,

ТМ231, ТМ133,

ТМ173)

201.16-5 (НР400)

239.24-2 (ИП181)

238.16-2 (ИВ165,

ИД161, ИД162, ИД164,

ИЕ136, ИЕ137, ИЕ160.

ИМ180, ИП179, ИР141

ЛЕ106, ЛЕШ, ЛЕ211

ЛКП7, ЛК121, ЛЛ110

ЛЛ210, ЛМ101, ЛМ102

ЛМ105, ЛМ109, ЛП107

ЛП115, ЛП116, ЛП128

ЛП129, ЛС118, ЛС119

36

36

П. 8 То же

П.

П.

П.

'КТЗ, ЛА9, П. 1

ЛЕЮ, ЛИ2, ТЛ1)

238.16-2 (КПЗ, ПУ4)

405.24-1 (ИП181)

402.16-6 (ИВ165

ИД161, ИД162, ИД164

ИЕ136, ИЕ137, ИЕ160

ИМ180, ИП179, ИР141

ЛЕ106, ЛЕШ, ЛЕ211

ЛКИ7, ЛК121, ЛЛПО

ЛЛ210, ЛМ101, ЛМ102

ЛМ105, ЛМ109, ЛП107

ЛП116, ЛП128

ЛП216, ЛС118

НР400, ПУ124

ТВ 135, ТМ130

ТМ231, ТМ133

ТМ173)

Комплекты ИС

повышенной степени

интеграции,

предназначенные для

построения

копроизводительных

вычислительных комплексов

П.

П.

п.

16

Продолжение табл. 1.3

3 4 5

ПУ124, ПУ125, ТВ135,

ТМ130, ТМ131, ТМ231,

ТМ133, ТМ134)

700 ЭСЛ бескорпусные

(ИВ165, ИД161, ИД162,

ИД 164, ИЕ160, ИМ 180,

ИП179, ИП181, ИР141,

ЛЕ106, ЛЕШ, ЛЕ211,

ЛКП7, ЛК121, ЛЛ210,

ЛМ101, ЛМ102, ЛМ105,

ЛМ109, ЛП107, ЛП115,

ЛП116, ЛП128, ЛП129,

ЛП216, ЛС118, ЛС119,

ИР400, ПУ124, ПУ125,

ТМ130, ТМ131, ТМ133,

ТМ134, ТМ173, ТМ231)

К1500 ЭСЛ 4114.24-1 (ВА123,

ИЕ160, ИП156, ИП194,

ИР141, ИР150, ИР151,

КШ55, КП163, КП164,

КП171, ЛКП7, ЛК118,

ЛМ102, ЛП107, ЛП112,

ТМ130, ТМ131)

По габаритным и присоединительным размерам сходные

по конструкции корпуса подразделяются на типоразмеры,

каждому из которых присваивается шифр, состоящий из

обозначения подтипа корпуса (табл. 1.3) и двузначного числа (от 01

до 99), обозначающего порядковый номер типоразмера, числа,

указывающего количество выводов, и порядкового

регистрационного номера (например, корпус 1202.14-1 —это

прямоугольный корпус подтипа 12 (тип 1), типоразмера 02, с 14

выводами, модификация первая).

До введения ГОСТ 17467—79 корпуса делились на четыре

типа, отличающиеся по форме и расположению выводов.

Каждому типономиналу корпуса присваивался шифр,

состоящий из обозначения типа корпуса (цифры 1, 2, 3 и 4)

и двузначного числа (от 01 до 99) — номера типоразмера.

Условное обозначение корпуса состояло из шифра его

типоразмера, числа, указывающего на количество выводов, и номера

модификации (например, корпус 201.9-1 — это прямоугольный

корпус типа 2, типоразмера 01, с 9 выводами, модификация

первая).

При размещении ИС в корпусе повой модификации перед

номером серии ставится буква, указывающая на

конструктивно-технологическое исполнение корпуса: Р — при выпуске серии

в пластмассовом корпусе второго типа; М — в керамическом

корпусе второго типа; Л — в керамическом корпусе четвертого

типа; Н — в металлостеклянном или металлополимерном кор-

Комплект

цифровых ИС,

предназначенных для

применения в

гибридных

микросхемах, микросборках

и блоках

30 Комплект ИС для

построения

радиоэлектронных

устройств широкого

применения

17

пусе четвертого типа; У — в металлостеклянном корпусе

третьего типа. Например, микросхема К155ЛАЗ, выпускаемая

в прямоугольном пластмассовом корпусе, при размещении ее

в поямоугольном кеоамическом корпусе обозначается

КМ155ЛАЗ, а серия—КМ 155.

Чертежи корпусов цифровых микросхем в справочнике

даны в приложении 1.

1.3. Параметры цифровых интегральных

микросхем

Термины, определения и буквенные обозначения

электрических параметров ИС, применяемые в науке, технике и

производстве, установлены согласно ГОСТам:

ГОСТ 19480—74 (СТ СЭВ 1817—79, 4755—84, 4756—84)

«Микросхемы интегральные. Термины, определения и

буквенные обозначения электрических параметров».

ГОСТ 17021—88 «Микросхемы интегральные. Термины

и определения».

В табл. 1.4 приведен перечень основных электрических

параметров, их буквенные обозначения и определения,

установленные этими ГОСТами. Вместе с тем в перечень не

включены обозначения и определения параметров, широко

распространенных в научно-технической литературе по радиотехнике,

таких, как частота /, длительность импульса t», входное

напряжение UB\ и другие. Читателям, которые желают

ознакомиться с полным перечнем электрических параметров, их

буквенными обозначениями и определениями, рекомендуем

обратиться к упомянутым ГОСТам.

Таблица 1.4. Параметры, характерные

для цифровых интегральных микросхем

Термин

[

Обозначения

международные

2

отечественные

3

Определение

4

Напряжение питания £/<•

Входное напряжение низ- Ui

кого уровня

Входное напряжение вы- Ui

сокого уровня

Um> Значение напряжения

источника питания,

обеспечивающего работу

интегральной микросхемы в

заданном режиме

U ах Значение входного

напряжения низкого уровня

на входе интегральной

микросхемы

UU Значение входного

напряжения высокого

уровня на входе

интегральной микросхемы

Продолжение табл. 1.4

Выходное напряжение Vol

низкого уровня

Выходное напряжение U0/i UlblK

высокого уровня

Входной ток низкого 1ц /",

уровня

ВХОДНОЙ ТОК ВЫСОКОГО //// /^

уровня

ВЫХОДНОЙ ТОК НИЗКОГО Iql Iaux

уровня

Выходной ток высокого /0// /^ыч

уровня

Ток потребления при низ- [CCL /f)0,

ком уровне выходного

напряжения

Ток потребления при вы- 1ССН

соком уровне выходного

напряжения

Средняя потребляемая Рсс.. Лют

мощность

Время задержки распро- tPIIL

странения при

включении

Значение выходного

напряжения низкого уровня

на выходе интегральной

микросхемы

Значение выходного

напряжения высокого

уровня на выходе иитеграль

ной микросхемы

Значение входного тока

при напряжении низкого

уровня на входе

интегральной микросхемы

Значение входного тока

при напряжении

высокого уровня на входе

интегральной микросхемы

Значение выходного тока

при напряжении низкого

уровня на выходе

интегральной микросхемы

Значение выходного тока

при напряжении

высокого уровня на выходе

интегральной

микросхемы

Значение тока,

потребляемого интегральной

микросхемой от

источника питания при низком

уровне выходного

напряжения

Значение тока,

потребляемого интегральной

' микросхемой от

источника питания при

высоком уровне выходного

напряжения

Значение мощности,

равное полусумме

мощностей, потребляемых

интегральной микросхемой

от источников питания

в двух различных

устойчивых состояниях

Интервал времени между

входным и выходным

импульсами при переходе

напряжения на выходе

интегральной микросхе

мы от напряжения

высокого уровня к

напряжению низкого уровня,

19

Продолжение табл. 1.4

Время задержки распро- tt

странеиия при

выключении

Ввемя задержки включе- (dhl

ния

Время задержки выклю- Idlh

чеиия

Время перехода

включении

при <

неизмеренный на уровне

0,5 или на заданном

значении напряжения

*зд. р Интервал времени между

входным и выходным

импульсами при

переходе напряжения на выходе

интегральной

микросхемы от напряжения

низкого уровня к

напряжению высокого уровня,

измеренный на уровне 0,5

или на заданном

значении напряжения

(■Л Интервал времени между

входным и выходным

импульсами при переходе

напряжения на выходе

интегральной

микросхемы от напряжения

высокого уровня к

напряжению низкого уровня,

измеренный на уровне 0,1

или на заданных

значениях напряжения

4V Интервал времени между

входным и выходным

импульсами при

переходе напряжения на выходе

интегральной

микросхемы от напряжения

низкого уровня к

напряжению высокого уровня,

измеренный на уровне

0,9 или на заданных

значениях напряжения

t ' Интервал времени, в

течение которого

напряжение на выходе

интегральной микросхемы

переходит от напряжения

высокого уровня к

напряжению низкого уровня,

измеренный на уровнях

0,1 и 0,9 или на заданных

значениях напряжения

Интервал времени, в

течение которого

напряжение на выходе интеграль-

20

Продолжение табл. 1.4

Время перехода при вы- trm

ключении

Коэффициент

разветвления по выходу

N

ной микросхемы

переходит от напряжения

низкого уровня к

напряжению высокого уровня,

измеренный на уровнях

0,1 и 0,9 или на заданных

значениях напряжения

Число единичных

нагрузок, которое можно

одновременно подключить к

выходу интегральной

микросхемы

ГЛАВА 2. Цифровые микросхемы

транзисторно-транзисторной логики

(ТТЛ!

Интегральные схемы транзисторно-транзисторной логики

(ИС ТТЛ) в настоящее время являются распространенными

микросхемами, которые используются в качестве элементной

базы ЭВМ. Сейчас усилия разработчиков и технологов

ИС ТТЛ направлены на расширение функционального состава

отдельных серий, усложнение выполняемых функций, улучшение

рабочих характеристик ИС. Существуют следующие

разновидности ИС ТТЛ:

три ранние разновидности микросхем без применения

р — «-переходов с барьером Шотки (стандартные или среднего

быстродействия — СТТЛ; маломощные — Мм ТТЛ; мощные —

МТТЛ);

две со структурами Шотки — ТТЛШ;

три новые, перспективные, усовершенствованные ТТЛШ.

В настоящее время в аппаратуре можно встретить все

перечисленные варианты микросхем ТТЛ. Напряжение питания

у них одинаковое Um = 5 В ±10%, а входные и выходные

логические уровни совместимы. Микросхемы ТТЛШ имеют

улучшенные электрические параметры, но расположение

выводов на корпусе остается прежним. Полная электрическая

и конструктивная совместимость однотипных ИС из разных

серий снимает многие проблемы развития и улучшения

параметров аппаратуры и стимулирует наращивание степени

внутренней интеграции вновь выпускаемых микросхем, когда

на одном кристалле размещается все большее число

функциональных узлов. Основная часть применяемых сейчас

микросхем ТТЛ имеет средний уровень интеграции.

Для оценки различных серий ИС используется энергия

переключения

J == 4яд.р« ПОТ)

т е. произведение задержки распространения (в

наносекундах) на рассеиваемую мощность (в милливатах) для базового

логического элемента.

Быстродействие микросхем принято сравнивать по времени

задержки распространения сигнала t3R.p, т. е. по интервалу

времени от подачи входного импульса до появления выходного.

За последние 20 лет энергия, затрачиваемая в элементе ТТЛ,

была уменьшена со (120...140) пДж до (5...20) пДж.

Основная часть такой экономии получена за счет многократного

уменьшения времени t3A.P, т. е. увеличения быстродействия.

Одновременно за это же время удалось снизить потребляемую

мощность в (2...5) раз [1, 2].

22

2.1. Основы схемотехники элементов ТТЛ

Основную логическую операцию в элементе ТТЛ выполняет

многоэмиттерный транзистор (рис. 2.1). Для удобства

рассмотрения переключения логического элемента ко входу

подключим управляющий переключатель 5/, движок которого

может занимать два положения — В и Н, а к выходу

подключим резистор Ru. В положении В на вход поступит напряжение

высокого уровня, т. е. питающее напряжение И„.п, а в

положении Н — напряжение низкого уровня, соответствующее

нулю (вход заземляем). Если на вход (рис. 2.1, а) подано

низкое напряжение (переключатель 5/ поставлен в положение

Н), то появится входной ток низкого уровня /вх, который будет

протекать от источника питания 11пл = 5 В через резистор

Rb, переход база-эмиттер многоэмиттерного транзистора VTJ,

контакт Н переключателя S1 на корпус. Величина этого

тока определяется сопротивлением резистора Rb:

/°Х = /Б Л (£/„.„ -£/бэ)//?б.

В быстродействующих и экономичных ИС ТТЛ

сопротивления резисторов Rb отличаются примерно на порядок.

Переход база — коллектор транзистора VT1 открыться не может,

так как на нем нет избыточного напряжения более чем 0,7 В =

= £/бэ- Напряжение на выходе близко к нулю UBbn ~ 0. Таким

образом, переход база — эмиттер транзистора VT1 открыт, а

переход база — коллектор VT1 закрыт, т. е. многоэмиттерный

транзистор VT1 находится в активном режиме, напряжение

на выходе равно нулю [/ВЫх — 0. Если число входов

транзистора VTJ более одного (рис. 2,1,6) (два из них не

присоединены), то величина тока /вх не изменится. Если все три

эмиттера VT1 соединить вместе, ток /вХ практически не изменится.

Следовательно, неиспользуемые входы можно оставлять

разомкнутыми. Если заземлен хотя бы один из входов

транзистора VT1 (рис. 2.1,6), смена логических уровней на

остальных входах не влияет на выходное напряжение UBUX.

Переведем движок переключателя 5/ в положение В

(рис. 2.1, в) (подано на вход напряжение высокого уровня),

тогда переход база — эмиттер транзистора VT1 будет закрыт,

так как напряжение между базой и эмиттером меньше или

равно нулю [/бэ ^ 0. Оба электрода (база и эмиттер)

подключены к источнику питания U„.n = 5 В. Большой ток базы

/б течет от источника питания Uu.n через резистор Rb,

открытый переход база — коллектор, а затем через резистор

нагрузки Rn к нулевому потенциалу (рис. 2.1, в). На коллекторе

<■ VT1 появляется напряжение высокого уровня:

UU^U„.„]Ru/(Rh-\-Rb)].

На вход / поступает лишь входной ток утечки высокого уровня

/Вх, не превышающий при нормальной температуре нескольких

наноампер (направление тока /вх показано на рис. 2.1, в)

23

(/юг f)

h

(лого)

J>HL

-U„rf5B

/We

О (лог1)в11\ 32J .

(лог op

-U,,^58

-UJff5B

(лоЩ

Выходе

,1+- U^o н r I

!nj?H (лого)\ S1

Рис. 2.1. Простейшие логические элементы ТТЛ:

а — путь входною тока /дх; б— токи в транзисторе YT1 при низком

входном уровне; в — токи в транзисторе VT1 при высоком входном

уровне; г — тики в простейшем инверторе нрн высоком входном уровне

Таким образом, переход база — эмиттер транзистора VT1

закрыт, а переход база — коллектор VT1 открыт, т. е. много-

эмиттерный транзистор VT1 находится в инверсном активном

режиме, напряжение на выходе больше нуля: £/вых > 0 (имеет

высокий уровень).

Следовательно, на рис. 2.1, в приведен одновходовый

элемент ТТЛ, реализующий логическую операцию И и не

изменяющий фазу входного сигнала. Такой элемент назовем пеин-

вертирующим. В такой схеме активным включающим является

напряжение низкого уровня и через переключатель S1 на

корпус стекает большой входной ток /°х (для стандартных

элементов ТТЛ, серия К155, ток одного входа /вХ~1,6 мА)

[1. 4].

Для получения инвертирующего логического элемента,

реализующего логическую операцию И-НЕ, необходимо к много-

эмиттерному транзистору VT1 добавить инвертор, выполненный

на транзисторе VT2 (рис. 2.1, г).

Если на вход I логического элемента поступает

напряжение высокого уровня (переключатель S/ в положении В), то

многоэмиттерный транзистор VT1 находится в инверсном

активном режиме, а транзистор VT2 насыщается базовым

током /б и выходное напряжение, снимаемое с коллектора

VT2, будет иметь низкий уровень, что соответствует

логическому нулю [/вы* (не превышает 0,3 В). Это напряжение

является напряжением насыщения коллектор — эмиттер [/кэ.н^с

для кремниевого транзистора VT2.

Если на вход I логического элемента подать напряжение

24

низкого уровня (переключатель 5/ в положении Н), то

транзистор VT2 практически закрыт, а во входной цепи течет

большой ток /вх. Выходное напряжение, снимаемое с коллектора

VT2, близко к напряжению источника питания U„ п, т. е. имеет

высокий уровень, что соответствует логической единице £/Быч.

Рассмотренный инвертор, выполненный на транзисторе VT2,

является простым инвертором. Он используется лишь в

микросхемах, выходы у которых имеют открытые коллекторы.

Недостатком простого инвертора является низкая нагрузочная

способность в закрытом состоянии (выходное сопротивление

определяется сопротивлением резистора, стоящего в

коллекторной цепи транзистора VT2).

Для повышения нагрузочной способности логического

элемента вместо простого инвертора большинство элементов ТТЛ

имеют сложный инвертор (рис. 2.2, а). Он состоит из фазо-

разделительного каскада, выполненного на транзисторе VT2,

и двухтактного выходного каскада, состоящего из выходных

транзисторов: насыщаемого VT5 и составного эмиттерного

повторителя VT3 и VT4. Рассмотрим функционирование

логического элемента со сложным инвертором.

Подадим на вход напряжение низкого уровня,

соответствующее логическому нулю (переключатель S1 поставлен

в положение Н), тогда многоэмиттерный транзистор VT1

будет находиться в активном режиме (переход база —

эмиттер открыт, а переход база — коллектор закрыт), течет большой

ток /вх во входную цепь, а транзисторы VT2, VT5 закрыты

(на рис. 2.2,6 не показаны VT2, VT5), транзисторы VT3 и VT4

будут открыты, т. к. база VT3 через резистор R2 подключена

к шине питания [/„.п=5 В. Поэтому выходное напряжение,

снимаемое с нагрузки, расположенной в эмиттерной цепи VT4,

будет иметь высокий уровень, что соответствует логической

единице и1ых.

Статическое выходное напряжение высокого уровня для

логического элемента равно: и1ВЫ\ = Un „ — IabwR4 — f/кэ —

-2Ubs.

Так как на транзисторах VT3, VT4 выполнен эмиттерный

повторитель, то он не может перейти в состояние насыщения,

и напряжение (Укэ VT4 не уменьшается меньше (0,7. .1) В,

а напряжение £/бэ примерно равно 0,7 В для транзисторов

без переходов Шотки. Падением напряжения на резисторе

R4, ограничивающем ток в выходном каскаде, когда VT4 и

VT5 открыты, можно пренебречь. Тогда получаем £/БЫХ ^

>2,6 В

Для транзисторов с переходами Шотки напряжение £/бэ

составляет (0,2...0,3) В. Следовательно, для перспективных

элементов ТТЛ напряжение высокого уровня £/,'шч ~ 3,5 В.

Подадим на вход I напряжение высокого уровня

(переключатель 5/ поставлен в положение В) (рис. 2.2, в),

соответствующего логической единице, тогда многоэмиттерный

транзистор VT1 будет находиться в инверсном активном режиме

25

Рис 2.2 Логические элементы ТТЛ со сложным инвертором:

о — схема элемента со сложным инвертором; б—распределение токов н

напряжений при низком входном \ ровне; в— распределение токов и напряжений

при высоком входном уровне

(переход база — эмиттер закрыт, а переход база — коллектор

открыт), течет большой ток /б в базу транзистора VT2, который

откроется. Часть эмиттерного тока транзистора VT2 поступает

в базу транзистора VT5, этот транзистор открывается и входит

в режим насыщения. Транзисторы VT3, VT4 будут закрыты.

Выходной сигнал, снимаемый с открытого и насыщенного

транзистора VT5 (гкэ ~ 30...50 Ом), имеет низкий уровень

L/вых — 0,3 В, что соответствует логическому нулю.

Диод VD1 предназначен для защиты входа транзистора

VT1 от пробоя и называется демпфирующим.

26

2.2. Стандартные серии ТТЛ

Базовым логическим элементом серий является логический

элемент И-НЕ. На рис. 2.3 приведены схемы трех

первоначальных элементов И-НЕ ТТЛ. Все схемы содержат три основных

каскада: входной на транзисторе VT1, реализующий логическую

функцию И; фазоразделительный на транзисторе VT2;

двухтактный выходной каскад, выполненный по схеме: составного

эмиттерного повторителя VT3, VT4 и насыщаемого транзистора

VT5 (рис. 2.3, а) или повторителя не составного (только

транзистор VT3) и насыщаемого транзистора VT5 с введением

диода сдвига уровня VD4 (рис. 2.3, б, в). Два последних

каскада образуют сложный инвертор, реализующий логическую

операцию НЕ. Если ввести два фазоразделительных каскада,

то реализуется функция ИЛИ-НЕ. На рис. 2.3, а показан

базовый логический элемент серии К131 (зарубежный аналог —

74Н). Базовый элемент серии К155 (зарубежный аналог —

74) показан на рис. 2.3, б, а на рис. 2.3, в — элемент серии

К134 (зарубежный аналог — 74L). Сейчас эти серии

практически не развиваются.

Микросхемы ТТЛ первоначальной разработки стали

активно заменяться на микросхемы ТТЛШ, имеющие во

внутренней структуре переходы с барьером Шотки. В основе

транзистора с переходом Шотки (транзистора Шотки) лежит

известная схема ненасыщенного транзисторного ключа

(рис. 2.4, а). Чтобы транзистор не входил в насыщение,

между коллектором и базой включают диод. Применение диода

обратной связи для устранения насыщения транзистора

впервые предложено Б. Н. Кононовым [2, 6]. Однако в этом

случае Ulux может увеличиться до 1 В. Идеальным диодом

является диод с барьером Шотки. Он представляет собой

контакт, образованный между металлом и слегка легированным

«-полупроводником. В металле только часть электронов

являются свободными (те, что находятся вне зоны валентности)

В полупроводнике свободные электроны существуют на

границе проводимости, созданной добавлением атомов примеси

При отсутствии напряжения смещения число электронов,

пересекающих барьер с обеих сторон, одинаково, т. е. ток

отсутствует. При прямом смещении электроны обладают энергией

для пересечения потенциального барьера и прохождения в

металл. С увеличением напряжения смещения ширина барьера

уменьшается и прямой ток быстро возрастает.

При обратном смещении электронам в полупроводнике

требуется больше энергии для преодоления потенциального

барьера. Для электронов в металле потенциальный барьер

не зависит от напряжения смещения, поэтому протекает

небольшой обратный ток, который практически остается постоянным

до наступления лавинного пробоя.

Ток в диодах Шотки определяется основными носителями

поэтому он больше при одном и том же прямом смещении

27

T 1—UU,.rf58

. SB

^^ • \\12K I I

Рис. 2.З. Принципиальные схемы первоначальных логических

элементов ТТЛ.

а — базовые элемент серии KJ31, б — базовый элемент серии К153; в — базоный элемент

серии К134

Ify VT!

Рис 2.4. Пояснение принципа получения структуры с

переходом Шотки:

а — ненасыщенный транзистрпьш ключ; б — транзистор с диодом Шотки,

о — символ транзистор.) Шотки

а, следовательно, прямое падение напряжения на диоде Шотки

меньше, чем на обычном р — я-переходе при данном токе.

Таким образом, диод Шотки имеет пороговое напряжение

28

' SB

Рис. 2.5. Принципиальные схемы логических элементов ТТЛШ с перс

ходом Шотки:

а — базовый элемент серии K53I; б базоный элемент серии К555

открывания порядка (0,2...0,3) В в отличие от порогового

напряжения обычного кремниевого диода 0,7 В и значительно

снижает время жизни неосновных носителей в полупроводнике.

В схеме рис. 2.4, б транзистор VT1 удерживается от

перехода в насыщение диодом Шотки с низким порогом

открывания (0,2...0,3) В, поэтому напряжение [/вЫ\ повысится мало

по сравнению с насыщенным транзистором VT1. На рис. 2.4, в

показана схема с «транзистором Шотки». На основе

транзисторов Шотки выпущены микросхемы двух основных серий

ТТЛШ (рис. 2.5)

На рис. 2.5, а показана схема быстродействующего

логического элемента, применяемого как основа микросхем серии

К531 (зарубежный аналог — 74S), [S — начальная буква

фамилии немецкого физика Шотки (Schottky)]. В этом элементе

в эмиттерную цепь фазоразделительного каскада, выполненного

на транзисторе VT2, включен генератор тока — транзистор VT6

с резисторами R4 и R5. Это позволяет повысить

быстродействие логического элемента. В остальном данный логический

элемент аналогичен базовому элементу серии К131. Однако

введение транзисторов Шотки позволило уменьшить /1д.р вдвое

На рис. 2.5, б показана схема базового логического

элемента серии К555 (зарубежный аналог — 74LS). В этой схеме

вместо многоэмиттерного транзистора на входе использована

матрица диодов Шотки Введение диодов Шотки исключает

накопление лишних базовых зарядов, увеличивающих время

выключения транзистора, и обеспечивает стабильность времени

переключения в диапазоне температур.

Резистор R6 верхнего плеча выходного каскада создает

необходимое напряжение на базе транзистора VT3 для его

открывания Для уменьшения потребляемой мощности, когда

логический элемент закрыт (L/Lx), резистор R6 подключен

не к общей шине, а к выходу элемента.

29

Вариант!

вариантЖ

Н5Ы

Входной и а сн ад Выходной каскад -1-

Рис. 2.6 Варианты входных каскадов перспективных элементов

ТТЛШ

Диод VD7, включенный последовательно с R6 и

параллельно резистору коллекторной нагрузки фазоразделительного

каскада R2, позволяет уменьшить задержку включения схемы

за счет использования части энергии, запасенной в емкости

нагрузки, для увеличения тока коллектора транзистора VT1

в переходном режиме.

Транзистор VT3 реализуется без диодов Шотки, т. к. он

работает в активном режиме (эмиттерный повторитель).

В настоящее время микросхемы серии К555 в основном

заменили серию К134, а в последующем должны полностью

заменить и серию К155.

Перспективные серии ТТЛШ имеют несколько измененные

схемы базовых логических элементов. На рис. 2.6 приведены

возможные схемы входных каскадов логических элементов.

Диодный вариант 1 входной цепи (маломощные, К555) имеет

большую входную емкость и сниженное пороговое напряжение

включения.

Транзисторный вариант II, применяемый в элементах

серии К531, имеет повышенное значение входного тока высокого

уровня /вХ.

Для перспективных ТТЛШ используется вариант III вход

ного каскада, где применен дополнительный усилитель тока

(транзистор 1/77). Поэтому в такой схеме значительно снижен

входной ток низкого уровня /вх, увеличено пороговое входное

30

напряжение до 1,5 В и оно зафиксировано. В перспективных

ИС применены новые интегральные транзисторы со

структурой, названной «Изопланар-П». Такие структуры отличаются:

оксидной (а не р — я-переходами) изоляцией между

соседними транзисторами;

оболочковыми областями р — я-переходов собственно

транзистора;

граничная частота транзисторов «Изопланар-П» достигает

5 ГГц (у транзисторов обычной планарной структуры /rp ~

~ 1,6 ГГц).

Среди трех перспективных серий ТТЛШ логические

элементы серии КР1531 (зарубежный аналог — 74F) считаются

как бы компромиссными, поскольку два других выполняются

в милливаттном и сверхскоростном вариантах.

Сравнительная характеристика основных параметров

микросхем ТТЛ приведена в табл. 2.1 [1].

Таблица 2.1. Основные параметры микросхем ТТЛ

Серия ТТЛ

огечест венная

зарубсжг

Параметры

Prior

mBi

э,

пДж

Нагрузка

Сн,

и Ф

Р.г.

кОм

нагрузочная

способность

К134

К155

К531

К555

КР1531

КР1533

SN74L

SN74

SN74S

SN74LS

SN74F

SN74ALS

33

10

3

10

3

4

1

10

20

2

4

2

33

100

60

20

12

8

50

15

15

15

15

15

4

0,4

0,28

2

0,28

2

10

10

10

20

10

20

2.3. Функциональный ряд ИС ТТЛ

Каждая серия ИС ТТЛ имеет определенный набор

микросхем различного функционального назначения. Совокупность

этих микросхем называют функциональным рядом. В различных

сериях существуют микросхемы одинакового функционального

назначения, имеющие одинаковую структурную схему, условное

обозначение и схему подключения (цоколевку). Однако такие

микросхемы имеют отличия в технологии изготовления,

различные корпуса и существенные отличия в параметрах. Функ

циопальный ряд ИС ТТЛ наиболее распространенных серий

приведен в табл. 2.2. Микросхемы указаны в алфавитном

порядке их функциональных буквенных обозначений.

Функциональный ряд можно разбить на несколько групп

по функциональному назначению: формирователи, генераторы,

логические элементы, триггеры, счетчики, ключи и

мультиплексоры, регистры, дешифраторы и другие Рассмотрение

таких функциональных групп в справочнике дается от простых

31

ё Таблица 2.2. Функциональный ряд основных серий микросхем ТТЛ

Одновибратор

2. Два одновибратора

3 Сдвоенный формирователь

4. Двухканальный восьмиразрядный

формирователь

5. Восьмиканальный

однонаправленный формирователь

6. Восьмиканальный двунаправленный

формирователь

7. Двойной управляемый генератор

8. Шифратор приоритетов 8—3

9. Двоично-десятичный дешифратор

высоковольтный

10 Дешифратор-демультиплексор 4Х1Ь

11. Сдвоенный

дешифратор-мультиплексор 2X4

Сдвоенный

дешифратор-мультиплексор 2X4 с открытым коллектором

Двоично-десятичный дешифратор

4X10

Двоичный дешифратор

Дешифратор для управления

матрицей на светодиодах

16. Двоично-десятичный дешифратор

12.

13.

14.

15.

АГ1

АГЗ

АП2

АПЗ

АП4

АП5

ч-

ч-

АП6

ГП

ИВ1

ИВЗ

ИД1

идз

ИД4

ИД5

ИД6

ИД7

ИД8

ИД9

ИДЮ

ч-

ч-

+

ч-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

+

+

ч-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

+

ч-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

+

+

+

+

ч-

+ +

,,,,«■*"

Продолжение табл. 2.2

7 8 9 10 И 12 13

17 Дешифратор 3X8:

а) с запоминанием ИДИ

б) со сдвигом 1 точки ИД 12

в) со сдвигом 2 точек ИД 13

18. Два дешифратора-демультиплексора ИД14

2X4

19. Дешифратор:

а) для управления шкалой красного ИД15 +

цвета

б) для управления шкалой зеленого ИД 16 Ч-

или желтого цвета

20. Дешифратор состояний ИД17

21 Дешифратор двоично-десятичного ИД18

кода в информацию для семисегмент-

ного индикатора

22. Дешифратор-демультиплексор 4X16 ИД19

23. Декадный счетчик ИЕ1

24. Четырехразрядный двоично-десятич- ИЕ2 Ч~

ный счетчик

25. Счегчик-делитель ИЕ4 -f

26. Двоичный счетчик ИЕ5 +

27. Двоично-десятичный реверсивный ИЕ6 -f-

счетчик

28. Четырехразрядный двоичный ревер- ИЕ7 -f-

сивный счетчик

29. Делитель частоты с переменным ИЕ8 Ч"

коэффициентом деления

30. Четырехразрядный десятичный син- ИЕ9

хронный счетчик

+

ч-

ч-

ч-

+

+

ч-

+

+ +

ч-

+

+

+

+ +

ч- +

+

+

Продолжение табл. 2.2

5 б

31. Четырехразрядный двоичны» сип- ИЕ10

хронный счетчик

32. Параллельный двоичный счетчик ИЕН

синхронный ИЕ13

33. Быстродействующий десятичный ИЕ14 +

счетчик асинхронный

34. Двоичный счетчик асинхронный ИЕ15

35. Четырехразрядный декадный ревер- ИЕ16

сивный счетчик синхронный

36. Четырехдвончный реверсивный счет- ИЕ17

чик синхронный

37. Четырехразрядный двоичный счетчик ИЕ18

синхронный

38. Два четырехразрядных счетчика ИЕ19

39. Схема быстрого умножителя 2X4 ИК1

разряда

40. Арифметическо-логическое устройст- ИК2

во с умножением

41. Одноразрядный полный сумматор ИМ1 +

42. Двухразрядный полный сумматор ИМ2 -\-

43. Четырехразрядный двоичный сумма- ИМЗ +

тор

44. Четырехразрядный полный сумматор ИМ4

45. Два одноразрядных двоичных пол- ИМ5

ных сумматора

46. Четырехразрядный двоичный сумма- ИМ6

тор с ускоренным переносом

47. Четырехразрядный сумматор-вычи- ИМ7

татель

+

+

+

+

+

+

+

+

+

"+* ~г*

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+ +

+ +

+ +

+

+

+

Продолжение табл. 2.2

48. 8-разрядная схема контроля четности ИП2

и нечетности

49. АЛУ для записи двух 4-разрядных ИПЗ

слов

50. Схема ускоренного переноса для ИП4

АЛУ

51 9-разрядная схема контроля четности ИП5

52. 4-шинный приемопередатчик с ин- ИП6

версными выходами

53. 4-шинный приемопередатчик ИП7

54. 8-разрядный последовательно-па- ИП9

раллельный двоичный

перемножитель

55. 4-разрядный универсальный сдвиго- ИР1

вый регистр

56. 8-разрядный сдвигающий регистр ИР2

57 8-разрядный параллельный двуна- ИРЗ

правленный регистр

58. 4-разрядный селективный накопи- ИР5

тельный регистр.

59. 8-разрядный последовательный сдви- ИР8

гающий регистр с параллельным

выходом

60. 8-разрядный сдвиговый регистр с па- ИР9

раллельным вводом информации

61 8-разрядный сдвиговый регистр ИР10

62 4-разрядный универсальный регистр ИР11

сдвига

+

+ 4~

+ +

+ +

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+ +

+

+ + + +

Продолжение табл. 2.2

5 6

12 13

63. 4-разрядный сдвиговый регистр с па- ИР12

раллельпым вводом информации

64. 8-разрядный реверсивный сдвиговый ИР13

регистр

65. 4-разрядный регистр ИР15

66. 4-разрядный универсальный регистр ИР16

сдвига

67 12-разрядный регистр последова- ИР17

тельного приближения

68. 6-разрядный параллельный регистр ИР 18

с D-триггерами

69. 4-разрядный параллельный регистр ИР19

с £>-триггерами

70. 4-разрядный двухвходовый регистр ИР20

71. 4-разрядное сдвигающее устройство ИР21

72. 8-разрядный регистр на D-триггерах ИР22

с потенциальным входом

73. 8-разрядный регистр на D-триггерах ИР23

с динамическим входом

74. 8-разрядный универсальный сдвиго- ИР24

вый регистр

75. 4-разрядный регистр с импульсным ИР25

управлением

76. Регистровый файл 4 слова на 4 раз- ИР26

ряда

77. 8-разрядный регистр ИР27

78. 8-разрядный последовательно-па ИР28

раллельный регистр

+

+

+

+

4-

+ 4-

4- 4-

I 4-

+ 4-

4-

4- +

Продолжение табл. 2.2

7 8 9 10

L2 13

79. 8-разрядный регистр хранения с

адресацией

80. 24-разрядный последовательный

регистр сдвига

81 Регистровый файл 4 слова на 4

разряда с открытым коллекторным

выходом

82. 8-разрядный буферный регистр

83. Два 4-разрядных буферных регистра

84. 8-разрядный буферный регистр с

импульсным управлением

85. Два 4-разрядных регистра D-типа

86. БИС регистров общего назначения

с многоканальным доступом

87 Селектор-мультиплексор на 16

каналов со стробированием

88. Сдвоенный цифровой

селектор-мультиплексор 4 — 1

89. Селектор-мультиплексор на 8

каналов

99. Селектор-мультиплексор на 8

каналов со стробированием

91. Три схемы переключателя

92. Сдвоенный коммутатор 4 каналов в 1

93. Коммутатор 8 каналов в 1

94. 4-разрядный

селектор-мультиплексор 2 каналов в 1 с тремя

состояниями

ИРЗО

ИР31

ИР32

ИРЗЗ

ИР34

ИР37

ИР38

ИР39

КП1

КП2

КП5

КП7

КП8

КП9

кпю

КПП

4-

4-

+

4-

4-

4-

+

4-

4-

4-

4-

4- 4-

4-4-4-4-

4-4-4-4-

4-

4-

7 8

95. 2-разрядный 4-канальный

коммутатор

96. Четыре 2-входовых мультиплексора

с запоминанием

97. 4-разрядный

селектор-мультиплексор 2 каналов в 1 с инверсными

выходами

и тремя устойчивыми состояниями

98. 8-входовый селектор-мультиплексор

99. 4-разрядный

селектор-мультиплексор 2 каналов в 1

100. Сдвоенный инверсный селектор-

мультиплексор 4 каналов в 1 с тремя

состояниями

101. 4-разрядный

селектор-мультиплексор 2 каналов в 1 с инверсными

выходами

102. Сдвоенный селектор-мультиплексор

4 каналов в 1

103. Два логических элемента 4 И-НЕ

104. Логический элемент 8 И-НЕ

105. Четыре логических элемента 2 И-НЕ

106. Три логических элемента ЗИ-НЕ

107. Два логических элемента 4 И-НЕ с

повышенной нагрузочной

способностью

108. Два логических элемента 4 И-НЕ

с открытым коллекторным выходом

109. Четыре логических элемента 2 И-НЕ

КП12

КП13

КП14

КП15

КП16

КП17

КП18

КП19

4- Ч-

4- + +

Л- + +

ч-

ЛА1

ЛА2

ЛАЗ

ЛА4

ЛА6

ЛА7

ЛА8

ч-

4-

ч-

ч-

4-

ч-

4-

ч-

4-

ч-

ч-

ч-

ч-

4-

4-

4-

ч-

ч-

ч-

ч-

ч-

ч-

ч-

+

ч-

ч-

ч-

ч-

ч-

4-

ч-

ишшнн

с открытым коллекторным выходом

110. Три логических элемента 3 И-НЕ с

открытым коллекторным выходом

111. Четыре логических элемента 2 И-НЕ

с открытым коллекторным выходом,

высоковольтных

112. Четыре логических элемента 2 И-НЕ

с высокой нагрузочной способностью

1 13. Четыре логических элемента 2 И-НЕ

с открытым коллектором и высокой

нагрузочной способностью

114. Четыре логических элемента 2 И-НЕ

сопряжения микросхем МОП

ЗУ-ТТЛ

115. Два логических элемента 4 И-НЕ

(магистральный усилитель)

116. Два логических элемента 4 И-НЕ с

тремя состояниями на выходе

117. Два логических элемента 2 И-НЕ

с мощным открытым коллекторным

выходом

118. Логический элемент 12 И-НЕ с тремя

состояниями на выходе

119. Четыре логических элемента 2 И-НЕ/

2 ИЛИ-НЕ

120. Два логических элемента 4 И-НЕ/

4 ИЛИ-НЕ и логический элемент

НЕ

121 Два 4-входовых логических

расширителя по ИЛИ

ЛА15

ЛД1

ЛА9

ЛАЮ

ЛАП

ЛА12

ЛА13

4-

ч-

ч-

ч-

ч-

ч-

ч-

4-

ч-

ЛАЮ

ЛА17

ЛА18

ЛА19

ЛБ1

ЛБ2

4-

ч-

ч-

ч-

ч-

ч-

+

ю

+ +

ч-

ч-

ч-

ч-

+

+

+

+

ч-

ч-

ч-

ч-

+

Продолжение табл. 2.2

ю и 12

122.

123.

124

125.

126.

127

128.

129.

130.

131

132.

133.

134.

135.

136.

137

8-входовый расширитель по ИЛИ

Четыре логических элемента 2 ИЛИ-

НЕ

Два 4-входовых логических элемента

ИЛИ-НЕ со стробированием на

одном и расширением по ИЛИ на

другом

Два логических элемента 4 ИЛИ-НЕ

со стробированием

Три логических элемента 3 ИЛИ-НЕ

Четыре логических элемента 2 ИЛИ-

НЕ буферных

Четыре логических элемента 2 ИЛИ-

НЕ, магистральный усилитель

Два логических элемента 5 ИЛИ-НЕ

Четыре логических элемента 2И

Четыре логических элемента 2И с

открытым коллекторным выходом

Три логических элемента ЗИ

Три логических элемента ЗИ с

открытым коллекторным выходом

Два логических элемента 2И с

мощным открытым коллекторным

выходом

Два логических элемента 4И

Логический элемент 4 И-2 ИЛИ-НЕ/

4 И-2 ИЛИ с возможностью

расширения по ИЛИ

Два логических элемента 2(2-2И-

ЛДЗ

ЛЕ1

ЛЕ2

ЛЕЗ

+

+

+

+

+

+

+

ЛЕ4

ЛЕ5

ЛЕ6

ЛЕ7

ЛИ1

ЛИ2

ЛИЗ

ЛИ4

+

+

+

+

+

+

+

+

ЛИ5

ЛИ6

ЛК1

Л КЗ

+

+

+ +

+ +

+ +

+ +

+

+

+

+

+

+

+

+

+

+

+

+

+ +

+

+

+

+ +

+

+

Продолжение табл. 2.2

10 11 12 13

140.

141

2ИЛИ-НЕ/2-2И-2ИЛИ)

138. Логический элемент 2-2-2-2И-4ИЛИ- ЛК4

НЕ/2-2-2-2И-4ИЛИ с возможностью

расширения по ИЛИ

139. Логический элемент 8И-НЕ/8И с воз- ЛК5

можностью расширения по ИЛИ

Два логических элемента 2И-2И- ЛК6

2ИЛИ/2И-2И-2ИЛИ-НЕ

Логический элемент 2И-2И-2И-2И-

4ИЛИ/2И-2И-2И-2И-4ИЛИ-НЕ с ЛК7

возможностью расширения по ИЛИ

142. Четыре логических элемента 2ИЛИ

143. Два логических элемента 2ИЛИ

с мощным открытым коллекторным

выходом

144. Шесть логических элементов НЕ

145. Шесть логических элементов НЕ с

открытым коллекторным выходом

146. Шесть буферных логических элемен- ЛНЗ

тов НЕ с повышенным коллекторным

напряжением

6 элементов НЕ с открытым коллек- ЛН4

тором

Шесть буферных логических элемен- ЛН5

тов НЕ

149. Шесть логических элементов НЕ с ЛН6

тремя состояниями па выходе

150. Два приемника сигналов с парафаз- ЛП1

ным входом и выходом

147

148

+

+

+

+

+

ЛЛ1

ЛЛ2

ЛН1

ЛН2

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

7 8 9

151 Три логических элемента

мажоритарной логики 2-2-2-И-З ИЛИ-НЕ

152. Шесть буферных формирователей с

открытым коллектором

153. Четыре 2-входовых элемента

«исключающее ИЛИ»

154. Два логических элемента 2И-НЕ с

общим входом и двумя мощными

транзисторами

155. Четыре буферных элемента с тремя

состояниями на выходе

156. Шесть буферных формирователей с

открытым коллектором и

повышенным коллекторным напряжением

157 Шесть повторителей с элементом

управления по входам и тремя

состояниями на выходе

158. Шесть повторителей с раздельными

элементами управления входами по

двум и четырем повторителям с тремя

состояниями на выходе

159. Четыре 2-входовых логических

элемента «исключающее ИЛИ» с

открытым коллекторным выходом

160. Два логических элемента 2-2И-

2ИЛИ-НЕ, один расширяемый по

ИЛИ

161 Логический элемент 2И-2И-ЗИ-

4ИЛИ-НЕ

ЛПЗ

ЛП4

ЛП5

ЛП7

ЛП8

ЛП9

ЛП10

ЛП11

+

+

+

+

+

+

+

+

+

+

+

+

ЛП12

ЛР1

ЛР2

+

+ + +

+

+ + +

+

162. Логический элемент 2-2-2-ЗИ-4ИЛИ-

НЕ с возможностью расширения по

ИЛИ

163. Логический элемент 4-4И-2ИЛИ-НЕ

с возможностью расширения по ИЛИ

164. Логический элемент 4-2-2-ЗИ-4ИЛИ-

-НЕ

165. Логический элемент 4-2-3-2И-4ИЛИ-

НЕ с открытым коллекторным

выходом

166. Два логических элемента 2-2И-

-2ИЛИ-НЕ

167. Логический элемент (2-3-3-2)И-

4ИЛИ-НЕ

168. Преобразователь

двоично-десятичного кода в двоичный

169. Преобразователь двоичного кода в

двоично-десятичный

170. Схема сравнения двух 4-разрядных

чисел

171. //< — триггер с логикой ЗИ на входе

172. Два J /(-триггера со сбросом

173. Два //(-триггера с установкой «0»

и «1»

174. Два J К — триггера с установкой «Ь

175. Два J К — триггера с установкой «Ь

и общей установкой нуля и

синхронизацией

ЛРЗ

ЛР4

ЛР9

ЛР10

ЛР11

ЛР13

ПР6

ПР7

СП1

TBI

ТВ6

ТВ9

ТВ10

ТВ 11

+

+

+

+

+

+

+

+

+

+

+

+ +

+

+ +

+ +

+

+

+

+

+

+

+

+

+

+

+

+

групп к сложным, с указанием их условного обозначения,

схемы подключения (цоколевки) и основных параметров,

сведенных в отдельные таблицы. Такие таблицы основных

параметров микросхем, сгруппированных по функциональному

назначению, позволяют очень быстро выбрать микросхему

с заданными параметрами из всего многообразия серий. Затем

в справочнике дается их применение в более сложных

устройствах с указанием конкретных серий, номиналов параметров

навесных элементов и отдельных вариантов практических

схем.

Микросхемы памяти и схемы вычислительных средств

в данном справочнике не рассматриваются ввиду их

специфического назначения и наличия специальных справочников

например [3].

2.4. Логические элементы

Функциональная группа ТТЛ включает все типы элементов,

реализующих основные логические функции: НЕ, И, И-НЕ,

ИЛИ, ИЛИ-НЕ, И-ИЛИ-НЕ и другие. Все основные элементы

группы выполнены с двухтактным выходом. Для реализации

монтажных функций И некоторые типы ИС имеют открытый

коллекторный выход. Логические элементы с повышенной

нагрузочной способностью используются в разветвленных и

межплатных соединениях. Также имеются логические

элементы с повышенной помехоустойчивостью.

Микросхемы типа Л А (ЛА1...ЛА4, ЛА6...ЛА13, ЛА15..

Л А19) выполняют логическую функцию тИ — НЕ, а ИС типа

ЛИ (ЛИ1...ЛИ6) выполняют логическую функцию тИ, где

m — число входов.

Чтобы рассмотреть схемотехнику таких элементов ТТЛ,

составим таблицу функций элементов И, И-НЕ для двух

входов А и В (простейший вариант). Каждая переменная

А и В (рис. 2.7) моделируется электронным ключом, который

можно замкнуть или разомкнуть. Если ключи соединены

последовательно, то они работают согласно логике И: ток в цепи

появится, если замкнуть оба ключа: и А и В. Если активными

входными сигналами считать замыкание ключей А и В и назвать

это событие логической 1, то, последовательно перебирая

состояние этих" ключей, составим таблицу входных и выходных

данных для элементов И и И-НЕ.

Рассмотрим способ реализации логической операции И-НЕ

на элементах ТТЛ На рис. 2.8, а приведена принципиальная

схема двухвходового логического элемента И-НЕ. Подавая от

ключей S/ и S2 на входы А и В напряжение высокого В

и низкого Н уровней, составим таблицу выходных уровней

элемента (рис. 2.8,6). Напряжение низкого уровня Н

появляется на выходе Q, когда на обоих входах А и В присутствует

высокое напряжение В. Условное графическое обозначение

двухвходового логического элемента показано на рис 2.8, в

45

a

an

\

к

\в

•Выходи

i'

Входные

переменные

A

0

0

t

1

В

0

f

0

t

События:

0 s

1

Выходная

Функция

И

Q

0

0

t

Й

1

/

/

0

Зле/с/пртеские

на об ни:

1—f

0—'

Рис. 2.7 Двухвходовый логический элемент и

таблица его состояний

Uu.n--5B

Вход

А

н

н

в

в

В

н

в

н

в

Выход

в

в

в

н

Вход

А

0

0

1

1

в

0

1

0

1

Выход

1

1

1

0

46

и,

ил

Sf

X

if

Г

8с

Q-AB

Рис. 2.8. Логический элемент

2И-НЕ:

а — принципиальная схема элемента, б

таблица состояний; в— условное

обозначение элемента

S2 В

Среди простейших ИС ТТЛ преобладают элементы И, И-НЕ.

Каждый из корпусов ИС типа ЛА и ЛИ содержит от двух до

четырех логических элементов, а микросхемы ЛА2 и ЛА19

содержат по одному логическому элементу И-НЕ на восемь

и двенадцать входов соответственно.

Цоколевки микросхем типа ЛА и ЛИ и их условные

графические обозначения приведены на рис. 2.9, а основные

параметры даны в табл. 2.3.

Следует особо выделить группу микросхем, логические

элементы которых имеют выходы с открытым коллектором

(ЛА7...ЛА11, ЛА13, ЛА18), (ЛИ2, ЛИ4, ЛИ5). Схема двух-

входового логического элемента И-НЕ с открытым коллектором

показана на рис. 2.10, а. Для формирования выходного

перепада напряжения к выходу такого элемента необходимо под-

ЛИЗ.ЛИЧ ЛИ5

А!

А2

82

A3

В1

Ah

вн

1

2

Ч

5

9

10

а!

JL

ли 1, лиг

8<

а

8с

Вс

J

А1В1

В

А2В2

8

АЗВЗ

11

АЧВЧ

A1JL

А2-^-

С2-3-

9

A3

BJ

СЗ

$

8с

12_

AfBfCI

AfBf-

А2

А2В2С2 В2

8с

8с

5

AfBf

10

А2В2

АЗВЗСЗ

^-питание;

7-общий

14-питание;

7-общий

лив

14-питание;

7-общий

А1 4г-

В1-%-

cf -4-

df 5

А2 9

82 J^

Г? Jff.._

8с

8с

6

A1B1CW1

JL

A282C2JJ2

14-питание;

7- общий

Рис. 2.9. Условные обозначения и цоколевки микросхем

типа ЛА и ЛИ

47

ЛА1,ЛАВ,ЛА7,ЛА/в

1

Л A'f, Л AW

А1-*

Bf-4-

V2---1

А282СШ2

М-питание;

7-общий

JIA2

р ^

с е

G "72

H --

ft-питание;

7- общий

ЛА31ЛА9,ЛАП,ЛА(31ЛА15

1

I't -питание;

7- общий

А1-±-

ef-ir

A2~4~

B2~±-

C2~§-

A3 9

"if

* \

*

12_

AWtCI

A333C3

m- питание;

7- OBWLUQ

ABCdEFBH

l1/-питание;

7-вбщий

ЛА/2

М-

Bf-

А2-

В2-

АЗ-

63.

АЧ-

Blt-

А181

Ш2

9

ШЗ

13

АЧВЧ

Ш-питание;

8-общий

Продолжение рис. 2.9.

ЛА17(ЛА17П}

А1-

Bf-

Е02

А2

82

С2

V2

~73*

6

Ш

-32

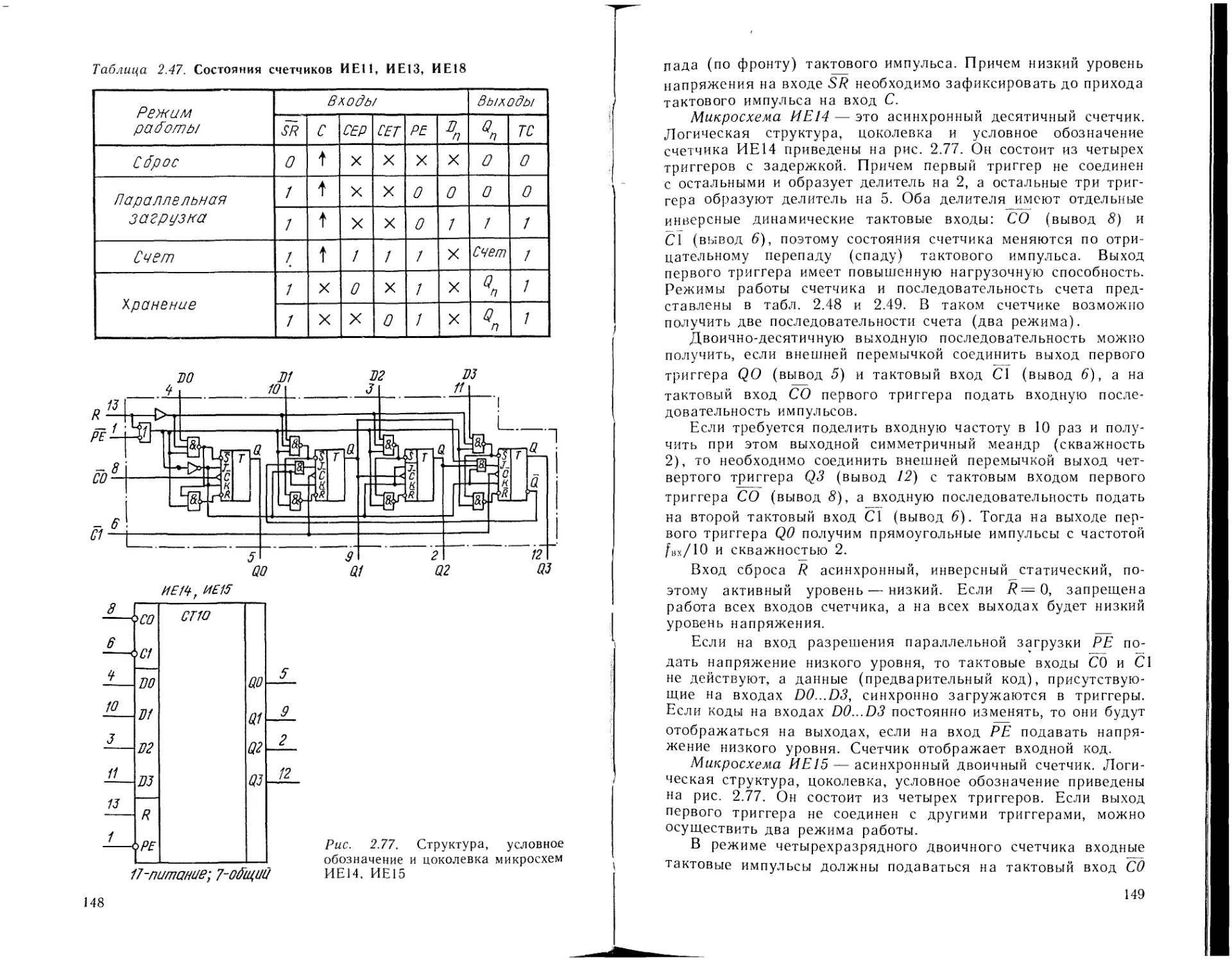

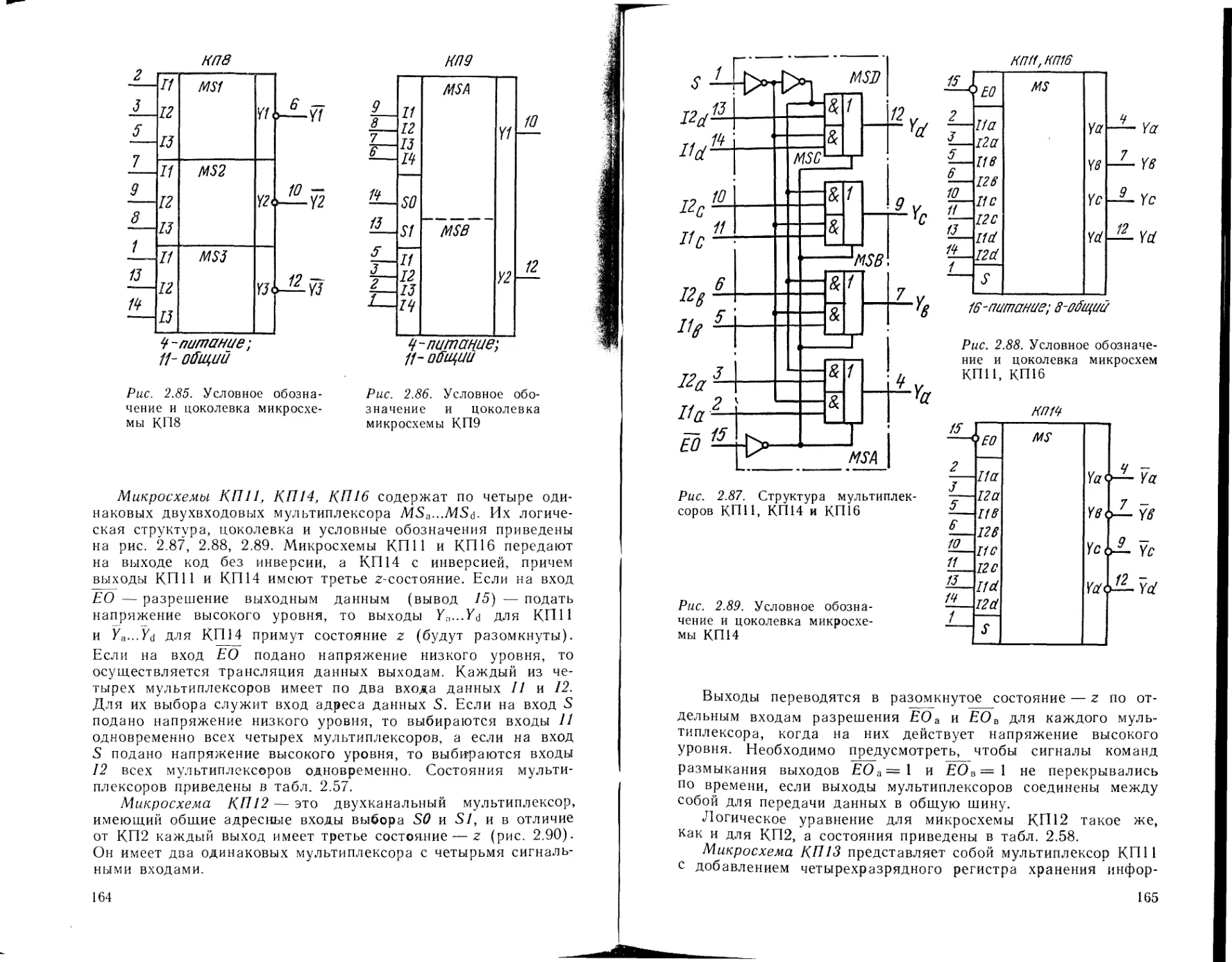

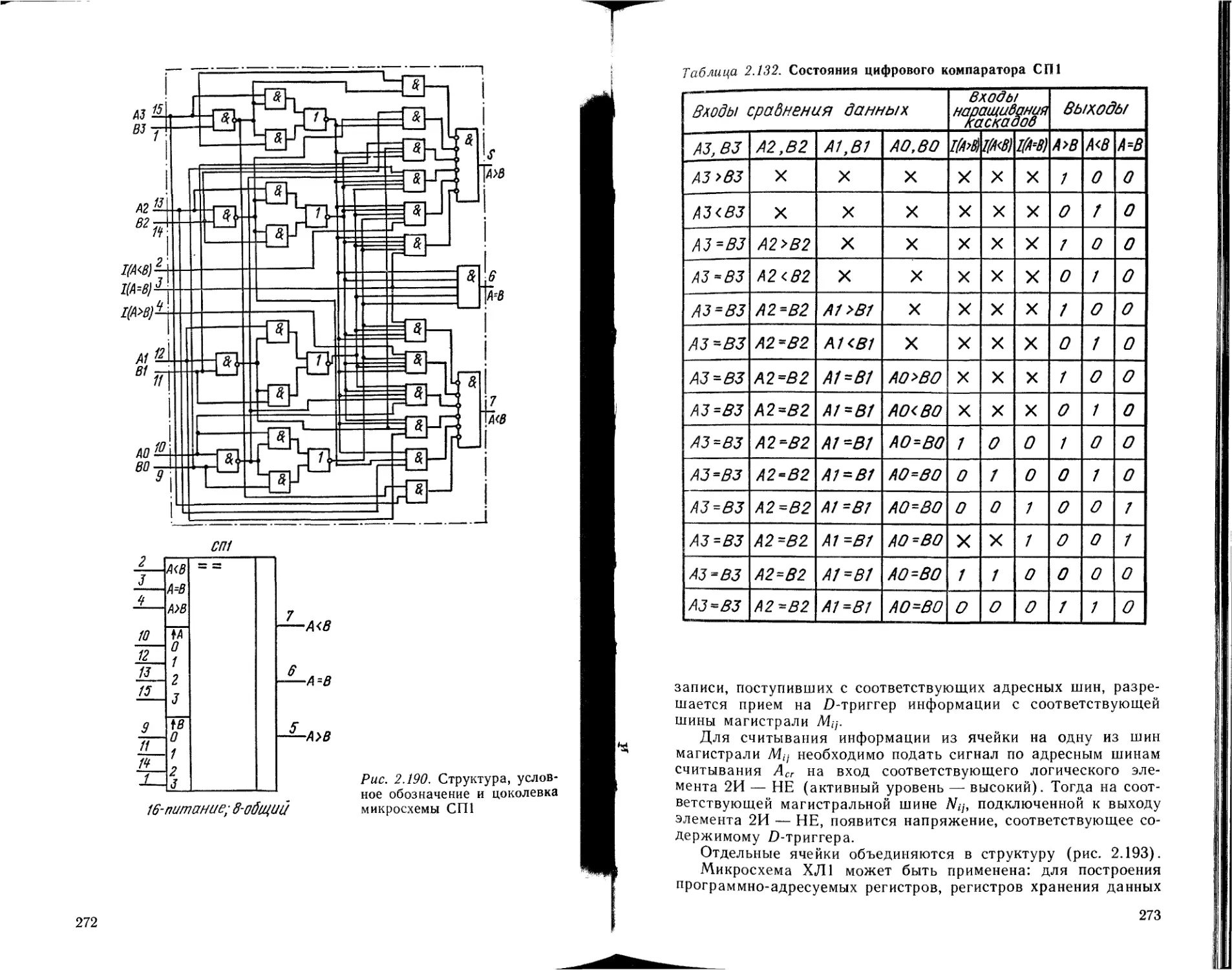

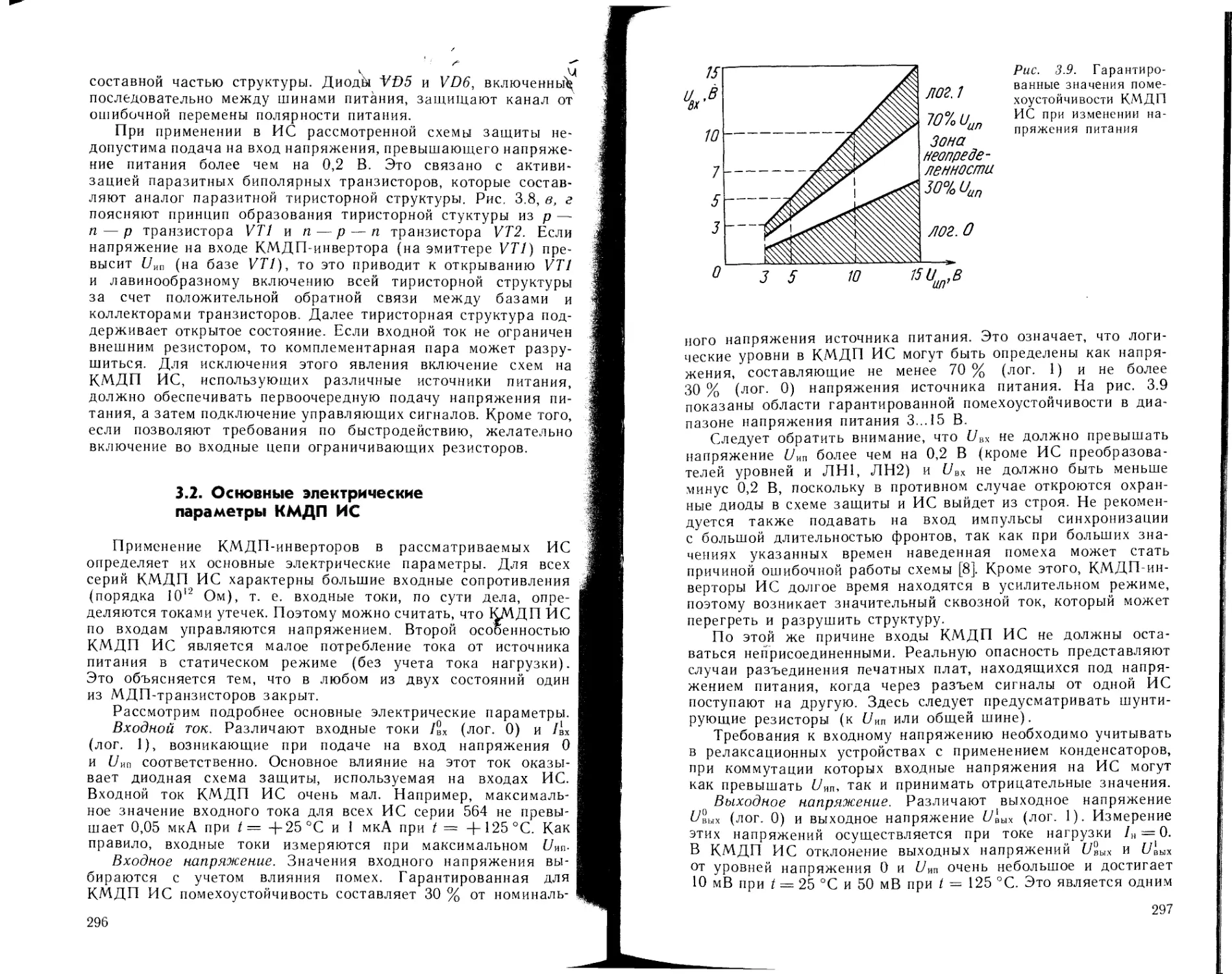

/4--питание;