Text

'W

Ю. В. Новиков

ОСНОВЫ м

ЦИФРОВОЙ

СХЕМОТЕХНИКИ

БАЗОВЫЕ ЭЛЕМЕНТЫ И СХЕМЫ

МЕТОДЫ ПРОЕКТИРОВАНИЯ

Издательство «МИР»

Ю. В. Новиков

ОСНОВЫ ЦИФРОВОЙ

СХЕМОТЕХНИКИ

БАЗОВЫЕ ЭЛЕМЕНТЫ И СХЕМЫ

МЕТОДЫ ПРОЕКТИРОВАНИЯ

Для студентов, преподавателей, профессионалов.

ISBN 5-03-003449-8

СОВРЕМЕННАЯ

СХЕМОТЕХНИКА

Ю. В. Новиков

основы

ЦИФРОВОЙ

СХЕМОТЕХНИКИ

БАЗОВЫЕ ЭЛЕМЕНТЫ И СХЕМЫ

МЕТОДЫ ПРОЕКТИРОВАНИЯ

Москва «МИР» 2001

УДК 621.374.1

ББК 32.85

Н73

Новиков Ю. В.

Н73 Основы цифровой схемотехники. Базовые элементы и

схемы. Методы проектирования. — М.: Мир, 2001. — 379 с.,

ил. — (Современная схемотехника)

ISBN 5-03-003449-8

Книга представляет собой учебник по основам цифровой схемотех-

ники. Рассматриваются основы схемотехники цифровых устройств,

которыми должен свободно владеть и активно пользоваться каждый

профессиональный разработчик цифровой аппаратуры. Обсуждается

функционирование и взаимодействие всех основных типов цифровых

микросхем — от самых простых до самых сложных. Описываются

модели и уровни представления цифровых микросхем, используемых

при проектировании цифровых электронных систем, способы опти-

мального построения высокоэффективных цифровых систем самой

различной степени сложности. Книга позволяет освоить азбуку цифро-

вой схемотехники даже читателям с начальным уровнем знаний по

электронике. Усвоению материала помогает большое количество кон-

кретных примеров построения самых различных цифровых устройств.

Для студентов, преподавателей и профессиональных разработчиков

цифровых электронных систем.

ББК 32.85

Редакция литературы по информатике и новой технике

ISBN 5-03-003449-8

© «Мир», 2001

ОГЛАВЛЕНИЕ

Предисловие ................................................... 7

Введение ...................................................... 8

Глава 1. Философия цифровой электроники.................... 13

1.1. Аналог или цифра?............................ 13

1.2. Модели и уровни представления цифровых устройств 17

1.3. Входы и выходы цифровых микросхем............ 24

1.4. Основные обозначения на схемах ................. 32

1.5. Серии цифровых микросхем........................ 37

1.6. Корпуса цифровых микросхем...................... 43

1.7. Двоичное кодирование ........................... 44

1.8. Функции цифровых устройств...................... 50

Глава 2. Применение логических элементов...................... 53

2.1. Инверторы....................................... 54

2.2. Повторители и буферы............................ 58

2.3. Логические элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ .... 65

2.4. Логические элементы Исключающее ИЛИ......... 74

2.5. Сложные логические элементы .................... 78

2.6. Триггеры Шмитта................................. 80

Глава 3. Применение комбинационных микросхем.................. 87

3.1. Дешифраторы и шифраторы......................... 88

3.2. Мультиплексоры.................................. 97

3.3. Компараторы кодов ............................. 101

3.4. Сумматоры ..................................... 105

3.5. Преобразователи кодов.......................... 109

3.6. Одновибраторы и генераторы..................... 114

Глава 4. Применение триггеров и регистров.................... 123

4.1. Триггеры....................................... 124

4.1.1. Принцип работы и разновидности триггеров. 124

4.1.2. Основные схемы включения триггеров.......... 131

4.2. Регистры....................................... 142

4.2.1. Регистры, срабатывающие по фронту........... 144

4.2.2. Регистры, срабатывающие по уровню........... 153

4.2.3. Сдвиговые регистры.......................... 157

Глава 5. Применение счетчиков ............................... 170

5.1. Асинхронные счетчики .......................... 172

5.2. Синхронные счетчики с асинхронным переносом ... 181

5.3. Синхронные счетчики............................ 209

6 Оглавление

Глава 6. Применение микросхем памяти...................... 222

6.1. Постоянная память........................... 225

6.1.1. ПЗУ как универсальная комбинационная микро-

схема .......................................... 231

6.1.2. ПЗУ в генераторах импульсных последовательно-

стей ........................................... 240

6.1.3. Микропрограммные автоматы на ПЗУ........ 245

6.2. Оперативная память.......................... 258

6.2.1. ОЗУ для временного хранения информации . 264

6.2.2. ОЗУ как информационный буфер............ 272

6.2.3. Улучшение параметров ОЗУ................ 280

Глава 7. Применение микросхем ЦАП и АЦП.................. 284

7.1. Применение ЦАП.............................. 285

7.2. Применение АЦП.............................. 295

Глава 8. Примеры разработки цифровых устройств........... 307

8.1. Разработка клавиатуры ...................... 308

8.2. Разработка вычислителя контрольной суммы... 316

8.3. Разработка логического анализатора ......... 321

8.4. Разработка генератора аналоговых сигналов... 336

Приложение. Микросхемы, параметры, сигналы................ 351

Список литературы......................................... 365

Словарь терминов и сокращений............................. 368

ПРЕДИСЛОВИЕ

Цель этой книги — помочь в изучении основ цифровой схемо-

техники любому желающему — от студента до профессионала.

Причем речь в данном случае идет не о физических основах элек-

троники, не о технологии производства электронных компонен-

тов, не об электронике или схемотехнике вообще, а именно о

цифровой схемотехнике с ее специфическими особенностями.

В книге рассмотрены многие важные вопросы цифровой

схемотехники, которым в литературе обычно уделяется недоста-

точно внимания. Видимо, авторы книг считают их чем-то само

собой разумеющимся или полагают, что читатели сами должны

сформулировать эти вопросы и сами же найти на них ответы.

В результате нередки случаи, когда даже выпускники институтов

по специальностям, связанным с электроникой, не могут само-

стоятельно разработать более или менее сложное нестандартное

цифровое устройство. После изучения данной книги читатель

будет обладать необходимыми навыками для проектирования как

простейших узлов, так и довольно сложных устройств.

Книга написана сжато, последовательно и доступно и тре-

бует минимального обращения к другим источникам. Часть ма-

териала, представленного в ней, написана на основе лекций, чи-

таемых автором в МИФИ.

Конечно, в такой небольшой книге невозможно рассмотреть

все компоненты цифровой электроники и все приемы проектиро-

вания цифровой схемотехники. Предполагается, что она станет

первой в серии книг по цифровой схемотехнике. В последующих

книгах серии будут рассмотрены, в частности, следующие темы:

• схемотехника устройств на основе программируемой логики;

• схемотехника микропроцессорных устройств;

• схемотехника устройств на основе микроконтроллеров;

• схемотехника персональных компьютеров;

• схемотехника компьютерных систем измерения, контроля и

управления;

• аппаратно-программные средства отладки и контроля цифровых

устройств;

• программные средства проектирования цифровых устройств.

Ю. В. Новиков

6 июня 2001 г.

ВВЕДЕНИЕ

Цифровая электроника в настоящее время все более и более вы-

тесняет традиционную аналоговую. Ведущие фирмы, произво-

дящие самую разную электронную аппаратуру, все чаще заяв-

ляют о полном переходе на цифровую технологию. Причем это

относится как к бытовой технике (аудио-, видеоаппаратура,

средства связи), так и к профессиональной технике (измеритель-

ная, управляющая аппаратура). Ставшие уже привычными пер-

сональные компьютеры также полностью реализованы на осно-

ве цифровой технологии. Видимо, в ближайшем будущем пол-

ностью аналоговые устройства будут применяться только в тех

редких случаях, когда требуется получить рекордные значения

некоторых параметров электронных устройств (например, быст-

родействия).

Между тем литературы, позволяющей самостоятельно изу-

чить основы и главные методы цифровой схемотехники, осво-

ить основные практические приемы проектирования цифровых

устройств, явно недостаточно. Книги, которые претендуют на

освещение основ цифровой схемотехники, можно разделить на

три большие группы.

К первой группе относятся книги, которые стремятся охва-

тить всю электронику в целом (как цифровую, так и аналого-

вую). Такой глобальный подход неизбежно приводит к тому,

что цифровая схемотехника рассматривается чересчур кратко,

поверхностно. Даже самые лучшие из книг этой группы уделя-

ют цифровой электронике не более четверти своего объема.

Между тем цифровая электроника существенно отличается от

аналоговой не только видом используемых сигналов, но, что

самое главное, приемами проектирования, требуемым стилем

мышления разработчика, принципами построения сложных сис-

тем. Данные книги хороши в основном для повышения общего

уровня образования читателя, для создания общего базиса, на

котором только и может вырасти настоящий специалист, разра-

ботчик электронной аппаратуры.

Ко второй группе относятся книги, посвященные цифро-

вым микросхемам и их применению. Эти книги стремятся

описать как можно более подробно все имеющиеся микро-

схемы, поэтому обязательно содержат большой справочный

Введение 9

материал. Однако в любом случае приводимые в них спра-

вочные данные далеко не полны и к тому же неизбежно со-

держат большое количество ошибок. Справочников по мик-

росхемам должно быть как можно меньше, и они должны

быть очень подробными, иначе они просто не имеют смысла.

В идеале справочники должны выпускаться только фирмами-

изготовителями микросхем. А попытка ввести в книгу даже

краткие справочные данные по всем существующим микро-

схемам не оставляет достаточно места для описания самого

главного — разнообразных применений этих микросхем, ме-

тодам проектирования цифровых узлов и устройств на их ос-

нове. Поэтому книги этой группы годятся обычно только для

первичного знакомства с темой.

Наконец, третья группа книг описывает готовые цифровые

устройства различного назначения. В основном такие книги

рассчитаны на «радиолюбителей», хотя обычно не совсем по-

нятно, что подразумевается под этим понятием. Среди тех, кто

называют себя радиолюбителями, немало прекрасных разра-

ботчиков, а среди дипломированных профессионалов встре-

чаются те, кто не может разработать даже простейшей схемы.

Книги этой третьей группы, как правило, не говорят о том, как

разрабатывались те или иные устройства, какие приемы про-

ектирования применялись и почему. Поэтому они могут сфор-

мировать у неподготовленного читателя привычку к бездум-

ному повторению готовых решений, использованию шабло-

нов. Настоящую пользу данные книги могут принести только

тому, у кого уже есть хороший базовый запас знаний и умений

по проектированию цифровых устройств. Впрочем, для таких

людей чужие схемы не слишком интересны, они могут проек-

тировать свои.

К недостаткам многих существующих книг можно отнести

также чрезмерное увлечение описание тонкостей физических

процессов, лежащих в основе цифровой электроники, и подроб-

ное рассмотрение особенностей технологии микросхем. Конеч-

но, все это тоже нужно, полезно, интересно, но с самой схемо-

техникой связано не жестко, не прямо и не слишком сильно.

Разработчик цифровой аппаратуры в подавляющем большинст-

ве случаев работает с микросхемами как с «черным ящиком»,

ему не слишком важно, что происходит внутри, как реализуется

та или иная функция микросхемы. Видимо, целесообразно фи-

10 Введение

зику полупроводников и технологию изучать отдельно от схе-

мотехники, параллельно с ней, до нее или после нее, чтобы не

смешивать две различные области знаний.

Наконец, еще одним недостатком книг о цифровой схемо-

технике можно назвать стремление охватить в одной книге все

области цифровой электроники: от логических элементов до

компьютеров и других сложных электронных систем. В резуль-

тате все вопросы рассматриваются недостаточно глубоко, и до

практики разработки дело не доходит. К тому же проектирова-

ние интеллектуальных устройств довольно сильно отличается от

проектирования устройств на жесткой логике. Эти направления

цифровой схемотехники требуют применения совершенно раз-

ных подходов, и поэтому их целесообразно рассматривать в

различных книгах.

Данная книга посвящена самым основам цифровой схемо-

техники, ее азбуке, ее основным методам, подходам и приемам.

Отличие ее состоит в том, что она может дать представление о

цифровой схемотехнике даже тем читателям, которые имеют

слабое представление об электронике вообще. Впрочем, это во-

все не означает, что книга посвящена только самым общим, не-

конкретным, отвлеченным вопросам. Наоборот, она призвана

сформировать действительно хорошего проектировщика, спо-

собного строить высокоэффективные цифровые системы самой

различной сложности и четко представляющего себе взаимо-

связь всех процессов в этих системах сверху донизу. Конечно,

чтобы стать таким классным специалистом, нужны определен-

ные способности, даже талант, но строить простейшие цифро-

вые устройства, пусть и не оптимальные, не уникальные, но по-

лезные и вполне работоспособные, способен практически каж-

дый человек. Хотелось бы надеяться, что данная книга окажет в

этом деле действенную помощь.

Книга ни в коем случае не претендует на то, чтобы заменить

собой справочники по микросхемам, хотя в ней и разъясняют-

ся функции многих микросхем. Главное, чему уделено внима-

ние — это применение микросхем для различных задач (причем

как стандартное применение, так и не стандартное), а также

приемы объединения, комбинирования микросхем, позволяю-

щие создавать разнообразные узлы, устройства и системы.

Материал данной книги представляет собой тот необходи-

мый минимум знаний, который должен иметь и которым дол-

Введение 11

жен свободно и активно пользоваться каждый профессиональ-

ный разработчик цифровой аппаратуры. Любые другие, допол-

нительные знания, конечно же, не повредят, но заменить собой

то, что изложено здесь, они не смогут.

Возможно, подход, предлагаемый в данной книге, несколько

отличается от общепринятого. Возможно также, что используе-

мый набор терминов не полностью совпадает со стандартным

(отечественные стандарты слишком часто меняются). Но глав-

ное — это научить проектировать цифровые устройства и сис-

темы, а какие для этого используются подходы и термины, на-

верное, не слишком принципиально.

Книга написана на основе многолетнего личного опыта ав-

тора по разработке цифровых устройств, а также на базе мате-

риала учебных курсов, читаемых автором, доцентом кафедры

электроники Московского инженерно-физического института

(МИФИ).

Несколько слов о структуре книги.

Первая глава рассматривает основополагающие принципы

цифровой электроники, знакомит с терминологией и основными

правилами оформления схем.

Главы со второй по шестую посвящены основным базовым

элементам цифровых устройств, типовым и нестандартным схе-

мам их включения. Практически все приведенные схемы прове-

рялись автором на практике. Микросхемы описаны начиная с

самых простейших логических элементов в порядке усложнения

через комбинационные микросхемы, триггеры, регистры, счет-

чики до микросхем памяти. Каждая глава включает в себя мно-

жество примеров включений микросхем, как рассматриваемых в

данной главе, так и рассмотренных в предыдущих главах.

Седьмая глава содержит краткие сведения о цифро-аналого-

вых и аналого-цифровых преобразователях и основных методах

их включения в аналого-цифровых устройствах. Без этих сведе-

ний книга была бы неполна.

В восьмой главе приводятся примеры нескольких сравни-

тельно сложных цифровых устройств с подробным описанием

всех этапов проектирования и принципов работы и взаимодей-

ствия всех узлов и микросхем. Цель этого не в том, чтобы чита-

тель повторил данные устройства, а в том, чтобы на практике

показать приемы проектирования, которые затем позволят стро-

ить любые другие цифровые устройства.

12 Введение

В приложении приведены таблицы параметров микросхем,

таблицы основных обозначений микросхем и сигналов, таблицы

соответствия отечественных и зарубежных микросхем. В конце

книги имеется подробный словарь терминов и сокращений циф-

ровой схемотехники.

В книгу не вошли материалы по основам микропроцессор-

ной техники, по принципам устройства и применения микро-

контроллеров и персональных компьютеров, по основам работы

с программируемыми микросхемами (ПЛИС), по методам кон-

троля и отладки цифровых устройств, а также по программным

средствам, предназначенным для проектирования цифровых

устройств и систем. Все эти вопросы планируется рассмотреть

в других книгах данной серии.

Глава 1

ФИЛОСОФИЯ

ЦИФРОВОЙ ЭЛЕКТРОНИКИ

Пусть не пугает читателя слово «философия» в названии главы.

В данном случае имеются в виду всего лишь главные принципы

цифровой электроники и обоснование ее преимуществ.

1.1. Аналог или цифра?

Для начала дадим несколько базовых определений.

Сигнал — это любая физическая величина (например, тем-

пература, давление воздуха, интенсивность света, сила тока

и т. д.), изменяющаяся со временем. Именно благодаря этому

изменению во времени сигнал может нести в себе какую-то ин-

формацию.

Электрический сигнал — это электрическая величина (на-

пример, напряжение, ток, мощность), изменяющаяся со време-

нем. Вся электроника в основном работает с электрическими

сигналами, хотя в последнее время все больше используются

световые сигналы, которые представляют собой изменяющуюся

во времени интенсивность света.

Аналоговый сигнал — это сигнал, который может прини-

мать любые значения в определенных пределах (например, на-

пряжение может плавно изменяться в пределах от нуля до деся-

ти вольт). Устройства, работающие только с аналоговыми сиг-

налами, называются аналоговыми устройствами.

Цифровой сигнал — это сигнал, который может принимать

только два значения (иногда — три значения). Причем разреше-

ны некоторые отклонения от этих значений (рис. 1.1). Напри-

мер, напряжение может принимать два значения: от 0 до 0,5 В

(уровень нуля) или от 2,5 до 5 В (уровень единицы). Устройства,

работающие исключительно с цифровыми сигналами, называ-

ются цифровыми устройствами.

14 Глава 1

В природе практически все сигналы аналоговые, то есть они

изменяются непрерывно в некоторых пределах. Именно поэто-

му первые электронные устройства были аналоговыми. Они

преобразовывали физические величины в пропорциональные им

напряжение или ток, выполняли над ними какие-то операции и

затем выполняли обратные преобразования в физические вели-

чины. Например, голос человека (колебания воздуха) с помощью

микрофона преобразуется в электрические колебания, затем эти

электрические сигналы усиливаются электронным усилителем и

с помощью акустической системы снова преобразуются в коле-

бания воздуха, в более сильный звук.

Рис. 1.1. Электрические сигналы: аналоговый (слева) и цифровой (справа).

Однако аналоговые сигналы и работающая с ними аналого-

вая электроника имеют большие недостатки, связанные именно

с природой аналоговых сигналов. Дело в том, что аналоговые

сигналы чувствительны к действию всевозможных паразитных

сигналов — шумов, наводок, помех. Шум — это внутренние

хаотические слабые сигналы любого электронного устройства

(микрофона, транзистора, резистора и т. д.). Наводки и поме-

хи — это сигналы, приходящие на электронную систему извне и

искажающие полезный сигнал (например, электромагнитные

излучения от радиопередатчиков или трансформаторов).

Все операции, производимые электронными устройства-

ми над сигналами, можно условно разделить на три большие

группы:

• обработка (или преобразование);

• передача;

• хранение.

Философия цифровой электроники 15

Во всех этих случаях полезные сигналы искажаются пара-

зитными сигналами — шумами, помехами, наводками. Кроме

того, при обработке сигналов (например, при усилении, фильт-

рации) еще искажается и их форма из-за несовершенст-

ва, неидеальности электронных устройств. А при передаче на

большие расстояния и при хранении сигналы к тому же ослаб-

ляются.

Сигнал

Наводка

*1...

Искаженный

сигнал

Рис. 1.2. Искажение шумами и наводками аналогового сигнала (слева) и циф-

рового сигнала (справа).

В случае аналоговых сигналов все это существенно ухуд-

шает полезный сигнал, так как все его значения разрешены

(рис. 1.2). Поэтому каждое преобразование, каждое промежу-

точное хранение, каждая передача по кабелю или эфиру ухуд-

шает аналоговый сигнал, иногда вплоть до его полного унич-

тожения. Надо еще учесть, что все шумы, помехи и наводки

принципиально не поддаются точному расчету, поэтому точно

описать поведение любых аналоговых устройств абсолютно не-

возможно. К тому же со временем параметры всех аналоговых

устройств изменяются из-за старения элементов, поэтому харак-

теристики этих устройств не остаются постоянными.

В отличие от аналоговых, цифровые сигналы, имеющие все-

го два разрешенных значения, защищены от действия шумов,

наводок и помех гораздо лучше. Небольшие отклонения от раз-

16 Глава 1

решенных значений никак не искажают цифровой сигнал, так

как всегда существуют зоны допустимых отклонений (рис. 1.2).

Именно поэтому цифровые сигналы допускают гораздо более

сложную и многоступенчатую обработку, гораздо более дли-

тельное хранение без потерь и гораздо более качественную

передачу, чем аналоговые. К тому же поведение цифровых

устройств всегда можно абсолютно точно рассчитать и пред-

сказать. Цифровые устройства гораздо меньше подвержены

старению, так как небольшое изменение их параметров никак

не отражается на их функционировании. Кроме того, цифро-

вые устройства проще проектировать и отлаживать. Понятно,

что все эти преимущества обеспечивают бурное развитие циф-

ровой электроники.

Однако у цифровых сигналов есть и крупный недостаток.

Дело в том, что на каждом из своих разрешенных уровней циф-

ровой сигнал должен оставаться хотя бы в течение какого-то

минимального временного интервала, иначе его невозможно

будет распознать. А аналоговый сигнал может принимать любое

свое значение бесконечно малое время. Можно сказать и иначе:

аналоговый сигнал определен в непрерывном времени (то есть в

любой момент времени), а цифровой — в дискретном времени

(то есть только в выделенные моменты времени). Поэтому мак-

симально достижимое быстродействие аналоговых устройств

всегда принципиально больше, чем цифровых устройств. Ана-

логовые устройства могут работать с более быстро меняющи-

мися сигналами, чем цифровые. Скорость обработки и передачи

информации аналоговым устройством всегда может быть сде-

лана выше, чем скорость ее обработки и передачи цифровым

устройством.

Кроме того, цифровой сигнал передает информацию только

двумя уровнями и изменением одного своего уровня на другой,

а аналоговый передает информацию еще и каждым текущим

значением своего уровня, то есть он более емкий с точки зрения

передачи информации. Поэтому для передачи того объема по-

лезной информации, который содержится в одном аналоговом

сигнале, чаще всего приходится использовать несколько цифро-

вых сигналов (обычно от 4 до 16).

К тому же, как уже отмечалось, в природе все сигналы ана-

логовые, то есть для преобразования их в цифровые сигналы и

для обратного преобразования требуется применение специаль-

Философия цифровой электроники 17

ной аппаратуры (аналого-цифровых и цифро-аналоговых преоб-

разователей). Так что ничто не дается даром, и плата за пре-

имущества цифровых устройств может порой оказаться непри-

емлемо большой.

1.2. Модели и уровни представления

цифровых устройств

Все цифровые устройства строятся из логических микросхем,

каждая из которых (рис. 1.3) обязательно имеет следующие вы-

воды (или, как их еще называют в просторечии, ножки):

• выводы питания: общий (или «земля») и напряжения пита-

ния (в большинстве случаев +5 В или +3,3 В), которые на

схемах обычно не показываются;

• выводы для входных сигналов (или «входы»), на которые

поступают внешние цифровые сигналы;

• выводы для выходных сигналов (или «выходы»), на кото-

рые выдаются цифровые сигналы из самой микросхемы.

А+5 В

Входы — — Выходы

J-Общий

Рис. 1.3. Цифровая микросхема.

Каждая микросхема преобразует тем или иным способом

последовательность входных сигналов в последовательность

выходных сигналов. Способ преобразования чаще всего описы-

вается или в виде таблицы (так называемой таблицы истинно-

сти) или в виде временных диаграмм, то есть графиков зависи-

мости от времени всех сигналов.

Все цифровые микросхемы работают с логическими сигна-

лами, имеющими два разрешенных уровня напряжения. Один из

этих уровней называется уровнем логической единицы (или

18 Глава 1

единичным уровнем), а другой — уровнем логического нуля

(или нулевым уровнем). Чаще всего логическому нулю соответ-

ствует низкий уровень напряжения, а логической единице —

высокий уровень напряжения. В этом случае говорят, что при-

нята «положительная логика». Однако при передаче сигналов на

большие расстояния и в системных шинах микропроцессорных

систем порой используют и обратное представление, когда ло-

гическому нулю соответствует низкий уровень напряжения, а

логической единице — высокий уровень. В этом случае говорят

об «отрицательной логике». Иногда логический нуль кодируется

положительным уровнем напряжения (тока), а логическая еди-

ница — отрицательным уровнем напряжения (тока) или наобо-

рот. Есть и более сложные методы кодирования логических ну-

лей и единиц. Но мы в основном будем говорить о положитель-

ной логике.

Для описания работы цифровых устройств используют са-

мые различные модели, отличающиеся друг от друга сложно-

стью, точностью, большим или меньшим учетом тонких физи-

ческих эффектов. В основном эти модели используются при

компьютерных расчетах цифровых схем. В настоящее время

существуют компьютерные программы, которые не только рас-

считывают готовые схемы, но способны и проектировать новые

схемы по формализованным описаниям функций, которые дан-

ное устройство должно выполнять. Это довольно удобно, но ни

одна программа никогда не может сравниться с человеком. По-

настоящему эффективные, оптимизированные по числу исполь-

зуемых аппаратурных модулей, наконец, красивые схемы может

разрабатывать только человек, который всегда подходит к про-

ектированию творчески и использует оригинальные идеи.

Разработчик цифровой аппаратуры тоже использует своеоб-

разные модели или, как еще можно сказать, различные уровни

представления цифровых схем. Но в отличие от компьютера че-

ловек может гибко выбирать нужную модель, ему надо только

взглянуть на схему, чтобы понять, где достаточно простейшей

модели, а где требуется более сложная. То есть человек никогда

не будет делать лишней, избыточной работы и, следовательно,

не будет вносить дополнительных ошибок, свойственных лю-

бой, даже самой сложной, модели. Правда, простота цифровых

устройств по сравнению с аналоговыми устройствами обычно

не дает возможности сделать чересчур серьезные ошибки.

Философия цифровой электроники 19

В подавляющем большинстве случаев разработчики цифро-

вых схем используют три модели, три уровня представления о

работе цифровых устройств.

1. Логическая модель.

2. Модель с временными задержками.

3. Модель с учетом электрических эффектов (или электри-

ческая модель).

Опыт показывает, что первая, простейшая модель оказыва-

ется достаточной примерно в 20% всех случаев. Она применима

для всех цифровых схем, работающих с низкой скоростью, в ко-

торых быстродействие не принципиально. Привлечение второй

модели, учитывающей задержки срабатывания логических эле-

ментов, позволяет охватить около 80% всех возможных схем. Ее

применение необходимо для всех быстродействующих устройств

и в случае одновременного изменения нескольких входных

сигналов. Наконец, добавление третьей модели, учитывающей

входные и выходные токи, входные и выходные сопротивления

и емкости элементов, позволяет проектировать практически

100% цифровых схем. В первую очередь эту третью модель на-

до применять при объединении нескольких входов и выходов,

при передаче сигналов на большие расстояния и при нетрадици-

онном включении логических элементов (с переводом их в ана-

логовый, в линейный режим).

Таблица 1.1. Таблица истинности инвертора

Вход Выход

0 1

1 0

Для иллюстрации работы перечисленных моделей рассмот-

рим работу самого простейшего логического элемента — ин-

вертора. Инвертор изменяет (инвертирует) логический уровень

входного сигнала на противоположный уровень выходного сиг-

нала или, как еще говорят, изменяет полярность логического

сигнала. Таблица истинности инвертора (табл. 1.1) элементарно

проста, так как возможны только две ситуации: нуль на входе

или единица на входе. На рис. 1.4 показано, как будет выглядеть

выходной сигнал инвертора при использовании трех его моде-

20 Глава 1

лей (трех уровней его представления). Такие графики логиче-

ских сигналов называются временными диаграммами, они по-

зволяют лучше понять работу цифровых схем.

Инвертор

3

Рис. 1.4. Три уровня представления цифровых устройств.

1

Из рисунка видно, что в первой, логической, модели счита-

ется, что элемент срабатывает мгновенно, любое изменение

уровня входного сигнала сразу же, без всякой задержки приво-

дит к изменению уровня выходного сигнала. Во второй модели

выходной сигнал изменяется с некоторой задержкой относи-

тельно входного. Наконец, в третьей модели выходной сигнал

не только задерживается по сравнению с входным, но и его из-

менение происходит не мгновенно, процесс смены уровней сиг-

нала (или, как говорят, фронт сигнала) имеет конечную дли-

тельность. Кроме того, третья модель учитывает изменение

уровней логических сигналов.

На практике разработчик, как правило, в начале проектиро-

вания пользуется исключительно первой моделью, а затем для

некоторых узлов применяет вторую модель или (реже) еще и

третью модель. При этом первая модель не требует вообще ни-

каких цифровых расчетов, для нее достаточно только знание

таблиц истинности или алгоритмов функционирования микро-

схем. Вторая модель предполагает расчет (по сути, суммирова-

ние) временных задержек элементов на пути прохождения сиг-

налов (рис. 1.5). В результате этого расчета может выясниться,

что в схему нужно внести изменения.

Расчеты по третьей модели могут быть различными, в том

числе и довольно сложными, но в большинстве случаев они все-

таки сводятся всего лишь к суммированию входных и выход-

ных токов логических элементов (рис. 1.6). В результате этих

Философия цифровой электроники 21

расчетов может выясниться, что требуется применение микро-

схем с более мощными выходами или включение дополни-

тельных элементов.

t-зад 1зад 2^-^'Зад з^-^зад 4

Рис. 1.5. Суммирование задержек элементов.

Рис. 1.6. Суммирование входных токов элементов.

Таким образом, проектирование цифровых устройств прин-

ципиально отличается от проектирования аналоговых уст-

ройств, при котором сложные расчеты абсолютно неизбежны.

Разработчик цифровых устройств имеет дело только с логикой,

с логическими сигналами и с алгоритмами работы цифровых

микросхем. А что происходит внутри этих микросхем, для него

практически не имеет значения.

Справочные данные на цифровые микросхемы обычно со-

держат большой набор параметров, каждый из которых можно

отнести к одному из трех перечисленных уровней представле-

ния, к одной из трех моделей.

Например, таблица истинности микросхемы (для простых

микросхем) или описание алгоритма ее работы (для более

сложных микросхем) относится к первому, логическому уров-

ню. Поэтому знать их наизусть каждому разработчику необхо-

димо в любом случае.

22 Глава 1

Величины задержек логических сигналов между входами и

выходами относятся ко второму уровню представления. Типич-

ные величины задержек составляют от единиц наносекунд

(1 нс = 10“9 с) до десятков наносекунд. Величины задержек для

разных микросхем могут быть различными, поэтому в справоч-

никах всегда указывается максимальное значение задержки. Не-

обходимо также помнить, что задержка при переходе выходного

сигнала из единицы в нуль (1рнь), как правило, отличается от за-

держки при переходе выходного сигнала из нуля в единицу

(fpm). Например, для одной и той же микросхемы tPLH < 11 нс,

atpHL < 8 нс. Здесь английская буква Р означает Propagation

(распространение), L означает Low (низкий уровень сигнала,

нуль), а Н — High (высокий уровень сигнала, единица). Количе-

ство величин задержек, определяемых справочником для мик-

росхемы, может изменяться от двух до нескольких десятков.

Уровни входных и выходных токов, а также уровни входных

и выходных напряжений относятся к третьему уровню пред-

ставления.

Входной ток микросхемы при приходе на вход логического

нуля (III), как правило, отличается от входного тока при приходе

на вход логической единицы (1ш). Например, Ijl = —0,1 мА, а

1[н = 20 мкА (считается, что положительный ток втекает во вход

микросхемы, а отрицательный — вытекает из него). Точно так

же выходной ток микросхемы при выдаче логического нуля

(Iol) может отличаться (и обычно отличается) от выходного то-

ка при выдаче логической единицы (Iqh)- Например, для одной и

той же микросхемы Iqh < —0,4 мА, a Iql < 8 мА (считается, что

положительный ток втекает в выход микросхемы, а отрицатель-

ный — вытекает из него). Надо также учитывать, что разные

входы и выходы одной и той же микросхемы могут иметь раз-

личные входные и выходные токи.

Для выходных напряжений логического нуля (Uol) и едини-

цы (Uoh) в справочниках обычно задаются предельно допусти-

мые значения при заданной величине выходного тока. При этом

чем больше выходной ток, тем меньше напряжение логической

единицы и тем больше напряжение логического нуля. Напри-

мер, Uoh > 2,5 В (при Iqh < —0,4 мА), a Uol < 0,5 В (при

Iql < 8 мА).

Задаются в справочниках также и допустимые уровни вход-

ных напряжений, которые микросхема еще воспринимает как

Философия цифровой электроники 23

правильные логические уровни нуля и единицы. Например,

ига > 2,0 В, Uil < 0,8 В. Как правило, входные напряжения логи-

ческих сигналов не должны выходить за пределы напряжения

питания.

В обозначениях напряжений и токов буква I означает Input

(вход), буква О означает Output (выход), L — Low (нуль), а Н —

High (единица).

К третьему уровню представления относятся также величи-

ны внутренней емкости входов микросхемы (обычно от единиц

до десятков пикофарад) и допустимая величина емкости, к ко-

торой может подключаться выход микросхемы, то есть емкость

нагрузки Cl (порядка 100 пФ). Отметим, что 1 пФ = 10”12 Ф.

На этом же уровне представления задаются максимально допус-

тимые величины длительности положительного фронта (tm)

и отрицательного фронта (tHL) входного сигнала, например

Ihl < 1,0 мкс, tm < 1,0 мкс. То есть при большей длительности

перехода входного сигнала из единицы в нуль и из нуля в еди-

ницу микросхема может работать неустойчиво, неправильно,

нестандартно.

К третьему уровню представления можно отнести также та-

кие параметры, как допустимое напряжение питания микросхе-

мы (Ucc) и максимальный ток, потребляемый микросхемой

(1сс). Например, может быть задано:

4,5 В < Ucc < 5,5 В; Ice < 100 мА.

При этом потребляемый ток Ice зависит от уровней выход-

ных токов микросхемы Iqh и Iql- Эти параметры надо учитывать

при выборе источника питания для проектируемого устройства,

а также в процессе изготовления печатных плат при выборе ши-

рины токоведущих дорожек.

Наконец, к третьему уровню относится ряд параметров, ко-

торые часто упоминаются в литературе, но не всегда приводятся

в справочных таблицах:

• Порог срабатывания — уровень входного напряжения,

выше которого сигнал воспринимается как единица, а ни-

же — как нуль. Для наиболее распространенных ТТЛ мик-

росхем он примерно равен 1,3... 1,4 В.

24 Глава 1

• Помехозащищенность — параметр, характеризующий ве-

личину входного сигнала помехи, накладывающегося на

входной сигнал, который еще не может изменить состоя-

ние выходных сигналов. Помехозащищенность определя-

ется разницей между напряжением Um и порогом срабаты-

вания (это помехозащищенность единичного уровня), а

также разницей между порогом срабатывания и Un. (это

помехозащищенность нулевого уровня).

• Коэффициент разветвления — число входов, которое мо-

жет быть подключено к данному выходу без нарушения

работы. Этот параметр определяется отношением выход-

ного тока к входному. Стандартная величина коэффициен-

та разветвления при использовании микросхем одного ти-

па (одной серии) равна 10.

• Нагрузочная способность — параметр выхода, характери-

зующий величину выходного тока, которую может выдать

в нагрузку данный выход без нарушения работы. Чаще

всего нагрузочная способность прямо связана с коэффици-

ентом разветвления.

Таким образом, большинство справочных параметров мик-

росхемы относятся к третьему уровню представления (к модели

с учетом электрических эффектов), поэтому в большинстве слу-

чаев (до 80%) знать их точные значения наизусть не обязатель-

но. Достаточно знать примерные типовые значения параметров

для данной серии микросхем.

1.3. Входы и выходы цифровых микросхем

Характеристики и параметры входов и выходов цифровых мик-

росхем определяются прежде всего технологией и схемотехни-

кой внутреннего строения микросхем. Но для разработчика

цифровых устройств любая микросхема представляет собой

всего лишь «черный ящик», внутренности которого знать не

обязательно. Ему важно только четко представлять себе, как по-

ведет себя та или иная микросхема в данном конкретном вклю-

чении, будет ли она правильно выполнять требуемую от нее

функцию.

Философия цифровой электроники 25

Наибольшее распространение получили две технологии циф-

ровых микросхем:

• ТТЛ (TTL) и ТТЛШ (TTLS) — биполярная транзисторно-

транзисторная логика и ТТЛ с диодами Шоттки;

• КМОП (CMOS) — комплементарные транзисторы со

структурой «металл-окисел-полупроводник».

Рис. 1.7. Входной и выходной каскады микросхем ТТЛШ.

Рис. 1.8. Входной и выходной каскады микросхем КМОП.

Различаются они типами используемых транзисторов и схе-

мотехническими решениями внутренних каскадов микросхем.

Отметим также, что микросхемы КМОП потребляют значитель-

но меньший ток от источника питания, чем такие же микросхе-

мы ТТЛ (или ТТЛШ), правда, только в статическом режиме или

на небольших рабочих частотах. На рис. 1.7 и 1.8 показаны

26 Глава 1

примеры схем входных и выходных каскадов микросхем, вы-

полненных по этим технологиям. Понятно, что точный учет

всех эффектов в этих схемах, включающих в себя множество

транзисторов, диодов и резисторов, крайне сложен, но обычно

он просто не нужен разработчику цифровых схем.

Рассмотрим сначала входы микросхем.

На первом уровне представления (логическая модель) и на

втором уровне представления (модель с временными задержка-

ми) о входах микросхем вообще ничего знать не надо. Вход рас-

сматривается как бесконечно большое сопротивление, никак не

влияющее на подключенные к нему выходы. Правда, количест-

во входов, подключаемых к одному выходу, влияет на задержку

распространения сигнала, но, как правило, незначительно, по-

этому это влияние учитывается редко.

Даже на третьем уровне представления (электрическая мо-

дель) в большинстве случаев не надо знать о внутреннем строе-

нии микросхемы, о схемотехнике входов. Достаточно считать,

что при подаче на вход сигнала логического нуля из этого входа

вытекает ток, не превышающий Iil, а при подаче сигнала логи-

ческой единицы в этот вход втекает ток, не превышающий 1щ.

А для правильной логики работы микросхемы достаточно, что-

бы уровень напряжения входного сигнала логического нуля был

меньше Uil, а уровень напряжения входного сигнала логической

единицы был больше Um-

Особым случаем является ситуация, когда какой-нибудь

вход не подключен ни к одному из выходов, ни к общему про-

воду, ни к шине питания (так называемый висящий вход). Ино-

гда возможности микросхемы используются не полностью, и на

некоторые входы не подаются сигналы. Однако при этом мик-

росхема может не работать или работать нестабильно, так как ее

правильное включение подразумевает наличие на всех входах

логических уровней, пусть даже и неизменных. Поэтому реко-

мендуется подавать на неиспользуемые входы напряжение пи-

тания микросхемы Ucc или подключать их к общему проводу

(земле) в зависимости от того, какой логический уровень не-

обходим на этом входе. Но для некоторых серий микросхем,

выполненных по технологии ТТЛ (например, К155 или КР531),

неиспользуемые входы надо подключать к шине питания не

прямо, а только через резистор величиной около 1 кОм (доста-

точно одного резистора на 20 входов).

Философия цифровой электроники 27

На неподключенных входах микросхем ТТЛ формируется

напряжение около 1,5—1,6 В, которое иногда называют висячим

потенциалом. Обычно этот уровень воспринимается микросхе-

мой как сигнал логической единицы, но надеяться на это не

стоит. Потенциал, образующийся на неподключенных входах

микросхем КМОП, может восприниматься микросхемой и как

логический нуль, и как логическая единица. В любом случае все

входы надо куда-то подключать. Неподключенными допускает-

ся оставлять только те входы (ТТЛ, а не КМОП), состояние ко-

торых в данном включении микросхемы не имеет значения.

Выходы микросхем принципиально отличаются от входов

тем, что учет их особенностей необходим даже на первом и вто-

ром уровнях представления.

Существуют три разновидности выходных каскадов, суще-

ственно различающихся как по своим характеристикам, так и по

областям применения:

• стандартный выход или выход с двумя состояниями (обо-

значается 2С, 2S или, реже, ТТЛ, TTL);

• выход с открытым коллектором (обозначается ОК, ОС);

• выход с тремя состояниями или (что то же самое) с воз-

можностью отключения (обозначается ЗС, 3S).

Стандартный выход 2С имеет всего два состояния: логиче-

ский нуль и логическую единицу, причем оба этих состояния

активны, то есть выходные токи в обоих этих состояниях (Iql и

1он) могут достигать заметных величин. На первом и втором

уровнях представления такой выход можно считать состоящим

из двух выключателей, которые замыкаются по очереди

(рис. 1.9), причем замкнутому верхнему выключателю соответ-

ствует логическая единица на выходе, а замкнутому нижнему —

логический нуль.

Выход с открытым коллектором ОК тоже имеет два воз-

можных состояния, но только одно из них (состояние логиче-

ского нуля) активно, то есть обеспечивает большой втекающий

ток Iql. Второе состояние сводится, по сути, к тому, что выход

полностью отключается от присоединенных к нему входов. Это

состояние может использоваться в качестве логической едини-

цы, но для этого между выходом ОК и напряжением питания

необходимо подключить нагрузочный резистор R (так называв-

28 Глава 1

мый pull-up) величиной порядка сотен Ом. На первом и втором

уровнях представления такой выход можно считать состоящим

из одного выключателя (рис. 1.9), замкнутому состоянию кото-

рого соответствует сигнал логического нуля, а разомкнутому —

отключенное, пассивное состояние. Правда, от величины рези-

стора R зависит время переключения выхода из нуля в единицу,

что влияет на задержку tm, но при обычно используемых номи-

налах резисторов это не слишком важно.

Рис. 1.9. Три типа выходов цифровых микросхем.

Наконец, выход с тремя состояниями ЗС очень похож на

стандартный выход, но к двум состояниям добавляется еще и

третье — пассивное, в котором выход можно считать отклю-

ченным от последующей схемы. На первом и втором уровнях

представления такой выход можно считать состоящим из двух

переключателей (рис. 1.9), которые могут замыкаться по очере-

ди, давая логический нуль и логическую единицу, но могут и

размыкаться одновременно. Это третье состояние называется

также высокоимпедансным или Z-состоянием. Для перевода

выхода в третье Z-состояние используется специальный управ-

ляющий вход, обозначаемый ОЕ (Output Enable — разрешение

выхода) или EZ (Enable Z-state — разрешение Z-состояния, или

третьего состояния).

Почему же помимо стандартного выхода (2С) были предло-

жены еще два типа выходов (ОК и ЗС)? Дело в том, что выходы,

имеющие помимо активных состояний еще и пассивное состоя-

ние, очень удобны для объединения их между собой. Например,

если на один и тот же вход надо по очереди подавать сигналы с

двух выходов (рис. 1.10), то выходы 2С для этого не подходят, а

вот выходы ОК и ЗС подходят.

Философия цифровой электроники 29

Рис. 1.10. Объединение выходов цифровых микросхем.

При объединении двух или более выходов 2С вполне воз-

можна ситуация, при которой один выход стремится выдать

сигнал логической единицы, а другой — сигнал логического

нуля. Легко заметить, что в этом случае через верхний замкну-

тый ключ выхода, выдающего единицу, и через нижний замкну-

тый ключ выхода, выдающего нуль, пойдет недопустимо боль-

шой ток короткого замыкания 1Ю. Это аварийная ситуация, при

которой уровень получаемого выходного логического сигнала

точно не определен, он может восприниматься последующим

входом и как нуль, и как единица. Конфликтующие выходы мо-

гут даже выйти из строя, нарушив работу микросхем и схемы в

целом.

Зато в случае объединения двух выходов ОК такого кон-

фликта в принципе произойти не может. Даже если ключ одного

выхода замкнут, а другого разомкнут, аварийной ситуации не

произойдет, так как недопустимо большого тока не будет, а на

объединенном выходе будет сигнал логического нуля. А при

объединении двух выходов ЗС аварийная ситуация хотя и воз-

можна (если оба выхода одновременно находятся в активном

состоянии), но ее легко можно предотвратить, если организо-

вать схему так, что в активном состоянии всегда будет нахо-

диться только один из объединенных выходов ЗС.

30 Глава 1

Объединение выходов цифровых микросхем совершенно

необходимо также при шинной (или, как еще говорят, магист-

ральной) организации связей между цифровыми устройствами.

Шинная организация связей применяется, например, в компью-

терах, других микропроцессорных системах. Суть ее сводится к

следующему.

Устройство 1 V Устройство 2

Устройство 3 » Устройство 4

Рис. 1.11. Классическая организация связей.

При классической организации связей (рис. 1.11) все сигна-

лы между устройствами передаются по своим отдельным лини-

ям (проводам). Каждое устройство передает свои сигналы всем

другим устройствам независимо от других устройств. В этом

случае обычно получается очень много линий связи, к тому же

правила обмена сигналами по этим линия (или протоколы обме-

на) чрезвычайно разнообразны.

При шинной организации связей (рис. 1.12) все сигналы ме-

жду устройствами передаются по одним и тем же линиям (про-

водам), но в разные моменты времени (это называется времен-

ным мультиплексированием). В результате количество линий

Философия цифровой электроники 31

связи резко сокращается, а правила обмена сигналами сущест-

венно упрощаются. Группа линий (сигналов), используемая не-

сколькими устройствами, как раз и называется шиной. Понятно,

что объединение выходов в этом случае совершенно необходи-

мо, ведь каждое устройство должно иметь возможность выда-

вать свой сигнал на общую линию. К недостаткам шинной орга-

низации относится прежде всего невысокая (по сравнению с

классической структурой связей) скорость обмена сигналами.

При простых структурах связи шинная организация может быть

избыточна.

Но вернемся к типам выходов цифровых микросхем.

На третьем уровне представления (электрическая модель)

необходимо уже учитывать, что выходные ключи (рис. 1.9)

представляют собой не простые тумблеры (как на первых двух

уровнях представления), а транзисторные ключи со своими спе-

цифическими параметрами. Однако в большинстве случаев дос-

таточно знать, какой ток может выдать данный выход в состоя-

ниях логического нуля (Iol) и логической единицы (1он). Вели-

чины этих токов не должны превышать суммы токов всех вхо-

дов, подключенных к данному выходу (соответственно 1ц, и 1щ).

Количество входов, которое можно подключить к одному выхо-

ду, определяет коэффициент разветвления или нагрузочную

способность микросхемы. Существуют микросхемы с обычной

нагрузочной способностью и с повышенной нагрузочной спо-

собностью (больше обычной в два раза и более). Выходы ЗС,

как правило, имеют повышенную нагрузочную способность (то

есть обеспечивают большие выходные токи). Выходы 2С и ОК

могут быть как с обычной, так и с повышенной нагрузочной

способностью.

На третьем уровне представления (электрическая модель)

необходимо также учитывать выдаваемые выходом микросхемы

величины выходных напряжений Uol и Uoh- Выходы ОК могут

быть рассчитаны как на обычное выходное напряжение логиче-

ской единицы (Uoh = Ucc = 5 В), так и на повышенное напряже-

ние логической единицы (до 30 В). В последнем случае внеш-

ний резистор этого выхода (см. рис. 1.9) подключается к источ-

нику повышенного напряжения.

Только в сложных случаях, например при переводе логиче-

ского элемента в линейный режим за счет обратных связей, ну-

жен учет других параметров входных и выходных каскадов. Но

32 Г лава 1

в этих редких случаях гораздо проще и надежнее не считать ни-

чего самому, а воспользоваться стандартными схемами включе-

ния микросхем или подобрать режимы работы и номиналы

внешних элементов (резисторов, конденсаторов) непосредст-

венно на макете проектируемого устройства. В отличие от рас-

четов такой подход даст полную гарантию работоспособности

выбранного решения.

1.4. Основные обозначения на схемах

Для изображения электронных устройств и их узлов применяет-

ся три основных типа схем:

• принципиальная схема;

• структурная схема;

• функциональная схема.

Различаются эти три вида схем своим назначением и, самое

главное, степенью детализации изображения устройств.

Принципиальная схема — это наиболее подробная схема.

Она обязательно показывает все использованные в устройстве

элементы и все связи между ними. Если схема строится на ос-

нове микросхем, то должны быть показаны номера выводов

всех входов и выходов этих микросхем. Принципиальная схема

должна позволять полностью воспроизвести устройство. Обо-

значения принципиальной схемы наиболее жестко стандартизо-

ваны, отклонения от стандартов не рекомендуются.

Структурная схема — это наименее подробная схема. Она

предназначена для отображения общей структуры устройства,

то есть его основных блоков, узлов, частей и главных связей

между ними. Из структурной схемы должно быть понятно, за-

чем нужно данное устройство, и что оно делает в основных ре-

жимах работы, как взаимодействуют его части. Обозначения

структурной схемы могут быть довольно произвольными, хотя

некоторые общепринятые правила все-таки лучше выполнять.

Функциональная схема представляет собой гибрид струк-

турной и принципиальной схем. Некоторые наиболее простые

блоки, узлы, части устройства отображаются на ней, как на

структурной схеме, а остальные — как на принципиальной схе-

ме. Функциональная схема позволяет понять всю логику работы

устройства, все его отличия от других подобных устройств, но

Философия цифровой электроники 33

не позволяет без дополнительной самостоятельной работы вос-

произвести это устройство. Что касается обозначений, исполь-

зуемых на функциональных схемах, то в части, показанной как

структура, они не стандартизованы, а в части, показанной, как

принципиальная схема, они стандартизованы.

В технической документации обязательно приводится струк-

турная или функциональная схема, а также обязательно прин-

ципиальная схема. В научных статьях и книгах чаще всего огра-

ничиваются структурной или функциональной схемой, приводя

принципиальные схемы только некоторых узлов.

А теперь рассмотрим основные обозначения, используемые

на схемах.

Все узлы, блоки, части, элементы, микросхемы показывают-

ся в виде прямоугольников с соответствующими надписями. Все

связи между ними, все передаваемые сигналы показываются в

виде линий, соединяющих эти прямоугольники. Входы и вхо-

ды/выходы должны быть расположены на левой стороне прямо-

угольника, выходы — на правой стороне, хотя это правило часто

нарушают, когда необходимо упростить рисунок схемы. Выводы

и связи питания, как правило, не показывают, если, конечно, не

используются нестандартные включения элементов схемы. Это

самые общие правила, касающиеся любых схем.

Прежде чем перейти к более частным правилам, надо дать

несколько определений.

Положительный сигнал (сигнал положительной полярнос-

ти)— это сигнал, активный уровень которого — логическая

единица, то есть: нуль — это отсутствие сигнала, единица —

сигнал пришел (рис. 1.13).

Положительный сигнал

пассивный /активный \

(нулевой) /(единичный)\

уровень / уровень \

передний задний

(положительный) (отрицательный)

фронт фронт

Отрицательный сигнал

(отрицательный) (положительный)

фронт фронт

Рис. 1.13. Элементы цифрового сигнала.

2 - 4589

34 Глава 1

Отрицательный сигнал (сигнал отрицательной полярнос-

ти)— это сигнал, активный уровень которого — логический

нуль, то есть: единица — это отсутствие сигнала, нуль — сигнал

пришел (рис. 1.13).

Активный уровень сигнала — это уровень, соответствую-

щий приходу сигнала, то есть выполнению этим сигналом соот-

ветствующей ему функции.

Пассивный уровень сигнала — это уровень, в котором сиг-

нал не выполняет никакой функции.

Инвертирование или инверсия сигнала — это изменение

его полярности.

Инверсный выход — это выход, выдающий сигнал инверс-

ной полярности по сравнению с входным сигналом.

Прямой выход — это выход, выдающий сигнал такой же

полярности, какую имеет входной сигнал.

Положительный фронт сигнала — это переход сигнала из

нуля в единицу.

Отрицательный фронт сигнала (спад) — это переход сиг-

нала из единицы в нуль.

Передний фронт сигнала — это переход сигнала из пас-

сивного уровня в активный уровень.

Задний фронт сигнала — это переход сигнала из активного

уровня в пассивный уровень.

Тактовый сигнал (или строб) — управляющий сигнал, ко-

торый определяет момент выполнения элементом или узлом его

функции.

Шина — группа сигналов (и соответствующих физических

линий передачи этих сигналов), объединенных по какому-то

принципу. Например, шиной называют сигналы, соответствую-

щие всем разрядам какого-то двоичного кода.

Для обозначения полярности сигнала на схемах использует-

ся простое правило: если сигнал отрицательный, то перед его

названием ставится знак минус, например, —WR или —ОЕ, или

же (реже) над названием сигнала ставится черта. Если таких

знаков нет, то сигнал считается положительным. Для названий

сигналов обычно используются латинские буквы, представляю-

щие собой сокращения английских слов. Например, WR — сиг-

нал записи (от Write — писать).

Философия цифровой электроники 35

Инверсия сигнала обозначается кружочком на месте входа

или выхода. Существуют инверсные входы и инверсные выходы

(рис. 1.14).

Если какая-то микросхема выполняет функцию по фронту

входного сигнала, то на месте входа ставится косая черта (под

углом 45°), причем наклон вправо или влево определяется тем,

какой фронт — положительный или отрицательный — исполь-

зуется в данном случае (рис. 1.14).

Вход, работающий

по отрицательному фронту

Рис. 1.14. Обозначение входов и выходов.

Тип выхода микросхемы помечается специальным значком:

выход ЗС — перечеркнутым ромбом, а выход ОК — подчеркну-

тым ромбом (рис. 1.14). Стандартный выход (2С) никак не по-

мечается.

Наконец, если у микросхемы необходимо показать неин-

формационные выводы, то есть выводы, не являющиеся ни ло-

гическими входами, ни логическими выходами, то такой вывод

помечается косым крестом (две перпендикулярные линии под

углом 45°). Это могут быть, например, выводы для подключе-

ния внешних элементов (резисторов, конденсаторов) или выво-

ды питания (рис. 1.15).

В схемах также предусматриваются специальные обозначе-

ния для шин (рис. 1.16). На структурных и функциональных

схемах шины обозначаются толстыми линиями или двойными

стрелками, причем количество сигналов, входящих в шину, ука-

зывается рядом с косой чертой, пересекающей шину. На прин-

2*

36 Глава 1

ципиальных схемах шина тоже обозначается толстой линией, а

входящие в шину и выходящие из шины сигналы показываются

в виде перпендикулярных к шине тонких линий с указанием их

номера или названия (рис. 1.16). При передаче по шине двоич-

ного кода нумерация начинается с младшего разряда кода.

Ucc

0V

При изображении микросхем используются сокращенные

названия входных и выходных сигналов, отражающие их функ-

цию. Эти названия располагаются на рисунке рядом с соответ-

ствующим выводом. Также на изображении микросхем указы-

вается выполняемая ими функция (обычно в центре вверху).

Изображение микросхемы иногда делят на три вертикальных

поля. Левое поле относится к входным сигналам, правое — к

выходным сигналам. В центральном поле помещаются название

микросхемы и символы ее особенностей. Неинформационные

выводы могут указываться как на левом, так и на правом поле,

иногда их показывают на верхней или нижней стороне прямо-

угольника, изображающего микросхему.

В табл. 1.2 приведены некоторые наиболее часто встречаю-

щиеся обозначения сигналов и функций микросхем. Микросхе-

ма в целом обозначается на схемах буквами DD (от английского

Digital — цифровой) с соответствующим номером, например

DD1, DD20.1, DD38.2 (после точки указывается номер элемента

или узла внутри микросхемы).

Философия цифровой электроники 37

Таблица 1.2. Некоторые обозначения сигналов и микросхем

Обозначение Название Назначение

& And Элемент И

=1 Exclusive Or Элемент Исключающее ИЛИ

1 Or Элемент ИЛИ

А Address Адресные разряды

BF Buffer Буфер

С Clock Тактовый сигнал (строб)

СЕ Clock Enable Разрешение тактового сигнала

ст Counter Счетчик

CS Chip Select Выбор микросхемы

D Data Разряды данных, данные

DC Decoder Дешифратор

EZ Enable Z-state Разрешение третьего состояния

G Generator Генератор

I Input Вход

I/O Input/Output Вход/Выход

ОЕ Output Enable Разрешение выхода

MS Multiplexer Мультиплексор

Q Quit Выход

R Reset Сброс (установка в нуль)

RG Register Регистр

S Set Установка в единицу

SUM Summator Сумматор

Т Trigger Триггер

ТС Terminal Count Окончание счета

Z Z-state Третье состояние выхода

Более полная таблица обозначений сигналов и микросхем, ис-

пользуемых в принципиальных схемах, приведена в Приложении.

1.5. Серии цифровых микросхем

В настоящее время выпускается огромное количество разнооб-

разных цифровых микросхем от простейших логических элемен-

тов до сложнейших процессоров, микроконтроллеров и специа-

лизированных БИС (больших интегральных микросхем). Выпус-

ком цифровых микросхем занимается множество фирм как у нас

38 Глава 1

в стране, так и за рубежом. Поэтому даже классификация этих

микросхем представляет собой довольно трудную задачу.

Однако в качестве базиса в цифровой схемотехнике принято

рассматривать классический набор микросхем малой и средней

степени интеграции, в основе которого лежат ТТЛ серии семейства

74, выпускаемые уже несколько десятилетий рядом фирм, напри-

мер американской фирмой Texas Instruments (ТП). Эти серии вклю-

чают в себя функционально полный комплект микросхем, исполь-

зуя который можно создавать самые разные цифровые устройства.

Даже при компьютерном проектировании современных сложных

микросхем с программируемой логикой (ПЛИС) применяются мо-

дели простейших микросхем этих серий семейства 74. При этом

разработчик рисует на экране компьютера схему в привычном для

него элементном базисе, а затем программа создает прошивку

ПЛИС, выполняющую требуемую функцию.

Каждая микросхема серий семейства 74 имеет свое обозна-

чение, и система обозначений отечественных серий существен-

но отличается от принятой за рубежом.

S^N '4 LS

Идентификатор

фирмы

XX XXX NT

Код типа

корпуса

Температурный

диапазон (семейство)

Код серии

Тип микросхемы

Идентификатор

специального типа

Рис. 1.17. Система обозначений фирмы Texas Instruments.

В качестве примера рассмотрим систему обозначений фир-

мы Texas Instruments (рис. 1.17). Полное обозначение состоит из

шести элементов:

1. Идентификатор фирмы SN (для серий АС и ACT отсутствует).

2. Температурный диапазон (тип семейства):

• 74 — коммерческие микросхемы (температура окружаю-

щей среды для биполярных микросхем — О...7О°С, для

КМОП микросхем--------40...+85°C),

• 54 — микросхемы военного назначения (температура ок-

ружающей среды--------55...+125°С).

Философия цифровой электроники 39

3. Код серии (до трех символов):

• Отсутствует — стандартная ТТЛ серия.

• LS (Low Power Schottky) — маломощная серия ТТЛШ.

• S (Schottky) — серия ТТЛШ.

• ALS (Advanced Schottky) — улучшенная серия ТТЛШ.

• F (FAST) — быстрая серия.

• НС (High Speed CMOS) — высокоскоростная КМОП серия.

• НСТ (High Speed CMOS with TTL inputs) — серия НС, сов-

местимая по входу с ТТЛ.

• AC (Advanced CMOS) — улучшенная серия КМОП.

• ACT (Advanced CMOS with TTL inputs) — серия AC, сов-

местимая по входу с ТТЛ.

• В CT (BiCMOS Technology) — серия с БиКМОП техноло-

гией.

• ABT (Advanced BiCMOS Technology) — улучшенная серия

с БиКМОП технологией.

• LVT (Low Voltage Technology) — серия с низким напря-

жением питания.

4. Идентификатор специального типа (2 символа) — может от-

сутствовать.

5. Тип микросхемы (от двух до шести цифр). Перечень некото-

рых типов микросхем приведен в Приложении.

6. Код типа корпуса (от одного до двух символов) — может от-

сутствовать. Например, N — пластмассовый корпус DIL

(DIP), J — керамический корпус DIL (DIC), Т — плоский

металлический корпус.

Примеры обозначений: SN74ALS373, SN74ACT7801, SN7400.

Отечественная система обозначений микросхем отличается

от рассмотренной довольно существенно (рис. 1.18). Основные

элементы обозначения следующие:

1. Буква К обозначает микросхемы широкого применения, для

микросхем военного назначения буква отсутствует.

2. Тип корпуса микросхемы (один символ) — может отсутство-

вать. Например, Р — пластмассовый корпус, М — керамиче-

ский корпус, Б — бескорпусная микросхема.

3. Номер серии микросхем (от трех до четырех цифр).

4. Функция микросхемы (две буквы).

40 Глава 1

X хххх

Область

применения

Тип корпуса

Номер серии

5. Номер микросхемы (от одной до трех цифр). Таблица функ-

ций и номеров микросхем, а также таблица их соответствия

зарубежным аналогам приведены в Приложении.

XX Х^Х

Номер микросхемы

Функция микросхемы

Рис. 1.18. Обозначения отечественных микросхем.

Примеры обозначений: KP1533JIA3, КМ531ИЕ17, КР1554ИР47.

Главное достоинство отечественной системы обозначений

состоит в том, что по обозначению микросхемы можно легко

понять ее функцию. Зато в системе обозначений Texas Instru-

ments виден тип серии с его особенностями.

Чем отличается одна серия от другой?

На первом уровне представления (логическая модель) серии

не различаются ничем. То есть одинаковые микросхемы разных

серий работают по одним и тем же таблицам истинности, по од-

ним и тем же алгоритмам. Правда, надо учитывать, что некото-

рые микросхемы имеются только в одной из серий, а некоторых

нет в нескольких сериях.

На втором уровне представления (модель с учетом задер-

жек) серии отличаются величиной задержки распространения

сигнала. Это различие может быть довольно существенным. По-

этому в тех схемах, где величина задержки принципиальна, надо

использовать микросхемы более быстрых серий (табл. 1.3).

На третьем уровне представления (электрическая модель) серии

различаются величинами входных и выходных токов и напряже-

ний, а также, что не менее важно, токами потребления (табл. 1.3).

Поэтому в тех устройствах, где эти параметры принципиальны,

надо применять микросхемы, обеспечивающие, например, низкие

входные токи, высокие выходные токи и малое потребление.

Серия К155 (SN74) — это наиболее старая серия, которая

постепенно снимется с производства. Она отличается не слиш-

ком хорошими параметрами по сравнению с другими сериями.

С этой классической серией принято сравнивать все остальные.

Философия цифровой электроники 41

Таблица 1.3. Сравнение параметров одинаковых микросхем в разных стан-

дартных сериях

К155ЛАЗ (SN7400N) К555ЛАЗ (SN74LSOON) КР1533ЛАЗ (SN74ALSOON) КР1554ЛАЗ (SN74ACOON)

TpLH, НС не более 22 15 11 8,5

Трнь нс не более 15 15 8 7,0

Iil, мА не более -1,6 -0,4 -0,1 -0,001

1щ, мА не более 0,04 0,02 0,02 0,001

lot, мА не менее 16 8 15 86

1он, мА не менее -0,4 -0,4 -0,4 -75

Uol, В не более 0,4 0,5 0,5 0,3

Uoh, В не менее 2,4 2,7 2,5 4,4

Ice, мА не более 12 4,4 3 0,04

Серия К555 (SN74LS) отличается от серии К155 малыми

входными токами и меньшей потребляемой мощностью (ток по-

требления почти втрое меньше, чем у К155). По быстродейст-

вию (по временам задержек) она близка к серии К155.

Серия КР531 (SN74S) отличается высоким быстродействием

(задержки примерно в 3—4 раза меньше, чем у серии К155), но

большими входными токами (на 25% больше, чем у К155) и

большой потребляемой мощностью (ток потребления больше

в полтора раза по сравнению с серией К155).

Серия КР1533 (SN74ALS) отличается повышенным пример-

но вдвое по сравнению с К155 быстродействием и малой по-

требляемой мощностью (в четыре раза меньше, чем у К155).

Входные токи еще меньше, чем у серии К555.

Серия КР1531 (SN74F) отличается высоким быстродействи-

ем (на уровне КР531), но малой потребляемой мощностью.

Входные токи и ток потребления примерно вдвое меньше, чем у

серии К155.

42 Глава 1

Серия КР1554 (SN74AC) отличается от всех предыдущих

тем, что она выполнена по КМОП-технологии. Поэтому она ха-

рактеризуется сверхмалыми входными токами и сверхмалым

потреблением при малых рабочих частотах. Задержки примерно

вдвое меньше, чем у серии К155.

Наибольшим разнообразием имеющихся микросхем отли-

чаются серии К155 и КР1533, наименьшим — серии КР1531 и

КР1554.

Следует отметить, что приведенные здесь соотношения по

быстродействию стандартных серий довольно приблизительны

и выполняются не для всех разновидностей микросхем, имею-

щихся в разных сериях. Точные значения задержек необходимо

находить в справочниках, причем желательно использовать

фирменные справочные материалы.

Микросхемы разных серий обычно легко сопрягаются меж-

ду собой, то есть сигналы с выходов микросхем одной серии

можно смело подавать на входы микросхем другой серии. Одно

из исключений — соединение выходов ТТЛ. микросхем со вхо-

дами КМОП микросхем серии КР1554 (74АС). При таком со-

единении необходимо применение резистора номиналом 560 Ом

между линиями сигнала и напряжения питания (рис. 1.19).

Рис. 1.19. Сопряжение микросхем ТТЛ и КР1554 (КМОП).

При выборе той или иной серии микросхем следует также

учитывать, что микросхемы мощной и быстрой серии КР531

создают высокий уровень помех по шинам питания, а микро-

схемы маломощной серии К555 очень чувствительны к таким

помехам. Поэтому серию КР531 рекомендуется использовать

только в крайних случаях, когда необходимо получить очень

высокое быстродействие. Не рекомендуется также применять

в одном и том же устройстве мощные быстродействующие и

маломощные микросхемы.

Философия цифровой электроники 43

1.6. Корпуса цифровых микросхем

Большинство микросхем имеют корпус, то есть прямоугольный

контейнер (пластмассовый, керамический, металлокерамиче-

ский) с металлическими выводами (ножками). Предложено

множество различных типов корпусов, но наибольшее распро-

странение получили два основных типа:

• Корпус с двухрядным вертикальным расположением выводов,

например: DIP (Dual In Line Package, Plastic) — пластмассо-

вый корпус, DIC (Dual In Line Package, Ceramic) — керамиче-

ский корпус. Общее название для таких корпусов — DIL

(рис. 1.20). Расстояние между выводами составляет 0,1 дюйма

(2,54 мм). Расстояние между рядами выводов зависит от коли-

чества выводов.

• Корпус с двухрядным плоскостным расположением выводов,

например: FP (Flat-Package, Plastic) — пластмассовый плоский

корпус, FPC (Flat-Package, Ceramic) — керамический плоский

корпус. Общее название для таких корпусов — Flat (рис. 1.20).

Расстояние между выводами составляет 0,05 дюйма (1,27 мм)

или 0,025 дюйма (0,0628 мм).

Рис. 1.20. Примеры корпусов DIL и Flat.

Flat

Номера выводов всех корпусов считаются начиная с вывода,

помеченного ключом, по направлению против часовой стрелки

(если смотреть на микросхему сверху). Ключом может служить

вырез на одной из сторон корпуса микросхемы, точка около пер-

вого вывода или утолщение первого вывода (рис. 1.20). Первый

вывод может находиться в левом нижнем углу или в правом

верхнем углу (в зависимости от того, как повернут корпус). Мик-

росхемы обычно имеют стандартное число выводов из ряда: 4, 8,

14, 16, 20, 24, 28,... Для микросхем стандартных цифровых серий

используются корпуса с количеством выводов начиная с 14.

44 Глава!

Назначение каждого из выводов микросхемы приводится в

справочниках по микросхемам, которых сейчас имеется множе-

ство. Правда, лучше ориентироваться на справочники, издавае-

мые непосредственно фирмами-изготовителями. В данной книге

назначение выводов микросхем не приводится.

Отечественные микросхемы выпускаются в корпусах,

очень похожих на DIL и Flat, но расстояния между их вывода-

ми вычисляются по метрической шкале и поэтому чуть-чуть

отличаются от принятых за рубежом. Например, 2,5 мм вместо

2,54 мм, 1,25 мм вместо 1,27 мм и т. д. Для корпусов с малым

числом выводов (до 20) это не слишком существенно, но для

больших корпусов расхождение в расстоянии может стать су-

щественным. В результате на плату, рассчитанную на зару-

бежные микросхемы, нельзя поставить отечественные микро-

схемы и наоборот.

1.7. Двоичное кодирование

Одиночный цифровой сигнал не слишком информативен, ведь

он может принимать только два значения: нуль и единица. По-

этому в тех случаях, когда необходимо передавать, обрабаты-

вать или хранить большие объемы информации, обычно приме-

няют несколько параллельных цифровых сигналов. При этом

все эти сигналы должны рассматриваться только одновременно,

каждый из них по отдельности не имеет смысла. В таких случа-

ях говорят о двоичных кодах, то есть о кодах, образованных

цифровыми (логическими, двоичными) сигналами. Каждый из

логических сигналов, входящих в код, называется разрядом.

Чем больше разрядов входит в код, тем больше значений может

принимать данный код.

Десятичное число

Двоичное число

х 10° (единицы)

х10 (десятки)

х102 (сотни)

ХЮ3 (тысячи)

1

‘----х2° (разряд 0)

------Х21 (разряд 1)

------х22 (разряд 2)

------х23 (разряд 3)

Рис. 1.21. Десятичное и двоичное кодирование.

Философия цифровой электроники 45

В отличие от привычного для нас десятичного кодирования чи-

сел, то есть кода с основанием десять, при двоичном кодировании в

основании кода лежит число два (рис. 1.21). То есть каждая цифра

кода (каждый разряд) двоичного кода может принимать не десять

значений (как в десятичном коде: 0, 1,2, 3, 4, 5, 6, 7, 8, 9), а всего

лишь два значения — 0 и 1. А система позиционной записи остает-

ся такой же, то есть справа пишется самый младший разряд, а сле-

ва— самый старший. Но если в десятичной системе вес каждого

следующего разряда в десять раз больше веса предыдущего разря-

да, то в двоичной системе (при двоичном кодировании) — в два

раза. Каждый разряд двоичного кода называется битом (от англий-

ского Binary Digit — двоичное число).

Таблица 1.4. Соответствие чисел в десятичной и двоичной системах

Десятичная система Двоичная система Десятичная система Двоичная система

0 0 10 1010

1 1 11 1011

2 10 12 1100

3 11 13 1101

4 100 14 1110

5 101 15 1111

6 110 16 10000

7 111 17 10001

8 1000 18 10010

9 1001 19 10011

В табл. 1.4 показано соответствие первых двадцати чисел в

десятичной и двоичной системах.

Из таблицы видно, что количество разрядов двоичного кода,

требуемое для представления каждого числа (кроме 0 и 1), значи-

тельно больше, чем требуемое количество разрядов десятичного

кода. Наибольшее число, которое можно представить 3-разрядным

кодом, в десятичной системе составляет 999, а в двоичной систе-

ме — всего лишь 7(111 в двоичном коде). В общем случае п-раз-

рядное двоичное число может принимать 2“ различных значений, а

n-разрядное десятичное число — 10° значений. Поэтому запись

больших двоичных чисел (с количеством разрядов больше десяти)

становится не слишком удобной.

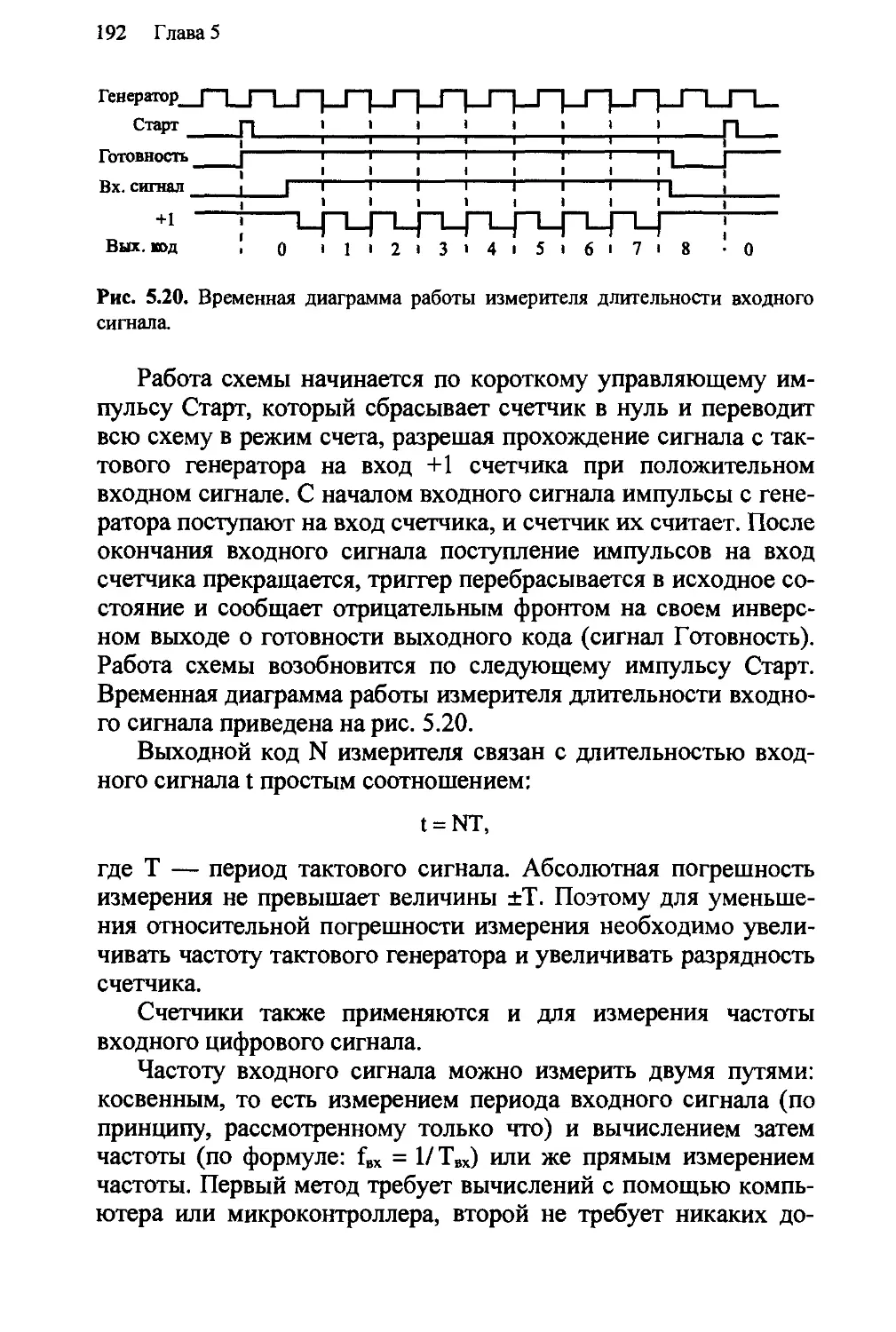

46 Глава 1