Author: Вальпа О.В.

Tags: компьютерные технологии общая радиотехника программирование программное обеспечение компьютерные науки

ISBN: 5-93517-342-5

Year: 2007

Text

Разра№ка устройств на основе

цифровых ситнальвых процессоров

фирмы Шоу Detices

с исвопьзоваиием Visual DSP++

О. Д. Валь па

Разработка устройств иа основе

цифровых сигнальных процессоров

фирмы Analog Devices

с использованием

Visual DSP++

Москва

Горячая линия - Телеком

2007

УДК 681.325.5

ББК 32.84

В16

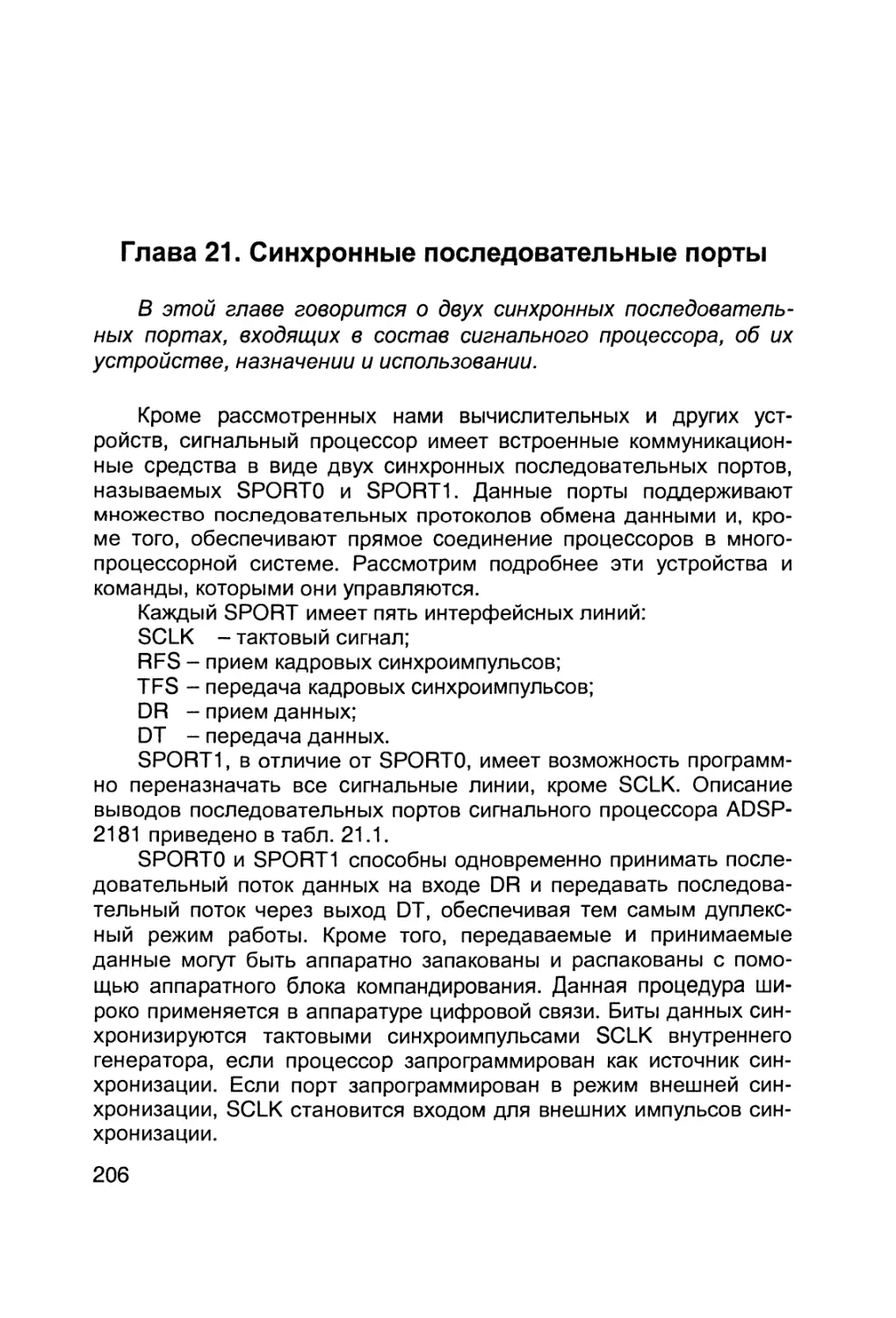

Вальпа О. Д.

В16 Разработка устройств на основе цифровых сигнальных процессоров

фирмы Analog Devices с использованием Visual DSP++. - М.: Горячая

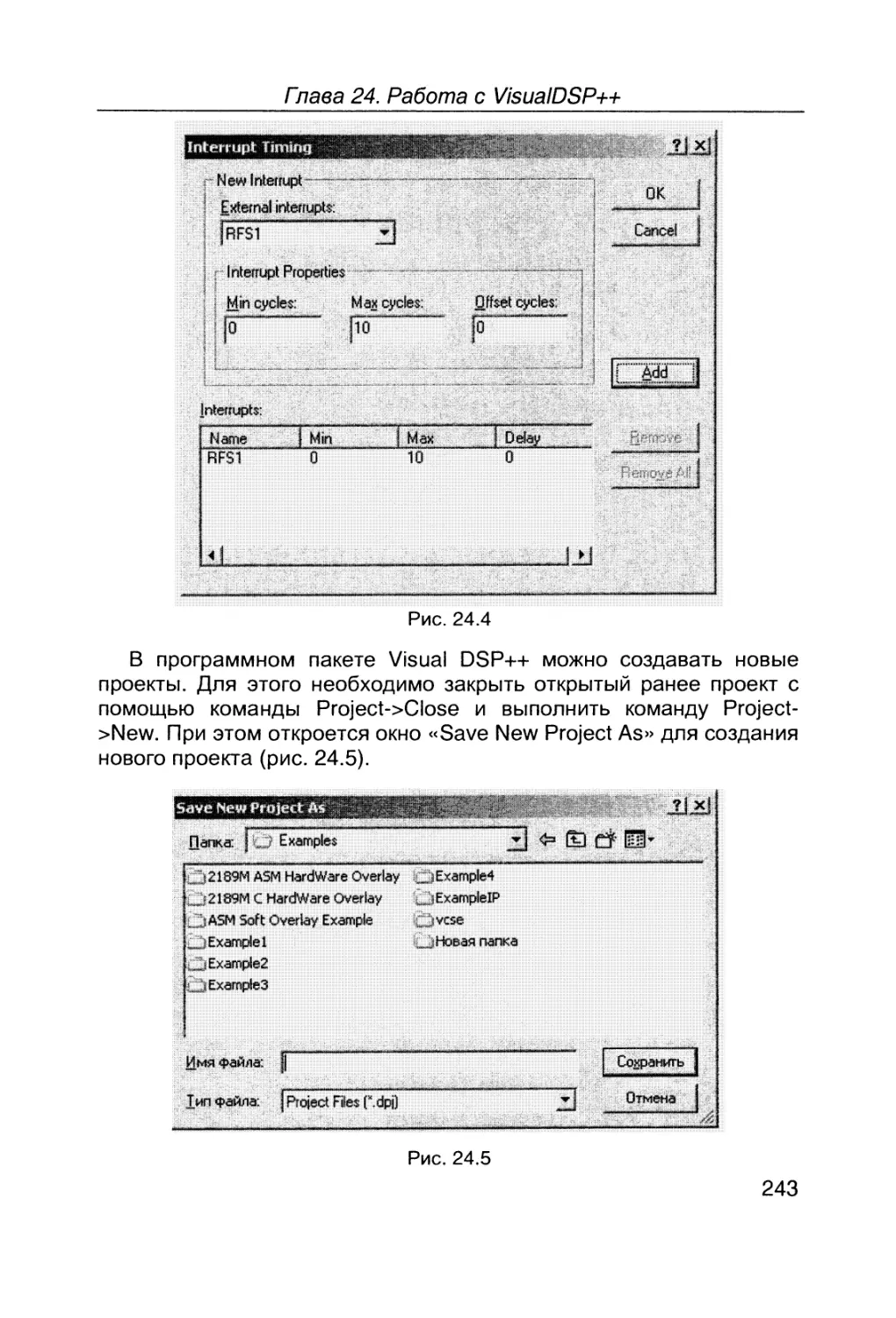

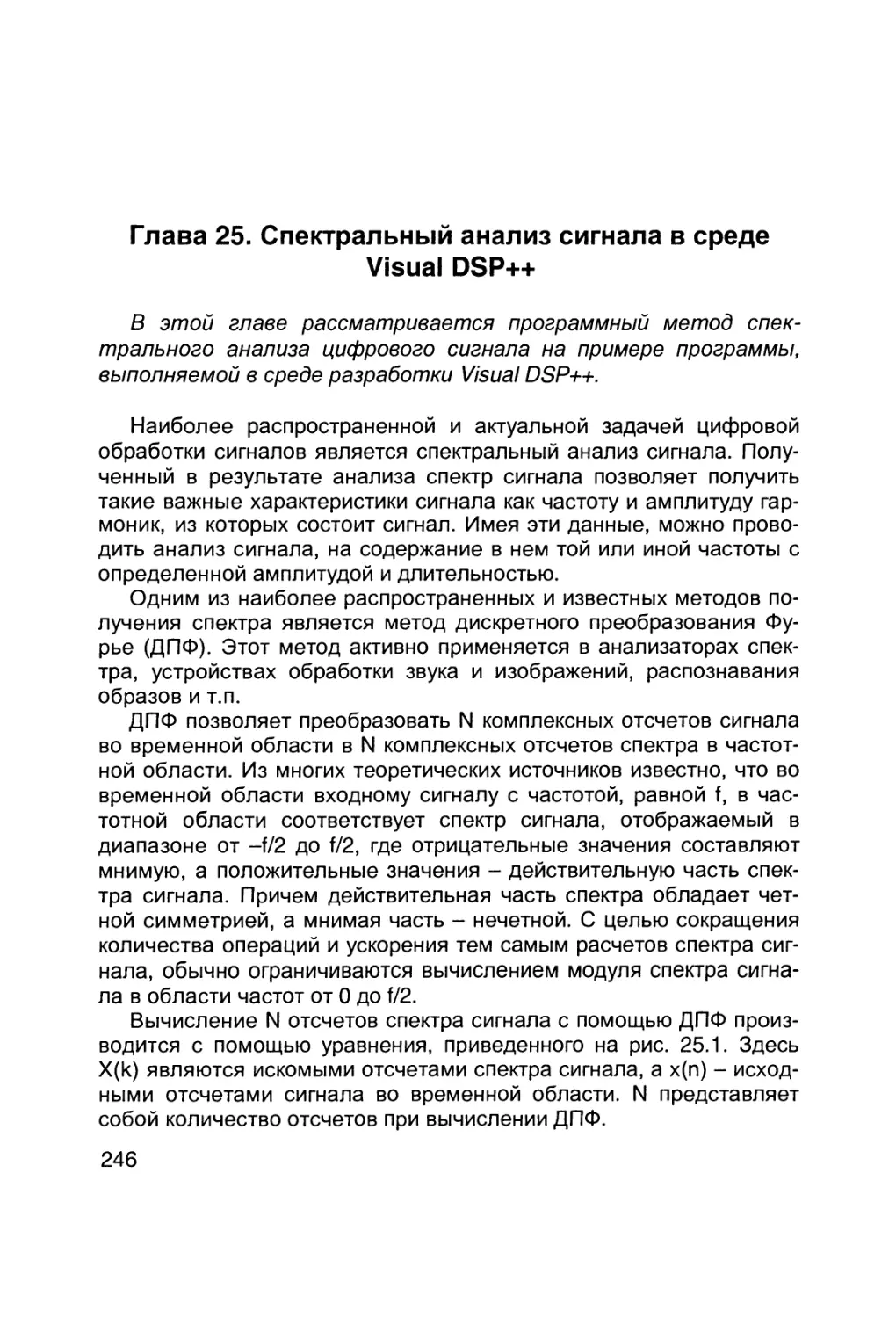

линия-Телеком, 2007 . - 270 с.

ISBN 5-93517-342-5.

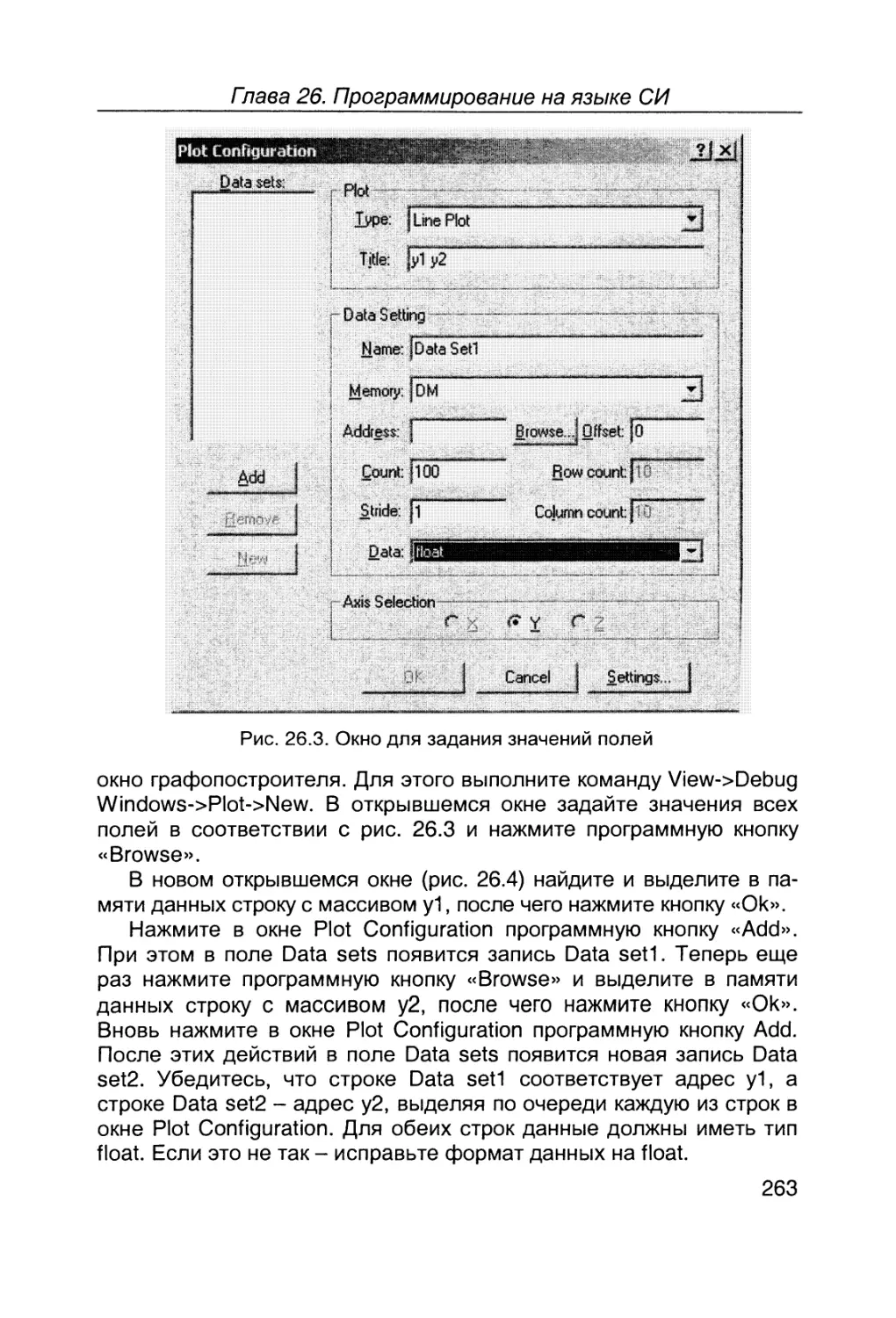

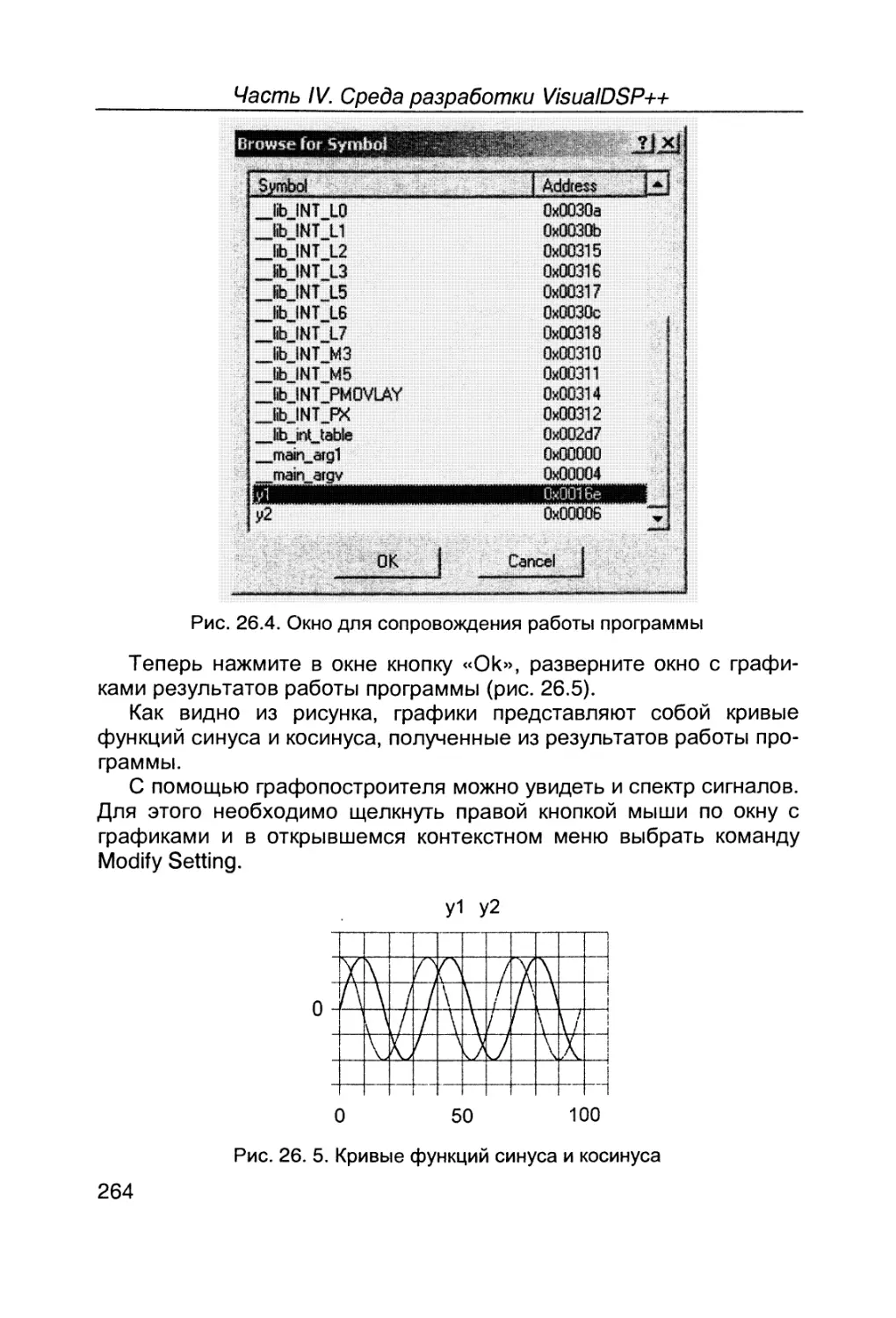

Книга предназначена для самостоятельного изучения и применения на

практике цифровых сигнальных процессоров DSP (Digital Signal Processor).

На примере популярной микросхемы ADSP2181 фирмы Analog Devices рас-

смотрены устройство, архитектура и технические характеристики цифрового

сигнального процессора. Приведено описание вычислительных блоков про-

цессора, средств разработки программного обеспечения, языка программи-

рования и системы команд процессора. Разработанные автором книги прак-

тические схемы с применением сигнального процессора, исходные тексты

программ и схемы вспомогательных устройств, полезных при отладке про-

грамм для процессора помогут получить необходимые практические навыки,

с помощью которых читатель легко освоит другие типы сигнальных процес-

соров. На прилагаемом к книге диске находятся исходные тексты и испол-

няемые файлы программ, а так же некоторые полезные утилиты и средства

разработки программного обеспечения для сигнальных процессоров.

Для специалистов в области разработки цифровой электронной аппара-

туры, будет полезна студентам и аспирантам.

ББК 32.84

Адрес издательства в Интернет www.techbook.ru

Справочное издание

Вальпа Олег Дмитриевич

Разработка устройств на основе

цифровых сигнальных процессоров фирмы Analog Devices

с использованием Visual DSP++.

Редактор А. Ю. Петкин

Корректор А. К. Степанова

Верстка Ю. Н. Рыськова

Обложка художника В. Н. Мятникова

Подписано в печать 30.10.2006. Формат 60x88/16. Бумага офс.

Усл. печ. л. 17. Тираж 2000 экз. Изд. № 6342

ISBN 5-93517-342-5

© О. Д. Вальпа, 2007

© Оформление издательства

«Горячая линия-Телеком», 2007

Предисловие

В настоящее время цифровые сигнальные процессоры, или

сокращенно DSP (Digital Signal Processor), приобрели большую

популярность в мире и даже признаны отдельной областью науки

и техники.

Эта книга является практическим руководством по самостоя-

тельному изучению и применению на практике одного из цифровых

сигнальных процессоров фирмы Analog Devices. Она включает в

себя подробное описание процессора, схемы для его практического

применения и технологию программирования.

Книга написана простым языком и позволяет очень быстро ос-

воить сигнальный процессор и применить его на практике в собст-

венных разработках, включает в себя разработанные автором кни-

ги практические схемы с применением сигнального процессора,

исходные тексты программ и схемы вспомогательных устройств,

полезных при отладке программ для процессора.

Состоит из четырех частей: часть I посвящена схемотехнике

сигнальных процессоров; в части II рассмотрено программирование

устройств; далее в части III описаны вычислительные и аппаратные

устойства; в части IV представлены установка, запуск, работа, спек-

тральный анализ сигнала, а также программирование на СИ в сре-

де разработки Visial DSP++.

На прилагаемом электронном диске находятся исходные тексты

и исполняемые файлы программ из книги, а также некоторые по-

лезные утилиты и средства разработки программного обеспечения

для сигнальных процессоров.

Изучив материалы этой книги, читатель получит фундаменталь-

ные знания, с помощью которых легко освоит другие типы сигналь-

ных процессоров.

Книга будет полезна как начинающим разработчикам, так и спе-

циалистам в области разработки цифровой электронной аппарату-

ры. Кроме того, она будет полезна студентам технических вузов,

инженерам и программистам.

Автор

3

ЧАСТЬ I. СХЕМОТЕХНИКА

В этой части книги освещается история развития раз-

личных сигнальных процессоров и дается обзор техниче-

ских характеристик сигнальных процессоров семейства

ADSP-21XX. Кроме того, в ней приводится практическая

схема применения процессора ADSP-2181, описываются его

архитектура и программно-логическая модель, дается опи-

сание системы прерываний процессора.

4

Глава 1. Обзор

В настоящее время большую популярность приобрели цифро-

вые сигнальные процессоры, или сокращенно DSP (digital signal

processor). Эта книга приподнимет завесу таинственности этих

компонентов и позволит читателям самостоятельно заняться

их освоением и применением в собственных разработках.

Свое название сигнальные процессоры получили в связи с

встроенной в них возможностью обработки звуковых и видеосигна-

лов. Это реализовано благодаря высокой скорости работы этих

процессоров и заложенной в них специальной системе команд под-

держивающей функции цифровой фильтрации и быстрого преобра-

зования Фурье. Ниже перечислены основные отличия сигнальных

процессоров от обычных микропроцессоров.

• Наличие аппаратного умножителя.

• Наличие специальных блоков обработки данных.

• Специальная система команд для цифровой обработки сигналов.

• Высокое быстродействие.

• Внутренний умножитель тактовой частоты.

• RISC архитектура.

• Возможность одновременного выполнения нескольких команд.

• Гарвардская архитектура построения процессора.

• Наличие конвейеризации команд и данных.

• Наличие циклических буферов.

• Развитая система внешних интерфейсов.

Некоторые типы данного семейства процессоров имеют также

встроенные аналого-цифровой преобразователь АЦП и цифро-

аналоговый преобразователь ЦАП, что позволяет подавать на процес-

сор непосредственно аналоговые сигналы, которые после оцифровки

обрабатываются в цифровом виде этим же процессором. Под обра-

боткой понимается, как правило, спектральный анализ сигнала, т.е.

определение наличия в этом сигнале определенной частоты заданной

амплитуды, фильтрация сигнала от ненужных частот, сравнение сиг-

нала с эталонным сигналом-шаблоном, синтез и генерация речи, сжа-

тие и декомпрессия звуковых и видеосигналов и т.п. В современном

5

Часть I. Схемотехника

мире существует огромное количество подобных задач в самых раз-

личных областях человеческой деятельности. Решение этих задач

требуется в радиоэлектронике, радиолокации, навигации, связи, ме-

дицине, автомобильной промышленности, космонавтике и др. науко-

емких областях. Ввиду своей важности, цифровая обработка сигна-

лов в настоящее время признана даже отдельной областью науки и

техники. По всему видно, что для этих процессоров открывается

большое будущее. Именно поэтому, находясь у истоков развития

сигнальных процессоров, важно вовремя познакомиться с ними, что-

бы в дальнейшем они не казались нам недоступными и закрытыми.

Проведем небольшой экскурс в историю развития данного се-

мейства процессоров. Первые сигнальные процессоры появились в

начале 80-х годов. Одной из первых компаний начавшей производ-

ство этих процессоров, была японская корпорация NEC, выпустив-

шая однокристальный сигнальный процессор MPD7720. Однако

этот процессор не получил широкого распространения, поскольку в

1982 г. на смену ему пришел более производительный и развитый

процессор TMS32010, выпущенный фирмой Texas Instruments. Бла-

годаря удачной архитектуре и ряду технических решений он стал

стандартом де-факто для сигнальных процессоров. Ниже приведе-

ны основные технические характеристики данного процессора.

Разрядность данных...................16 бит

Производительность...................5 млн. операций в секунду

Объем оперативной памяти.............256 слов

Объем памяти программ................4 К слов

Объем подключаемой внешней памяти....4 К слов

Разрядность арифметико-логического

устройства...........................32 бит

Разрядность умножителя...............6x16 бит с 32-битным

результатом

Разрядность портов ввода-вывода......16 бит

Количество портов ввода-вывода.......8

Пропускная способность внешней шины.....50 Мбит

Освоение новых микронных технологий и, как следствие, повы-

шение степени интеграции микросхем позволили значительно

улучшить характеристики процессоров. И уже в середине 1980-х

годов появились сигнальные процессоры второго поколения. К ним

можно отнести процессоры все той же фирмы Texas Instruments

TMS320C25 и TMS320C5X. Эти процессоры более скоростные и

имеют больший объем памяти. Кроме того, у них появилась разви-

тая система обработки прерываний и энергосберегающие режимы

работы. В некоторых моделях процессоров снижено напряжение

6

Гпава 1. Обзор

питания. Появились теневые регистры для автоматического сохра-

нения результатов работы в случае возникновения аппаратного или

программного прерывания программы. В состав архитектуры про-

цессора добавились таймеры и последовательные синхронные

порты с развитой конфигурацией настройки.

В свою очередь, фирма Motorola выпустила сигнальные процессоры

семейства DSP56000, которые имеют разрядность 24 бита, двойную

внутреннюю шину данных X и Y, удобную при операциях с комплекс-

ными числами, и обладают высокой степенью конвейеризации и па-

раллелизма. Эти свойства делают данные процессоры еще более

производительными и удобными для цифровой обработки сигналов.

Еще один производитель в лице фирмы AT&T Microelectronics

выпускает сигнальные процессоры серии DSP16, которые отлича-

ются наличием кэш памяти и встроенного высокоскоростного, до

30 Мбайт, параллельного порта.

Фирма Analog Devices вышла на рынок сигнальных процессоров

со своей серией ADSP-21XX, которые конкурируют с выше рас-

смотренными моделями по некоторым техническим параметрам, а

кроме того, по цене. Например, процессор ADSP-21msp50 имеет

встроенные АЦП и ЦАП и в то же время его стоимость составляет

несколько долларов.

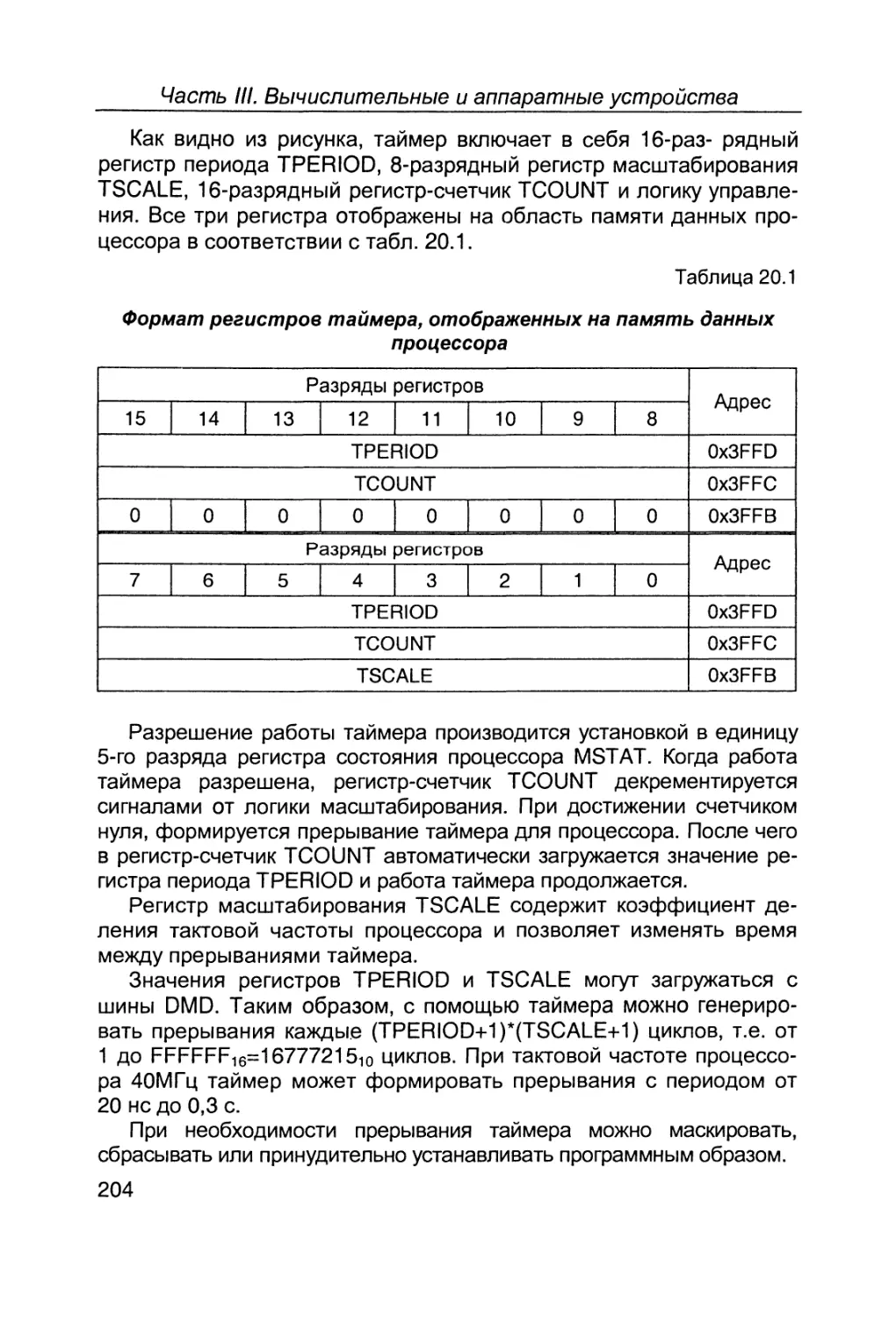

На этом развитие сигнальных процессоров не остановилось, и

уже в конце 1980-х годов на рынке появились процессоры третьего

поколения от перечисленных выше фирм. Отличительной особенно-

стью этого поколения стало появление двоичной плавающей ариф-

метики, увеличение разрядности шины данных, емкости памяти и

программ. К этому числу процессоров можно отнести TMS320C30

фирмы Texas Instruments, DSP96002 фирмы Motorola, DSP32C фир-

мы AT&T Microelectronics и ADSP21020 фирмы Analog Devices.

Впоследствии на рынке появились сигнальные процессоры дру-

гих фирм. Однако в настоящее время, лидирующее положение в

этой области занимают фирмы Texas Instruments, Motorola, AT&T

Microelectronics и Analog Devices.

История развития сигнальных процессоров на этом не заканчи-

вается, и можно было бы продолжать ее повествование, но целью

данной книги является не исторический рассказ, а практическое

руководство по освоению и приобретению навыков работы с этими

перспективными компонентами. Поэтому я хочу остановиться на

более подробном описании внутренней архитектуры и практическо-

го применения одного из сигнальных процессоров фирмы Analog

Devices. Именно об этом и пойдет речь в следующей главе.

7

Глава 2. Архитектура

В этой главе описывается внутренняя архитектура одного

из сигнальных процессоров фирмы Analog Devices ADSP-2181 и

примеры его подключения.

Фирма Analog Devices разработала целые семейства сигналь-

ных процессоров и постоянно продолжает выпускать на рынок но-

вые модели. В настоящее время существуют следующие семейст-

ва: ADSP-21XX, Shark DSP, BlackFin DSP и др. Но, несмотря на все

многообразие этих групп, все они имеют похожую друг на друга ар-

хитектуру. Отличие семейств друг от друга заключается, например,

в арифметических блоках, которые поддерживают вычисления с

фиксированной или плавающей запятой. Кроме того, семейства

отличаются производительностью, разрядностью шин данных,

структурой внутренних регистров, интерфейсами и т.п. Отличие

процессоров друг от друга внутри семейства состоит в основном в

объеме и организации внутренней памяти и типе встроенных ин-

терфейсов. В состав каждого из процессоров этого семейства вхо-

дят следующие функциональные устройства.

• Арифметико-логическое устройство АЛУ.

• Умножитель-накопитель.

• Устройство сдвига.

• Два генератора адреса данных.

• Программный автомат.

• Таймер.

• Последовательный многоканальный порт.

Н иже приведена табл. 2.1 с отличительными характеристиками

сигнальных процессоров семейства ADSP-21XX.

Остановимся на рассмотрении архитектуры одного из самых

распространенных на сегодняшний день процессоров семейства

ADSP-21XX, а именно на процессоре ADSP-2181. Этот компонент

является самым развитым в своем семействе и включает в себя

наибольший объем памяти и множество встроенных интерфейсов.

Сигнальный процессор ADSP-2181 представляет собой одно-

кристальный чип, выпускаемый в 128 выводных корпусах типа

8

Глава 2. Архитектура

Таблица 2.1

Характеристики сигнальных процессоров семейства ADSP-21XX

Ресурсы 2101 2103 2105 2111 2115 00 L0 Q. (Л Е см 2171 2173 2181 2183

Объем оперативной памяти программ (слов) СМ СМ т— СМ т— см см см (О Т— (О т—

Объем оперативной памяти данных (слов) ы т— Ы т— СМ L0 т— см LO см см см (О (О 1—

Второй последова- тельный порт - + +

Порт хост интер- фейса - - - + - + + + - -

Порт прямого дос- тупа к памяти - + +

Максимальная внешняя тактовая частота, МГц о CXI 10,24 13,82 о см о см 16,67 16,67 16,67 о см о см

Аналого-цифровые преобразователи и фильтры - - - - - + - - - -

Режим малого по- требления - - - - - + + + + +

Напряжение пита- ния, В LO со со" L0 LO L0 L0 L0 со со L0 со со

Количество сигнальных выво- дов 00 со 00 (О 00 (О о о Г" 00 (О О О Г" 00 СМ т— 00 см 00 см 00 см

9

Часть I. Схемотехника

PQFP-128 или TQFP-128. Из вышеприведенной информации уже

можно составить общее представление о возможностях, зало-

женных в данный процессор. Но для полноты картины рассмот-

рим структурную схему внутренней архитектуры этого чипа, при-

веденную на рис. 2.1.

Процессор имеет сильно развитую структуру внутренних шин ад-

реса и данных. К их числу относятся шина адреса памяти программ

PROGRAM MEMORY ADDRESS, шина адреса памяти данных DATA

MEMORY ADDRESS, шина данных памяти программ PROGRAM

MEMORY DATA и шина данных памяти данных DATA MEMORY

DATA.

Слева на схеме изображен базовый блок архитектуры всего

семейства ADSP-2100 BASE ARCHITECTURE включаемый в со-

став любого из процессоров данного семейства. Он состоит из

блока генераторов адреса данных DATA ADRESS GENERATORS,

программного автомата PROGRAM SEQUENCER и арифметиче-

ского блока ARITHMETIC UNITS.

Блок генераторов адреса данных содержит два генератора:

DAG1 и DAG2, предназначенных для инвертирования бит адреса

во время выполнения процессором операций быстрого преобразо-

вания Фурье (БПФ).

Рис. 2.1. Структурная схема внутренней архитектуры чипа

10

Гпава 2. Архитектура

Программный автомат осуществляет поддержку операций с ус-

ловными переходами, вызов подпрограмм и возврат в основную

программу, ускоряя тем самым работу процессора в целом.

Арифметический блок включает в себя арифметико-логическое

устройство ALU, умножитель с накопителем МАС и устройство

сдвига SHIFTER. Первый из этих блоков предназначен для выпол-

нения арифметических и логических операций над данными, а вто-

рой для выполнения арифметического умножения чисел. SHIFTER

позволяет нормировать числа после выполнения арифметических

операций.

Рассмотрим блоки, расположенные справа вверху по схеме.

Блок управления пониженным питанием POWER DOWN CONTROL

обеспечивает управление процессором для перехода в режим по-

ниженного потребления после выполнения соответствующей инст-

рукции и возврат из этого режима после возникновения прерывания

или после перезапуска. Блок памяти MEMORY состоит из памяти

данных DATA MEMORY и памяти программ PRORAM MEMORY.

Таким образом, оперативная память всего процессора разделена

на две независимых части в соответствии с Гарвардской архитекту-

рой построения процессоров. Тем не менее, система команд этого

процессора позволяет использовать память программ для хранения

данных. Блок программируемых входов-выходов PROGRAMMABLE

I/O позволяет запрограммировать несколько выводов по усмотрению

разработчика на ввод или на вывод битовых сигналов, что обеспечи-

вает возможность гибкого применения этих выводов. Блок флагов

FLAGS управляет тремя битовыми выводами, организованными как

сигнальные выходы. Наконец, блок байтового контроллера прямого

доступа к памяти BYTE DMA CONTROLLER, сокращенное и часто

употребляемое в дальнейшем название которого BDMA, обеспечи-

вает быстрый аппаратный ввод и вывод байтовых данных через

внешнюю шину данных процессора.

Теперь рассмотрим блоки, расположенные справа внизу по схе-

ме. Одним из самых популярных и полезных является блок после-

довательных многофункциональных портов SERIAL PORTS, кото-

рый включает в себя два последовательных порта SPORT1 и

SPORT2. Отличительной особенностью этих портов является то,

что они программируемые, синхронные и многоканальные. Т.е. ка-

ждый из этих портов способен принимать и передавать информа-

цию от однословного до тридцатидвухсловного последовательного

потока бит. Каждое слово в потоке может иметь длину от трех до

шестнадцати бит. Этот формат передачи данных часто применяет-

11

Часть I. Схемотехника

ся при построении телекоммуникационных систем. К такому порту

можно подключить одновременно до 32 кодеков и получить на их

выходе соответственно 32 аналоговых канала ввода-вывода. Со-

гласитесь - это мощный инструмент, который можно применить

во многих областях. Кроме того, порты могут программироваться

на внешнюю или внутреннюю синхронизацию. Управляющие вы-

воды портов также могут быть запрограммированы на ввод или

вывод.

Следующий блок таймера TIMER, обеспечивает организацию

отсчета необходимых интервалов времени и прерываний по тайме-

ру. Прерывание генерируется каждый раз, когда обнуляется счет-

чик таймера, который после обнуления загружается значением из

шестнадцатиразрядного регистра, хранящего период таймера.

И, наконец, блок внутреннего порта INTERNAL DMA PORT IDMA,

сокращенное название которого IDMA, предназначен для организа-

ции прямого доступа к памяти данных и памяти программ процес-

сора по шестнадцатиразрядной внешней шине. Этот порт играет

важную роль при работе с процессором, поскольку позволяет за-

гружать программу и данные непосредственно в память процессора

до его старта, стартовать процессор и производить операции чте-

ния и записи данных в память во время его работы, незначительно

влияя при этом на производительность процессора.

С внешним миром процессор общается посредством четырна-

дцатиразрядной шины адреса EXTERNAL ADDRESS BUS, двадца-

ти четырехразрядной шины данных EXTERNAL DATA BUS и шест-

надцатиразрядной шины IDMA DMA BUS.

На рис. 2.2 приведена более подробная структурная схема про-

цессора, с указанием разрядности внутренних и внешних шин и бо-

лее детальным изображением всех описанных выше блоков.

Более подробную структуру процессора мы рассмотрим позже,

когда будем изучать его внутренние регистры и примеры программ.

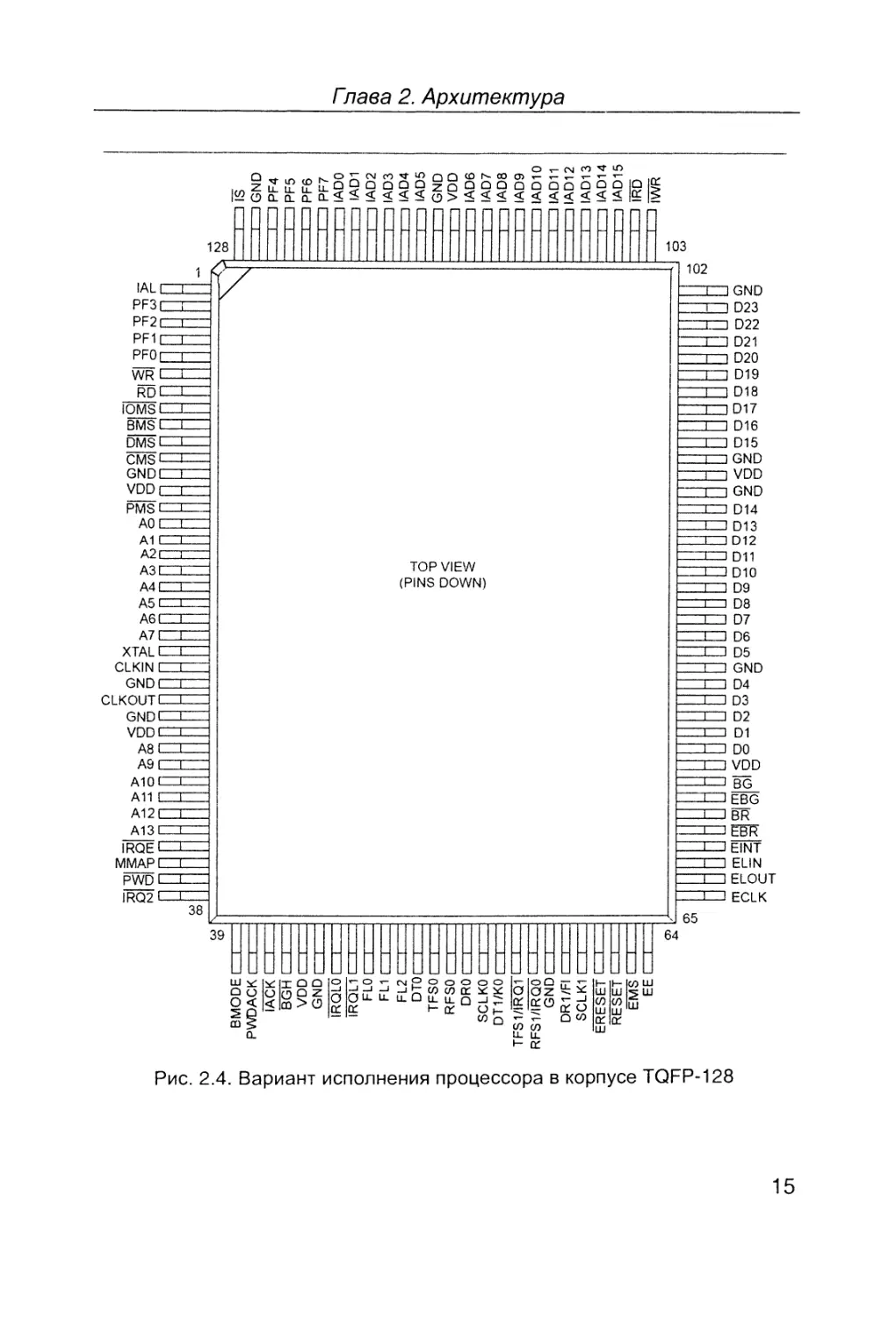

На рис. 2.3 и 2.4 представлены варианты исполнения процессо-

ра в корпусах PQFP-128 и TQFP-128, соответственно. На этих же

рисунках изображено назначение всех контактов процессора и при-

ведена их нумерация.

Изображения дают вид сверху TOP VIEW, выводами вниз PINS

DOWN. Сигналы с низкими активными уровнями имеют обозначения

с чертой над сигналом. Выводы двойного назначения, определяемо-

го программированием этих выводов, обозначаются через символ

«/».

12

Рис. 2.2. Структурная схема процессора

Гпава 2. Архитектура

Часть I. Схемотехника

i

О Т- CSI СО q-toQQCOCOr-Cog’v- Т- Т- т-

OOOOOQZOOQOOOO О Q О О

97

BMS i_1

DMS

CMS

GND I

VDD c

128

PF0

RD

IOMS

96

3 021

3 020

J D19

PMS

AO

A1

A2

A3

A4

A6

A7

XTAL

CLKIN

GND

VDD

A8

A9

А11

А13

IRQE

MMAP

32

33

128LPQFP

(28 MM x 28 MM)

TOP VIEW

(PINS DOWN;

3 D16

j 015

] GND

j VDD

J GND

3 D14

3 D13

3 D12

3 011

3 D10

...I I D7

----Г—I D6

~..I ' I D5

3 D3

3 D2

J 01

33 VDD

Z3 BG_

□ EBR

=□ BR

il 65

64

Рис. 2.3. Вариант исполнения процессора в корпусе PQFP-128

В табл. 2.2 дается описание назначения выводов процессора.

Способ подключения к процессору различных периферийных

устройств показан на структурной схеме, приведенной на рис. 2.5.

В качестве примера, на этой схеме показано, как подключаются

следующие устройства:

14

Гпава 2. Архитектура

128

103

1 TOP VIEW (PINS DOWN) ' 102

IALI I '1 ' I GND

PF3EZLZT ~~T' 4 D23

PF2I—I —ZE—I D22

PF 11 1 1—I D21

PFOl 1 4 1 D20

WR □= 1_J D19

RDl L ' 'I. I D18

IOMS1 1 _ - '•I ' ID17

BMSL I....Z 7Г.77Г' ''.I D16

dms ii : Z__i_J D15

CMS1—1 -~-r l GND

GNDL__L_ — Г-l VDD

VDDl l —T I GND

pms 1—f I ! П1Л

ДП i—i L—J U 14

r\U I 1 1—1 D13 1 1 гио

A21 1 1 1 U1Z

1—I D11

АЗ Г 1 " I I D10

A4l 1 I I D9

A5 1 1 I I D8

A6I L_ —L, I D7

A7 L_J I I D6

XTALI 1 I I D5

CL KIN Г 1. I J GND

GNDI 1 I I D4

CLKOUTI—L— I I D3

GNDI 1 I I D2

VDDl 1 I I D1

A8I 1 I I DO

A9I 1 I I VDD

A10C 1—I BG

A11 I I —L-J EBG

А12ГТ~~~~ BR

A13[=n= I i ebr

IRQE I—I 1—I EINT

MMAPCZZZEZZZ I I ELIN

PWD I I. — I I ELOUT

IRO7 L_l. I I ECI К

Рис. 2.4. Вариант исполнения процессора в корпусе TQFP-128

15

Часть I. Схемотехника

Таблица 2.2

Описание выводов процессора ADSP-2181

Наименова- ние Вы- вод I/O Функция

А0...А13 0 Адресные выводы для адресации области внеш- ней памяти программ, памяти данных, байтовой памяти (BDMA) и устройств ввода-вывода

D0...D23 I/O Выводы данных для обмена данными с внешней памятью программ и памятью данных. Восемь старших разрядов также используются как адрес байтовой памяти.

-WR -RD -IOMS -BMS -DMS -CMS -PMS 0 0 0 0 0 0 0 Сигнал записи Сигнал чтения Выбор области памяти Выбор байтовой памяти Выбор памяти данных Выбор комбинированной памяти Выбор программной памяти

FLO, FL1, FL2 PF0...PF7 0 I/O Выходы-флаги Программируемые выводы

MMAP -PWD BMODE PWDACK I I I 0 Выбор карты памяти процессора Управление потреблением Режим загрузки O-ROM, 1-IDMA Контроль низкого потребления питания

XTAL CLKIN CLKOUT I I 0 Соединение с кварцем Внешний генератор, или соединение с кварцем Выходная тактовая частота

-RESET -ERESET I I Сброс процессора Разрешение сброса

-IRQLO -IRQL1 -IRQ2 -IRQE I I I I Потенциальный запрос прерывания 0 Потенциальный запрос прерывания 1 Динамический или потенциальный запрос пре- рывания 2 Динамический запрос прерывания

16

Гпава 2. Архитектура

Наименова- ние Вы- вод I/O Функция

-BR -BG -BGH I 0 0 Внешний запрос шины Внешнее предоставление шины Внешнее предоставление шины, подтянутое к питанию

IAD0...IAD15 -IACK -IWR -IRD -IS IAL I/O 0 I I I I Шина адреса/данных порта IDMA Подтверждение доступа к порту IDMA Вход записи в порт IDMA Вход чтения из порта IDMA Вход выборки порта IDMA Вход защелки адреса порта IDMA

DT0 TFS0 RFSO DR0 SCLK0 0 I/O I/O I I/O Передача данных Кадровая синхронизация передачи Кадровая синхронизация приема Прием данных Программируемый генератор порта 0

DT1/FO TFS1/IRQ1 RFS1/IRQ0 DR1/FI SCLK1 0 I/O I/O I I/O Передача данных, или выходной флаг Кадровая синхронизация передачи, или внешний запрос прерывания 1 Кадровая синхронизация приема, или внешний запрос прерывания 0 Прием данных, или входной флаг Программируемый генератор порта 1

-EMS ЕЕ ECLK ELOUT ELIN EINT -EBR -EBG Сигналы, используемые только в режиме эмуля- ции

GND Выводы заземления

VDD Выводы питания

Примечание:! - вход, О - выход; минус перед сигналом означает

низкий активный уровень сигнала.

17

Часть I. Схемотехника

Рис. 2.5. Способ подключения к процессору различных периферийных

устройств

Внешний генератор или кварцевый резонатор с половинной так-

товой частотой процессора 1/2х CLOCK OR CRYSTAL.

Последовательные устройства SERIAL DEVICE, например кодеки.

Системный интерфейс или микроконтроллер SYSTEM

INTERFACE OR MICROCONTROLLER.

Байтовая память BYTE MEMORY.

До 2048 периферийных устройств ввода-вывода I/O SPACE

PERIPHERALS.

Внешняя память OVERLAY MEMORY.

При использовании внешней памяти, допускается подключение

двух 8К-словных сегмента памяти программ TWO 8К РМ

SEGMENTS и двух 8К-словных сегмента памяти данных TWO 8К

DM SEGMENTS.

Из схемы видно также, какие именно сигналы процессора ис-

пользуются для подключения всех перечисленных внешних уст-

ройств.

18

Гпава 2. Архитектура

Рис. 2.6. Способ подключения кварцевого резонатора к сигнальному

процессору

На рис. 2.6 показан способ подключения кварцевого резонатора

к сигнальному процессору. Конденсаторы должны иметь номиналь-

ную емкость от 22 до 33 пФ, а максимальная частота кварцевого

резонатора должна быть вдвое ниже максимальной внутренней

частоты процессора, поскольку внутри процессора производится

аппаратное умножение внешней задающей тактовой частоты. Эта

удвоенная частота выводится на сигнальный вывод CLKOUT процес-

сора. Вместо кварцевого резонатора, для формирования задающей

частоты синхронизации можно использовать интегральный генера-

тор, который, однако, несколько дороже резонатора. В этом случае

выход генератора необходимо подключить к выводу CLKIN процес-

сора, а вывод XTAL оставить неподключенным.

Карта памяти процессора изображена в табл. 2.3. На первых двух

фрагментах таблицы показаны режимы использования памяти про-

грамм. Эти режимы задаются с помощью внутреннего регистра

PMOVLAY и подключения внешнего вывода процессора ММАР к нуле-

вому потенциалу или к источнику питания соответственно. При сбросе

процессора регистр PMOVLAY обнуляется, и подключается внутренняя

память. В процессе выполнения программы содержимое этого регист-

ра можно изменить, и переключить тем самым процессор на использо-

вание внешней памяти программ. Адресация памяти приведена в ше-

стнадцатеричном формате записи.

Память программ может быть внутренней INTERNAL, т.е. раз-

мещенной на кристалле самого процессора, или внешней

EXTERNAL, т.е. размещенной во внешних микросхемах памяти.

Поскольку память программ организована 24 разрядными словами,

суммарный объем внутренней памяти программ процессора может

быть равен (8К слов+8К слов) х Збайта - 48 Кбайт.

На последнем фрагменте рисунка приведена карта памяти дан-

ных. Ее режим работы, как внешней или внутренней, определяется

с помощью внутреннего регистра процессора DMOVLAY, который

19

Часть I. Схемотехника

Таблица 2.3

Карта памяти процессора

Параметр Адрес Память программ Адрес Память данных Адрес

8 Келов ВНУТРЕННИЕ (PMOVLAY=0, ММАР=0) или 8 Келов ВНЕШНИЕ (PMOVLAY=1 или 2, ММАР=0) 0x3FFF 0x2000 8К слов ВНУТРЕННИЕ (PMOVLAY=0, ММАР=1) 0x3FFF 0x2000 32 РЕГИСТРА 0x3FFF 0x3FE0

8160 слов ВНУТРЕННИЕ 0x3FDF 0x2000

8К слов ВНУТРЕННИЕ 0x1FFF 0x0000 8К слов ВНЕШНИЕ 0x1FFF 0x0000 8К слов ВНУТРЕННИЕ (DMOVLAY=0) или 8К слов ВНЕШНИЕ (DMOVLAY=1 или 2) 0x1FFF 0x0000

аналогично регистру PMOVLAY обнуляется при сбросе или включении

процессора, обеспечивая тем самым включение режима использова-

ния внутренней памяти данных. В самой верхней области памяти дан-

ных размещены 32 служебных регистра процессора, которые органи-

зованы как память данных. Поэтому память данных усечена по объему

на это количество ячеек памяти. Память данных организована шестна-

дцатиразрядными словами, поэтому суммарный объем внутренней

памяти данных процессора составляет (8К слов + 8К слов) х 2 байта =

32 Кбайт.

Учитывая разрядность банков памяти программ и памяти дан-

ных, суммарная емкость памяти процессора составляет 80 Кбайт.

Это довольно большой объем памяти, достаточный для решения

многих задач, написанных на языках ассемблера или Си.

В следующих главах, приведены примеры электрических прин-

ципиальных схем с применением описываемого сигнального про-

цессора и рассказ о способах его программирования.

20

Глава 3. Практические схемы включения

В этой главе приводятся примеры принципиальных схем с при-

менением сигнального процессора ADSP-2181, показывающие спо-

соб его подключения для применения в различных разработках.

Итак, приступим непосредственно к практике по освоению сиг-

нального процессора. На рис. 3.1 изображена принципиальная

схема тестовой платы для изучения процессора и отладки про-

грамм. Файл этой схемы, созданный в системе автоматического

проектирования PCAD 4.5, записан на компакт-диск, прилагаемый к

данной книге. На схеме показан способ включения самого сигналь-

ного процессора и периферийных устройств, подключаемых к нему.

Рассмотрим последовательно все сигнальные выводы процессора

и их назначение.

Как видно из схемы, процессор D1 имеет несколько выводов для

подключения питания, что связано с необходимостью распределе-

ния токоведущих цепей для обеспечения помехоустойчивости. Ис-

пользуемый в схеме сигнальный процессор допускает питание от

источника напряжением 4,5...5,5 В. Стабилизированное напряже-

ние питания 5 В поступает с разъема питания ХР1. Конденсаторы

СР2 и СЗ-С7 обеспечивают фильтрацию напряжения по низким и

высоким частотам соответственно. Индикатор HL4 с токоограничи-

вающим резистором R3 индицирует наличие питания в схеме. Для

питания аналоговой части схемы используются дополнительные

элементы фильтрации L1 и С8-С10.

Следующими важными цепями являются входы и выходы гене-

раторных сигналов XTAL, CLKIN и CLKOUT. Первые две цепи

предназначены для подключения внешнего источника синхрониза-

ции. На приведенной схеме показан способ подключения к процес-

сору кварцевого резонатора BQ1. В случае применения интеграль-

ного генератора выход генератора подключается к выводу CLKIN,

а вывод XTAL не используется. Стоимость генераторов на сего-

дняшний день еще превышает стоимость кварцевых резонаторов,

поэтому к процессору подключен более дешевый кварцевый резо-

натор. Номинальная резонансная частота такого резонатора или

21

Часть I. Схемотехника

AD0 , XU1 ^2 AD1

АО 2 1 ц > AD3

АО 4 5б AD5

АО Б >8 AD7

АО В 9 у ц-. >10 AD9

АО 10 >12 AD11

AD12 13х I >1 Л AD13

AD14 15? m 516 AO1S

0V 17х >18 -0RD

-DUR 14 >20 0V

-1АСК 21> >22 -5EL

-RESI х24 0V

-AWR 25^ >26 0V

+SV 1 ^XU2 2 +sv

0V 3 > Е > 4 0V

5 > 7 < 6

7 > £ < 8

9 > < 10

AD0 2 А0 Al А2 АЗ А4 ш В0 В1 В2 ВЗ 84 IS IAO0

АО! 5 17 J ADI

AD2 4 16 1 A02

AD3 5 15 I ДОЗ

АО 4 6 14 IAD4

АО 5 7 13 I AOS

АО 6 8 А5 I В5 12 1006

АО 7 9 R6 Гх ВБ И IA07

87

-1 RD 1 20 ♦ SV

-15 А '♦В )ОЕ Vcc GND 10 0V

02

AD8 2 A0 Al A2 A3 A4 A5 -0 m B0 Bl 82 B3 B4 B5 B6 18 1AD8

AO 9 3 17 IA09

AD 10 4 16 IAO10

AOll 5 15 [ADIL

ADI 2 6 14 I AO I 2

AD 13 7 13 I AO 13

AD I 4 e 12 I AO 14

AD15 9 A6 ’f 11 [A015

-IRQ 1 B7 20 ♦ SV

-IS 19 < fl -*B 03 Vcc GND 10 0V

-ORO 2 18 -I RO

-OUR 4 00 B0 16 -I UR

-5EL в Al Bl 14 - ] 5

-RE51 8 A2 <N B2 B3 12 -IR

0V 1 f A3 )0E T

D4 1

-AWR

СР1 10мк® 108

74L500

0, 1

XR51

D8R-9M

CP4 10гн«Ф 106

XEZ

- ВС.__________2 Н"14^J_____________0V

- BR_______ 4 С. ^3___________-EBG

- E1NT________6 x. <5___________-EBR

Elin 8^ 3т

ECLK J 0x >3 ELOUT

-EMS__________I2x U i__________EE

-ERESET 14^ 43_________-RESET

Рис. 3.1. Принципиальная схема тестовой платы

22

Гпава 3. Практические схемы включения

В01

16384КГа D5P 90 ll 90 90 20 21 DD0

20 CLK.IN 12 61 91 19 HC uv 22 DOI

T 22 R1 13 92 A2 10 Al и i 23 0D2

Tn “Те? R2 14 93 93 17 Я2 иг 25 003

-RFSFT 58 93 94 03

)Rtbt 1 15 A4 П П 4

c-7 Q R4 15 H 4 U4 005

-ERE5ET Ь/ ( 16 95 A5

feRESET RS AB 17 96 96 14 на из 28 006

-IRQL0 18 AE 06 007

41 / )IRQL0 13

-IRQL1 4? R7 RB R9 R10 25 98 98 3

-IRQ2 34 ) IRQL1 )[R02 >IRQE 26 99 99 2 AB ( §

-IROE 31, J 27 610 910 31 610 611 R12

2S 91 1 Al I 1

-BR. 66 ? )BR )BG >6GH Al 1 912 913 29 912 A12 12 1 J

-ВС 68 f 30 913 913 r

38 D08 5 613 914 915 616 917 A13

00 70 009 11

JRD0 118 1600 1601 1602 1603 1004 IAD5 1906 1607 IAD8 1909 16010 19011 71 0010 10

3 AD1 1 17 01 72 □ Oi 1 6

1902 1 16 02 D3 73 0012 9

1903 115 74

IAD4 114 76 •ROM0 30 I

1RD5 1 13 05 06 77 -RO 32 ( > CE t ! + 5V

IRD6 110 78 -UR 7 > OE iV 24 0V

1907 10Я 07 OB 09 D10 DI 1 DI 2 DI 3 014 79 000 > VE и/ UNU

1Я08 108 60 DD1

IR09 107 81 002 0013 1 E -ROM0

IRD10 105 52 □03 0014 2 UL 1 s .14

ЗАО» 1 105 83 □04 0015 3 H 1 S

19D12 104 84 □05

10013 103 IAD13 16014 16015 95 006 *5V 6 l Л Lri

1Й014 102 89 □07 0 V 5(

IRD15 101 DI 5 DIB D17 90 008 -BMS 4, >E i

91 009 >E2 E

IACK 37 I6CK >IWR )IRD >15 92 0010-

-IWR DI В D19 020 93 001 1

-IRD 100 / 94 0D12 -5V 1 G13. i

-15 1?4 95 □013 -8MS 2 1 10

IRL 125 D21 022 9? 0014 -I0M5 3 Q 1

IAL 97 0015 -RO 4 2 c 2

□ Г0 46 DT0 023 -UR 5 3 *- , и 1 1 13

TFS0 47 WR C RD ( -UR PF0 6 . 12|

RFS0 48 TFS0 -RO PF 1 7 5 c I

OR0 49 RF50 4 -I QMS PF 2 8 6 c r 013. 4

SCLK0 50 DR0 SCLK0 I QMS ( BM5 C QMS C CMS c PM5 C -BMS PF3 9

6 _J0_ 8

F0 51 DT 1 7 Г 9

52 £10 L

TFS1 RF51 DR1 )

F 1 . 55 43 FL0 FL0 11 A B0 9 FLB0

56 FL0 44 FL1 FL I 13 Hlfl 7 7 FLBI

5CLK 1 ELI 45 PL2 FL2 IS A I D J 5 FLB2

-EMS )EH5 FL2 PF0 PF 1 1 PF0 PF7 17 A2 DZ 3 PFB7

ЕЕ 60 ( 128 PF 1

ECLK 61 EE 127 PF2 0V JL^ >DE

ELDUT 6? EC LK PF2 PF3 PF4 128 PF3 0 4. 2

El in 63 ELOLJT ELIN >EINT >EBR 122

-EINT 64 z 121 PF0 i SB0-SB3

-E8R G5 J PF5 PF6 120 PFl SOI ]

-ЕВС 119 PF 7 PF 2 s'

)ebg PF7 PF3 sb: $J 0V

8 CND1 CND2 GND3 CND4 GND5 GN06 GND7 GND8 GND9 CND10 GN01 1 MMQP PUD < В MODE 3WDACK 32 0V F ILt 3 R5

t 21 ,33 *5V FLB0 P .5-R8

, 23 35 BMODE IK

, 40 36 F <L1 L R6

> 54 FLBI 1/ ft

; 75 9 14 12

, 86 +5V1 ♦SV2 24 , F <l: > R7

; 88 39 , FLB2 V P ft

; 98 +5V3 69 , 14 у

, 112 1-5 V4 +SV5 +5VB 87 ( F 1L2 5

0V ' ; 173 01 1!1 ' -»5V PFB7 ГЧО -5V

Рис. 3.1. Принципиальная схема тестовой платы (продолжение)

HL0-HL3

L-934HC

23

Рис. 3.1. Принципиальная схема тестовой платы (окончание)

!асть /. Схемотехника

Гпава 3. Практические схемы включения

генератора не должна превышать половину предельно допустимой

частоты для данного процессора. Так, для процессора с максимальной

тактовой частотой 40 МГц она не должна превышать 20 МГц. Конден-

саторы С1 и С2 должны быть керамического типа, емкостью от 18 до

30 пФ.

Внутри процессора производится аппаратное умножение внеш-

ней частоты, которая затем используется для синхронизации про-

цессора. Внутренняя частота процессора будет составлять 40 МГц,

а длительность выполнения команд 25 нс. Внутренняя частота вы-

водится также на CLKOUT процессора и может быть использована

для синхронизации других микросхем, подключаемых к процессору.

Временная диаграмма сигналов синхронизации показана на рис.

3.2, а допустимые параметры этих сигналов приведены в табл. 3.1.

Рис. 3.2. Временная диаграмма сигналов синхронизации

Таблица 3.1

Допустимые параметры сигналов синхронизации процессора

Параметр Минимум Максимум Единица измерения

Сигналы синхронизации

Требуемые длительности:

tcKI 50 150 нс

tcKIL 20 нс

tcKIH 20 нс

25

Часть I. Схемотехника

Параметр Минимум Максимум Единица измерения

Сигналы синхронизации

Характеристика переключения:

tcKL 0,5tCK-7 нс

tcKH 0,5tCK-7 нс

tcKOH 0 20 нс

tcK= 0,5*tcKi

При выборе сигнального процессора необходимо пользоваться

табл. 3.2, в которой приведены заводские маркировки и соответст-

вующие им характеристики.

Таблица 3.2

Характеристики сигнальных процессоров

Заводская марки- ровка Рабочий темпера- турный диапазон, °C Макси- мальная тактовая частота, МГц Тип корпуса Услов- ное обо- значе- ние кор- пуса

ADSP-2181KST-115 0...+70 28,8 TQFP-128* ST-128

ADSP-2181BST-115 -40...+85 28,8 TQFP-128 ST-128

ADSP-2181 KS-115 0...+70 28,8 PQFP-128** S-128

ADSP-2181 BS-115 -40...+85 28,8 PQFP-128 S-128

ADSR-2181KST-133 0...+70 33,3 TQFP-128 ST-128

ADSP-2181BST-133 -40...+85 33,3 TQFP-128 ST-128

ADSP-2181 KS-133 0...+70 33,3 PQFP-128 S-128

ADSP-2181 BS-133 -40...+85 33,3 PQFP-128 S-128

ADSP-2181 KST-160 0...+70 40 TQFP-128 ST-128

ADSP-2181 KS-160 0...+70 40 PQFP-128 S-128

* TQFP - Plastic Thin Quad Flatpack (пластиковый тонкий четырехуголь-

ный плоский корпус).

** PQFP - Plastic Quad Flatpack (пластиковый четырехугольный плоский

корпус).

26

Гпава 3. Практические схемы включения

В нашем случае использован процессор ADSP-2181KS-133 в

корпусе PQFP-128, как получивший большое распространение и

легко доступный. В табл. 3.3 приведено соответствие выводов кор-

пуса этого процессора его сигналам.

Таблица 3.3

Соответствие выводов корпуса сигналам процессора

Вы- вод Сигнал Вы- вод Сигнал Вы ВОД Сиг- нал Вы- вод Сиг- нал

1 PF0 33 PWD 65 EBR 97 D23

2 WR 34 IRQ2 66 BR 98 GND

3 RD 35 BMODE 67 EBG 99 IWR

4 IOMS 36 PWDACK 68 BG 100 IRD

5 BMS 37 IACK 69 VDD 101 IAD15

6 DMS 38 BGH 70 DO 102 IAD14

7 CMS 39 VDD 71 D1 103 IAD13

8 GND 40 GND 72 D2 104 IAD12

9 VDD 41 IRQLO 73 D3 105 IAD11

10 PMS 42 IRQL1 74 D4 106 IAD10

11 AO 43 FLO 75 GND 107 IAD9

12 A1 44 FL1 76 D5 108 IAD8

13 A2 45 FL2 77 D6 109 IAD7

14 A3 46 DTO 78 D7 110 IAD6

15 A4 47 TFSO 79 D8 111 VDD

16 A5 48 RFSO 80 D9 112 GND

17 A6 49 DRO 81 D10 113 IAD5

18 A7 50 SCLKO 82 D11 114 IAD4

19 XTAL 51 DT1/FO 83 D12 115 IAD3

20 CLKIN 52 TFS1/IRQ1 84 D13 116 IAD2

21 GND 53 RFS1/IRQ0 85 D14 117 IAD1

22 CLKOUT 54 GND 86 GND 118 IAD0

23 GND 55 DR1/FI 87 VDD 119 PF7

24 VDD 56 SCLK1 88 GND 120 PF6

27

Часть I. Схемотехника

Вы- вод Сигнал Вы- вод Сигнал Вы вод Сиг- нал Вы- вод Сиг- нал

25 А8 57 ERESET 89 D15 121 PF5

26 А9 58 RESET 90 D16 122 PF4

27 А10 59 EMS 91 D17 123 GND

28 А11 60 ЕЕ 92 D18 124 IS

29 А12 61 ECLK 93 D19 125 IAL

30 А13 62 ELOUT 94 D20 126 PF3

31 IRQE 63 ELIN 95 D21 127 PF2

32 ММАР 64 EINT 96 D22 128 PF1

Сигнал -RESET обеспечивает сброс процессора в исходное со-

стояние. Этот сигнал должен находиться в активном низкоуровневом

состоянии при включении и перезагрузке процессора в течение не

менее пяти тактовых периодов внешней синхронизации процессора.

Обычно для надежного сброса процессора этот сигнал удерживается

в активном состоянии не менее нескольких микросекунд. Формирова-

ние сигнала сброса в схеме возможно от любого из двух источников.

Первый источник этого сигнала реализован на зарядной цепочке R1,

СР1. В момент подачи питания на схему, конденсатор СР1 разряжен

и на нем удерживается низкий потенциал в течении времени его за-

ряда, достаточного для приведения процессора в исходное состоя-

ние. Диод VD1 обеспечивает быстрый разряд этого конденсатора в

момент отключения или кратковременного пропадания питания.

Кнопка SB4 предназначена для принудительного сброса процессора

вручную. Резистор R2 ограничивает ток разряда, предохраняя кон-

такты кнопки от образования искр, и устраняет дребезг контактов со-

вместно с конденсатором СР1. Вторым источником сигнала сброса

является сигнал - RESI с разъема XU1, который буферируется шин-

ным повторителем D4.1 и поступает на микросхему D6. С помощью

элементов D6.3 и D6.4 оба сигнала объединяются в один сигнал

сброса процессора в инверсном (-RESET) и неинверсном виде

(RESET). Наличие неинверсного сигнала требуется для сброса дру-

гих микросхем с активным высокоуровневым входом сброса.

Сигнал -ERESET и сигналы на выводах 59...65 и 67 процессора

предназначены для подключения к нему специального аппаратного

эмулятора EZ-ICE, который можно приобрести через представите-

лей фирмы Analog Device в России. Выводы эмулятора подключены

к разъему XEZ в соответствии с рекомендациями по применению

28

Гпава 3. Практические схемы включения

данного сигнального процессора. Однако на практике вполне можно

обходиться и без этого эмулятора.

Следующая группа сигналов -IRQLO, -IRQL1, -IRQ2 и -IRQE отве-

чает за передачу процессору внешних прерываний. В качестве источ-

ников прерываний могут выступать различные микросхемы, датчики,

кнопки и т.п. Так, к сигнальному выводу-IRQE подключена кнопка SB5

через цепочку устранения дребезга контактов R22 и СР4. Резистор R23

предназначен для удержания сигнала прерывания в пассивном со-

стоянии. В дальнейшем с ее помощью можно будет принудительно

вызывать прерывание процессора при необходимости.

Следующие три сигнала обеспечивают запрос и предоставление

внешней шины процессора другим внешним устройствам. На схеме

сигнал запроса шины -BR используется только при подключении к

схеме эмулятора EZ-ICE и подключен к разъему XEZ. Этот сигнал

подтянут к шине питания для приведения его в пассивное состоя-

ние. Выходной сигнал -BG, подтверждающий предоставление ши-

ны процессором, также подключен к разъему XEZ. Сигнал -BGH не

используется и остается не подключенным.

Далее следует группа важных сигналов порта прямого доступа к

памяти процессора. Это шестнадцать мультиплексированных сигна-

лов шины адреса данных IAD0-IAD15 и сигналы управления IACK,

-IWR, -IRD, -IS, IAL. Данный порт можно использовать для загрузки

программ и данных во внутреннюю память процессора и, кроме того,

читать содержимое памяти процессора во время его работы. Это

позволяет обходиться без эмулятора EZ-ICE, облегчает отладку про-

грамм и дает большую гибкость при разработке многопроцессорных

схем. На схеме все эти сигналы подключены через буферные микро-

схемы D2, D3, D4.1, D5.1, D5.5 и D5.5 к внешнему разъему XU1. В

дальнейшем мы рассмотрим специальный адаптер, который позво-

лит нам оперативно загружать программы в процессор, читать и за-

писывать данные в его память и окажет большую помощь в изучении

самого процессора и освоении его системы команд и способов про-

граммирования. Цепочка элементов R4 и С11 фильтрует высокочас-

тотные импульсы, проникающие на чувствительный вход IAL процес-

сора, обеспечивая тем самым повышенную помехозащищенность.

Резисторные сборки RN1 и RN2 подтягивают сигналы порта IDMA и

прерываний к высокому пассивному уровню.

Следующие две группы сигналов последовательных портов

SPORTO и SPORT1 обеспечивают работу с последовательными

устройствами. К порту SPORTO в схеме подключен кодек DA1 типа

MC14LC5480, который содержит в себе кодер и декодер с фильт-

рами и компандер. В отличие от аналого-цифрового и цифро-

29

Часть I. Схемотехника

аналогового преобразователей, он отличается тем, что выполняет

преобразование сигналов по A-типу или ц-типу. Фактически оба эти

типа преобразования являются аппроксимацией логарифмической

функции с различной степенью приближения. Они активно приме-

няются в телекоммуникационных системах для цифрового преоб-

разования и сжатия информации с максимальным сохранением

соотношения сигнал-шум. Для этого аналоговые сигналы малой

амплитуды дискретизируются чаще. Для сжатия цифровой инфор-

мации используется функция компандирования, встроенная в кодек

и сигнальный процессор. С помощью этой функции производится

прямое и обратное преобразование 13- или 14-разрядных слов

в 8-разрядные, за счет нелинейного прореживания. В цифровых

каналах связи используются именно такие 8-битные данные. Для

нормальной работы кодеку необходимы сигналы синхронизации и

кадровые стробы приемника и передатчика. Эти сигналы формиру-

ются портом SPORTO на выводах SCLKO, RFS0 и TFS0 соответст-

венно. Все перечисленные сигналы синхронизации и стробов про-

граммируются в процессоре по направлению, частоте, длительно-

сти и фазовому сдвигу. Цифровые данные приемника и передатчи-

ка порта транслируются на кодек по сигнальным выводам DR0 и DT0

соответственно. Помимо перечисленных узлов, кодек содержит в се-

бе операционные усилители и источник опорного напряжения для

смещения напряжения на входах усилителей относительно нулевого

потенциала. Аналоговый сигнал на кодек заведен с разъема XIN типа

тюльпан, через развязывающий конденсатор С16.

Стабилитроны VS1 и VS2 защищают вход кодека от сигналов

большой амплитуды. Резисторы R9 и R10 определяют коэффициент

усиления входного сигнала. Опорное напряжение подведено к неин-

версному входу кодека через резистор R12. Цепочка R11-C17 кор-

ректирует смещение по высоким частотам. Конденсатор С18 являет-

ся фильтрующим. Оцифрованный сигнал поступает в процессор на

вход DR0 для обработки или цифровой записи. В свою очередь, про-

цессор посылает в кодек цифровые сигналы для последующего их

преобразования в аналоговый сигнал. После цифро-аналогового

преобразования сигнала DT0 от процессора выходной аналоговый

сигнал с кодека поступает через ограничительный резистор R14 на

разъем XOUT. Кроме того, этот же сигнал поступает на низкочастот-

ный усилитель, выполненный на транзисторах VT1 и VT2. В нагрузку

усилителя, через развязывающий конденсатор СРЗ, включена ми-

ниатюрная динамическая головка ВА1. Она позволит прослушивать

сигналы, генерируемые процессором через кодек. Резисторы R13 и

R16 определяют коэффициент усиления всего каскада, а резистор

30

Гпава 3. Практические схемы включения

R15 обеспечивает необходимое смещение на базах транзисторов.

Выводы порта SPORT1 являются многофункциональными. Они мо-

гут быть запрограммированы как на работу с последовательными уст-

ройствами подобно порту SPORTO, так и в альтернативном режиме как

флаги входа-выхода и входы прерывания. В нашей схеме использует-

ся второй способ их применения. Вывод 51 порта будет работать как

выход, а вывод 55 как вход. Кроме того, задействован вход прерыва-

ния IRQ1, для формирования прерывания процессора при поступлении

информации по сигнальному выводу FI. Эти выводы задействованы

для организации последовательного порта RS-232 или проще - ком-

пьютерного СОМ порта. Для этого они подключены к микросхеме пре-

образования уровней DA2. Эта микросхема преобразует ТТЛ уровни

сигнала в уровни стандарта RS-232. Конденсаторы С12-С15 обеспе-

чивают работу внутренних умножителей напряжения в микросхеме.

Сигналы порта RS-232 выведены на девятиштырьковый разъем XRS1.

Назначение сигналов на этом разъеме соответствует стандарту, при-

нятому для персональных компьютеров IBM PC. В дальнейшем к этому

порту можно подключить компьютер, с помощью нульмодемного кабе-

ля, для загрузки обучающих программ с помощью программного пакета

EZ-KIT Lite, распространяемого фирмой Analog Device.

Сигналы А0-А13 являются адресными и предназначены для адре-

сации внешней памяти или устройств ввода-вывода. В схеме они под-

ключены к адресным выводам микросхемы постоянной памяти D7, а

некоторые из них, к дешифратору устройств ввода-вывода D9.

Сигналы D0-D23 предназначены для передачи данных и для

адресации. Младшие восемь бит этой шины участвуют в обмене

данными только с расширенной памятью. В нашей схеме эта па-

мять не подключена и, соответственно, сигналы D0-D7 не задейст-

вованы. Разряды D8-D15 используются для передачи данных при

обращении к байтовой памяти BDMA.

В нашей схеме эту роль выполняет микросхема постоянной

флэш-памяти D7. Наконец, старшие разряды этой шины D16-D23

выполняют двоякую роль. При обращении к байтовой памяти они

несут функцию старших адресных линий, а при обращении к устрой-

ствам ввода-вывода являются старшими разрядами шины данных.

Далее следуют сигналы записи -WR, чтения -RD и выборки

внешних устройств. В нашей схеме из внешних устройств будет ис-

пользоваться байтовая память D7, выбираемая сигналом -BMS с

помощью дешифратора D8, и устройства ввода-вывода, выбираемые

сигналом -IOMS с помощью дешифратора D9 и логических элемен-

тов D13.1, D13.2. В схеме присутствует восьмиразрядный регистр

ввода D11 и восьмиразрядный регистр вывода D12. Первый из них

31

Часть I. Схемотехника

позволяет снимать дискретные сигналы с различных цифровых дат-

чиков, контактов и пр. А второй обеспечивает возможность управле-

ния цифровыми ключами, индикаторами и т.п. Выводы этих регист-

ров заведены на разъемы XI и ХО соответственно.

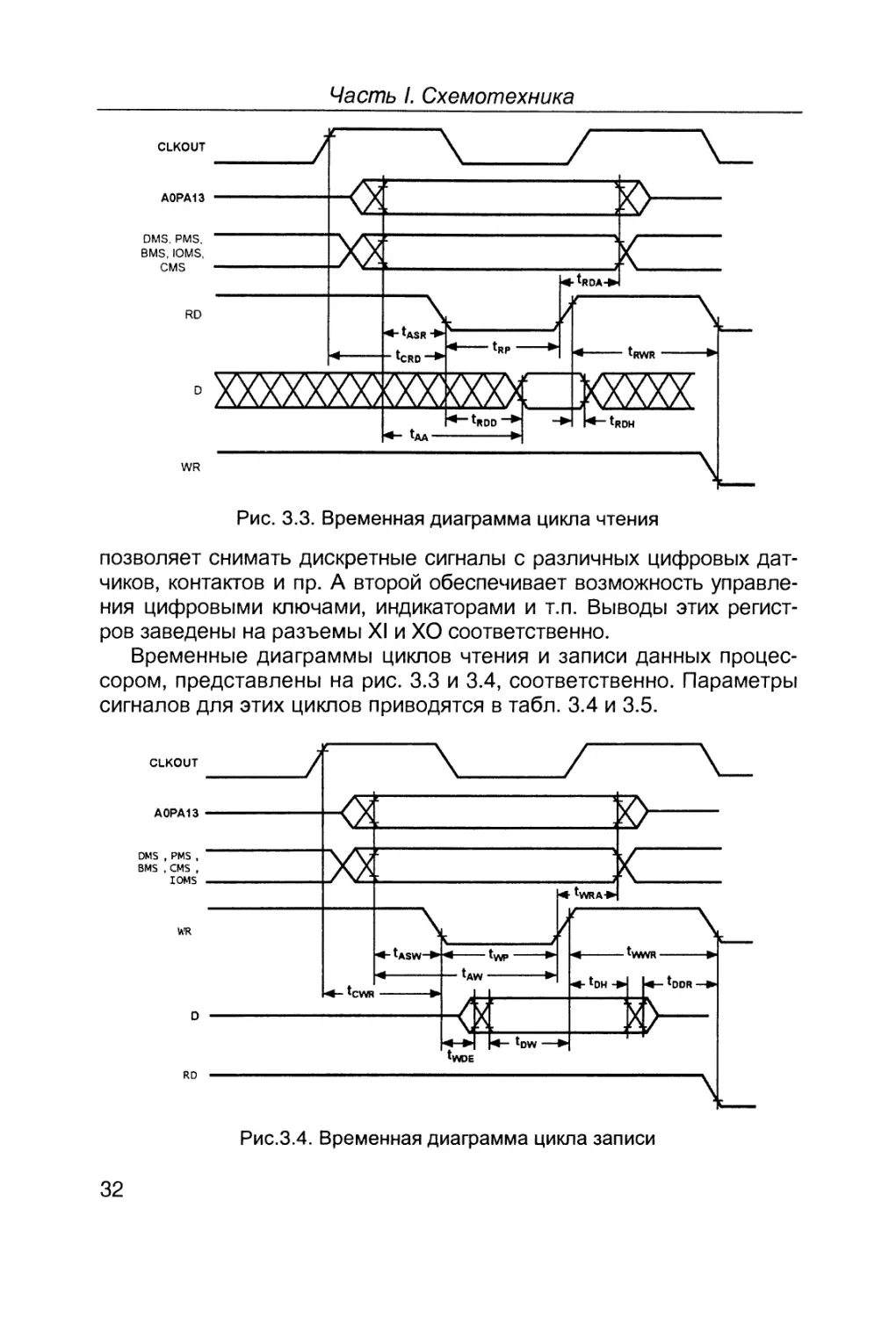

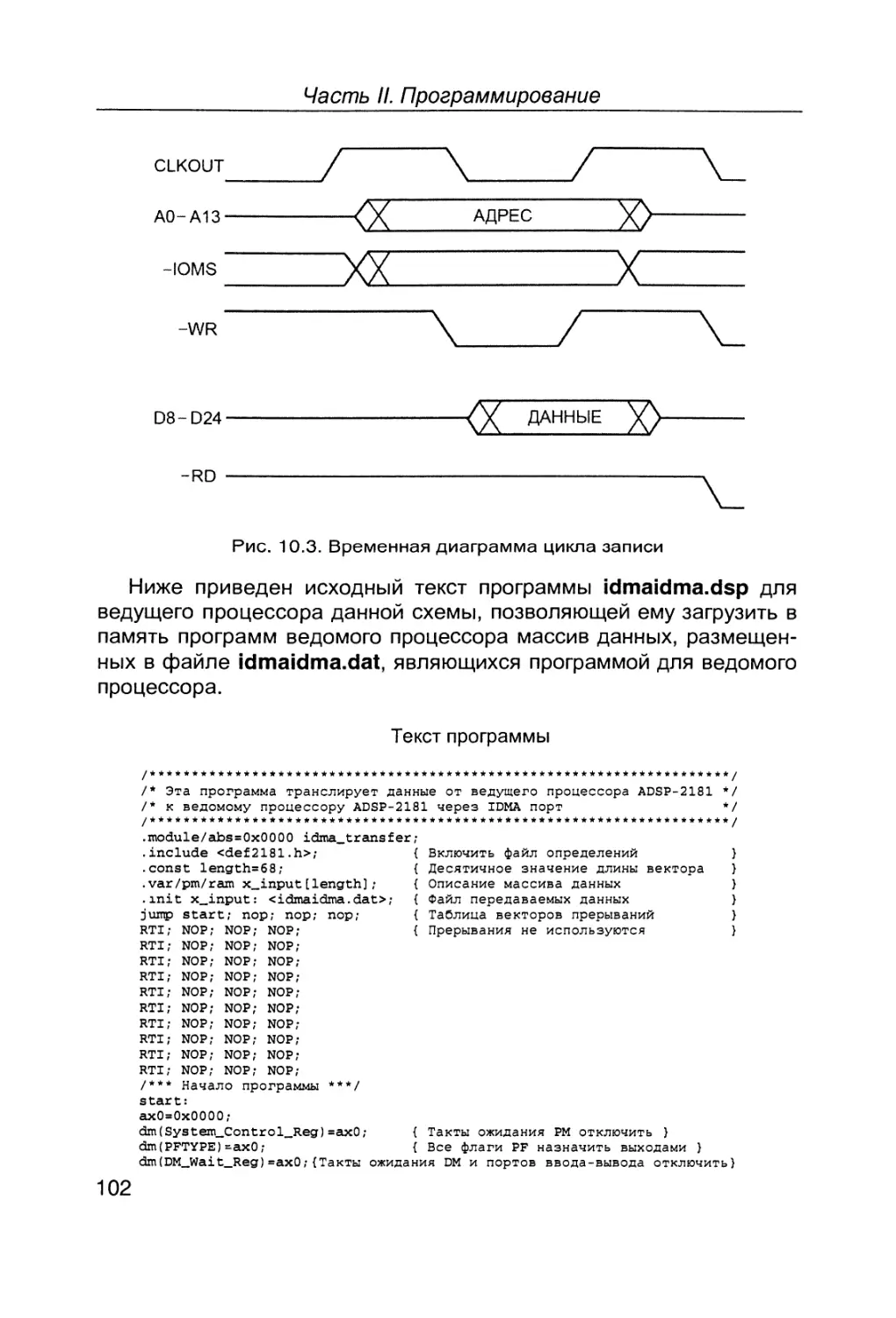

Временные диаграммы циклов чтения и записи данных процес-

сором, представлены на рис. 3.3 и 3.4, соответственно. Параметры

сигналов для этих циклов приводятся в табл. 3.4 и 3.5.

Рис.3.4. Временная диаграмма цикла записи

32

Гпава 3. Практические схемы включения

Таблица 3.4

Параметры сигналов для цикла чтения данных процессором

Параметр Минимум Максимум Единица измерения

Чтение памяти

Требуемые длительности:

tRDD 0,5 tcK - 9 + w нс

tAA 0,25 tcK — 10.5 + w нс

tRDH 0 нс

Характеристика переключения:

tRP 0,5 tcK - 5 + w 0,25tCK + 7 нс

tcRD 0,25 tcK - 5 НС

tASR 0,25 tcK-6 нс

tRDA 0,25 tcK - 3 нс

tRWR 0,5 tcK — 5 нс

Таблица 3.5

Параметры сигналов для цикла записи данных процессором

Параметр Минимум Максимум Единица измерения

Запись памяти

Характеристика

переключения:

tow 0,5 tcK - 7 + w нс

tDH 0,25 tCK - 2 нс

twp 0,5 tcK - 5 + w нс

twDE 0 нс

tASW 0,25 tcK — 6 нс

tDDR 0,25 tcK - 7 нс

tcWR 0,25 tCK - 5 нс

tAW 0,75 tcK — 9 + w 0,25 tCK + 7 нс

twRA 0,25 tCK - 3 нс

twWR 0,5 tcK — 5 нс

w - число циклов задержки * 1ск

33

Часть I. Схемотехника

Из приведенных данных видно, что чтение и запись данных в

процессор необходимо производить по нарастающему фронту сиг-

налов чтения или записи соответственно, когда обеспечена досто-

верность данных на шине.

Следующая группа сигналов FL0-FL2 является битовыми выход-

ными сигналами, которые работают только на вывод. К ним подключе-

ны индикаторы HL0-HL2 через буферный повторитель D4.2.

В отличие от FL0-FL2, выводы PF0-PF7 являются двунаправ-

ленными битовыми сигналами и могут быть запрограммированы как

на ввод, так и на вывод побитно. Так, к выводу PF7 подключен ин-

дикатор HL3, а выводы PF0-PF3 будут запрограммированы как вхо-

ды и к ним подключены кнопки SB0-SB3. Резисторы R5 - R8 явля-

ются токоограничивающими, а резисторная сборка RN3 подтягива-

ет сигналы управления и входные сигналы к высокому уровню.

Назначение сигнала ММАР было показано в предыдущей главе

при рассмотрении способов организации памяти процессора. По-

скольку в нашей схеме используется внутренняя память процессо-

ра и задействован механизм загрузки процессора, этот вывод под-

ключен к нулевому потенциалу.

Сигнал -PWD отвечает за формирование немаскируемого пре-

рывания при снижении питания процессора ниже нормы. Для его

использования необходимо подключить к нему выход узла, отсле-

живающего напряжение питания и формирующего потенциал низ-

кого уровня для формирования прерывания при снижении напря-

жения питания ниже установленной границы. В результате процес-

сор успевает сохранить необходимые данные в энергонезависимой

внешней памяти или выполнить другие необходимые инструкции для

предотвращения неблагоприятных последствий, связанных с пропа-

данием питания. В нашей схеме данный сигнал подключен непо-

средственно к плюсовому выводу шины питания и не используется.

Также не используется и выходной сигнал PWDACK, предназначен-

ный для транзита сигнала, уведомляющего о снижении питания.

Наконец последний вывод процессора BMODE определяет ин-

терфейс, через который будет производиться загрузка процессора.

Если на этот вывод подан нулевой потенциал, загрузка процессора

будет производиться через интерфейс BDMA, т.е. из байтовой па-

мяти. В противном случае процедура загрузки будет производиться

через интерфейс IDMA. В дальнейшем мы рассмотрим оба вариан-

та загрузки. Для автоматизации процесса загрузки в схеме приме-

нен триггер, выполненный на элементах D4.1 и D4.2. В зависимости

от источника сброса, триггер переключается в такое состояние, ко-

торое обеспечивает установку на выводе BMODE сигнала, необхо-

димого для загрузки через соответствующий интерфейс.

34

Гпава 3. Практические схемы включения

А

С19.С20 19пФ

BQ2 11059КГи,1С

XTAL1

XTAL2

RESET C2ZI

А0 28

Al 7/

А2 26

0V 25,

000 L

DOI 2

DD2 T

DD3 4

D04 5

005 5

□ OS 7

□ 07 S

0V e22

-RO f 21,,

-WR [_15' 18,.

-SV 12

-UART

А0

А1

А2

А5

□0

01

П/

03

П4

05

ОС

07

1CR

’’OR

IOW

[GW

CS0

CS2

UAR1

RxRduj*

Т xRdy< Rx Гх

Rc 1 k В Out (

10

□Die <>3

9

J5

RX

tx

S

LD

1Л

DTR.

ere (^-

DSR

j,

oTT

INr

со

R[

CND

-5V

19

20

40

-RT5

-CIS

-0Р1

-0Р2

-5V

0V

•5V

РАЗ

9

D5. 2

г-Ь

□5. 3

□ АЗ

МАХ491

ТХ

-CPI 3 _0V RX /с Л-J £ ... ,..,3 : 2

R19

0V

-Cr5

0V______10K

ТХ-

_[х_:

RX

RX-

0V

тх-

-5V

RX

RX-

0 V

RT5

10 RTS-

14 R20 c\/

Vcc t э V

12 CT5+-

1 I 1 CTS-

0V

XRS2

□5R-9M

б <

R21 R18-R21

51К

-т-3

>4

-»5

8 <-

9 «

R~5-

RTS<-

CI.5±

CT5-

Рис. 3.5. Внешнее устройство в качестве дополнения схемы процессора

35

Часть I. Схемотехника

Еще одно внешнее устройство в качестве дополнения схемы

приведено на рис. 3.5. Это дополнение схемы не является обяза-

тельным и может не распаиваться на основную плату. Но если поя-

вится необходимость оснащения рассмотренной выше схемы еще

одним последовательным портом типа RS-422, это дополнение по-

может в этом.

Как видно из рисунка, схема содержит интегрированную микро-

схему UART D12 с подключенными к ней резонатором BQ2 и вспо-

могательными конденсаторами С19, С20 для запуска внутреннего

генератора. Программирование этой микросхемы производится че-

рез сигналы шины данных DD0 - DD7. Выходные сигналы микро-

схемы UART подключены к приемопередатчикам - преобразовате-

лям уровней сигналов DA3 и DA4 для организации последовательно-

го порта RS-422. Элементы D5.2 и D5.3 инвертируют выходные сиг-

налы управления UART, обеспечивая отключение приемопередатчи-

ков DA3 и DA4 в момент сброса самого UART или при включении.

Элемент D5.3 инвертирует выходной сигнал запроса прерыва-

ния от UART. Резисторы R17-R21 обеспечивают пассивное со-

стояние сигналов при отключенной линии связи. Этот порт позво-

ляет обмениваться информацией со 127 другими устройствами по

аналогичному порту на расстоянии до 1200 метров. Все сигналы

порта выведены на разъем XRS2.

Вся схема может быть распаяна на небольшой макетной плате

или на специально изготовленной плате с разработанной топологи-

ей электрических соединений. Для разработки топологии печатной

платы необходимо создать файл посадочного места для компонен-

та - процессора, который будет использоваться системой автома-

тического проектирования САПР. Чертеж корпуса процессора при-

веден на рис. 3.6.

На нем даны все необходимые размеры в двух системах единиц

измерения. В скобках приведены размеры в дюймах, а без скобок-

в миллиметрах. Ввиду того, что процессор имеет большое количест-

во выводов и мелкий шаг между ними, для изготовления электронных

устройств с его применением может потребоваться разработка пе-

чатной платы. Однако некоторые умельцы используют другие хитрые

приемы для установки таких компонентов на печатной плате. Одним

из таких способов является наклейка фрагментов текстолита с кон-

тактными площадками по периметру установочного места компонен-

та. После чего выводы компонента припаиваются к контактным пло-

щадкам этих фрагментов, и уже после этого тонкими проводниками

осуществляется остальной монтаж всего устройства.

36

Гпава 3. Практические схемы включения

4,07

(0,160)

МАХ

3,67(0,144)

3,17 (0,125)

0,87 (0,034) 0,45 (0,018)

0,73 (0,29) 0.30 (0,012)

Рис. 3.6. Корпус процессора

Естественно, контактные площадки фрагментов должны совпа-

дать с шагом устанавливаемого компонента. Эти фрагменты можно

вырезать, например, с неисправных компьютерных плат или по-

добрать из наборов, продающихся в специализированных магази-

нах по электронике.

В следующих главах говорится о внутренней программной модели

процессора, а также о средствах и способах программирования сиг-

нального процессора. А приведенная и описанная здесь схема по-

может на практике начать освоение сигнальных процессоров.

37

Глава 4. Программно-логическая модель

В этой главе говорится о внутренней программно-логической

модели процессора и его системе прерываний.

Прежде чем начать разрабатывать программы для сигнального

процессора, необходимо познакомиться с его программно-

логической моделью, системой команд и программными инструмен-

тами. Освоение данного материала потребует времени и терпения.

Но без хорошего знания этих основ невозможно будет научиться

программировать сигнальный процессор.

Итак, начнем с программно-логической модели процессора. Та-

кая модель для ADSP-2181 приведена на рис. 4.1.

На ней представлены все регистры процессора с указанием их

размерности и условными обозначениями. Несмотря на многочис-

ленность этих регистров, все они систематически распределены по

логическим блокам процессора, что позволяет понять их назначе-

ние без особого труда.

Главный блок регистров представлен на рисунке слева, в про-

цессорном ядре. В первую очередь это блоки регистров программ-

ных генераторов адреса DAG1 и DAG2. Данные блоки регистров

включают в себя индексные регистры I, регистры длины буфера L и

регистры-модификаторы М.

Все перечисленные регистры имеют размерность 14 бит. Эти

регистры позволяют организовывать в памяти процессора цикличе-

ские и линейные буферы, с автоматическим инкрементом адреса

слов в этих буферах и отслеживанием их длины. В каждом из бло-

ков генераторов адресов присутствует по четыре группы таких ре-

гистров. Использование этих и других регистров будет рассмотрено

позже на конкретных примерах.

Блок программного автомата содержит регистры, отвечающие за

автоматические операции процессора. В их число входят:

• программный счетчик с 16-уровневым 14-разрядным стеком

PC STACK, для организации вызова подпрограмм и обработки пре-

рываний;

• счетчик циклов CNTR с 4-уровневым 14-разрядным стеком

COUNT STACK, для организации вложенных программных циклов;

38

Гпава 4, Программно-логическая модель

• псевдорегистр OWRCNTR, для обновления значения счетчика

CNTR;

• цикловой компаратор LOOP STACK с 4-уровневым 18-

разрядным стеком, для обеспечения выполнения программных

циклов без тактов ожидания.

Назначение остальных регистров управления и состояния блока

программного автомата процессора, приводится в табл. 4.1. Обра-

щение к этим регистрам из программы производится по их логиче-

ским именам, совпадающим с именами, приведенными на рис. 4.1 и

в табл. 4.1.

Таблица 4.1а

Регистр состояния арифметико-логического устройства ASTAT

Раз- ряд Исход- ное состоя- ние Назначение

7 0 Флаг знака ввода в устройство сдвига SHIFTER (SS)

6 0 Флаг переполнения в умножителе-накопителе МАС (MV)

5 0 Флаг частного АЛУ (AQ)

4 0 Флаг знака ввода порта X в АЛУ (AS)

3 0 Флаг переноса бита в АЛУ (АС)

2 0 Флаг переполнения АЛУ (AV)

1 0 Флаг отрицательного результата в АЛУ (AN)

0 0 Флаг нулевого значения в АЛУ (AZ)

Таблица 4.16

Регистр состояния режима процессора MSTAT

Раз- ряд Исход- ное состоя- ние Назначение

6 0 Разрешение режима GO

5 0 Разрешение работы таймера

4 0 Результаты умножителя: 0 - дробные, 1 - целые

3 0 Разрешение режима насыщения регистра AR АЛУ

39

Часть I. Схемотехника

Процессорное ядро

Генераторы адреса данных

DAG1

DAG2

Адресация только DM

Адресация только DM и РМ

I0 L0 МО I4 L4 М4

и L1 М1 I5 L5 М5

I2 L2 М2 I6 L6 Мб

I3 L3 М3 I7 L7 М7

14 14 14 14 14 14

Программный автомат

18 5 14

ALU

МАС

16 16

|АХ0| АХ1

16

16 16

AYO АУ1

16

AR AF

16 16 16 16

МХ0|МХ1| |myo|myi|

8 16 16 16

|MR2|MR1|MRO] |~MF

SHIFTER

16 16 16

si~| | SE | |~SB

16 16

|SR1|SRO

Устройство обмена

между шинами

8

|PX~I

40

Гпава 4. Программно-логическая модель

Таймер

Интерфейс памяти

0x3FFD TPERIOD

0x3FFC TCOUNT

0x3FFB TSCALE

0x3FFF SCR

0x3FFE WCR

Sport О

RXO TXO

Разрешение

мультиканальности

0x3FFA S0RW1

0x3FF9 SORWO

0x3FF8 SOTW1

0x3FF7 SOTWO

Управление

0x3FF6 SOCR

0x3FF5 SOCLKDIV

0x3FF4 SORFDIV

0x3FF3 SOABUF

DMOVLAY PMOVLAY

Sport 1

| RX1 | | TX1 |

Управление

0x3FF2 SICR

0x3FF1 S1CLKDIV

0x3FF0 S1RFDIV

0x3FEF S1ABUF

IDMA Порт

BDMA Порт

Программируемые флаги

IDMA Регистры BDMA Регистры

0x3FE0 IDMACR 0x3FE4 BWCOUNT

Регистры 0x3FE3 BDMACR

программируемых флагов 0x3FE2 BEAD

0x3FE6 PFTYPE Ox3FE1 BIAD

0x3FE5 PFDATA

Рис. 4.1. Программно-логическая модель процессора ADSP-2181

41

Часть I. Схемотехника

Продолжение таблицы 4.16

Раз- ряд Исход- ное состоя- ние Назначение

2 0 Разрешение режима фиксации переполнения АЛУ

1 0 Разрешение бит-реверсивной адресации DAG1

0 0 Выбор банка регистров данных: 0 - главный, 1 - теневой

Таблица 4.1 в

Регистр разрешения прерываний IMASK (0 - запрещено,

1 - разрешено)

Разряд Исход- ное со- стояние Назначение

J5...10 0 Не используются

9 0 -IRQ2

8 0 -IRQL1

7 0 -IRQL0

6 0 Передатчик SPORTO

5 0 Приемник SPORTO

4 0 -IRQE

3 0 BDMA

2 0 Передатчик SPORT1 или-IRQI

1 0 Приемник SPORTO или -IRQ0

0 0 Таймер

Таблица 4.1г

Регистр состояния стека SSTAT

Раз- ряд Исход- ное состоя- ние Назначение

7 0 Стек циклов переполнен

6 1 Стек циклов пуст

42

Гпава 4. Программно-логическая модель

Раз- ряд Исход- ное состоя- ние Назначение

5 0 Стек состояний переполнен

4 1 Стек состояний пуст

3 0 Стек счетчика переполнен

2 1 Стек счетчика пуст

1 0 Стек счетчика команд переполнен

0 1 Стек счетчика команд пуст

Таблица 4.1д

Регистр управления прерываниями ICNTL

Раз- ряд Исход- ное состоя- ние Назначение

4 X Вложенность прерываний: 0 - запрещена, 1 - раз- решена

3 0 Не используется

2 X Чувствительность -IRQ2: 0 - уровень, 1 - фронт

1 X Чувствительность -IRQ1: 0 - уровень, 1 - фронт

0 X Чувствительность -IRQ0: 0 - уровень, 1 - фронт

Таблица 4.1 е

Регистр установки и сброса прерываний IFC (только запись)

Раз- ряд Исход- ное состоя- ние Назначение

15 0 Принудительная установка прерывания -IRQ2

14 0 Принудительная установка прерывания передатчика SPORTO

13 0 Принудительная установка прерывания приемника SPORTO

12 0 Принудительная установка прерывания -IRQE

43

Часть I. Схемотехника

Раз- ряд Исход- ное состоя- ние Назначение

11 0 Принудительная установка прерывания BDMA

10 0 Принудительная установка прерывания передатчика SPORT1 или -IRQ1

9 0 Принудительная установка прерывания приемника SPORTO или -IRQ0

8 0 Принудительная установка прерывания таймера

7 0 Сброс прерывания -IRQ2

6 0 Сброс прерывания передатчика SPORTO

5 0 Сброс прерывания приемника SPORTO

4 0 Сброс прерывания -IRQE

3 0 Сброс прерывания BDMA

2 0 Сброс прерывания передатчика SPORT1 или -IRQ1

1 0 Сброс прерывания приемника SPORTO или -IRQ0

0 0 Сброс прерывания таймера

X - произвольное состояние после сброса.

Блок арифметико-логического устройства ALU включает в себя:

• два 16-разрядных регистра операндов АХО и АХ1;

• два 16-разрядных регистра операндов AY0 и AY1;

• один 16-разрядный регистр результата AR;

• один 16-разрядный регистр обратной связи AF.

Все эти регистры имеют своих двойников - теневые регистры,

изображенные на рисунке программно-логической модели процес-

сора в виде теней. Переключение между основными и теневыми

регистрами производится программно.

Блок умножителя МАС включает в себя:

• два 16-разрядных регистра операндов МХО и МХ1;

• два 16-разрядных регистра операндов MY0 и MY1;

• два 16-разрядных регистра результата MR0 и MR1;

• один 8-разрядный регистра результата MR2;

• один 16-разрядный регистр обратной связи AMF.

Блок устройства сдвига SHIFTER включает в себя:

44

Гпава 4. Программно-логическая модель

• два 16-разрядных регистра результата SRO и SR1;

• один 5-разрядный регистр блочных операций SB;

• один 8-разрядный регистр экспоненты SE;

• один 16-разрядный регистр операнда SL

Так же как и в ALU, в блоках МАС и SHIFTER все регистры име-

ют своих двойников - теневые регистры.

Устройство обмена между шинами представляет собой 8-

разрядный регистр РХ, участвующий в пересылках между шинами

адреса и данных.

Остальные регистры процессора распределены между блоками

таймера, интерфейсной памяти, портов SPORTO и SPORT1, портов

IDMA и BDMA и блоком программируемых флагов.

Все эти регистры процессора доступны как ячейки памяти данных,

т.е. отображены на память данных процессора. Для таких регистров,

на рисунке программно-логической модели приведен адрес каждого

регистра в шестнадцатеричном виде, слева от его обозначения.

Всего в процессоре отведено тридцать две ячейки 16-разрядных

слов с адреса 0x3FE0 по адрес 0x3FFF для регистров такого типа.

Часть ячеек памяти для таких регистров не используется в рас-

сматриваемом процессоре ADSP-2181, но используется в других

процессорах семейства ADSP-21XX.

В табл. 4.2 приведено назначение разрядов всех регистров, ото-

браженных на память процессора.

Таблица 4.2а

Регистр управления системой SCR, адрес памяти данных = 0x3FFF

Разряд Исход- ное со- стояние Назначение

15...13 0 Не используются

12 0 Разрешение порта SPORTO: 0=порт запрещен, 1= порт разрешен

11 0 Разрешение порта SPORT1: 0=порт запрещен, 1 = порт разрешен

10 0 Конфигурация режима работы порта SPORT1: 0=сигналы Fl FO IRQO IRQ1 SCLK, ^последовательный порт SPORT1

9...3 0 Не используются

2...0 1 Циклы ожидания памяти программ от 0 до 7

45

Часть I. Схемотехника

Таблица 4.26

Регистр тактов ожидания WSR, адрес памяти данных=0хЗРРЕ

Разряд Исход- ное со- стояние Назначение

15 0 Не используется

14...12 1 Циклы ожидания памяти данных от 0 до 7

11...9 1 Циклы ожидания 3-й группы портов ввода-вывода от 0 до 7

8...6 1 Циклы ожидания 2-й группы портов ввода-вывода от 0 до 7

5...3 1 Циклы ожидания 1-й группы портов ввода-вывода от 0 до 7

2...0 1 Циклы ожидания 0-й группы портов ввода-вывода от 0 до 7

Таблица 4.2в

Регистры таймера

Разряд Исход- ное со- стояние Назначение

Регистр периода таймера TPERIOD, адрес памяти данных=ОхЗРРО

15...0 I...... X | Период таймера от 0 до OxFFFF

Регистр счетчика таймера TCOUNT, адрес памяти данных=0хЗРРС

15...0 I X | Счетчик таймера от 0 до OxFFFF

Регистр масштабирования таймера TSCALE, адрес памяти данных=0хЗРРВ

15...8 0 Не используются

7...0 X Масштабирование таймера от 0 до OxFF

Таблица 4.2г

Регистры последовательного порта SPORTO

Раз- ряд Исходное состояние Назначение

Регистр разрешения многоканального приема S0RW1, адрес памяти данных = 0x3FFA

15...0 X Разрешение приема канала 31... 16

46

Гпава 4. Программно-логическая модель

Раз- ряд Исходное состояние Назначение

Регистр разрешения многоканального приема S0RW0, адрес памяти данных = 0x3FF9

15...0 X Разрешение приема канала 15...0

Регистр разрешения многоканальной передачи S0TW1, адрес памяти данных=0хЗРР8

15...0 X Разрешение передачи канала 31... 16

Регистр разрешения многоканальной передачи S0TW0, адрес памяти данных=0хЗРР7

15...0 X Разрешение передачи канала 15...0

Регистр управления S0CR, адрес памяти данных=0хЗРР6

15 0 Разрешение многоканальное™: 0 - запрещено, 1 - разрешено

14 0 Разрешение внутреннего тактового генератора: 0 - запрещен, 1 - разрешен

13 0 Требование кадровой синхронизации приема: 0 - не требуется, 1 - требуется (в многока- нальном режиме - задержка)

12 0 Требование широкого кадрового импульса приемника: 0 - не требуется, 1 - требуется (в многока- нальном режиме - задержка)

11 0 Требование кадровой синхронизации передат- чика: 0 - не требуется, 1 - требуется (в многока- нальном режиме - задержка)

10 0 Требование широкого кадрового импульса передатчика: 0 - не требуется, 1 - требуется (в многока- нальном режиме - задержка)

9 0 Разрешение внутреннего тактового генератора передатчика: 0 - запрещен, 1 - разрешен (в многоканальном режиме - число каналов: 0-24 канала, 1 - 32 канала)

8 0 Разрешение внутреннего кадрового генерато- ра приемника: 0 - запрещено, 1 - разрешено

47

Часть I. Схемотехника

Раз- ряд Исходное состояние Назначение

7 0 Разрешение инвертирования кадрового гене- ратора передатчика: 0 - запрещено, 1 - разрешено (только в много- канальном режиме)

6 0 Разрешение инвертирования кадрового гене- ратора приемника: 0 - запрещено, 1 - разрешено

5, 4 0 Формат данных: 00 - выравнивание по правому краю, старшие биты=0, 01 - выравнивание по правому краю, старшие биты=знаку, 10 - компандирование по МЮ закону, 11 - компандирование по А закону

3...0 0 Длина слова минус 1

Регистр делителя тактовых импульсов S0CLKDIV, адрес памяти данных = 0x3FF5

15...0 0 Делитель частоты тактовых импульсов = (CLKOUT/2*SCLK)-1

Регистр делителя кадровых импульсов приемника S0RFDIV, адрес па- мяти данных=0хЗРБ4

15...0 0 Делитель частоты тактовых импульсов = (SCLK/RFS)-1

Регистр управления авто буферизацией S0ABUF, адрес памяти данных = 0X3FF3

15 0 Не используется

14 0 Бит разрешения CLKOUT

13 0 Не используется

12 0 Бит управления округлением со смещением

11...9 0 Номер индексного регистра передатчика

8, 7 0 Номер регистра модификатора передатчика

6...4 0 Номер индексного регистра приемника

3,2 0 Номер регистра модификатора приемника

1 0 Разрешение автобуферизации передатчика

0 0 Разрешение автобуферизации приемника

48

Гпава 4. Программно-логическая модель

Таблица 4.2д

Регистры последовательного порта SPORT1

Раз- ряд Исходное состояние Назначение

Регистр управления S1CR, адрес памяти данных=0хЗРР2

15 0 Флаг FO (только чтение)

14 0 Разрешение внутреннего тактового генератора: 0 - запрещен, 1 - разрешен

13 0 Требование кадровой синхронизации приема: 0 - не требуется, 1 - требуется

12 0 Требование широкого кадрового импульса приемника: 0 - не требуется, 1 - требуется

11 0 Требование кадровой синхронизации передат- чика: 0 - не требуется, 1 - требуется

10 0 Требование широкого кадрового импульса передатчика: 0 - не требуется, 1 - требуется

9 0 Разрешение внутреннего тактового генератора передатчика: 0 - запрещен, 1 - разрешен

8 0 Разрешение внутреннего кадрового генерато- ра приемника: 0 - запрещено, 1 - разрешено

7 0 Разрешение инвертирования кадрового гене- ратора передатчика: 0 - запрещено, 1 - разрешено

6 0 Разрешение инвертирования кадрового гене- ратора приемника: 0 - запрещено, 1 - разрешено

5, 4 0 Формат данных: 00 - выравнивание по правому краю, старшие биты=0, 01 - выравнивание по правому краю, старшие биты=знаку, 10 - компандирование по МЮ закону, 11 - компандирование по А закону

49

Часть I. Схемотехника

Раз- ряд Исходное состояние Назначение

3...0 0 Длина слова минус 1

Регистр делителя тактовых импульсов S1CLKDIV, адрес памяти дан- ных=0хЗРР1

15...0 0 Делитель частоты тактовых импульсов = (CLKOUT/2*SCLK)-1

Регистр делителя кадровых импульсов приемника S1RFDIV, адрес па- мяти данных=0хЗРР0

15...0 0 Делитель частоты тактовых импульсов = (SCLK/RFS)-1

Регистр управления автобуферизацией S1ABUF, адрес памяти дан- Hbix=0x3FEF

15 0 Блокирование вывода XTAL в режиме пони- женной мощности: 0 - активен, 1 - блокирован (этот вывод дол- жен быть блокирован, если к процессору под- ключен генератор, а не кварцевый резонатор)

14 0 Разрешение задержки запуска процессора из режима пониженной мощности на 4096 циклов: 0 - запрещено, 1 - разрешено

13 0 Принудительный вход в режим пониженной мощности: 0 - нормальный режим, 1 - режим понижен- ной мощности (осуществляется переход на вектор прерыва- ния пониженной мощности)

12 0 Принудительный перезапуск процессора при подаче питания: 0 - нормальный режим, 1 - программный пе- резапуск

11...9 0 Номер индексного регистра передатчика

8, 7 0 Номер регистра модификатора передатчика

6...4 0 Номер индексного регистра приемника

3, 2 0 Номер регистра модификатора приемника

1 0 Разрешение автобуферизации передатчика

0 0 Разрешение автобуферизации приемника

50

Гпава 4. Программно-логическая модель

Таблица 4.2е

Регистры управления программируемыми флагами

Разряд Исходное состояние Назначение

Регистр управления программируемыми флагами РРТУРЕ, адрес памя- ти данных=0хЗРЕ6

15 0 Не используется

14...12 1 Циклы ожидания байтовой памяти данных BDMA от 0 до 7