Author: Бойко В.И. Гуржий А.Н. Жуйков В.Я.

Tags: компьютерные технологии программирование микропроцессоры схемотехника микроконтроллеры электронные системы

ISBN: 5-94157-467-3

Year: 2004

Text

11010111

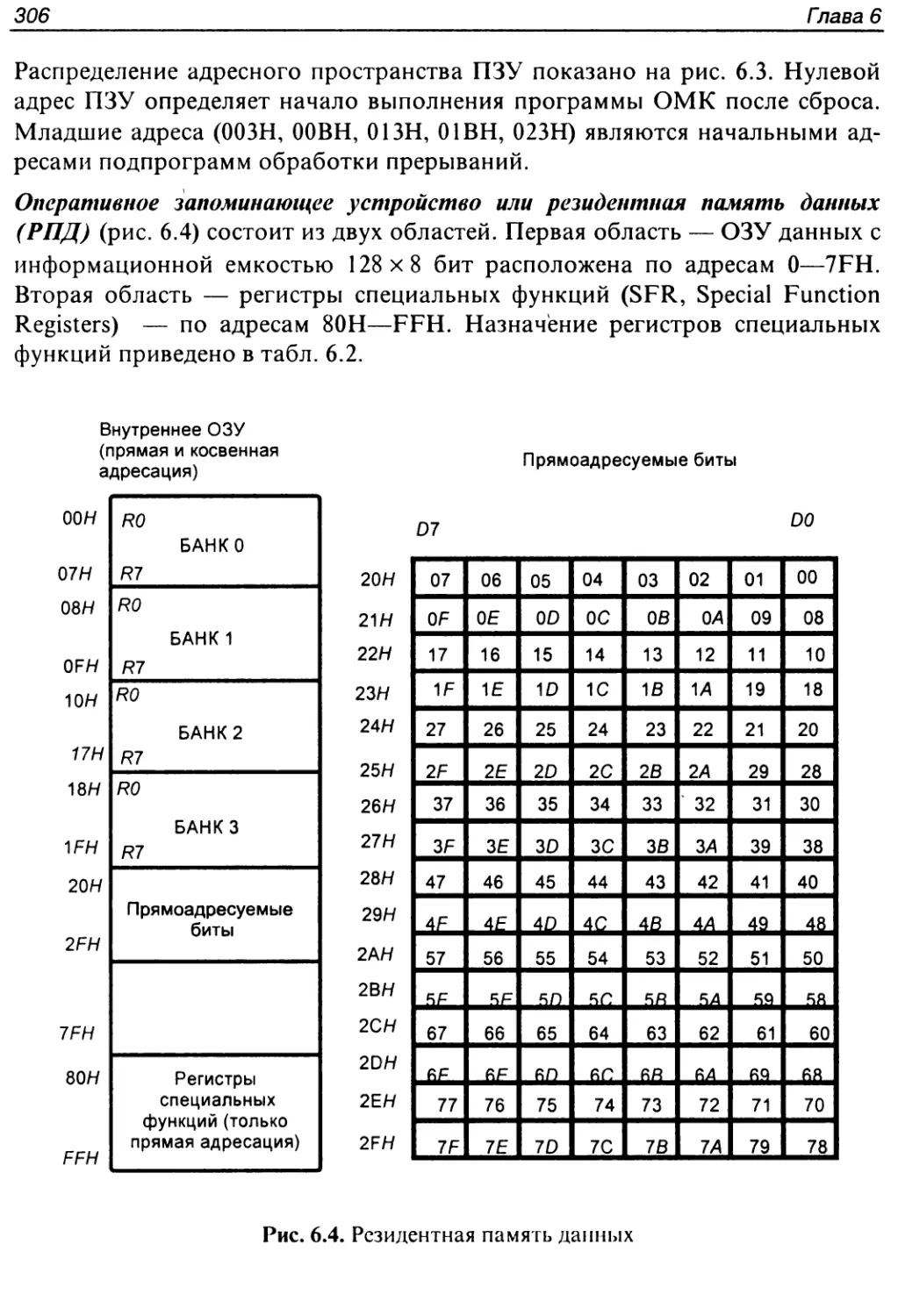

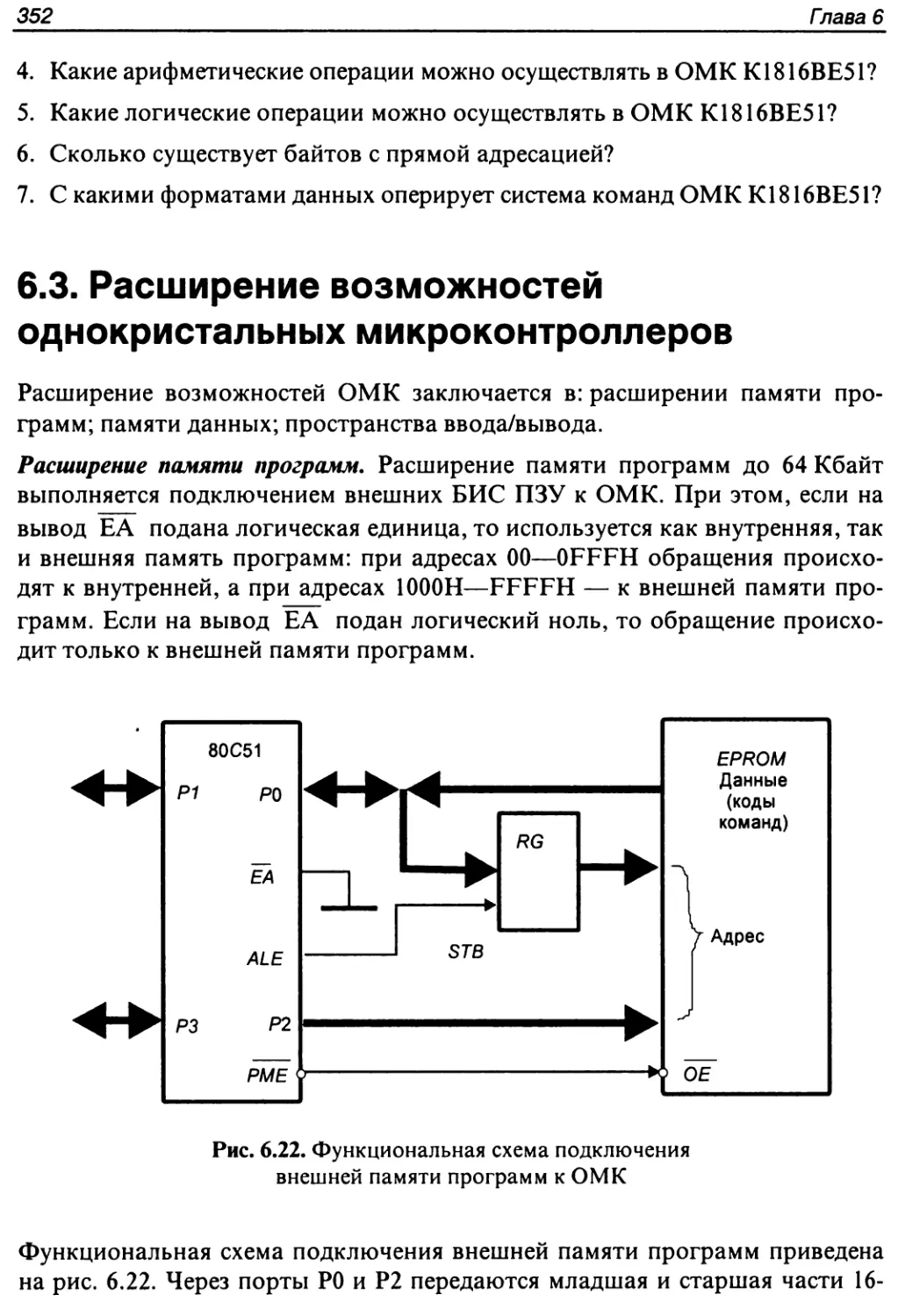

СХЕМОТЕХНИКА

ЭЛЕКТРОННЫХ

СИСТЕМ

Микропроцессоры

и микроконтроллеры

Особенности архитектуры

и функциональные возможности

В, 16, 32 и 64-разрядных процессоров

Системы команд языка Ассемблер

для разных типов микропроцессоров

Сигнальные и нейропроцессоры

СХЕМОТЕХНИКА

ЭЛЕКТРОННЫХ

СИСТЕМ

Микропроцессоры

и микроконтроллеры

Санкт-Петербург

«БХВ-Петербург»

2004

УДК 681.3(075.8)

ББК 32.973-02я73

Б72

Бойко В. И. и др.

Б72 . Схемотехника электронных систем. Микропроцессоры

и микроконтроллеры/Авторы: В. И. Бойко, А. Н. Гуржий,

В. Я. Жуйков, А. А. Зори, В. М. Спивак, Т. А. Терещенко,

Ю. С. Петергеря. — СПб.: БХВ-Петербург, 2004. — 464 с.: ил.

ISBN 5-94157-467-3

В книге рассматриваются следующие разделы курса: общие принципы

построения микропроцессорных систем, однокристальные микропроцессо-

ры, однокристальные микроконтроллеры, построение модулей памяти, сис-

темы ввода/вывода, сигнальные процессоры и нейронные вычислители.

Приведены примеры составления программ, проектирования микропроцес-

сорных систем, методы расширения возможностей системы. После каждого

подраздела есть контрольные вопросы.

Для студентов, преподавателей и специалистов

в области электронной и микропроцессорной техники

УДК 681.3(075.8)

ББК 32.973-02я73

Группа подготовки издания:

Главный редактор

Зам. главного редактора

Зав. редакцией

Редактор

Компьютерная верстка

Корректор

Дизайн обложки

Зав. производством

Екатерина Кондукова

Людмила Еремеевская

Григорий Добин

Анатолий Хрипов

Натальи Смирновой

Наталия Першакова

Игоря Цырульникова

Николай Тверских

Затверждено ММстерством осв!ти i науки УкраТни як пщручник

для студент1в вищих навчальних заклад1в

Лицензия ИД Na 02429 от 24.07.00. Подписано в печать 30.09.04.

Формат 70x1001/ie. Печать офсетная. Усл. печ. л. 37,41.

Тираж 3000 экз. Заказ No 3550

"БХВ-Петербург", 190005, Санкт-Петербург, Измайловский пр., 29.

Гигиеническое заключение на продукцию, товар No 77.99.02.953.Д.001537.03.02

от 13.03.2002 г. выдано Департаментом ГСЭН Минздрава России.

Отпечатано с готовых диапозитивов

в ГУП "Типография "Наука"

199034, Санкт-Петербург, 9 линия, 12

ISBN 5-94157-467-3 ° °МД Групп, 2004

© Оформление, издательство "БХВ-Петербург”, 2004

Содержание

Глава 1. Общие принципы построения микропроцессорных систем.......1

1.1. Основные понятия и определения.............................1

Контрольные вопросы...........................................3

1.2. Организация шин............................................3

Контрольные вопросы...........................................5

1.3. Принципы построения микропроцессорных систем...............5

Контрольные вопросы..........................................10

1.4. Архитектура микропроцессора...............................10

Контрольные вопросы..........................................14

1.5. Основы программирования на языке ассемблера...............14

Контрольные вопросы и задания................................34

Глава 2. Однокристальные микропроцессоры.........................37

2.1. Однокристальный 8-разрядный микропроцессор............... 37

Контрольные вопросы и задания................................54

2.2. Однокристальные 16-разрядные микропроцессоры..............55

Контрольные вопросы и задания................................80

2.3. Система команд МП /8086.................................. 81

Контрольные вопросы.........................................117

2.4. Построение модуля центрального процессора на базе i8086. 117

Контрольные вопросы и задания...............................124

Глава 3. Однокристальные универсальные микропроцессоры

(старшие модели)................................................125

3.1. Микропроцессор /80286....................................125

Контрольные вопросы и задания...............................140

3.2. Архитектура 32-разрядных микропроцессоров................140

Контрольные вопросы и задания...............................155

3.3. Особенности архитектуры микропроцессоров i386 и i486.... 155

Контрольные вопросы и задания...............................161

3.4. Особенности архитектуры микропроцессоров Pentium.........162

Контрольные вопросы и задания...............................178

3.5. Особенности архитектуры 64-разрядных микропроцессоров....179

Контрольные вопросы и задания...............................181

Глава 4. Построение модулей памяти микропроцессорных систем.....183

4.1. Классификация систем памяти..............................183

Контрольные вопросы и задания...............................186

IV

Содержание

4.2. Построение модуля постоянного запоминающего устройства..186

Контрольные вопросы и задания..............................190

4.3. Построение модуля оперативного запоминающего устройства

статического типа............................................191

Контрольные вопросы и задания..............................194

4.4. Построение модулей оперативного запоминающего устройства

динамического типа.......................................... 195

Контрольные вопросы и задания..............................199

4.5. Принципы организации кэш-памяти.........................199

Контрольные вопросы и задания..............................205

4.6. Принципы организации стековой памяти....................206

Контрольные вопросы и задания..............................209

Глава 5. Интерфейс устройств ввода/вывода......................211

5.1. Функции интерфейса ввода/вывода.........................211

Контрольные вопросы и задания..............................220

5.2. Программируемый параллельный интерфейс..................221

Контрольные вопросы и задания..............................234

5.3. Программируемый интерфейс клавиатуры и индикации........234

Контрольные вопросы и задания..............................249

5.4. Программируемый таймер................................. 249

Контрольные вопросы и задания..............................260

5.5. Архитектура и функциональные возможности контроллера

прямого доступа к памяти................................... 261

Контрольные вопросы и задания..............................269

5.6. Программируемый последовательный интерфейс..............270

Контрольные вопросы........................................279

5.7. Программируемый контроллер прерываний...................279

Контрольные вопросы и задания..............................293

5.8. Пример разработки микропроцессорной системы.............293

Глава 6. Однокристальные микроконтроллеры с CISC-архитектурой..301

6.1. Архитектура и функциональные возможности однокристальных

микроконтроллеров............................................301

Контрольные вопросы и задания..............................340

6.2. Система команд..........................................341

Контрольные вопросы и задания..............................351

6.3. Расширение возможностей однокристальных микроконтроллеров.352

Контрольные вопросы и задания..............................358

6.4. Применение однокристального микроконтроллера 83C51FA

для управления двигателем постоянного тока...................358

Контрольные вопросы и задания..............................363

6.5. Архитектура и функциональные возможности 16-разрядных

однокристальных микропроцессоров серии MCS 196/296.............364

Контрольные вопросы и задания................................376

Содержание

V

Глава 7. Однокристальные микроконтроллеры с RISC-архитектурой....377

7.1. Р1С-контроллеры...........................................377

Контрольные вопросы и задания................................384

7.2. Однокристальные AVR-микроконтроллеры......................385

Контрольные вопросы и задания................................391

7.3. Характеристики AVR-микроконтроллеров......................391

Контрольные вопросы и задания................................397

Глава 8. Сигнальные микропроцессоры..............................399

8.1. Сигнальные процессоры обработки данных в формате

с фиксированной запятой........................................400

Контрольные вопросы и задания................................408

8.2. Сигнальные процессоры обработки данных в формате

с плавающей запятой............................................409

Контрольные вопросы и задания................................417

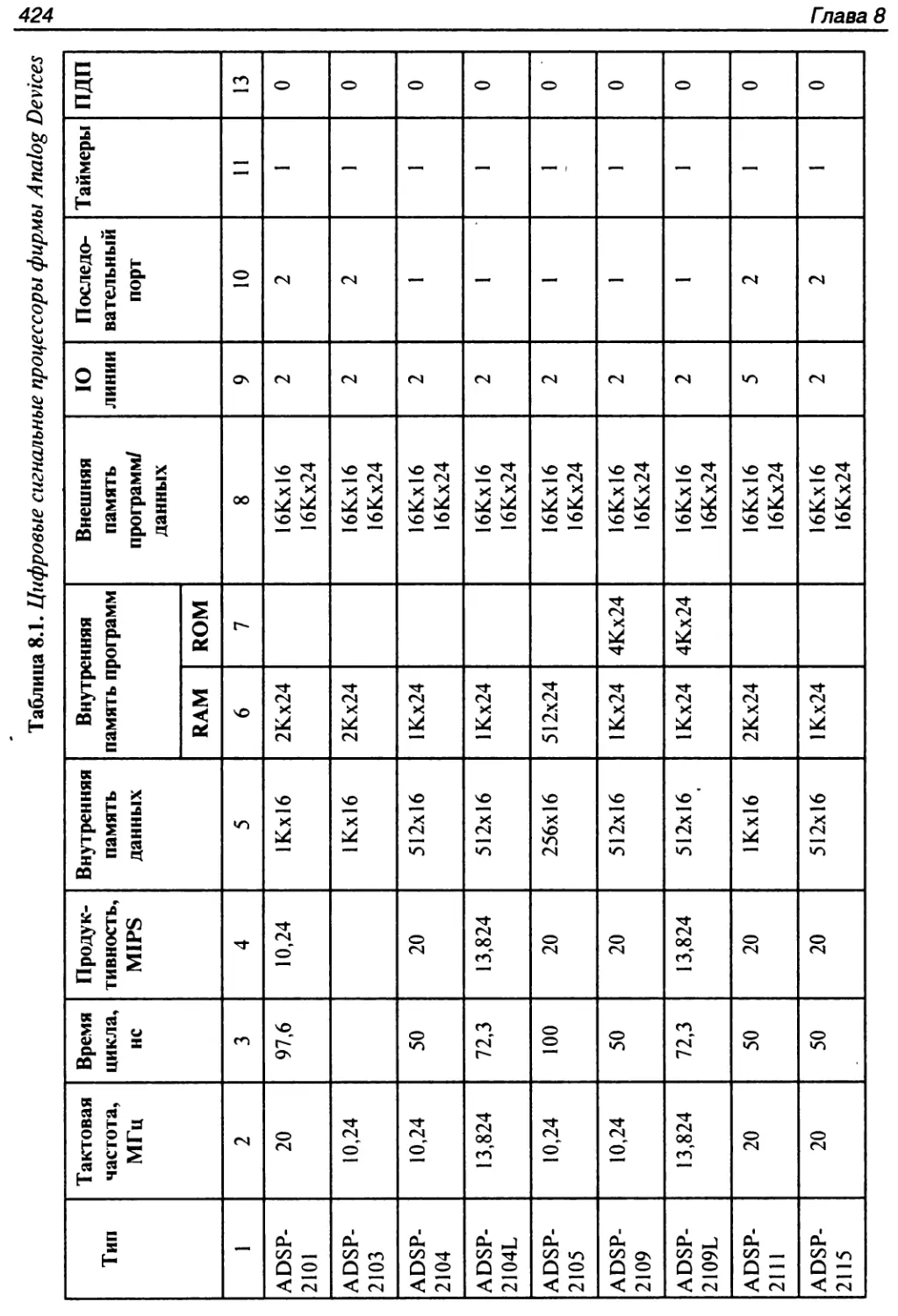

8.3. Технические характеристики сигнальных процессоров.........418

Контрольные вопросы и задания................................427

Глава 9. Нейронные вычислители...................................429

9.1. Основные понятия и задачи нейронных вычислителей..........429

Контрольные вопросы и задания................................435

9.2. Основы построения алгоритмов обучения нейронных сетей.....436

Контрольные вопросы и задания................................437

9.3. Аппаратная реализация нейронных вычислителей..............437

Контрольные вопросы и задания................................444

Список литературы и ресурсов Интернета...........................445

К главе 1......................................................445

К главе 2......................................................445

К главе 3......................................................446

К главе 4......................................................446

К главе 5......................................................446

К главе 6......................................................447

К главе 7......................................................447

К главе 8......................................................448

К главе 9......................................................448

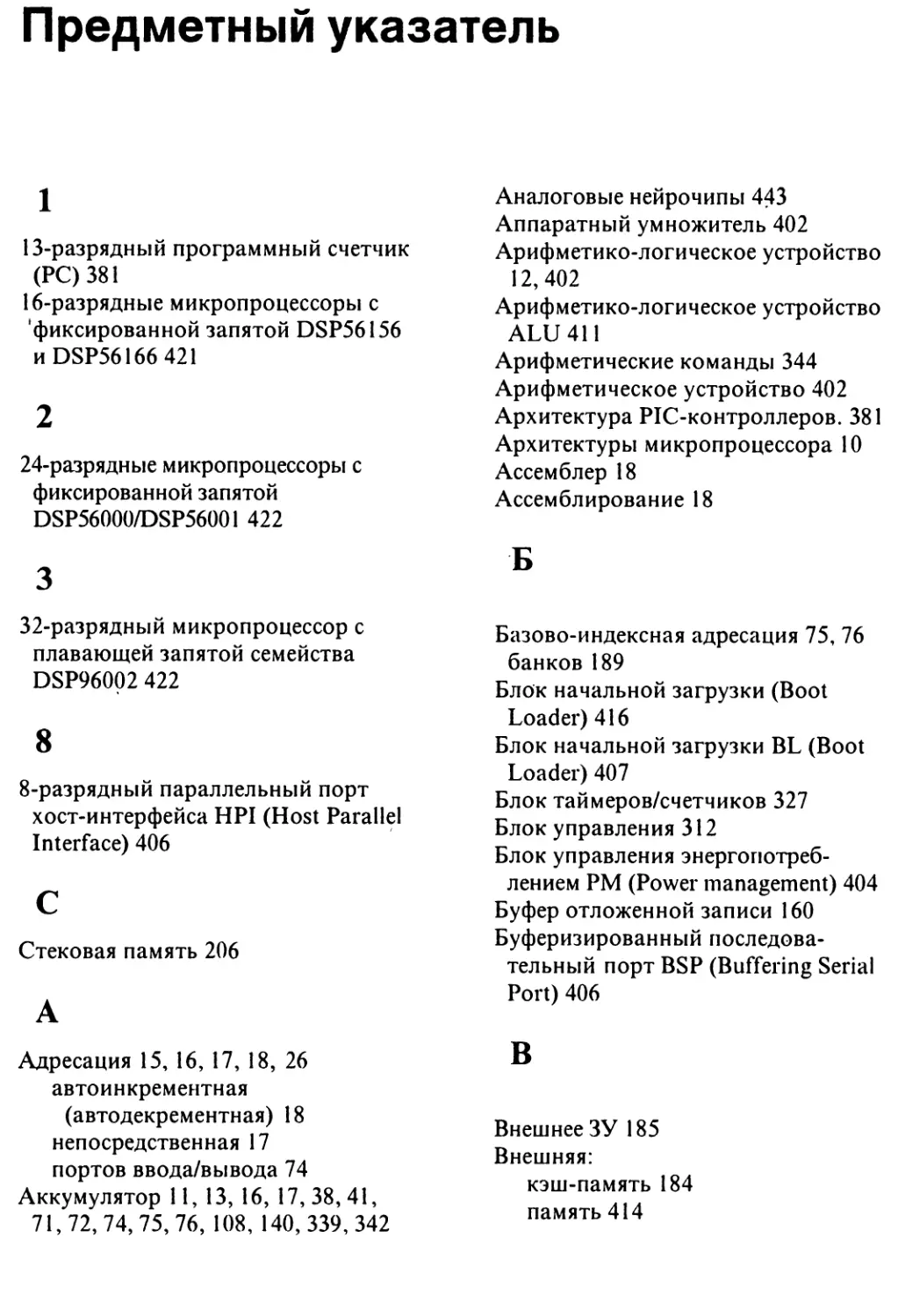

Предметный указатель.............................................449

Общие принципы построения

микропроцессорных систем

1.1. Основные понятия и определения

Микропроцессор (МП) — это устройство, которое осуществляет прием, об-

работку и выдачу информации. Конструктивно МП содержит одну или не-

сколько интегральных схем и выполняет действия, определенные програм-

мой, записанной в памяти.

Микропроцессорная система — это вычислительная, контрольно-измери-

тельная или управляющая система, основным устройством обработки ин-

формации в которой является МП. Микропроцессорная система строится из

набора микропроцессорных БИС.

Мультимикропроцессорная (или мультипроцессорная) система — система,

которая образуется объединением некоторого количества универсальных

или специализированных МП, благодаря чему обеспечивается параллельная

обработка информации и распределенное управлений.

Микропроцессорный комплект (МПК) — совокупность интегральных схем,

совместимых по электрическим, информационным и конструктивным па-

раметрам и предназначенных для построения электронно-вычислительной

аппаратуры и микропроцессорных систем управления. В типичный состав

МПК входят: БИС МП (один или несколько корпусов интегральных схем);

БИС оперативных запоминающих устройств (ОЗУ); БИС постоянных за-

поминающих устройств (ПЗУ); БИС интерфейсов или контроллеров внеш-

них устройств; служебные БИС (тактовый генератор, регистры, шинные

формирователи, контроллеры шин, арбитры шин).

Мйкропроцессоры и МПК классифицируют по таким признакам: назначе-

ние; количество БИС; способ управления; тип архитектуры; тип системы

команд.

2

Глава 1

По назначению МП разделяют на универсальные и специализированные.

Универсальными микропроцессорами являются МП общего назначения, кото-

рые решают широкий класс задач вычисления, обработки и управления.

Специализированные микропроцессоры предназначены для решения задач лишь

определенного класса. К специализированным МП относятся: сигнальные;

медийные, мультимедийные МП и транспьютеры.

Сигнальные процессоры предназначены для цифровой обработки сигналов в

реальном масштабе времени (например, для фильтрации сигналов, вычис-

ления свертки, вычисления корреляционной функции, ограничения и пре-

образования сигнала, выполнения прямого и обратного преобразования

Фурье). К сигнальным процесорам относятся процессоры компаний Texas

Instruments — TMS320C80, Analog Devices — ADSP2106x, Motorola —

DSP560xx и DSP9600x.

Медийные и мультимедийные процессоры предназначены для обработки ау-

диосигналов, графической информации, видеоизображений, а также для

решения ряда задач в мультимедиакомпьютерах, игровых приставках, бы-

товой технике. К медийным и мультимедийным процессорам относятся

процессоры компаний MicroUnity — Mediaprocessor, Philips — Trimedia,

Cromatic Reserch— Mpact Media Engine, Nvidia — NV1, Cyrix —MediaGX.

Транспьютеры предназначены для организации массовых параллельных

вычислений и работы в мультипроцессорных системах. Для них характер-

ным является наличие внутренней памяти и встроенного межпроцессорного

интерфейса, т. е. каналов связи с другими БИС МП. К транспьютерам отно-

сятся процессоры компании Inmos — Т-2, Т-4, Т-8, Т9000.

По количеству БИС в МПК различают многокристальные МПК и однокри-

стальные микроконтроллеры (ОМК). К многокристальным МПК относят

МПК с однокристальными и секционными МП.

Однокристальный микропроцессор — это конструктивно законченное изделие

в виде одной БИС. Другое название однокристальных МП — микропроцессоры

с фиксированной разрядностью данных. К этому типу относятся процессоры

компаний Intel — Pentium (Р5, Р6, Р7), AMD — К5, Кб, Cyrix — 6x86, Diqital

Equipment — Alpha 21064, 21164A, Silicon Graphics — MIPS R10000,

Motorola — Power PC 603, 604, 620, Hewlett-Packard — PA-8000, Sun Micro-

systems — Ultra SPARC II.

В секционных микропроцессорах в одной БИС реализуется лишь некоторая

функциональная часть (секция) процессора. Другое название секционных

МП — разрядно-модульные микропроцессоры или микропроцессоры с наращи-

ванием разрядности. Секционность БИС МП обуславливает значительную

гибкость МПС, возможность наращивания разрядности данных, создание

Общие принципы построения микропроцессорных систем

3

специфических технологических команд из набора микрокоманд. К секци-

онным относятся МП серий К589, К1804.

Однокристальный микроконтроллер представляет собой устройство, выпол-

ненное конструктивно в одном корпусе БИС и содержащее все основные

составные части МПК. К таким микроконтроллерам относятся ОМК ком-

паний Intel — MCS-196/296, MicroChip — PIC 17С4х PIC 17С75х, Mitsubishi

Electric — M3820, Motorola —MC33035, MC33039.

По способу управления различают МП со схемным и с микропрограммным

управлением. Микропроцессоры со схемным управлением имеют фиксирован-

ный набор команд, разработанный компанией-производителем, который не

может изменяться потребителем. В микропроцессорах с микропрограммным

управлением систему команд разрабатывают при проектировании конкрет-

ного МПК на базе набора простейших микрокоманд с учетом класса задач,

для решения которых предназначен МПК.

По типу архитектуры, или принципу построения, различают МП с фонней-

мановской архитектурой и МП с гарвардской архитектурой.

По типу системы команд различают CISC-процессоры (Complete Instruction

Set Computing) с полным набором команд и RISC-процессоры (Reduced

Instruction Set Computing) с уменьшенным набором команд.

Следует отметить, что многие МПК подпадают под разные классификаци-

онные признаки, поскольку способны решать задачи разных классов. Так,

существуют универсальные МП с мультимедийным расширением наборов

команд, например, Pentium MMX, Pentium П, Cyrix 6х86МХ, AMD Кб,

Ultra SPARC. В CISC-процессорах Pentium PRO реализовано ядро с RISC-

архитектурой.

Контрольные вопросы

1. Назовите составные части МПК.

2. По каким классификационным признакам делятся МП и МПК?

3. На какие задачи ориентированы специализированные МП?

4. Какие преимущества и недостатки имеют секционные МП по сравнению

с однокристальными?

1.2. Организация шин

Шина — это информационный канал, который объединяет все функцио-

нальные блоки МПС и обеспечивает обмен данными в виде двоичных чисел.

4

Глава 1

Конструктивно шина представляет собой п проводников и один общий

проводник (земля). Данные по шине передаются в виде слое. которые явля-

ются группами бит. -

В параллельной шине п бит информации передаются по отдельным линиям

одновременно, в последовательной шине — по одной линии последовательно

во времени. Параллельные шины выполняют в виде плоского кабеля, а по-

следовательные — в виде коаксиального или волоконно-оптического кабе-

ля. Коаксиальный кабель используют при передаче данных на расстояние

до 100 метров, согласовывая передающие и приемные каскады с волновым

сопротивлением линии. Волоконно-оптический кабель используют для пе-

редачи на большие расстояния.

Все основные блоки МПС соединены с единой параллельной шиной, кото-

рая называется системной шиной SB (System Bus). Системная шина содержит

три шины: адреса, данных и управления.

Шина адреса АВ (Address Bus) явлется однонаправленной. Она предназна-

чена для передачи адреса ячейки памяти или устройства ввода/вывода. На-

правление передачи по шине адреса — от МП к внешним устройствам. Ва-

рианты условных обозначений однонаправленной параллельной шины

показаны на рис. 1.1, где стрелка указывает направление передачи.

Рис. 1.1. Варианты условных обозначений

однонаправленной параллельной 16-разрядной шины

Число 16 на рис 1.1 обозначает разрядность шины. Допускается обозначе-

ние шин и без указания разрядности.

Шина данных DB (Data Bus) является двунаправленной. Она предназначена

для передачи данных между блоками МПС. Информация по одним и тем же

линиям DB может передаваться в двух направлениях — как к МП, так и от

него. Варианты условных обозначений двунаправленной шины показаны на

рис. 1.2.

Рис. 1.2. Варианты условных обозначений

двунапряавленной параллельной 8-разрядной шины

Общие принципы построения микропроцессорных систем

5

Шина управления СВ (Control Bus) предназначена для передачи управляю-

щих сигналов. Хотя направление управляющих сигналов может быть раз-

ным, однако шина управления не является двунаправленной, поскольку для

сигналов разного направления используются отдельные линии. Обозначает-

ся эта шина так же, как и однонаправленная (см. рис. 1.1).

Контрольные вопросы

1. Укажите назначение и составные части системной шины.

2. Назовите принципы передачи информации по шинам: адреса; данных;

управления.

3. Как передается информация по параллельным и последовательным шинам?

1.3. Принципы построения

микропроцессорных систем

В основу построения МПС-систем положено три принципа:

□ магистральности;

□ модульности;

□ микропрограммного управления.

Принцип магистральности определяет характер связей между функциональ-

ными блоками МПС — все блоки соединяются с единой системной шиной.

Принцип модульности состоит в том, что система строится на основе огра-

ниченного количества типов конструктивно и функционально законченных

модулей. Каждый модуль МПС имеет вход управления третьим (высокоим-

педансным) состоянием. Этот вход называется CS (Chip Select) — выбор

кристала, или ОЕ (Output Enable) — разрешение выхода.

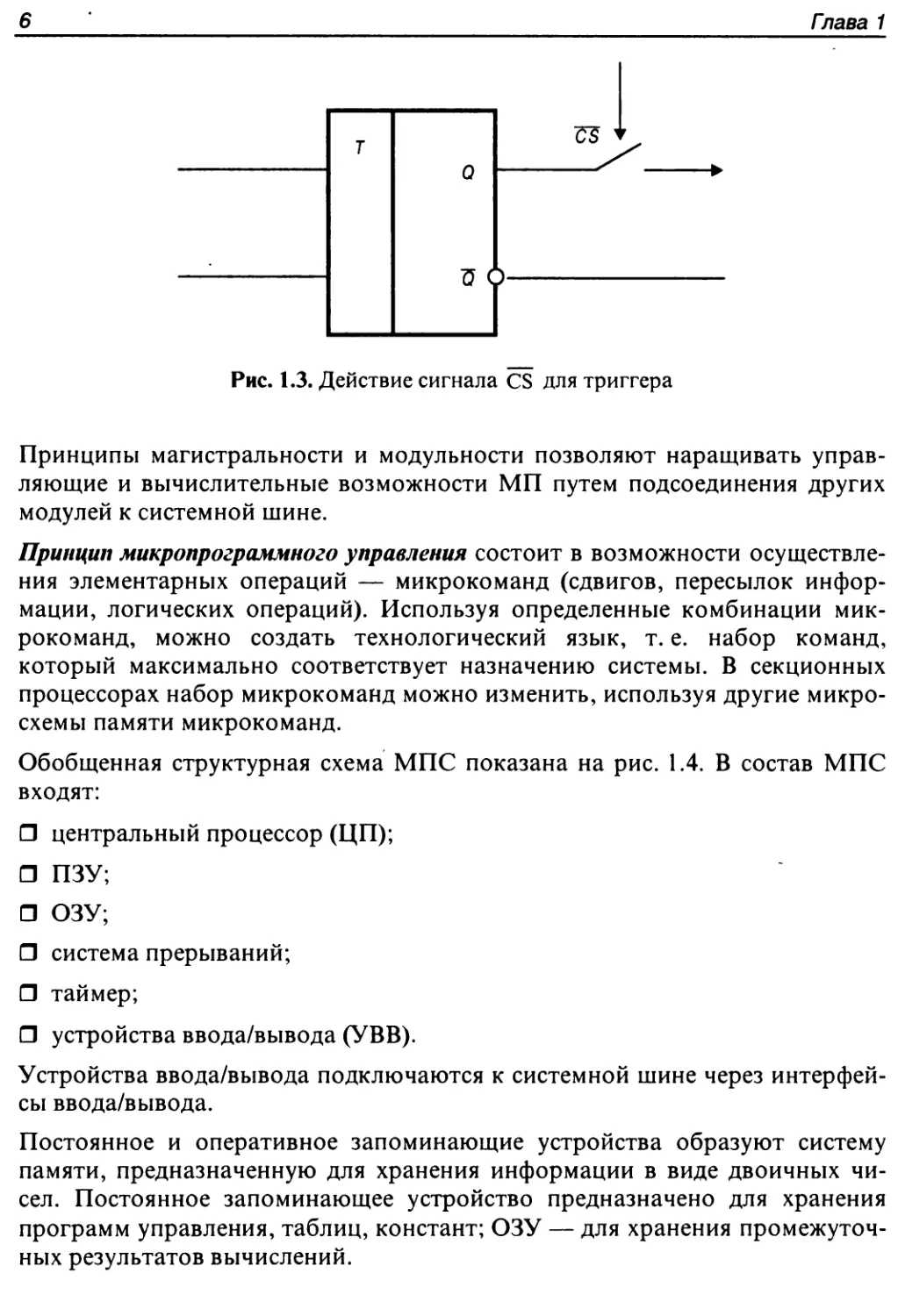

Действие сигнала CS для триггера показано на рис. 1.3. Выходной сигнал

триггера Q появится на выходе лишь при активном (в данном случае — ну-

левом) уровне сигнала CS. Если CS = 1, триггер переводится в высокоимпе-

дансное состояние. Выход тригера является трехстабильным, т. е. может

находиться в одном из трех состояний: логической единицы, логического

нуля или высокоимпедансном. В каждый момент времени к системной шине

МПС подсоединено лишь два модуля — передающий и принимающий ин-

формацию. Остальные модули находятся в высокоимпедансном состоянии.

6

Глава 1

Принципы магистральности и модульности позволяют наращивать управ-

ляющие и вычислительные возможности МП путем подсоединения других

модулей к системной шине.

Принцип микропрограммного управления состоит в возможности осуществле-

ния элементарных операций — микрокоманд (сдвигов, пересылок инфор-

мации, логических операций). Используя определенные комбинации мик-

рокоманд, можно создать технологический язык, т. е. набор команд,

который максимально соответствует назначению системы. В секционных

процессорах набор микрокоманд можно изменить, используя другие микро-

схемы памяти микрокоманд.

Обобщенная структурная схема МПС показана на рис. 1.4. В состав МПС

входят:

□ центральный процессор (ЦП);

□ ПЗУ;

□ ОЗУ;

□ система прерываний;

□ таймер;

□ устройства ввода/вывода (УВВ).

Устройства ввода/вывода подключаются к системной шине через интерфей-

сы ввода/вывода.

Постоянное и оперативное запоминающие устройства образуют систему

памяти, предназначенную для хранения информации в виде двоичных чи-

сел. Постоянное запоминающее устройство предназначено для хранения

программ управления, таблиц, констант; ОЗУ — для хранения промежуточ-

ных результатов вычислений.

Общие принципы построения микропроцессорных систем

7

Память организована в виде массива ячеек, каждая из которых имеет свой

адрес и содержит байт или слово. Байтом называется группа из 8 бит, а сло-

во может иметь любую длину в битах. Наиболее часто под словом понима-

ют двоичное число длиной два байта. Для обращения к ячейке памяти необ-

ходимо выдать ее адрес на шину адреса. На рис. 1.5 изображена структура

памяти с 8 однобайтными ячейками, где каждому адресу отвечает опреде-

ленное содержимое ячейки. Так, ячейка с адресом ООО имеет содержимое

010111112 = 5F16.

Рис. 1.4. Обобщенная структурная схема

микропроцессорной системы управления

Сегментом называется область памяти, которая начинается с любого адреса,

кратного 16, и занимает до 64 Кбайт. Существуют три основных сегмента:

□ сегмент кодов;

□ сегмент данных;

□ сегмент стека.

8

Глава 1

Адрес Данные

ООО 01011111

001 00010011

010 01110111

011 00001100

100 00000000

101 11111111

110 10101010

111 11110000

Рис. 1.5. Структура памяти из 8 однобайтных ячеек

Сегмент кодов содержит коды команд, которые адресуются сегментным ре-

гистром кодов CS и регистром — указателем команд IP (Instruction Pointer).

Регистр CS определяет начальный адрес сегмента кодов, а регистр IP —

смещение в сегменте (расстояние от начала сегмента до ячейки, в которой

находится адрес команды).

Сегмент данных содержит данные, константы и рабочие области, необхо-

димые для выполнения программы. Начальный адрес сегмента данных со-

держится в регистре DS, а смещение в сегменте задается командой.

Сегмент стека содержит адрес возврата из подпрограмм и данные. Регистр

SS содержит начальный адрес сегмента стека, а регистр SP — смещение в

сегменте.

Некоторые операции используют дополнительный сегмент данных, началь-

ный адрес которого задается регистром ES, а смещение в сегменте опреде-

ляется командой.

Двухбайтное смещение (16 бит) может находиться в пределах от 000016 до

FFFFi6. Для обращения к любому адресу в программе выполняется сложе-

ние адресов, которые находятся в регистре сегмента и смещения. Например,

первый байт в сегменте кодов имеет смещение ноль, второй байт - единицу

и т. д. до FFFFi6.

Конкретный адрес команды (для сегмента кодов), ячейки памяти (для сег-

мента данных и дополнительного сегмента) или ячейки стека (для сегмента

стека) определяется результатом сложения адреса сегмента, который нахо-

дится в соответствующем регистре, и смещения.

Общие принципы построения микропроцессорных систем

9

Модуль центрального процессора осуществляет обработку данных и управ-

ляет всеми остальными модулями системы. Центральный процессор, кроме

БИС МП, содержит схемы синхронизации и интерфейса с системной шиной.

Он осуществляет выборку кодов команд из памяти, дешифрует их и выпол-

няет. В течение времени выполнения команды — командого цикла — ЦП

выполняет такие действия:

1. Выставляет адрес команды на шину адреса АВ.

2. Получает код команды из памяти и дешифрует его.

3. Вычисляет адрес операнда и считывает данные.

4. Выполняет операцию, определенную командой.

5. Воспринимает внешние управляющие сигналы, например, запрос преры-

ваний.

6. Генерирует сигналы состояния и управления, необходимые для работы

памяти и УВВ.

Устройства ввода/вывода или внешние устройства — это устройства, пред-

назначенные для ввода информации в МП или вывода информации из него.

Примерами УВВ являются дисплеи, печатающие устройства, клавиатура,

цифро-аналоговый и аналогоцифровой преобразователи, реле, коммутато-

ры. Для соединения УВВ с системной шиной их сигналы должны соответст-

вовать определенным стандартам, что реализуется с помощью интерфейсов

ввода/вывода.

Интерфейсы ввода/вывода называют также контроллерами или адаптерами.

Микропроцессор обращается к интерфейсам с помощью специальных ко-

манд ввода/вывода. При этом МП выставляет на шину адреса АВ адрес ин-

терфейса, а по шине данных DB считывает данные с устройства ввода или

записывает в устройство вывода. На рис. 1.5 показаны один интерфейс вво-

да и один интерфейс вывода.

Система прерываний позволяет МПС реагировать на внешние сигналы —

запросы прерываний, источниками которых могут быть: сигналы готовно-

сти от внешних устройств, сигналы от генераторов, сигналы с выходов дат-

чиков. При появлении запроса на прерывание ЦП прекращает выполнение

основной программы и переходит к выполнению подпрограммы обслужи-

вания запроса прерывания. Для построения системы прерываний МПК со-

держат БИС специальных программируемых контроллеров прерываний.

Таймер предназначен для реализации функций, связанных с отсчетом вре-

мени. После того как МП загружает в таймер число, задающее частоту,

задержку или коэффициент деления, таймер реализует необходимую

функцию.

10

Глава 1

Контрольные вопросы

1. Назовите принципы построения МПС и охарактеризуйте их.

2. Приведите типовую структуру МПС и объясните назначения функцио-

нальных модулей.

3. Объясните назначение входа управления третьим состоянием.

1.4. Архитектура микропроцессора

Понятие архитектуры микропроцессора определяет его составные части, а

также связи и взаимодействие между ними. Архитектура включает:

□ структурную схему МП;

□ программную модель МП (описание функций регистров);

□ информацию об организации памяти (емкость и способы адресации па-

мяти);

□ описание организации процедур ввода/вывода.

Существуют два основных типа архитектуры — фоннеймановская и гар-

вардская. Фоннеймаиовскую архитектуру (рис. 1.6, а) предложил в 1945 году

американский математик Джо фон Нейман. Особенностью этой архитекту-

ры является то, что программа и данные находятся в общей памяти, доступ

к которой осуществляется по одной шине данных и команд.

Гарвардская архитектура впервые была реализована в 1944 году в релейной

вычислительной машине Гарвардского университета (США). Особенностью

этой архитектуры является то, что память данных и память программ раз-

делены и имеют отдельные шину данных и шину команд (рис. 1.6, 6), что

позволяет повысить быстродействие МП системы.

Структурные схемы обоих типов архитектур содержат: процессорный эле-

мент, память, интерфейсы ввода/вывода (ИВВ) и УВВ.

Память и ИВВ для разных типов МП могут быть как внутренними, т. е.

размещаться на том же кристалле, что и процессорный элемент, так и внеш-

ними. Процессорный элемент содержит регистры, арифметико-логическое

устройство (АЛУ), устройство управления и выполняет функции обработки

данных и управления процессами обмена информацией. Память обеспечи-

вает хранение данных и кодов команд программы. Интерфейсы вво-

да/вывода предназначены для связи с УВВ, например, с клавиатурой, дис-

плеем, печатающими устройствами, датчиками. Все элементы структурной

схемы соединены с помощью шин.

Общие принципы построения микропроцессорных систем

11

Память

Шина j к

адреса

Шина данных

и команд

Процессорный элемент

Регистры

АЛУ

Устройство

управления

Рис. 1.6. Основные типы архитектуры:

а — фоннейманвская; б — гарвардская

Расширенная структурная схема с процессором фоннеймановской архитектуры

показана на рис. 1.7. Схема процессора содержит устройство управления,

АЛУ и регистры: адреса, данных, команд, а также состояния, аккумулятор,

указатель команд и указатель стека.

Устройство управления вырабатывает управляющие сигналы для всех бло-

ков структурной схемы МП в соответствии с кодами команд, внешними

управляющими сигналами и сигналами синхронизации, а также управляет

обменом информацией между МП, памятью и УВВ. Устройство управления

реализует такие функции: начальная установка МП, синхронизация, прерыва-

ния, согласование быстродействия модулей МПС.

Функция начальной установки МП. Внешний сигнал начальной установки

процессора RESET формируется при включении источника питания МП

или при нажатии кнопки RESET. При появлении этого сигнала устройство

управления обеспечивает загрузку нулевого значения в указатель команд, кото-

рый инициирует выборку из памяти байта команды с нулевым адресом.

В конце выборки содержимое указателя команд увеличивается на единицу,

и выбирается байт команды со следующйм адресом. Таким образом выпол-

няется вся записанная в памяти программа.

12

Глава 1

Рис. 1.7. Структурная схема МПС

с процессором фоннеймановской архитектуры

Функция синхронизации. В соответствии с внешними управляющими сигна-

лами и сигналами синхронизации устройство управления синхронизирует

работу всех блоков МП.

Функция прерываний. С поступлением сигнала прерывания устройство уп-

равления инициирует выполнение подпрограммы обработки соответст-

вующего прерывания. Потребность в реализации функций прерываний воз-

никает тогда, когда во время выполнения основной программы надо пере-

вести МП на решение другой задачи, например, обработки аварийной

ситуации или работы с УВВ.

Функция согласования быстродействия модулей микропроцессорной системы.

Во время обслуживания памяти и УВВ, быстродействие которых значитель-

но меньше, чем у МП, согласование быстродействия реализуется генераци-

ей тактов ожидания МП. Во время обслуживания устройств с большим бы-

стродействием, чем у МП, используется режим прямого доступа к памяти.

Арифметико-логическое устройство представляет собой комбинационную

схему на основе сумматора, которая сигналами с выходов устройства

Общие принципы построения микропроцессорных систем

13

управления настраивается на выполнение определенной арифметической

или логической операции: сложение, вычитание, логическое И, логическое

ИЛИ, логическое НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ, сдвиг, сравнение, десятич-

ная коррекция. Таким образом, АЛУ выполняет арифметические или логи-

ческие операции над операндами, которые пересылаются из памяти и/или

регистров МП. Операнд — это объект в виде значения данных, содержимого

регистров или содержимого ячейки памяти, с которым оперирует команда. На-

пример, в команде сложения операндами являются слагаемые. Операнд мо-

жет задаваться в команде в виде числа либо находиться в регистре или

ячейке памяти. Полученный после выполнения команды в АЛУ результат

пересылается в регистр или ячейку памяти.

Регистры предназначены для хранения n-разрядного двоичного числа. Они

представляют собой п триггеров со схемами управления чтением/записью и

выборки. Регистры создают внутреннюю память МП и используются для

хранения промежуточных результатов вычислений.

Аккумулятор — это регистр, в котором хранится один из операндов. После

выполнения команды в аккумуляторе вместо операнда размещается резуль-

тат операции. В 8-разрядных процессорах аккумулятор принимает участие

во всех операциях АЛУ. В 16-разрядных МП большинство команд выпол-

няется без участия аккумулятора, однако в некоторых командах (ввод, вы-

вод, умножение, деление) аккумулятор действует так же, как и в 8-

разрядных МП, т. е. сохраняет один из операндов, а после выполнения ко-

манды — результат операции.

Указатель команд или программный счетчик' предназначен для хранения

адреса ячейки памяти, которая содержит код следующей команды. Про-

грамма действий МП записана в памяти в виде последовательности кодов

команд. Для перехода к следующей команде содержимое счетчика увеличи-

вается на единицу в момент выборки команды из памяти. Таким образом, в

конце выполнения команды в счетчике команд хранится адрес следующей

команды.

Указатель стека — это регистр, который хранит адрес последней занятой

ячейки стека. Стеком или стековой памятью называется область памяти,

которая организована по принципу "последним пришел — первым вышел".

Регистр команд хранит код команды на протяжении всего времени выпол-

нения команды.

Регистр адреса и регистры данных предназначены для хранения адресов и

данных, используемых во время выполнения текущей команды в МП.

1 В литературе используются два обозначения этого регистра. Обычно в МП используют

обозначение IP (Instruction Pointer) — указатель команд, а в однокристальных микро-

ЭВМ и микроконтроллерах — PC (Program Counter) — программный счетчик.

14

Глава 1

Регистр состояния или регистр флагов (признаков) предназначен для хра-

нения информации о результате операции в АЛУ и представляет собой не-

сколько триггеров, выходы которых находятся в единичном или нулевом

состоянии. Например, флаг нуля устанавливается в единицу при нулевом

результате операции.

Контрольные вопросы

1. Дайте определение архитектуры МП.

2. Укажите различия между гарвардской и фоннеймановской архитектурами.

3. Какие функции выполняет устройство управления?

4. Что определяет содержимое счетчика команд? Как оно изменяется?

5. Чем отличается аккумулятор от других регистров МП?

1.5. Основы программирования

на языке ассемблера

Программа представляет собой последовательность команд, выполнение

которых приводит к решению задачи.

Команда определяет операцию, которую выполняет МП над данными.

Команда содержит в явной или неявной форме информацию о том, где бу-

дет помещен результат операции, а также об адресе следующей команды.

Код команды состоит из нескольких частей, которые называются полями.

Состав, назначение и расположение полей называется форматом команды.

В общем случае формат команды содержит операционную и адресную час-

ти. Операционная часть содержит код операции (например, сложение, ум-

ножение, передача данных). Адресная часть состоит из нескольких полей и

содержит информацию об адресах операндов, результата операции и сле-

дующей команды. Формат команды, в котором адресная часть состоит из

двух полей (признака адресации и адреса операндов), показан на рис. 1.8.

Код операции (л? разрядов) Признак адресации (к разрядов) Адреса операндов (л разрядов)

Операционная часть

Адресная часть

Рис. 1.8. Формат команды

Общие принципы построения микропроцессорных систем

15

Поле "признак адресации" определяет способ адресации операнда. Биты

полей "Признак адресации" и "Адрес операндов" в совокупности определя-

ют ячейки памяти, в которых хранятся операнды.

Различают такие группы команд:

□ команды передачи данных;

□ команды ввода/вывода;

□ команды обработки информации (арифметические, логические, сдвиг,

сравнение операндов, десятичная коррекция);

□ команды управления порядком выполнения программы (переход, вызов

подпрограмм, возврат из подпрограмм, прерывания);

□ команды задания режимов работы МП.

Общее количество бит в коде команды называется длиной формата. Количе-

ство двоичных разрядов m в поле "код операции" обеспечивает возможность

представления всех операций, которые выполняет МП. Если МП выполняет

М разных операций, то количество разрядов m определяется так:

т > log 2 М.

Если память содержит S ячеек, то количество разрядов п в поле "Адреса

операндов", необходимое для записи адреса одного операнда, составляет:

т > log 2 S.

Длина формата команды определяет скорость выполнения команды и зави-

сит от способа адресации операндов. Существуют следующие способы ад-

ресации: прямая; косвенная; непосредственная; автоинкрементная (авто-

декрементная); страничная; индексная; относительная.

□ Прямая адресация. При прямой адресации адрес операнда указан непо-

средственно в команде. В качестве примера рассмотрим команду МП

К580ВМ80А (i8080) прямой загрузки аккумулятора содержимым ячейки

памяти, расположенной по адресу 001216. Формат и схема выполнения

этой команды показаны на рис. 1.9.

В байте 1 команды (рис. 1.9, а) находится код команды пересылки дан-

ных в аккумулятор из ячейки памяти, а в байтах 2 и 3 — адрес ячейки па-

мяти. В байте 2 расположен младший (121б), а в байте 3 — старший (001б)

байты адреса.

На рис. 1.9, б ячейка памяти с адресом 0012|б имеет содержимое

110101112. Содержимое акумулятора до выполнения команды составляет

ООООООООг. После выполнения команды значение содержимого ячейки

памяти копируется в аккумулятор.

16

Глава 1

Байт 1

Байт 3

Код операции 12,. оо16

Операционная часть Адресная часть

а

Память

Адреса Содержимое ячеек

ячеек

б

Рис. 1.9. Команда прямой загрузки в аккумулятор содержимого ячейки памяти:

a — формат команды; б — схема выполнения

□ Косвенная адресация. При косвенной адресации в формате команды ука-

зывается регистр, в котором хранится адрес ячейки памяти, содержащей

операнд. Для хранения 16-разрядного адреса в 8-разрядном процессоре

8-разрядные регистры объединяются в регистровые пары. В первом реги-

стре регистровой пары хранится старший байт адреса, а во второй —

младший байт. Номер регистровой пары, в которой хранится адрес, яв-

ляется двуразрядным двоичным числом, поэтому он размещается в од-

нобайтной2 команде вместе с кодом команды.

На рис. 1.10 показан пример выполнения команды МП К580ВМ80А кос-

венной загрузки в аккумулятор содержимого ячейки памяти с адресом

001216, который хранится в регистровой паре DE. Команда косвенной за-

грузки аккумулятора является однобайтной и, кроме кода операции, со-

держит номер 01 регистровой пары DE. Старшая часть адреса ячейки па-

мяти (001б) хранится в регистре D, а младшая часть (12|б) — в регистре Е.

2 Команда, длина формата которой 1 байт.

Общие принципы построения микропроцессорных систем

17

Содержимое регистровой пары передается в регистр адреса МП, в ре-

зультате чего содержимое 110101112 ячейки с адресом 001216 копируется в

аккумулятор.

□ Непосредственная адресация. В первом байте команды с непосредствен-

ной адресацией размещается код операции. Значения операндов заносят-

ся в команду во время программирования и находятся во втором или

втором и третьем байтах. Этими значениями в основном являются неко-

торые константы, заранее известные программисту. В процессе выполне-

ния программы значения операндов остаются неизменными, поскольку

они вместе с командой размещаются в ПЗУ. Использование такого спо-

соба не требует адресов операндов.

В качестве примера на рис. 1.11 изображены формат и схема выполнения

команды непосредственной загрузки аккумулятора значением 110101 И 2,

которое хранится во втором байте команды. После выполнения команды

это число копируется в аккумулятор. При каждом очередном обращении

к этой команде в аккумулятор записывается такое же число.

Код операции 01

a

б

Рис. 1.10. Команда косвенной загрузки аккумулятора:

а — формат команды; б — схема выполнения

18

Глава 1

Рис. 1.11. Команда непосредственной загрузки аккумулятора

□ Автоинкрементная (автодекрементная) адресация. При автоинкремент-

ной адресации адрес операнда вычисляется так же, как и при косвенной

адресации, после чего осуществляется увеличение содержимого регистра:

на один — для обращения к следующему байту, на два — для обращения

к следующему слову. Размер операнда определяется кодом операции.

□ Страничная адресация. Во время использования страничной адресации

память делится на ряд Страниц одинаковой длины. Адресация страниц

осуществляется по содержимому программного счетчика или отдельного

регистра страниц. Адресация памяти внутри страниц осуществляется ад-

ресом, который содержится в команде.

□ Индексная адресация. Для преобразования адреса операнда к значению ад-

ресного поля команды прибавляется значение содержимого индексного

регистра, которое называется индексом.

□ Относительная адресация. При относительной адресации адрес операнда

определяется сложением содержимого программного счетчика или дру-

гого регистра с указанным в команде числом. Содержимое программно-

го счетчика или другого регистра называется базовым адресом. Для хра-

нения базовых адресов в МП могут быть предусмотренны базовые

регистры или специально выделенные ячейки памяти. Тогда в адресном

поле команды указывается номер базового регистра.

В МПС используется программирование на языке ассемблера. Ассемблером

называется и язык программирования в мнемокодах команд, и специальная

программа-транслятор, которая переводит (транслирует) мнемокоды в ма-

шинные коды, считываемые микропроцессором из памяти программ, де-

шифрируемые и выполняемые. Процесс перевода в машинные коды называ-

ется ассемблированием.

Общие принципы построения микропроцессорных систем

19

Программа на языке ассемблера содержит два типа выражений:

□ команды, которые транслируются в машинные коды;

□ директивы, которые управляют ходом трансляции.

Выражение имеет вид:

{(метка)}: (мнемокод) {(операнд)}{,}{( операнд )}{; комментарий}.

В фигурных скобках приведены элементы выражения, которых может не

быть в некоторых командах. Метка, мнемокод и операнды отделяются хотя

бы одним пробелом или табуляцией. Максимальная длина строки составля-

ет 132 символа, однако наиболее часто используются строки из 80 символов,

что соответствует длине экрана.

Примеры команд ассемблера'.

Метка Мнемокод Операнд(ы) Комментарии

MOV AX, 0 ; команда, два операнда

Ml: ADD AX, BX ; метка, команда, два операнда

DELAY: MOV CX, 1234 ; метка, команда, два операнда

Пример директивы'.

Метка Мнемокод Операнд(ы) Комментарии

COUNT: DB 1 ; метка, команда, один операнд

Метка на языке ассемблера является символическим адресом команды.

Метками обозначаются не все команды, а лишь те, к которым надо выпол-

нять переход с помощью команд переходов или вызовов подпрограмм. По-

сле метки ставится двоеточие. Первым символом в метке может быть буква

или один из специальных символов: вопросительный знак точка знак

амперсанд подчеркивание "_";знак доллара "$". Вопросительный знак

и точка могут занимать только первое место. Максимальная длина метки — 31

символ. Примеры меток: COUNT, PAGE25, $Е10. Рекомендуется использо-

вать описательные и смысловые метки. Все метки в программе должны быть

уникальными, т. е. не может быть нескольких команд с одинаковыми мет-

ками. Нельзя использовать в качестве меток зарезервированные ассембле-

ром слова, к которым принадлежат коды команд, директивы, имена регист-

ров. Например, имена АХ, DI и AL являются зарезервированными и

используются только для указания соответствующих регистров. В командах

переходов или вызовов подпрограмм обозначения метки используется как

операнд — символический адрес перехода, например:

Метка Мнемокод Операнд(ы) Комментарии

JMP CALL Ml DELAY ; переход к команде с меткой Ml ; вызов подпрограммы с меткой ; DELAY

20

Глава 1

Мнемокод идентифицирует команду ассемблера. Для мнемокодов исполь-

зуют сокращенные или полные английские слова, которые передают значе-

ния основной функции команды: ADD — прибавить, SUB (SUBtract) ---

вычесть, XCHG (eXCHanGe) — поменять.

Операнды отделяются запятыми. Если заданы два операнда, то первый из

них всегда является источником, а второй — приемником информации.

Команда может содержать различное количество операндов разных типов,

например:

Метка Мнемокод Операнд(ы) Комментарии

RET INC ADD MOV ex AX, 12H BX, [SI] ; возврат (операнды не указанные) ; увеличить СХ (один операнд) ; прибавить 12Н к содержимому АХ ; (два операнда) ; занести в регистр ВХ число из ; ячейки памяти с адресом DS:SI ; (два операнда)

Комментарии игнорируются в процессе трансляции и используются для до-

кументирования и лучшего понимания содержания программы. Коммента-

рий всегда начинается с символа и может содержать любые символы.

Комментарий может занимать всю строку или быть расположенным за

командой в одной строке, например:

Мнемокод Операнд(ы) Комментарии

ADD АХ, ВХ ; эта строка является комментарием. ; команда и комментарий в одной строке.

Поскольку комментарии не транслируются в машинные коды, то их количе-

ство не влияет на эффективность выполнения программы.

Программа на языке ассемблера называется начальной программой или на-

чальным программным модулем. Ассемблирование или перевод начальной

программы в машинные коды выполняет программа-транслятор, например,

TASM.CQM. В зависимости от установок, задаваемых пользователем, про-

грамма переводит начальный модуль в один из двух программных модулей:

командный модуль (файл с расширением СОМ) или объектный модуль

(файл с расширением OBJ).

Командный модуль содержит машинные коды команд с абсолютными адре-

сами и выполняется микропроцессором. Командный модуль целесообразно

использовать в тех случаях, когда емкость программы не превышает разме-

ра одного сегмента (64 Кбайт). Первым оператором командного модуля яв-

ляется директива ORG 100Н (ORIGIN — начало), которая располагает пер-

Общие принципы построения микропроцессорных систем

21

вую команду программы в сегменте кодов со смещением 100Н. Заканчи-

ваться программа должна или командой ret, или стандартной процедурой

корректного выхода в MS-DOS:

Метка Мнемокод Операнд(ы) Комментарии

MOV INT АН, 4СН 21Н ; занести в АН число 4СН; (значение ; параметра прерывание INT 21Н) ; вызвать стандартную процедуру ; прерывания 21Н - корректного ; выхода в MS DOS.

Последней строкой программы может быть директива end.

Объектный модуль содержит машинные коды команд с относительными ад-

ресами. Объектный модуль выполняется МП после замены относительных

адресов на абсолютные с помощью программы-компоновщика, например,

LINK.EXE, которая генерирует модуль с расширением ехе (ЕХЕ-файл или

ЕХЕ-программу); ЕХЕ-файл, в отличие от командного модуля, может пре-

вышать объем одного сегмента. Однако в этом случае обязательно опреде-

лять сегменты с помощью директив ассемблера. Заканчивается ЕХЕ-файл

стандартной процедурой корректного выхода в MS-DOS.

Программа-компоновщик имеет еще одно назначение — она объединяет

объектный модуль с библиотечными модулями, либо несколько отдельных

объектных модулей в один ЕХЕ-файл. Библиотечными модулями называ-

ются объектные файлы, которые содержат наиболее распространенные

подпрограммы. Библиотечные модули размещаются в специальном систем-

ном файле — библиотеке (LIBRARY).

При ассемблировании программа-транслятор генерирует листинг и файл

листинга программы. Листинг — это отображения на дисплее или бумаге

текстов начального программного модуля, программного модуля (сом или

obj) и сообщений, которые указывают на ошибки программирования, свя-

занные с нарушением правил записи выражений (например, нет операнда

или неправильный мнемокод команды).

Директивы предназначены для управления процессом ассемблирования и

формирования листинга. Они действуют только в процессе ассемблирова-

ния программы и не переводятся в машинные коды. Язык ассемблера со-

держит такие основные директивы:

□ начала и конца сегмента segment и ends;

□ начала и конца процедуры proc и endp;

□ назначения сегментов assume;

22

Глава 1

□ начала org;

□ распределения и инициирования памяти db, dw, dd;

□ завершения программы end;

□ МеТКИ LABEL.

Директивы начала и конца сегмента segment и ends предназначены для опи-

сания сегментов, используемых программой. Директивы начала и конца

сегмента используются вместе, например:

Название Мнемокод Операнд

DATASG DATASG SEGMENT ENDS {<параметры>} • "1 Другие команды или дирек- ‘ Г тивы сегмента

Обе директивы — segment и ends — должны иметь одинаковые названия.

Директива segment может содержать три типа параметров: выравнивания,

объединения и класса.

Параметр выравнивания определяет начальный адрес или границу сегмента,

например:

PAGE = хххОО,

PARA = ххххО (граница по умолчанию),

word = ххххе (четная граница),

BYTE = ххххх,

где х — любая шестнадцатеричная цифра; е — четная шестнадцатеричная

цифра. Если параметр выравнивания отсутствует, по умолчанию использу-

ется параметр para, что указывает на то, что сегмент располагается в начале

параграфа, а начальный адрес сегмента является кратным 16. Параграфом

называется область памяти размером 16 байт, начальный адрес которого

кратный 16, т. е. имеющий в двоичном представлении четыре нулевых

младших разряда.

Значения параметра объединения указывают на способ обработки сегмента

при компоновке нескольких программных модулей:

□ none — значение по умолчанию. Сегмент может быть логически отде-

ленным от других сегментов, хотя физически он может располагаться ря-

дом. Предполагается, что сегмент имеет собственный базовый адрес;

□ public — данные сегменты с одинаковым названием и классом загру-

жаются в соседние области и имеют один базовый адрес;

Общие принципы построения микропроцессорных систем 23

□ stack — назначение аналогично параметру public. В любой программе

может быть определен по крайней мере один сегмент stack. Если опре-

делено больше одного сегмента stack, то указатель стека SP (Stack

Pointer) устанавливается на начало первого стека;

□ common — для сегментов common с одинаковым названием и классом ус-

танавливается один общий базовый адрес. Во время выполнения про-

граммы осуществляется наложение второго сегмента на первый. Размер

общей области определяется наиболее длинным сегментом;

□ АТ-параграф следует определять заранее. Этот параметр обеспечивает

определение меток и переменных по фиксированным адресам в фиксиро-

ванных рбластях памяти;

□ 'Класс' — этот параметр может иметь любое корректное название, ко-

торое размещается в одинарных кавычках. Параметр используется для

обработки сегментов, которые имеют одинаковые названия и классы.

Типичными являются классы "stack"’ и '"code"’, например:

Название Мнемокод Операнд

STACKSG SEGMENT PARA STACK 'STACK’

В случае, если программа не должнаюбъединяться с другими программами,

параметр объединения не указывается.

Директивы начала и конца процедуры proc и endp используются для опреде-

ления подпрограмм в сегменте кодов и имеют следующий формат:

<Название> PROC {<тип процедуры>}.

Возможны два типа процедур:

□ near — процедура находится в одном и том же сегменте, что и команды,

которые ее вызывают;

□ far — процедура находится за пределами сегмента.

По умолчанию используется тип процедуры near.

Сегмент кодов может содержать несколько процедур. Описание сегмента

кодов, который содержит только одну процедуру, имеет вид:

Название Мнемокод Операнд

Имя_сегмента Имя_процедуры SEGMENT PROC PARA FAR

Имя_процедуры RET ENDP

Имя сегмента ENDS

24

Глава 1

Имя процедуры должно присутствовать обязательно и совпадать с именем в

директиве endp, которая определяет конец процедуры.

Директива назначения сегментов assume используется для установки соот-

ветствия между сегментами и сегментными регистрами и имеет следующий

формат:

ASSUME <сегментный регистр>: <имя> {,

Например, запись 35:им_стек указывает, что имя стека определяется со-

держимым регистра SS. Одна директива assume может назначать до четырех

сегментных регистров в любой последовательности, например:

Мнемокод Операнд(ы)

ASSUME 33:им_стек, DS:им_данные, CS:им_код, ES:hm дополнительные данные

Для отмены любого назначенного ранее директивой assume сегментного

регистра используется слово nothing:

Мнемокод Операнд(ы)

ASSUME ES:NOTHING

Если программа не использует какой-либо сегмент, то соответствующий

ему операнд можно опустить или указать слово nothing.

Директива org используется для изменения содержимого программного

счетчика без команд условного или безусловного перехода. Чаще всего эту

директиву используют для установки начального адреса программы: На-

пример, директива org юон устанавливает программный счетчик на сме-

щение 100Н относительно начала сегмента кодов. Операнд со знаком дол-

лара "$" имеет текущее значение программного счетчика. Например,

директива org $+юн увеличивает адрес, загруженный в программный

счетчик, на ЮН.

Директивы распределения и инициирования памяти используются для опреде-

ления содержимого и резервирования ячеек памяти.

Директива имеет формат:

{ <имя> } Dn {количество повторений DUP}<выражение>,

где мнемокод

Dn =

DB

DW

DD

DQ

DT

Общие принципы построения микропроцессорных систем

25

указывает на длину данных: db — байт; dw — слово (два байта); dd — двойное

слово; dq — четыре слова; dt — десять байтов. Если в формате имеется имя, то

далее в программе оно может использоваться для обозначения ячейки памяти.

<выражение> в формате директивы содержит одну или несколько констант

для задания начальных значений содержимого ячеек памяти или знак "?"

для неопределенного значения содержимого. Например, директива

ALPHA DB 34

означает, что ячейка памяти с именем alpha содержит число 34. В ходе вы-

полнения программы содержимое ячейки может быть изменено. Директива

BETA DW ?

определяет, что ячейка с именем beta имеет разрядность 16, но содержимое

ячейки является неопределенным. Директива может содержать несколько

констант, разделенных запятыми и ограниченных лишь длиной строки. На-

пример, выражение

ARRAY DB 01, 02, 11, 12, 21, 22

определяет 6 констант в виде последовательности соседних байтов. Ссылка

на ячейку с именем array указывает на первую константу (01), с именем

array + 1 — на вторую (02), с именем array + 2 — на третью (И) и т. д.

Запись

MOV AL, ARRAY + 4

загружает в регистр al значение 21.

Одна директива может определить несколько ячеек памяти. В этом случае

директива имеет вид:

{ <имя> } Dn {количество повторений} DUP <выражение>

Например, директива, которая определяет 5 байт, содержащих число 21,

записывается следующим образом:

DB 5 DUP (21)

Директива завершения программы end является последней в программе и

имеет формат:

END {<стартовый адрес>)

Параметр «стартовый адрес> используется лишь при создании ЕХЕ-

файлов.

Директива метки label предназначена для установления соответствия ме-

жду именем и типом переменных. Она имеет формат:

<имя> LABEL {<тип>}

В качестве типа могут использоваться слова byte, word, dword, определяю-

щие длину данных: байт, слово или двойное слово. Директива label пере-

определяет параметры процедур near или far.

26

Глава 1

Например, директива

TOS LABEL WORD

присваивает ячейке памяти имя tos и указывает, что ее содержимое является

словом.

Примеры написания простых программ. Простые программы целесообразно

оформлять в виде командных файлов. Первой директивой таких программ

является директива org юон, последней — end.

Пример 1.1. Написать программу сложения содержимого двух 8-разрядных

ячеек памяти, которые находятся в сегменте данных ds со смещениями

1000Н и 1001Н соответственно. Результат разместить в ячейке памяти с ад-

ресом DS.1002H.

В этом примере для простоты не будем учитывать возможность возникно-

вения переносов. Программа имеет вид:

Мнемокод Операнд(ы) Комментарии

ORG юон ; Начало программы

MOV AL, [ЮООН] ; AL <Г DS: [ЮООН] ; Переслать в 8-разрядный регистр AL ; содержимое ячейки памяти с адресом ; DS:1000H

ADD AL, [Ю01Н] ; AL <r AL + DS: [1001Н] - ; Прибавить к содержимому AL содержимое ; ячейки DS:[1001Н]

MOV END. [1002Н], AL ; DS:[1002Н] <- AL ; Переслать содержимое AL в ячейку ; DS:[1002H] ; Завершение программы

Отметим, что запись mov al, [ЮООН] равнозначна записи

mov al, ds: [ЮООН], поскольку сегмент DS принят по умолчанию.

Пример 1.2. Написать программу, которая обеспечивает разделение содер-

жимого 16-разрядной ячейки памяти с адресом ES:[2000H] на четыре тетра-

ды. Тетрады должны быть записаны в младшие части четырех последова-

тельных 8-разрядных ячеек памяти, начиная с адреса DS:1000H, причем

старшая тетрада должна быть записана в ячейку со старшим адресом.

В этом примере для записи результата удобно использовать косвенную ад-

ресацию.

Общие принципы построения микропроцессорных систем

27

Программа имеет вид:

Мнемо- код Операнд(ы) Комментарии

ORG 100H ; Начало программы

MOV AX, ES:[2000H] ; AX <- ES: [2000H] ; Переслать содержимое 16-разрядной ; ячейки ES:[2000H] в 16-разрядный ; регистр АХ

MOV DX, AX ; DX <- АХ ; сохранить начальное число в DX

AND AX, 000FH ; АХ<—АХ л 0000 0000 0000 1111 ; Выделить младшую тетраду (сбросить все ; разряды АХ, кроме четырех младших)

MOV SI, 1000H ; SI <- 1000Н ; Записать в SI начальный адрес результата

MOV [SI], AL, ; DS: [SI] <- AL ; Переслать содержимое AL в ячейку памяти ; с адресом DS:SI

MOV AX, DX ; АХ <— DX ; * Переслать начальное число из DX в АХ

AND AX, 00F0H ; АХ<—АХ л 0000 0000 1111 0000 ; Выделить вторую тетраду

MOV CL, 4 ; Загрузить в CL число разрядов сдвига

ROR AL, CL ; Циклический сдвиг AL на четыре разряда ; вправо, в результате выделенное ; 4-разрядное число переместится в AL

INC SI ; si <- si +• 1 ; Увеличить SI для записи второго числа

MOV [SI], AL ; DS:[SI] <— AL ; Запомнить вторую тетраду в ячейке ; DS:[SI]

MOV AX, DX ; АХ <- DX ; переслать начальное число из DX в АХ

AND AX, 0F00H ; АХ <- АХ л 0000 1111 0000 0000 ; Выделить третью тетраду

INC SI ; si <- si + 1 ; Увеличить адрес результата

MOV [SI], AH ; DS: [SI] <— АН ; Запомнить третью тетраду

MOV AX, DX ; АХ<—DX ; Переслать начальное число из DX в АХ

AND AX, 0F000H ; АХ<—АХ Л1111 0000 0000 0000 ; Выделить четвертую тетраду

INC SI ; Увеличить адрес результата

MOV CL, 4 ; Загрузить в CL число разрядов

ROR AH, CL ; Циклический сдвиг AL на четыре разряда ; вправо

MOV END. [SI], AH ; Запомнить четвертую тетраду ; Завершение программы

28

Глава 1

Чтобы уменьшить громоздкость программы, целесообразно сводить ее к

однотипным шагам и использовать циклические операции. Рассмотренный

пример можно упростить, если выполнить сдвиг 16-разрядного числа таким

образом, чтобы тетрада, которая выделяется, всегда была младшей. Алго-

ритм такой программы вместе с командами показан на рис. 1.12.

ORG 100Н

MOV AX,ES;[2000H]

MOV DX,AX

MOV S/, 1000H

MOV BL,0

MOV BH,4

MV.MOV CL, BL

MOV AX,DX

ROR AX, CL

AND AX.OOOFH

MOV [SI], AL

DEC BH

JZ EN

INC SI

ADD BL, 4

JMP M1

EN:NOP

END

Рис. 1.12. Алгоритм решения задачи примера 1.2

Типичные вычислительные процедуры. Алгоритм типичной вычислительной

процедуры ЕСЛИ-ТО-ИНАЧЕ показан на рис. 1.13.

Эта процедура применяется тогда, когда необходимо реализовать переход

до одной из двух вычислительных процедур в зависимости от условия. При

написании программ на языке ассемблера алгоритм процедуры выполняет-

ся с помощью команд переходов по условиям установки (сброса) флагов.

Общие принципы построения микропроцессорных систем

29

Пример 1.3. Написать программу деления содержимого АХ на содержимое

BL. Результат поместить в 8-разрядную ячейку памяти с адресом

DS : ЮООН. Остатком от деления пренебречь. Если содержимое BL = 0, то

деление не выполнять, а на место результата поместить число 0FFH.

Программа имеет вид:

Метка Мнемо- Операнд(ы) Комментарии

код

ORG СМР юон BL, 0 f Начало программы Сравнить содержимое BL с нулем

f (команда влияет на установку флага

t нуля Z)

JZ Ml f Если Z = 1 (BL = 0), то переход на

r метку Ml,

DIV BL f иначе выполнить деление

f AL <— АХ : BL, остаток —» АН

JMP М2 f Безусловный переход на метку М2

Ml: MOV AL,OFFH r Занести число 0FFH в AL

М2: MOV [1000H],AL f Запомнить AL в ячейке DS : [ЮООН]

END. r Завершение программы

Рис. 1.13. Алгоритм процедуры

ЕСЛИ-ТО-ИНАЧЕ

Процедура ЕСЛИ-TO (рис. 1.14) является частным случаем процедуры

ЕСЛИ-ТО-ИНАЧЕ и используется в том случае, когда необходимо реа-

лизовать одну вычислительную процедуру в зависимости от условия.

30

Глава 1

Рис. 1.14. Алгоритм процедуры ЕСЛИ-ТО

Процедура ДЕЛАЙ-ПОКА (рис. 1.15) используется для повторения одно-

типных действий до момента выполнения условия окончания цикла.

Рис. 1.15. Алгоритм процедуры ДЕЛАЙ-ПОКА

Пример 1.4. Написать программу сложения по модулю 256 массива с 100Н

байт, расположенных по начальному адресу 7000Н : 3000Н. Результат в виде

одного байта записать в ячейку с адресом 7000Н : 5000Н.

Программа имеет вид:

Метка Мнемо- код Операнд(ы) Комментарии

ORG 100Н ; Начало программы

MOV АХ,7000Н ; Загрузить в АХ адрес сегмента

MOV DS, АХ ; Загрузить в DS адрес сегмента

Общие принципы построения микропроцессорных систем

31

(окончание)

MOV SI,3000H z z Загрузить в SI смещение первого элемента массива

MOV CX,101H / 9 Загрузить в счетчик СХ, число на 1 большее, чем длина массива

MOV AL,[SI] f ; Загрузить в AL первый элемент массива

Ml: LOOP MO 9 9 Уменьшить содержимое СХ на 1, если СХ 0, то перейти на метку МО,

MOV [5000H], AL 9 9 иначе запомнить результат в DS:[5000Н]

JMP EXIT 9 Перейти на выход

MO: INC SI 9 SI<—SI+1- адрес следующего элемента

ADD AL,[SI] 9 9 Прибавить содержимое DS:SI к предыдущей сумме в аккумуляторе AL

JMP Ml 9 9 Перейти на метку Ml для проверки условия выхода из цикла

EXIT: NOP END. 9 9 Выход из программы Завершение программы

Процедура ПОВТОРЯЙ-ДО-ТОГО-КАК (рис. 1.16) аналогичная предыду-

щей, но однотипные действия выполняются перед проверкой условия.

Рис. 1.16. Алгоритм процедуры

ПОВТОРЯЙ-ДО-ТОГО-КАК

Программа выполнения задачи примера 1.4 в соответствии с алгоритмом

(1.21) имеет вид:

Метка Мнемо- код Операнд(ы) Комментарии

ORG 100Н ; Начало программы

32

Глава 1

(окончание)

MOV AX,7000H ; Загрузить в AX адрес сегмента

MOV DS, AX ; Загрузить в DS адрес сегмента

MOV SI,3000H ; Загрузить в SI смещение первого ; элемента массива

MOV CX,100H ; Загрузить в счетчик СХ, число на 1 ; большее, чем длина массива

MOV AL,[SI] ; Загрузить в AL первый элемент ; массива

MO: INC SI ' SI<—SI+1 - адрес следующего элемента

ADD AL,[SI] ; Прибавить содержимое DS:SI к ; предыдущей сумме в AL

LOOP MO ; Уменьшить содержимое СХ на единицу, '* если СХ^ 0 , то перейти на метку

MOV [5000H],AL ; МО,иначе - запомнить результат в ; DS:[5000H]

END. ; Завершение программы

Написание ЕХЕ-программ. Написание ЕХЕ-программ осуществляется при

выполнении следующих условий:

□ указания соответствия между сегментами и сегментными регистрами;

□ сохранения содержимого DS в стеке;

□ записи числа 0 в стек;

□ загрузки адреса сегмента данных в регистр DS.

Первое требование выполняется с помощью директивы assume, другие — с

помощью соответствующих команд ассемблера.

Пример 1.5. Написать ЕХЕ-программу .нахождения максимального числа в

массиве 8-разрядных беззнаковых чисел. Результат записать в регистр DL.

Программа имеет вид:

Метка (или имя) Мнемо- код Операнд(ы) Комментарии

DATASG SEGMENT PARA ’DATA’ ; Определить сегмент данных

MASSIV DATASG DB ENDS 01,02,03,45, 56, 67,78,89,OFE,10 ; Определить в сегменте ; данных 10 значений ; массива MASSIV

STACKSG SEGMENT PARA STACK 'Stack' DW 100 DUP (?) ; Определить сегмент стека ; Определить 100 слов

Общие принципы построения микропроцессорных систем

33

(продолжение)

TOS STACKSG LABEL ENDS WORD r f Определить имя и формат вершины стека

CODESG . SEGMENT PARA ’CODE’ r Определить сегмент кодов

BEGIN PROC FAR ! Начало процедуры

ASSUME PUSH SS: STACKSG, DS:DATASG, CS: CODESG DS f Загрузить содержимое DS

r в стек

SUB AX, AX r Установить нулевое

r содержимое в АХ

PUSH AX f Записать нуль в стек

MOV AX,DATASG f Загрузить адрес DATASG

f в АХ

MOV DS, AX f Записать адрес DATASG

f в регистр DS

LEA BX,MASSIV r Загрузить в регистр ВХ

f адрес первого элемента

MOV CX, 10 f Загрузить в СХ длину

r массива

MOV DL,[BX] r DL<—DS: [ВХ]

СОМР: MOV AL,[BX] ! AL<—DS: [ВХ]

CMP AL,[BX+1] f Сравнить два соседних

• f элемента массива

JAE NEXT f Если содержимое

r предыдущего элемента

f массива [ВХ] больше или

f равняется содержимому

f Следующего [ВХ +1], то

f перейти на метку NEXT,

MOV DL,[BX+1] f иначе загрузить в DL

34

Глава 1

(окончание)

NEXT: ; значение [ВХ + 1] INC ВХ ; увеличить ВХ для

’ BEGIN CODESG ; адресации следующего ; элемента массива LOOP COMP ; проверка условия выхода ; из цикла RET ; возврат ENDP ; конец процедуры BEGIN ENDS ; конец сегмента кодов END. ; Завершение программы

В рассмотренном примере выход в MS-DOS осуществляется командой

ret с использованием адреса, записанного в стек в начале программы

командой push ds. Иначе можно завершить программу командой int

20Н.

Контрольные вопросы и задания

1. Приведите основные характеристики и структурные схемы процессоров

с фоннеймановской и гарвардской архитектурой.

2. Укажите назначение регистров МП с фоннеймановской архитектурой.

3. Охарактеризуйте функции устройства управления.

4. Приведите определение и назначение аккумулятора.

5. Объясните работу программного счетчика.

6. Укажите местонахождение операнда с прямой адресацией.

7. Объясните, каким образом определяется адрес операнда с косвенной

адресацией.

8. Объясните, как определяется значение операнда с непосредственной ад-

ресацией.

9. Объясните, каким образом определяется адрес операнда с относитель-

ной адресацией.

10. Напишите программу пересылки содержимого 8-разрядной ячейки па-

мяти с адресом 7000Н:1000Н в 8-разрядный регистр AL.

Общие принципы построения микропроцессорных систем

35

11. Напишите программу вычитания содержимого двух последовательных

ячеек памяти с адресами DS:35A0H и 35А1Н с записью результата в

ячейку с адресом 35А2Н.

12. Напишите программу сложения массивов байтов с адресами 8350:4735Н

и 3660:2200Н по правилу "первый с первым, второй со вторым и т. д.".

Занести в массив 6250:2400Н адреса тех пар слагаемых, сумма которых

равняется нулю. Длина массива 100Н.

13. Выполните деление массива из 25Н слов 5В00:3000Н на массив с 25Н

байт 5С00:4000Н по правилу "первый на первый, второй на второй

и т. д.". Результаты занести в массив 6000:5000Н. При возникновении

необходимости деления на 0 деление не выполнять, а байты результата

загрузить числом 1АН.

Глава 2

Однокристальные

микропроцессоры

2.1. Однокристальный 8-разрядный

микропроцессор

Структурная схема обобщенного 8-разрядного однокристального МП по-

казана на рис. 2.1.

Рис. 2.1. Структурная схема 8-разрядного микропроцессора

38

Гпава 2

Схема имеет единую внутреннюю 8-разрядную шину, по которой передают-

ся данные, коды команд и адреса.

Структурная схема содержит: устройство управления (УУ), дешифратор

команд (ДШК), регистр команд (РК), арифметико-логическое устройство

(АЛУ), аккумулятор (А), временной аккумулятор (ВА), временной регистр

(ВР), регистр флагов F, блок 8-разрядных регистров общего назначения

(РОН), мультиплексор, указатель стека (Stack Pointer SP), указатель команд

(Instruction Pointer IP), буферный регистр адреса (БА), буферный регистр

данных (БД), схему инкремента/декремента (СИД).

Устройство управления (УУ) в соответствии с дешифрованными кодами

команд и внешними управляющими сигналами генерирует управляющие

сигналы для всех блоков структурной схемы.

Дешифратор команд (ДШК) формирует сигналы для устройства управле-

ния в соответствии с дешифрованным кодом команды.

В 8-разрядном регистре команд (РК) хранится машинный код команды

(один байт).

Арифметико-логическое устройство (АЛУ) представляет собой комбинаци-

онную схему на основе сумматора и логических элементов, которое сигнала-

ми с выходов устройства управления настраивается на ту или иную арифмети-

ческую или логическую операцию — суммирование, вычитание, И, ИЛИ,

"Исключающее ИЛИ", НЕ, сдвиг.

Аккумулятор (А) является 8-разрядным регистром, в котором хранится

один из операндов в двухоперандных командах, а также результат опера-

ции. Например, в команде суммирования

ADD В; А+В—>А

явным образом указан лишь один операнд — 8-разрядный регистр В. Ре-

гистр В — один из РОН. В некоторых МП РОН обозначаются буквами ла-

тинского алфавита: В, С, D, Н, L, в других — RO, Rl, R2, ... Вторым опе-

рандом является содержимое аккумулятора. Результат суммирования

содержимого аккумулятора и регистра В заносится в аккумулятор, что сим-

волически записывается в комментарии к команде.

Временной аккумулятор (ВА) и временной регистр (ВР) — это 8-разрядные

буферные регистры, позволяющие отделить входы АЛУ от его выходов, т. е.

исключить гонку сигналов.

Регистр флагов (F, Flag), или признаков, представляет собой несколько

триггеров (пять или шесть), которые устанавливаются в единичное или

сбрасываются в нулевое состояние в зависимости от результата операции в

АЛУ.

Регистры общего назначения (РОН) — блок 8-разрядных регистров, в кото-

рых хранятся данные и промежуточные результаты. Блок РОН можно рас-^

Однокристальные микропроцессоры

39

сматривать как быстродействующее ОЗУ, имеющее наибольшее быстродей-

ствие среди ОЗУ различных типов, поскольку оно размещено непосредст-

венно на кристалле БИС МП. Некоторые типы 8-разрядных процессоров,

кроме 8-разрядных РОН, содержат 16-разрядные индексные регистры для

организации косвенной адресации, другие предполагают обращения к паре

8-разрядных регистров как к одному 16-разрядному.

Мультиплексор (М) — устройство, соединяющее один из регистров общего

назначения с внутренней шиной МП.

Указатель стека (SP) — 16-разрядный регистр, в котором хранится адрес

последней занятой ячейки стека.

Указатель команд (IP) — 16-разрядный регистр, в котором хранится адрес

выполняемой команды. После выборки из памяти программ очередного

байта команды содержимое IP увеличивается на единицу.

Буферный регистр адреса (БА) и буферный регистр данных (БД) — регист-

ры с тремя состояниями выхода, предназначенные для формирования сиг-

налов на линиях шин адреса и данных соответственно.

Схема инкремента/декремента (СИД) — устройство, позволяющее без уча-

стия АЛУ увеличить или уменьшить на единицу содержимое одного из ре-

гистров РОН, IP или SP.

Конструктивно БИС 8-разрядного процессора выполнена в корпусе с 40 выво-

дами, из которых 16 приходятся на шину адреса, 8 — на шину данных, 2 (4) —

на подключение питания, а все остальные — на линии шины управления.

Основные линии шины управления показаны на рис. 2.1:

□ Fl, F2 — вход двух неперекрывающихся последовательностей импульсов

синхронизации (рис. 2.2);

□ RESET — вход сигнала начальной установки (сброса);

□ READY — вход сигнала готовности внешнего устройства или памяти к

обмену; используется для организации обмена с менее быстродействую-

щими (по сравнению с МП) устройствами;

□ WAIT — выход сигнала подтверждения ожидания; активный уровень

сигнала свидетельствует о том, что процессор перешел в режим ожида-

ния и выполняет такты ожидания;

□ HOLD — вход сигнала запроса прямого доступа к памяти (ПДП) или

запроса захвата шин; используется для организации обмена с устройст-

вами, быстродействие которых больше, чем быстродействие процессора;

□ HLDA (HoLD Acknowledge) — выход сигнала подтверждения прямого

доступа к памяти; активный уровень этого сигнала свидетельствует о

том, что процессор перевел свои шины адреса, данных и управления в

высокоимпедансное состояние;

40

Гпава 2

Рис. 2.2. Временные диаграммы импульсов синхронизации F\ и F2

□ INT (INTerrupt) — вход сигнала запроса прерывания;

□ INTE (INTerrupt Enable) — выход сигнала разрешения прерывания;

□ DBIN (Data Bus IN) — выход сигнала чтения; высокий уровень (Н-

уровень — уровень логической единицы) этого сигнала свидетельствует о

том, что двунаправленная шина данных находится в режиме приема ин-

формации;

□ WR (WRite) — выход сигнала записи; низкий уровень (L-уровень —

уровень логического нуля) этого сигнала свидетельствует о том, что дву-

правленная шина данных находится в режиме выдачи информации;

□ SYNC (SYNChronization) — выход сигнала синхронизации; высокий

уровень этого сигнала свидетельствует о том, что по шине данных пере-

дается байт состояния, который используется для формирования некото-

рых управляющих сигналов.

Схемы конкретных МП отличаются количеством и обозначением регистров, а

также некоторыми управляющими сигналами. Например, в МП i8085 вме-

сто двух сигналов F1 и F2 используется один сигнал синхронизации CLK

(CLocK); вместо сигнала DBIN — сигнал чтения RD(ReaD). Низкий уро-

вень этого сигнала свидетельствует о том, что двунаправленная шина дан-

ных находится в режиме приема информации. В МП i8085 есть дополни-

тельный сигнал М/Ю (Memory/Input-Output) — признак обращения к

памяти (логическая единица) или к устройству ввода/вывода (логический

ноль), но нет сигнала SYNC.

Схема (см. рис. 2.1) работает следующим образом. При включении питания

или при формировании сигнала начальной установки RESET содержимое

указателя команд IP приобретает нулевое значение и начинается машинный

цикл выборки команды из памяти. Содержимое ячейки памяти по нулевому

адресу через буферный регистр данных и внутреннюю шину МП поступает

в регистр команд, после этого — в дешифратор команд. Соответственно

дешифрованным кодам команд и внешним сигналам синхронизации и

Однокристальные микропроцессоры

41

управления устройство управления формирует управляющие импульсы для

каждой микрооперации команды.