Author: Пузанкова Д.В.

Tags: компьютерные технологии языки программирования трансляторы микропроцессы

ISBN: 5-7325-0516-4

Year: 2002

Text

УЧЕБНОЕ ПОСОБИЕ ДЛЯ ВУЗОВ

Под общей редакцией Д. В. Пузанкова

Допущено Министерством образования Российской Федерации в качестве учебного пособия для студентов высших учебных заведений, обучающихся по направлению подготовки бакалавров и магистров “Информатика и вычислительная техника”

БИБЛИОТЕКА

/ омского государственного университ<т & систем упрамлеяил и

радиоэл*ектрон ики ИНВ.иУе

203

ПОЛИТЕХНИКА

ИЗДАТЕЛЬСТВО

Санкт-Петербург 2002

УДК 681.3 ББК 32.973.2

М59

Федеральная программа книгоиздания России

wdo noi':

М59 Микропроцессорные системы: Учебное пособие для вузов / Е. К. Александров, Р. И. Грушвицкий, М. С. Куприянов, О. Е. Мартынов, Д. И. Панфилов, Т. В. Ремизевич, Ю. С. Татаринов, Е. П. Угрюмов, И. И. Шагурин; Под общ. ред. Д. В. Пузанкова. — СПб/. Политехника, 2002. — 935 с.: ил.

ISBN 5-7325-0516-4

Излагаются вопросы организации функционирования и программирования микропроцессорных средств. Представлены микропроцессоры общего применения ведущих мировых производителей, процессоры обработки сигналов, а также микроконтроллеры для встроенных приложений: коммуникационные, для задач управления и др. Рассматриваются программные модели процессоров и микроконтроллеров, особенности организации периферийных устройств, средства отладки и проектирования. Приводятся примеры применения и программирования. Учебное пособие ориентировано на студентов технических университетов, обучающихся по направлению «Информатика и вычислительная техника».

УДК 681.3 ББК 32.973.2

ISBN 5-7325-0516-4

© Е. К. Александров, Р. И. Грушвицкий, М. С. Куприянов, О. Е. Мартынов, Д. И. Панфилов, Т. В. Ремизевич, Ю. С. Татаринов, Е. П. Угрюмов, И. И. Шагурин, 2002

© Издательство «Политехника», 2002

ПРЕДИСЛОВИЕ

С момента выхода последних учебников и учебных пособий по микропроцессорной технике прошло значительное время. Данные книги содержали, как правило, описания конкретных микропроцессоров или микропроцессорных комплексов, включали разделы, посвященные средствам программирования, вопросам проектирования и отладки.

В настоящее время на российском рынке представлены самые разнообразные микропроцессорные средства преимущественно многочисленных зарубежных компаний: микропроцессоры (МП), используемые в первую очередь для персональных компьютеров и рабочих станций; микроконтроллеры (МК) и интегрированные процессоры (ИП), используемые для встраиваемых систем. Безусловно, в первую очередь представляют интерес МК и ИП, ориентированные на встроенные применения для таких областей как управление оборудованием, сетевые приложения, связь, портативная техника, автоматизация и т. п.

Обширная номенклатура и богатые функциональные возможности МП, МК и ИП создают специалистам хорошие условия для проектирования конкурентоспособных систем различного назначения. Однако осуществить правильный выбор типа микропроцессорного средства можно только опираясь на знания архитектуры, системных возможностей, организации и средств поддержки процесса проектирования.

Ситуация на рынке информационных ресурсов, детальное изучение фирменной литературы, а также практическая работа с микроконтроллерами и процессорами, описываемыми ниже, убеждают в том, что в классе микропроцессоров для персональных компьютеров бесспорно лидирующие позиции занимает компания Intel, а в классах интегрированных процессоров и микроконтроллеров, используемых для встраиваемых приложений, ведущее положение занимает фирма «Motorola», определяя многие стандарты и типовые решения.

Данное обстоятельство и определило структуру предлагаемой книги.

Работа над книгой распределилась следующим образом: гл. 1 написана И.И. Шагуриным и М.С. Куприяновым, гл. 2 - И.И. Шагуриным, гл. 3 - Е.К. Александровым, гл. 4 - Т.В. Ремизевич и Д.И. Панфиловым, гл. 5 - М.С. Куприяновым и О.Е. Мартыновым, гл. 6 - М.С. Куприяновым, гл. 7 - Е.П. Угрюмовым, гл. 8 - Р.И. Груш-вицким и И.И. Шагуриным, гл. 9 - Ю.С. Татариновым.

Материал по главам изложен с разной степенью детализации Это объясняется тем, что для отдельных классов микропроцессорных средств уже накоплены базовые решения, позволяющие сделать определенные обобщения, для других же классов, как, например, коммуникационных контроллеров, идеология организации и применения только формируется.

Особо нужно сказать о программном обеспечении микропроцессорных систем. Этому вопросу должна быть посвящена отдельная книга, так как слишком велико множество достаточно сложных вопросов, которые необходимо рассмотреть: языки и инструментальные средства программирования, вопросы тестирования и отладки, схемы и технологии разработки программных изделий и др. Причем для каждого класса микропроцессорных средств существуют свои особенности и отличия. В настоящей книге в отдельных главах авторы касаются вопросов программного обеспечения в той лишь степени, которая позволяет раскрыть особенности организации, функционирования или применения рассматриваемых типов процессоров или микроконтроллеров.

Конечно, принцип «с высоты птичьего полета», которым пришлось воспользоваться при подготовке книги, позволяет лишь показать общий ландшафт и область, которую занимают отдельные процессоры или микроконтроллеры. Однако в отдельных разделах «высота» рассмотрения намеренно снижена, что позволило представить читателю не только общие принципы организации, но отдельные достоинства и потребительские свойства более мелких деталей анализируемых устройств.

ПРЕДИСЛОВИЕ

Книгу нельзя рассматривать как энциклопедию: в ней нет разделов, посвященных, например, 16-разрядным микроконтроллерам общего применения, идеология организации которых во многом совпадает с организацией наиболее массового класса 8-разрядных микроконтроллеров. По аналогичной причине не излагаются вопросы организации интегрированных процессоров. Содержание книги определилось тем видением авторами общих тенденций и закономерностей развития микропроцессорной техники, которые в настоящее время имеют место с учетом достижений полупроводниковой технологии и требованиями практики проектирования информационных систем различного назначения.

Книга ориентирована на читателя разной профессиональной ориентации. Прежде всего она будет полезна студентам технических университетов, изучающих компьютерные технологии и системы. Для руководителей служб снабжения, менеджеров, инженерно-технических работников, не знакомых с МК, безусловно, полезным будет знакомство с разделами, в которых рассматривается идеология построения МК, приводятся общие сведения о МК и областях их целесообразного использования. Заинтересованный читатель далее может ознакомиться с технологией проектирования микропроцессорных систем с учетом достижений в области программируемой логики и оценить ориентировочно трудоемкость разработки системы.

Цель книги считается достигнутой, если читатель убеждается в следующем.

• Высокая эффективность проектирования достигается в тех случаях, когда каждой области применения соответствует семейство МК или ИП, максимальным образом учитывающих ее особенности,

• Работа компаний на «заказ для области использования» не приводит, как принято считать, к росту потребительской стоимости. Это достигается за счет модульной организации и технологии процессорного ядра, которые снижают затраты на производство и упрощают проектирование. Отобранные компанией в результате многолетней практики периферийные устройства с последующим их интегральным исполнением вместе с процессорным ядром обеспечивают пользователю быстрое и эффективное проектирование системы с абсолютно ясной перспективой развития.

• Преемственность в решениях (использование принципов открытых систем) дает возможность разработчику наращивать возможности своих систем, не разрушая предшествующий задел. Поистине бережное отношение компании к пользователям ее продукции воплощается в программной совместимости, наличии в разных семействах одной и той же периферии, использовании одинаковой технологии отладки и проектирования.

Семейства микропроцессорных средств создают функциональный ряд архитектур с масштабированием параметров (параметрический ряд) от 8-разрядных реализаций с CISC-архитектурой малой и средней производительностью до 32-разрядных реализаций с RISC-архитектурой сверхвысокой производительности:

• Практически все семейства МК и ИП содержат внутрикристальные средства отладки, что позволяет без дополнительного оборудования осуществить настройку аппаратного обеспечения.

• Для всех семейств созданы программно-аппаратные средства, обеспечивающие разработчиков всем необходимым для решения задач проектирования и отладки целевой системы.

• Ведущие компании - производители программного обеспечения создают системы реального времени, ориентированные на МК и ИП, что позволяет сократить сроки выполнения крупномасштабных проектов.

ВВЕДЕНИЕ

Микропроцессорная техника (МПТ) включает технические и программные средства, используемые для построения различных микропроцессорных систем, устройств и персональных микроЭВМ.

Микропроцессорная система (МПС) представляет собой функционально законченное изделие, состоящее из одного или нескольких устройств, главным образом микропроцессорных: микропроцессора и/или микроконтроллера.

Микропроцессорное устройство (МПУ) представляет собой функционально и конструктивно законченное изделие, состоящее из нескольких микросхем, в состав которых входит микропроцессор; оно предназначено для выполнения определенного набора функций: получение, обработка, передача, преобразование информации и управление.

Под микропроцессором (МП) будем понимать в дальнейшем программно-управляемое устройство, осуществляющее процесс цифровой обработки информации и управления им и построенное, как правило, на одной БИС.

Термин «микроконтроллер» (МК) вытеснил из употребления ранее использовавшийся термин «однокристальная микроЭВМ». Первый же патент на однокристальную микро-ЭВМ был выдан в 1971 году М. Кочрену и Г. Буну. Именно они предложили на одном кристалле разместить не только микропроцессор, но и память, устройства ввода-вывода. С появлением однокристальных микроЭВМ связывают начало эры компьютерной автоматизации в области управления. По-видимому, это обстоятельство и определило термин «микроконтроллер» (control - управление).

Однако впоследствии расширение сферы использования МК повлекло за собой развитие их архитектуры за счет размещения на кристалле устройств (модулей), отражающих своими функциональными возможностями специфику решаемых задач. Такие дополнительные устройства стали называться периферийными. Поэтому неслучайно в последнее время введен еще один термин - «интегрированный процессор» (ИП), который определяет новый класс функционально-емких однокристальных устройств с другим составом модулей. По количеству и составу периферийных устройств ИП уступают МК и занимают промежуточное положение между МП и МК. По этой же причине появились не только семейства МК, которые объединяют родственные МК (с одинаковой системой команд, разрядностью), но и стали выделяться подвиды МК: коммуникационные, для управления и т. д.

МП в настоящее время преимущественно используются для производства персональных ЭВМ, а МК и ИП являются основой создания различных встраиваемых систем, телекоммуникационного и портативного оборудования и т. д.

Анализ различных семейств МП, ИП и МК показывает, что наиболее жизнеспособными являются такие семейства, которые опираются в своем развитии на предшествующую эволюцию микропроцессоров, т.е. за счет «селекции» выделяются устойчивые и проверенные практикой структурные решения и закладываются в новые семейства МК. Это позволяет использовать кадры, освоившие микропроцессоры, программное обеспечение, средства поддержки этапов разработки. Фирмы «Motorola» и «Intel», являясь общепризнанными лидерами в производстве микропроцессорных средств и развивая свои семейства МК, блестяще демонстрируют на практике технологии эволюционного проектирования.

Разные МП или МК объединяют в семейства как технология «микроядра», в качестве которого выступает процессорное ядро, взаимодействующее с периферийными устройствами различной номенклатуры, так и принципы, свойственные открытым системам: совместимость (compatibility), масштабируемость (scalability), переносимость (portability) и взаимодействие приложений (introperability).

Совместимость, состоящая в выполнении приложений на всех версиях МК, обеспечивается использованием в качестве базовой системы команд и интерфейса микропроцессора с последующей унификацией путем добавления дополнительных команд и внешних выводов, повышающих эффективность использования в задачах, на которые ориентируется семейство МК. Полученное таким образом структурное образование называется процессорным ядром, на орбите которого вращаются как «отрицательно заряженные частицы» -периферийные устройства, требующие ресурсов процессорного ядра (например, память,

5

ВВЕДЕНИЕ

последовательный порт и др.), так и «положительно заряженные частицы» - периферийные устройства, аппаратно поддерживающие вычислительный процесс в МК (например, сопроцессор обработки сигналов, таймерный сопроцессор, коммуникационный сопроцессор и др.). Подобная функционально распределенная модель кристалла МК, с одной стороны, позволяет добиться более полного соответствия между особенностями предметной области и организацией кристалла, а с другой - обеспечить совместимость как в пределах различных версий определенного типа МК, так и в пределах всего семейства МК.

Масштабируемость обеспечивается выполнением приложений в пределах полного диапазона архитектур. Действительно, за счет технологии процессорного ядра обеспечивается переносимость приложений как для обычных микропроцессоров, так и для встроенных микропроцессоров (embedded microprocessors), а также для микроконтроллеров.

Переносимость для открытых систем рассматривается как возможность выполнения приложения на разных компьютерах с одной операционной системой. В нашем случае этот важный принцип состоит в том, что ядро операционной системы реального времени (OS-9, VxWorks и др.) портируется в целевые платформы на базе МК всех семейств, создавая тем самым комфортные условия для разработчика: процесс проектирования от дешевых систем с невысокой производительностью до многопроцессорных конфигураций осуществляется в рамках единой инструментальной среды.

Взаимодействие приложений - возможность общения приложений разных систем, использующих одни протоколы. Этот принцип в полной мере реализуется в системах на базе коммуникационных контроллеров фирмы «Motorola», так как на уровне кристалла реализованы типовые протоколы (HDLC, Х.25 и др.).

Таким образом, определенная выше открытая модель взаимосвязи МК (Open Microcontrollers/Microprocessors Interconnection - OMI-модель), сформированная в ходе эволюции микропроцессорных средств, находится в русле магистрального развития информационных систем и является гарантом эффективности применения микропроцессорных средств, удовлетворяющих требованиям этой модели.

Задачи системной интеграции для российских специалистов являются областью приложения их высокого интеллектуального потенциала. При этом эффективность решения этих задач во многом зависит от правильного выбора микропроцессорных средств ввиду их значительного разнообразия.

Если взять за критерий комплексный показатель «количество данных - количество вычислений», то возможны следующие его значения, определяющие классы задач и основные характеристики МК (табл. В.1).

Перечисленным четырем классам задач безусловно соответствуют определенные типы МК и ИП, наиболее полно учитывающих в своей архитектуре их специфику, а установленное соответствие, конечно, не является строгим. Так, среди 8-разрядных МК есть развитые модели (например, семейство М68НС11), которые с успехом можно использовать для решения отдельных задач из второго класса. Точно так же семейства 32-разрядных микроконтроллеров в последнее время активно вытесняют 16-разрядные микроконтроллеры, поскольку разница в цене становится несущественной, при более развитой архитектуре.

При создании системы любого назначения на базе микроконтроллеров либо интегрированных процессоров, в общем случае, необходимо выполнить следующие этапы.

1. Системный анализ задачи - выделяются процессы и функции, реализация которых будет возложена на МК или ИП.

2. Алгоритмизация процессов и функций - разрабатываются алгоритмы решения задачи.

3. Выбор МК или ИП и комплексная разработка программно аппаратных средств - осуществляется выбор технических средств соответствующей компании, инструментальных средств поддержки процесса проектирования (отладочных средств, языков программирования и т. д.), а также операционной системы реального времени, если это требуется для решения задачи. Производится программирование алгоритмов, полученных на втором этапе, изготовление системы на базе выбранного МК или ИП и комплексная отладка.

ВВЕДЕНИЕ

Таблица В. 1

Области использования МК

Значение критерия Характеристика задач Разрядность МК/ производительность

Мало данных -мало вычислений Задачи логического управления несложными объектами и процессами 8/Низкая

Мало данных-много вычислений Локальные регуляторы, системы управления электрическими двигателями, подвижными аппаратами, различными электрическими агрегатами, роботами-манипуляторами, станками, портативное оборудование и т. д. 16/Средняя

Много данных -мало вычислений Многие сетевые задачи, системы управления потоками данных, коммутаторы, концентраторы, маршрутизаторы и т.п. 32/Высокая

Много данных -много вычислений Задачи управления реального времени, обработка сигналов с интенсивным обменом, системы распознавания речи, изображений и т. п. 32/Сверхвысокая

Безусловно, для разработчика (пользователя) важно знать затраты, которые его ожидают на этом пути. Как показывает анализ практических приложений (в этом также убеждают и различные публикации), затраты распределяются по этапам следующим образом: 30 - 40; 40 - 50; 10 - 20. Затраты по каждому этапу варьируются в некотором диапазоне, но очевидно одно: первые два этапа являются определяющими.

Если МК или ИП не «окрашен» определенной областью применения (структура не содержит дополнительных модулей, которые для данной области «специализируют» ее за счет аппаратной реализации функций, выделенных на первом этапе), то разработчик реализует этапы в полной мере. Если структура МК или ИП «начинена» дополнительными модулями, то это не только упрощает программирование на третьем этапе, но и существенно сокращает трудоемкость первого и второго этапов. Кроме этого, важно иметь семейство МК или ИП, программно совместимых, но отличающихся производительностью и набором периферийных модулей, так как в процессе проектирования, во-первых, могут измениться критерии и добавиться новые функции, во-вторых, после первой версии созданной системы, даже если она удачна и жизнеспособна, как правило, создается более совершенная версия с расширенными возможностями, в которой учитываются результаты практической апробации и эксплуатации. Очевидно также, что формализация знаний на первом этапе (доведение знаний специалистов в конкретной области до алгоритмических моделей) приобретает направленный характер, если разработчик ориентируется на компанию, выпускающую многономенклатурную электронную продукцию, так как сама компания предварительно позиционирует свои микропроцессорные средства и другие электронные компоненты по определенным областям с учетом их разрядности, архитектурных особенностей, программного обеспечения, а главное, своего опыта создания электронных компонентов под конкретные задачи.

Сложность задач второго этапа также резко снижается за счет наличия в МК и ИП модулей, аппаратно реализующих алгоритмы типовых функций для тех задач, на которые он ориентируется. В этом случае разработчик, пользуясь предоставленным ему «конструктором», в котором определены типы деталей (МК и ИП, а также набор модулей), соединительные элементы (интерфейсы и средства сопряжения), а также правила соединения (средства программирования и отладки), за довольно короткий срок (в пределах одного-двух месяцев) «собирает» (решает задачи системной интеграции) в соответствии со своими требованиями на разработку изделия (систему определенного целевого назначения).

ГЛАВА 1

ОСНОВЫ МИКРОПРОЦЕССОРНОЙ ТЕХНИКИ

Микропроцессором называется программно-управляемое устройство для обработки цифровой информации и управления процессом обработки, реализованное в виде большой (БИС) или сверхбольшой (СБИС) интегральной микросхемы. Таким образом, микропроцессор играет роль процессора в цифровых системах различного назначения. Это могут быть системы обработки информации (компьютеры), системы управления объектами и процессами, информационно-измерительные системы и другие виды систем, используемых в промышленности, бытовой технике, аппаратуре связи и многих других областях применения.

1.1. КЛАССИФИКАЦИЯ МИКРОПРОЦЕССОРОВ, ОСНОВНЫЕ ВАРИАНТЫ ИХ АРХИТЕКТУРЫ И СТРУКТУРЫ

Микропроцессор является универсальным устройством для выполнения программной обработки информации, которое может использоваться в самых разнообразных сферах человеческой деятельности. Десятки компаний-производителей выпускают несколько тысяч типов микропроцессоров, имеющих разные характеристики и предназначенных для различных областей применения. Выпускаемые микропроцессоры делятся на отдельные классы в соответствии с их архитектурой, структурой и функциональным назначением. В данном разделе дается обзор основных архитектурных и структурных вариантов реализации современных микропроцессоров, используемых в различных сферах применения.

Основными направлениями развития микропроцессоров является увеличение их производительности и расширение функциональных возможностей, что достигается как повышением уровня микроэлектронной технологии, используемой для производства микропроцессоров, так и применением новых архитектурных и структурных вариантов их реализации. Развитие микроэлектронной технологии обеспечивает непрерывное уменьшение размеров полупроводниковых компонентов, размещаемых на кристалле микропроцессора. При этом уменьшаются паразитные емкости, определяющие задержку переключения логических элементов, и увеличивается число элементов, размещаемых на кристалле. В настоящее время разрешающая способность промышленной технологии изготовления микросхем обеспечивает создание компонентов с минимальными размерами 0,13-0,18 мкм. При этом обеспечивается создание микропроцессоров, работающих с тактовой частотой до 1 - 2 ГГц и содержащих на кристалле десятки миллионов транзисторов. В соответствии с эмпирическим правилом, которое сформулировал Гордон Мур, один из основателей компании Intel, степень интеграции микросхем удваивается каждые 1,5-2 года. Это правило выполнялось в течение 40 лет развития микроэлектроники, и можно прогнозировать, что оно будет выполняться и в близком будущем. Поэтому можно ожидать последующего быстрого прогресса технологии и связанного с ним повышения характеристик микропроцессоров.

Развитие технологии обеспечивает возможность создания на кристалле все большего количества активных компонентов - транзисторов, которые могут быть использованы для реализации новых архитектурных и структурных решений, обеспечивающих повышение производительности и расширение функциональных возможностей микропроцессоров. Кратко рассмотрим основные из этих решений.

Архитектурой процессора называется комплекс его аппаратных и программных средств, предоставляемых пользователю. В это общее понятие входит набор программно-доступных регистров и исполнительных (операционных) устройств, система основных команд и способов адресации, объем и структура адресуемой памяти, виды и спосо-

КЛАССИФИКАЦИЯ МИКРОПРОЦЕССОРОВ. ОСНОВНЫЕ ВАРИАНТЫ ИХ АРХИТЕКТУРЫ И СТРУКТУРЫ

бы обработки прерываний. Например, все модификации процессоров Pentium, Celeron, i486 и i386 имеют архитектуру IA-32 (Intel Architecture - 32 bit), которая характеризуется стандартным набором регистров, предоставляемых пользователю, общей системой основных команд и способов организации и адресации памяти, одинаковой реализацией защиты памяти и обслуживания прерываний.

При описании архитектуры и функционирования процессора обычно используется его представление в виде совокупности программно-доступных регистров, образующих регистровую или программную модель. В этих регистрах содержатся обрабатываемые данные (операнды) и управляющая информация. Соответственно, в регистровую модель входит группа регистров общего назначения, служащих для хранения операндов, и группа служебных регистров, обеспечивающих управление выполнением программы и режимом работы процессора, организацию обращения к памяти (защита памяти, сегментная и страничная организация и др.).

Регистры общего назначения образуют РЗУ - внутреннюю регистровую память процессора. Состав и количество служебных регистров определяется архитектурой микропроцессора. Обычно в их состав входят:

• программный счетчик PC (или CS + IP в архитектуре микропроцессоров Intel);

• регистр состояния SR (или EFLAGS);

• регистры управления режимом работы процессора CR (Control Register);

• регистры, реализующие сегментную и страничную организацию памяти;

• регистры, обеспечивающие отладку программ и тестирование процессора.

Кроме того, различные модели микропроцессоров содержат ряд других специализированных регистров.

Функционирование процессора представляется в виде реализации регистровых пересылок - процедур изменения состояния этих регистров путем чтения-записи их содержимого. В результате таких пересылок обеспечивается адресация и выбор команд и операндов, хранение и пересылка результатов, изменение последовательности команд и режимов функционирования процессора в соответствии с поступлением нового содержимого в служебные регистры, а также все другие процедуры, реализующие процесс обработки информации согласно заданным условиям.

В ряде процессоров выделяются регистры, которые используются при выполнении прикладных программ и доступны каждому пользователю, и регистры, которые управляют режимом работы всей системы и доступны только для привилегированных программ, входящих в состав операционной системы (супервизора). Соответственно, такие процессоры представляются в виде регистровой модели пользователя, в которую входят регистры, используемые при выполнении прикладных программ, или регистровой модели супервизора, которая содержит весь набор программно-доступных регистров процессора, используемых операционной системой.

Структура микропроцессора определяет состав и взаимодействие основных устройств и блоков, размещенных на его кристалле. В эту структуру входят;

• центральный процессор (процессорное ядро), состоящее из устройства управления (УУ), одного или нескольких операционных устройств (ОУ);

• внутренняя память (РЗУ, кэш-память, блоки оперативной и постоянной памяти);

• интерфейсный блок, обеспечивающий выход на системную шину и обмен данными с внешними устройствами через параллельные или последовательные порты вво-да/вывода;

• периферийные устройства (таймерные модули, аналого-цифровые преобразователи, специализированные контроллеры);

• различные вспомогательные схемы (генератор тактовых импульсов, схемы для выполнения отладки и тестирования, сторожевой таймер и ряд других).

9

ОСНОВЫ МИКРОПРОЦЕССОРНОЙ ТЕХНИКИ

Состав устройств и блоков, входящих в структуру микропроцессора, и реализуемые механизмы их взаимодействия определяются функциональным назначением и областью применения микропроцессора.

Архитектура и структура микропроцессора тесно взаимосвязаны. Реализация тех или иных архитектурных особенностей требует введения в структуру микропроцессора необходимых аппаратных средств (устройств и блоков) и обеспечения соответствующих механизмов их совместного функционирования.

В современных микропроцессорах реализуются следующие варианты архитектур.

CISC(Complex Instruction Set Computer)-apxumeKmypa реализована во многих типах микропроцессоров, выполняющих большой набор разноформатных команд с использованием многочисленных способов адресации. Эта классическая архитектура процессоров, которая начала свое развитие в 1940-х годах с появлением первых компьютеров. Типичным примером CISC-процессоров являются микропроцессоры семейства Pentium. Они выполняют более 200 команд разной степени сложности, которые имеют размер от 1 до 15 байт и обеспечивают более 10 различных способов адресации. Такое большое многообразие выполняемых команд и способов адресации позволяет программисту реализовать наиболее эффективные алгоритмы решения различных задач. Однако при этом существенно усложняется структура микропроцессора, особенно его устройства управления, что приводит к увеличению размеров и стоимости кристалла, снижению производительности. В то же время многие команды и способы адресации используются достаточно редко. Поэтому, начиная с 1980-х годов, интенсивное развитие получила архитектура процессоров с сокращенным набором команд (RISC-процессоры).

RISC(Reduced Instruction Set Сотри(ег)-архитектура отличается использованием ограниченного набора команд фиксированного формата. Современные RISC-процессоры обычно реализуют около 100 команд, имеющих фиксированный формат длиной 4 байта. Также значительно сокращается число используемых способов адресации. Обычно в RISC-процессорах все команды обработки данных выполняются только с регистровой или непосредственной адресацией. При этом для сокращения количества обращений к памяти RISC-процессоры имеют увеличенный объем внутреннего РЭУ - от 32 до нескольких сотен регистров, тогда как в CISC-процессорах число регистров общего назначения обычно составляет 8-16.

Обращение к памяти в RISC-процессорах используется только в операциях загрузки данных в РЗУ или пересылки результатов из РЗУ в память. При этом используется небольшое число наиболее простых способов адресации: косвенно-регистровая, индексная и некоторые другие. В результате существенно упрощается структура микропроцессора, сокращаются его размеры и стоимость, значительно повышается производительность.

Указанные достоинства RISC-архитектуры привели к тому, что во многих современных CISC-процессорах используется RISC-ядро, выполняющее обработку данных. При этом поступающие сложные и разноформатные команды предварительно преобразуются в последовательность простых RISC-операций, быстро выполняемых этим процессорным ядром. Таким образом, работают, например, последние модели микропроцессоров Pentium и К7, которые по внешним показателям относятся к CISC-процессорам. Использование RISC-архитектуры является характерной чертой многих современных микропроцессоров.

VLIW(Very Large Instruction Word)-apxumeKmypa появилась относительно недавно -в 1990-х годах. Ее особенностью является использование очень длинных команд (до 128 бит и более), отдельные поля которых содержат коды, обеспечивающие выполнение различных операций. Таким образом, одна команда вызывает выполнение сразу нескольких операций параллельно в различных операционных устройствах, входящих в структуру микропроцессора. При трансляции программ, написанных на языке высокого уровня,

КЛАССИФИКАЦИЯ МИКРОПРОЦЕССОРОВ, ОСНОВНЫЕ ВАРИАНТЫ ИХ АРХИТЕКТУРЫ И СТРУКТУРЫ

соответствующий компилятор производит формирование «длинных» VLIW-команд, каждая из которых обеспечивает реализацию процессором целой процедуры или группы операций. Данная архитектура реализована в некоторых типах современных микропроцессоров (РА8500 компании «Hewlett-Packard», Itanium - совместная разработка «Intel» и «Hewlett-Packard», некоторые типы DSP-цифровых процессоров сигналов) и является весьма перспективной для создания нового поколения сверхвысокопроизводительных процессоров.

Кроме набора выполняемых команд и способов адресации важной архитектурной особенностью микропроцессоров является используемый вариант реализации памяти и организация выборки команд и данных. По этим признакам различаются процессоры с Принстонской и Гарвардской архитектурой. Эти архитектурные варианты были предложены в конце 1940-х годов специалистами соответственно Принстонского и Гарвардского университетов США для разрабатываемых ими моделей компьютеров.

Принстонская архитектура, которая часто называется архитектурой Фон-Неймана, характеризуется использованием общей оперативной памяти для хранения программ, данных, а также для организации стека. Для обращения к этой памяти используется общая системная шина, по которой в процессор поступают и команды, и данные. Эта архитектура имеет ряд важных достоинств. Наличие общей памяти позволяет оперативно перераспределять ее объем для хранения отдельных массивов команд, данных и реализации стека в зависимости от решаемых задач. Таким образом, обеспечивается возможность более эффективного использования имеющегося объема оперативной памяти в каждом конкретном случае применения микропроцессора. Использование общей шины для передачи команд и данных значительно упрощает отладку, тестирование и текущий контроль функционирования системы, повышает ее надежность. Поэтому Принстонская архитектура в течение долгого времени доминировала в вычислительной технике.

Однако ей присущи и существенные недостатки. Основным из них является необходимость последовательной выборки команд и обрабатываемых данных по общей системной шине. При этом общая шина становится «узким местом» (bottleneck - «бутылочное горло»), которое ограничивает производительность цифровой системы. Постоянно возрастающие требования к производительности микропроцессорных систем вызвали в последние годы все более широкое применение Гарвардской архитектуры при создании многих типов современных микропроцессоров.

Гарвардская архитектура характеризуется физическим разделением памяти команд (программ) и памяти данных. В ее оригинальном варианте использовался также отдельный стек для хранения содержимого программного счетчика, который обеспечивал возможности выполнения вложенных подпрограмм. Каждая память соединяется с процессором отдельной шиной, что позволяет одновременно с чтением-записью данных при выполнении текущей команды производить выборку и декодирование следующей команды. Благодаря такому разделению потоков команд и данных и совмещению операций их выборки реализуется более высокая производительность, чем при использовании Принстонской архитектуры.

Недостатки Гарвардской архитектуры связаны с необходимостью проведения большего числа шин, а также с фиксированным объемом памяти, выделенной для команд и данных, назначение которой не может оперативно перераспределяться в соответствии с требованиями решаемой задачи. Поэтому приходится использовать память большего объема, коэффициент использования которой при решении разнообразных задач оказывается более низким, чем в системах с Принстонской архитектурой. Однако развитие микроэлектронной технологии позволило в значительной степени преодолеть указанные недостатки, поэтому Гарвардская архитектура широко применяется во внутренней структуре современных высокопроизводительных микропроцессоров, где используется отдельная кэш-память для хранения команд и данных. В то же время во внешней структуре большинства микропроцессорных систем реализуются принципы Принстонской архитектуры.

11

ОСНОВЫ МИКРОПРОЦЕССОРНОЙ ТЕХНИКИ

Гарвардская архитектура получила также широкое применение в микроконтроллерах -специализированных микропроцессорах для управления различными объектами, рабочая программа которых обычно хранится в отдельном ПЗУ.

Во внутренней структуре современных высокопроизводительных микропроцессоров реализуется конвейерный принцип выполнения команд. При этом процесс выполнения команды разбивается на ряд этапов. На рис. 1.1, а приведен пример разбиения команды на шесть этапов ее выполнения:

1) выборка очередной команды (ВК);

2) декодирование выбранной команды (ДК);

3) формирование адреса операнда (ФА);

4) прием операнда из памяти (ПО);

5) выполнение операции (ВО);

6) размещение результата в памяти (РР).

Реализация каждого этапа занимает один такт машинного времени и производится устройствами и блоками процессора, образующими ступени исполнительного конвейера, на каждой из которых выполняется соответствующая микрооперация. При последовательной загрузке в конвейер выбираемых команд каждая его ступень реализует определенный этап выполнения очередной команды. Таким образом, в конвейере одновременно находятся несколько команд, находящихся на разных этапах выполнения. В идеальном варианте при полной загрузке конвейера на его выход в каждом такте будет поступать результат выполнения очередной команды (рис. 1.1, а). В этом случае производительность процессора (операций/с) будет равна его тактовой частоте (тактов/с).

Однако такая эффективная работа конвейера обеспечивается только при его равномерной загрузке однотипными командами. Реально отдельные ступени конвейера могут оказаться незагруженными, находясь в состоянии ожидания или простоя. Ожиданием называется состояние исполнительной ступени, когда она не может выполнить требуемую микрооперацию, так как еще не получен необходимый операнд, являющийся результатом выполнения предыдущей команды. Простоем называется состояние ступени, когда она вынуждена пропустить очередной такт, так как поступившая команда не требует выполнения соответствующего этапа. Например, при выполнении безадресных команд не требуется производить формирование адреса и прием операнда (простой на ступенях ФА и ПО конвейера).

Тактовые импульсы

Команды 1 | ВК Дк ФА по ВО РР Результат 1

Команды 2 ВК дк ФА ПО ВО РР Результат 2

Команды 3 ВК ДК ФА по ВО РР | Результат 3

6)

Команды 1

Команды 2

Команды 3

| ВК ДК ПР ПР во ПР Результат 1

ВК дк ож ож ФА ПО ВО ПР Результат 2

ВК дк ФА ПО ОЖ ОЖ ВО ПР | Результат 3

Рис. 1.1. Реализация конвейерного исполнения команд при идеальной (а) и реальной (6) загрузке 6-ступенчатого конвейера

КЛАССИФИКАЦИЯ МИКРОПРОЦЕССОРОВ. ОСНОВНЫЕ ВАРИАНТЫ ИХ АРХИТЕКТУРЫ И СТРУКТУРЫ

На рис. 1.1,6 показан пример работы 6-ступенчатого конвейера при выполнении фрагмента реальной программы, когда отдельные ступени оказываются в состоянии ожидания (ОЖ) или простоя (ПР). Команда INC R2, которая увеличивает на 1 содержимое регистра R2, не требует выборки операндов из памяти и размещения в ней результата. Поэтому при ее выполнении реализуется состояние простоя (ПР) на ступенях конвейера, выполняющих микрооперации ФА, ПО, РР. Команда MOV (R2), R3 производит пересылку содержимого ячейки памяти, адресуемой содержимым регистра R2, в регистр R3. При ее выполнении реализуются состояния ожидания (ОЖ), пока в регистре R2 не будет получен результат предыдущей операции. Такты ожидания (ОЖ) вводятся также при выполнении команды сложения ADD R3, (R4) до получения необходимого значения операнда в регистре R3. В результате введения состояний ожиданий и простоя реальная производительность процессора при выполнении данного фрагмента программы составит 5/3 команд/такг, то есть будет в 1,7 раз меньше, чем в идеальном случае (рис. 1.1, а).

В современных высокопроизводительных микропроцессорах процедура выполнения команд может разбиваться на еще более мелкие этапы, чтобы успеть выполнить соответствующие микрооперации на каждой ступени за один такт, длительность которого при тактовой частоте более 1 ГГц составляет менее наносекунды. Поэтому в таких процессорах число ступеней конвейера достигает 10 и более. Например, в микропроцессора) Pentium 4 используется 20-ступенчатый конвейер.

Эффективность использования конвейера определяется типом поступающих команд При поступлении однородных команд обеспечивается сокращение числа состояний про стоя и ожидания в процессе их выполнения, в результате чего повышается производи тельность процессора. При использовании в программе разноформатных команд, со держащих различное количество байтов, число состояний простоя и ожидания, которые приходится вводить в процессе выполнения команд, значительно увеличивается. Поэто му принятый во многих RISC-процессорах стандартный 4-байтный формат команд обес печивает существенное сокращение числа ожиданий и простоев конвейера, что позво ляет значительно повысить производительность.

Другой причиной снижения эффективности конвейера являются команды условной ветвления. Если выполняется условие ветвления, то приходится производить перезаг рузку конвейера командами из другой ветви программы, что требует выполнения долог нительных рабочих тактов и вызывает значительное снижение производительности. Пс этому одним из основных условий эффективной работы конвейера является сокращена числа его перезагрузок при выполнении условных переходов. Эта цель достигается помощью реализации различных механизмов предсказания направления ветвления, кс торые обеспечиваются с помощью специальных устройств - блоков предсказания вете пения, вводимых в структуру процессора.

В современных микропроцессорах используются разнообразные способы предсказг ния ветвлений. Наиболее простой способ состоит в том, что процессор фиксирует ре зультат выполнения предыдущих команд ветвления по данному адресу и считает, чт следующая команда с обращением по этому адресу даст аналогичный результат, flat ный способ предсказания предполагает более высокую вероятность повторного обр< щения к определенной команде, задаваемой данным условием ветвления. Для реализг ции этого способа предсказания ветвления используется специальная память ВТВ (Вгапс Target Buffer), где хранятся адреса ранее выполненных условных переходов. При посту| пении аналогичной команды ветвления предсказывается переход к ветви, которая быг выбрана в предыдущем случае, и производится загрузка в конвейер команд из соотве ствующей ветви. При правильном предсказании не требуется перезагрузка конвейера эффективность его использования не снижается. Эффективность такого способа пре, сказания зависит от емкости ВТВ и оказывается достаточно высокой: вероятность пр

1

ОСНОВЫ МИКРОПРОЦЕССОРНОЙ ТЕХНИКИ

вильного предсказания составляет 80% и более. Повышение точности предсказания достигается при использовании более сложных способов, когда хранится и анализируется предыстория переходов - результаты нескольких предыдущих команд ветвления по данному адресу. В этом случае возможно определение чаще всего реализуемого направления ветвления, а также выявление чередующихся переходов. Реализация таких алгоритмов требует использования более сложных блоков предсказания, но при этом вероятность правильного предсказания повышается до 90-95%.

Возможность повышения производительности процессора достигается также при введении в структуру процессора нескольких параллельно включенных операционных устройств, обеспечивающих одновременное выполнение нескольких операций. Такая структура процессора называется суперскалярной. В этих процессорах реализуется параллельная работа нескольких исполнительных конвейеров, в каждый из которых поступает для выполнения одна из выбранных и декодированных команд. В идеальном случае число одновременно выполняемых команд равно числу операционных устройств, включенных в исполнительные конвейеры. Однако при выполнении реальных программ трудно обеспечить полную загрузку всех исполнительных конвейеров, поэтому на практике эффективность использования суперскалярной структуры оказывается несколько ниже. Современные суперскалярные процессоры содержат до 4 до 10 различных операционных устройств, параллельная работа которых обеспечивает выполнение за один такт в среднем от 2 до 6 команд.

Эффективная одновременная работа нескольких исполнительных конвейеров обеспечивается путем предварительной выборки-декодирования ряда команд и выделения из них группы команд, которые могут выполняться одновременно. В современных суперскалярных процессорах производится выборка нескольких десятков команд, которые декодируются, анализируются и группируются для параллельной загрузки в исполнительные конвейеры. Обычно в процессорах имеется несколько устройств для выполнения целочисленных операций, одно или несколько устройств для обработки чисел с плавающей точкой, отдельные устройства для обработки специальных форматов видео- и аудиоданных. Параллельно работают также устройства формирования адресов и выборки операндов для загружаемых команд. При этом обычно реализуется спекулятивная (предварительная) выборка операндов, чтобы для поступающих на исполнение команд уже были готовы операнды, которые записываются в специальные регистры. Чтобы обеспечить возможно полную загрузку исполнительных конвейеров, в процессе анализа и группировки декодированных команд возможно изменение порядка их следования. В результате команды выполняются не в порядке их выборки из памяти, а по мере готовности необходимых операндов и исполнительных устройств. Таким образом, позже поступившие команды могут быть выполнены до ранее выбранных. Чтобы запись в память результатов происходила в соответствии с исходной последовательностью поступления команд программы, на выходе данных включается специальная буферная память, восстанавливающая порядок выдачи результатов согласно выполняемой программе.

Одновременное параллельное выполнение команд может оказаться невозможным, если они обращаются к одному регистру. При ограниченной емкости РЗУ процессора такие случаи могут возникать достаточно часто, что снижает эффективность работы исполнительных конвейеров. Поэтому в ряде процессоров вводятся специальные регистровые блоки, дублирующие РЗУ. При поступлении команд, которые обращаются к одинаковым регистрам РЗУ, производится их переадресация к дублирующим регистровым блокам - «переименование» регистров. В результате обеспечивается возможность одновременного выполнения таких команд, что позволяет реализовать более эффективную параллельную работу исполнительных конвейеров.

В качестве примера на рис. 1.2 показана типичная суперскалярная структура процессора с Гарвардской архитектурой, которая реализована в высокопроизводительных 32-

КЛАССИФИКАЦИЯ МИКРОПРОЦЕССОРОВ. ОСНОВНЫЕ ВАРИАНТЫ ИХ АРХИТЕКТУРЫ И СТРУКТУРЫ

шины

Рис. 1.2. Типичная суперскалярная структура процессора с Гарвардской внутренней архитектурой разрядных микропроцессорах семейства PowerPC, выпускаемых компаниями Motorola и IBM. Гарвардская архитектура обеспечивается разделением потоков команд и данных во внутренней структуре процессора путем использования отдельных блоков кэш-памя-ти IC (кэш-команд) и DC (кэш-данных). Каждая кэш-память имеет отдельный блок управления MMU (Memory Managment Unit). В процессоре реализуется 6-ступенчатый конвейер выполнения команд. Устройство управления содержит три первых ступени конвейера, реализующие выборку, декодирование и распределение команд по параллельно работающим исполнительным устройствам. Команды условных ветвлений поступают на выполнение в блок предсказания ветвлений BPU (Branch Prediction Unit), который обеспечивает загрузку в конвейер следующих команд в соответствии с наиболее вероятным направлением хода программы. Исполнительные устройства сгруппированы в два блока. Блок целочисленных операций содержит два исполнительных устройства - SIU1 и SIU2 (Single Instruction Unit)-для простых операций, выполняемых за один такт, и одно устройство для выполнения сложных операций MIU (Multiple Instruction Unit), которые занимают несколько тактов. Эти устройства обслуживаются блоком из 32 регистров общего назначения GPR (General Purpose Registers). Блок FPU (Floating Point Unit) выполняет операции с плавающей точкой за несколько тактов. Он обслуживается отдельным блоком из 32 регистров FPR (Floating Point Registers), которые имеют по 64 разряда. Каждый из регистровых блоков имеет набор дублирующих регистров (буферы GPR и FPR), которые обеспечивают возможность «переименования» регистров в случае их одновременного использования несколькими командами, находящимися на стадии исполнения. Блок LSU (Load-Store Unit) производит операции загрузки регистров из памяти и записи содержимого регистров в память. После выполнения операций полученные результаты поступают в блок завершения, где они накапливаются в специальной буферной памяти, а затем записываются в кэш-данных или основную память в соответствии с исходной последовательностью команд программы (процедура обратной записи, восстанавливающая нормальную последовательность выдачи результатов). Контроллер шины BIU (Bus Interface Unit) обеспечивает обращение к системной шине, которая содержит 32-разрядную шину адреса А31-0, 64-разрядную шину данных D63-0 и многочисленные линии для передачи управляющих сигналов Схх.

ОСНОВЫ МИКРОПРОЦЕССОРНОЙ ТЕХНИКИ

Рис. 1.3. Классификация современных микропроцессоров по функциональному признаку

Хотя микропроцессор является универсальным средством для цифровой обработки информации, однако отдельные области применения требуют реализации определенных специфических вариантов их структуры и архитектуры. Поэтому по функциональному признаку выделяются два класса: микропроцессоры общего назначения и специализированные микропроцессоры (рис. 1.3). Среди специализированных микропроцессоров наиболее широкое распространение получили микроконтроллеры, предназначенные для выполнения функций управления различными объектами, и цифровые процессоры сигналов (DSP - Digital Signal Processor), которые ориентированы на реализацию процедур, обеспечивающих необходимое преобразование аналоговых сигналов, представленных в цифровой форме (в виде последовательности числовых значений).

Микропроцессоры общего назначения предназначены для решения широкого круга задач обработки разнообразной информации. Их основной областью использования являются персональные компьютеры, рабочие станции, серверы и другие цифровые системы массового применения. К этому классу относятся CISC-процессоры Pentium компании «Intel», К7 - компании «Advanced MicroDevices» (AMD), 680x0 - компании «Motorola», RISC-процессоры PowerPC, выпускаемые компаниями «Motorola» и IBM, SPARC - компании «Sun Microsystems» и ряд других изделий различных производителей.

Расширение области применения таких микропроцессоров достигается главным образом путем роста производительности, благодаря чему увеличивается круг задач, который можно решать с их использованием. Поэтому повышение производительности является магистральным направлением развития этого класса микропроцессоров. Обычно это 32-разрядные микропроцессоры (некоторые микропроцессоры этого класса имеют 64-разрядную или 128-разрядную структуру), которые изготавливаются по самой современной промышленной технологии, обеспечивающей максимальную частоту функционирования.

Ряд наиболее популярных микропроцессоров этого класса (Pentium, AMD К7 и некоторые другие) следует отнести к CISC-процессорам, так как они выполняют большой набор разноформатных команд с использованием многочисленных способов адресации. Однако в их внутренней структуре содержится RISC-процессор, который выполняет поступившие команды после их преобразования в последовательность простых RISC-операций. Ряд других микропроцессоров этого класса непосредственно реализует RISC-

КЛАССИФИКАЦИЯ МИКРОПРОЦЕССОРОВ. ОСНОВНЫЕ ВАРИАНТЫ ИХ АРХИТЕКТУРЫ И СТРУКТУРЫ

архитектуру. Поэтому можно считать, что использование RISC-архитектуры характерно для большинства этих микропроцессоров. Однако в ряде последних разработок (Itanium, РА8500) некоторых ведущих производителей успешно применяются принципы VLIW-ap-хитектуры, которая может составить конкуренцию RISC-архитектуре в соревновании за достижение наивысшей производительности.

Практически все современные микропроцессоры этого класса используют Гарвардскую внутреннюю архитектуру, где разделение потоков команд и данных реализуется с помощью отдельных блоков кэш-памяти. В большинстве случаев они имеют суперскалярную структуру с несколькими исполнительными конвейерами (до 10 в современных моделях), которые содержат до 20 ступеней.

Благодаря своей универсальности микропроцессоры общего назначения используются также в специализированных системах, где требуется высокая производительность. На их основе реализуются одноплатные компьютеры и промышленные компьютеры, которые применяются в системах управления различными объектами. Одноплатные (встраиваемые) компьютеры содержат на плате необходимые дополнительные микросхемы, обеспечивающие их специализированное применение, и предназначены для встраивания в аппаратуру различного назначения. Промышленные компьютеры размещаются в корпусах специальной конструкции, обеспечивающих их надежную работу в жестких производственных условиях. Обычно такие компьютеры работают без стандартных периферийных устройств (монитор, клавиатура, «мышь») или используют специальные варианты этих устройств, модифицированные с учетом специфических условий применения.

Микроконтроллеры являются специализированными микропроцессорами, которые ориентированы на реализацию устройств управления, встраиваемых в разнообразную -Yi. аппаратуру. Ввиду огромного количества объектов, управление которыми обеспечивает-\ ся с помощью микроконтроллеров, годовой объем их выпуска превышает 2 миллиарда экземпляров, на порядок превосходя объем выпуска микропроцессоров общего приме-нения. Весьма широкой является также номенклатура выпускаемых микроконтроллеров, ' которая содержит несколько тысяч типов.

' S Характерной особенностью структуры микроконтроллеров является размещение на одном кристалле с центральным процессором внутренней памяти и большого набора периферийных устройств. В состав периферийных устройств обычно входят несколько 8-разрядных параллельных портов ввода-вывода данных (от 1 до 8), один или два последовательных порта, таймерный блок, аналого-цифровой преобразователь. Кроме того, различные типы микроконтроллеров содержат дополнительные специализированные устройства - блок формирования сигналов с широтно-импульсной модуляцией, контроллер жидкокристаллического дисплея и ряд других. Благодаря использованию внутренней памяти и периферийных устройств реализуемые на базе микроконтроллеров системы управления содержат минимальное количество дополнительных компонентов.

В связи с широким диапазоном решаемых задач управления требования, предъявляемые к производительности процессора, объему внутренней памяти команд и данных, набору необходимых периферийных устройств, оказываются весьма разнообразными. Для удовлетворения запросов потребителей выпускается большая номенклатура микроконтроллеров, которые принято подразделять на 8-, 16- и 32-разрядные.

• 8-разрядные микроконтроллеры представляют наиболее многочисленную группу этого класса микропроцессоров, которые имеют относительно низкую производительность, которая, однако, вполне достаточна для решения широкого круга задач управления различными объектами. Это простые и дешевые микроконтроллеры, ориентированные на использование в относительно несложных устройствах массового выпуска. Основными областями их применения являются бытовая и измерительная техника, промышленная автоматика, автомобильная электроника, теле-, видео- и аудиоаппаратура, средства связи.

ОСНОВЫ МИКРОПРОЦЕССОРНОЙ ТЕХНИКИ

Для этих микроконтроллеров характерна реализация Гарвардской архитектуры, где используется отдельная память для хранения программ и данных. Для хранения программ в различных типах микроконтроллеров применяется либо масочно-программируемое ПЗУ (ROM), либо однократно-программируемое ПЗУ (PROM), либо электрически репрограммируемое ПЗУ (EPROM, EEPROM или Flash). Внутренняя память программ обычно имеет объем от нескольких единиц до десятков Кбайт. Для хранения данных используется регистровый блок, организованный в виде нескольких регистровых банков, или внутреннее ОЗУ. Объем внутренней памяти данных составляет от нескольких десятков байт до нескольких Кбайт. Ряд микроконтроллеров этой группы позволяет в случае необходимости дополнительно подключать внешнюю память команд и данных, объемом до 64—256 Кбайт.

Микроконтроллеры этой группы обычно выполняют относительно небольшой набор команд (50-100), использующих наиболее простые способы адресации. В ряде последних моделей этих микроконтроллеров реализованы принципы RISC-архитектуры, что позволяет существенно повысить их производительность. В результате такие микроконтроллеры обеспечивают выполнение большинства команд за один такт машинного времени.

• 16-разрядные микроконтроллеры во многих случаях являются усовершенствованной модификацией своих 8-разрядных прототипов. Они характеризуются не только увеличенной разрядностью обрабатываемых данных, но и расширенной системой команд и способов адресации, увеличенным набором регистров и объемом адресуемой памяти, а также рядом других дополнительных возможностей, использование которых позволяет повысить производительность и обеспечить новые области применения. Обычно эти микроконтроллеры позволяют расширить объем памяти программ и данных до нескольких Мбайт путем подключения внешних микросхем памяти. Во многих случаях реализуется их программная совместимость с более младшими 8-разрядными моделями. Основная сфера применения таких микроконтроллеров - сложная промышленная автоматика, телекоммуникационная аппаратура, медицинская и измерительная техника.

• 32-разрядные микроконтроллеры содержат высокопроизводительный процессор, соответствующий по своим возможностям младшим моделям микропроцессоров общего назначения. В ряде случаев процессор, используемый в этих микроконтроллерах, аналогичен CISC- или RISC-процессорам, которые выпускаются или выпускались ранее в качестве микропроцессоров общего назначения. Например, в 32-разрядных микроконтроллерах компании Intel используется процессор I386, в микроконтроллерах компании Motorola широко применяется процессор 680x0, в ряде других микроконтроллеров в качестве процессорного ядра служат RISC-процессоры типа PowerPC. На базе данных процессоров были реализованы различные модели персональных компьютеров. Введение этих процессоров в состав микроконтроллеров позволяет использовать в соответствующих системах управления огромный объем прикладного и системного программного обеспечения, созданный ранее для соответствующих персональных компьютеров.

Кроме 32-разрядного процессора на кристалле микроконтроллера размещается внутренняя память команд емкостью до десятков Кбайт, память данных емкостью до нескольких Кбайт, а также сложно-функциональные периферийные устройства - таймерный процессор, коммуникационный процессор, модуль последовательного обмена и ряд других. Микроконтроллеры работают с внешней памятью объемом до 16 Мбайт и выше. Они находят широкое применение в системах управления сложными объектами промышленной автоматики (двигатели, робототехнические устройства, средства комплексной автоматизации производства), в контрольно-измерительной аппаратуре и телекоммуникационном оборудовании.

Во внутренней структуре этих микроконтроллеров реализуется Принстонская или Гарвардская архитектура. Входящие в их состав процессоры могут иметь CISC- или RISC-

ОБЩАЯ СТРУКТУРА И ПРИНЦИПЫ ФУНКЦИОНИРОВАНИЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ

архитектуру, а некоторые из них содержат несколько исполнительных конвейеров, образующих суперскалярную структуру.

Цифровые процессоры сигналов (ЦПС) представляют класс специализированных микропроцессоров, ориентированных на цифровую обработку поступающих аналоговых сигналов. Специфической особенностью алгоритмов обработки аналоговых сигналов является необходимость последовательного выполнения ряда команд умножения-сложения с накоплением промежуточного результата в регистре-аккумуляторе. Поэтому архитектура ЦПС ориентирована на реализацию быстрого выполнения операций такого рода. Набор команд этих процессоров содержит специальные команды MAC (Multiplication with Accumlation), реализующие эти операции.

Значение поступившего сигнала может быть представлено в виде числа с фиксированной или с «плавающей» точкой. В соответствии с этим ЦПС делятся на процессоры, обрабатывающие числа с фиксированной или плавающей точкой. Более простые и дешевые ЦПС с фиксированной точкой обычно обрабатывают 16-разрядные операнды, представленные в виде правильной дроби. Однако ограниченная разрядность в ряде случаев не позволяет обеспечить необходимую точность преобразования. Поэтому в ЦПС с фиксированной точкой, выпускаемых компанией «Motorola», принято 24-разрядное представление операндов. Наиболее высокая точность обработки обеспечивается в случае представления данных в формате с «плавающей» точкой. В ЦПС, обрабатывающих данные с «плавающей» точкой, обычно используется 32-разрядный формат их представления.

Для повышения производительности при выполнении специфических операций обработки сигналов в большинстве ЦПС реализуется Гарвардская архитектура с использованием нескольких шин для передачи адресов, команд и данных. В ряде ЦПС нашли применение также некоторые черты VLIW-архитектуры: совмещение в одной команде нескольких операций, обеспечивающих обработку имеющихся данных и одновременную загрузку в исполнительный конвейер новых данных для последующей обработки.

1.2. ОБЩАЯ СТРУКТУРА И ПРИНЦИПЫ ФУНКЦИОНИРОВАНИЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ

Большинство микропроцессорных систем имеет магистрально-модульную структуру (рис. 1.4), в которой отдельные устройства (модули), входящие в состав системы, обмениваются информацией по общей системной шине - магистрали.

Основным модулем системы является микропроцессор, который содержит устройство управления (УУ), операционное устройство (ОУ) и регистровое запоминающее устройство (РЗУ) - внутреннюю память, реализованную в виде набора регистров. Оперативное запоминающее устройство (ОЗУ) служит для хранения выполняемой программы (или ее фрагментов) и данных, подлежащих обработке. В простейших микропроцессорных системах объем ОЗУ составляет десятки и сотни байт, а современных персональных компьютерах, серверах и рабочих станциях он достигает сотен Мбайт и более. Так как обращение к ОЗУ по системной шине требует значительных затрат времени, в большинстве современных высокопроизводительных микропроцессоров дополнительно вводится быстродействующая промежуточная память (кэш-память) ограниченного объема (от нескольких Кбайт до сотен Кбайт).

Постоянное запоминающее устройство (ПЗУ) служит для хранения констант и стандартных (неизменяемых) программ. В ПЗУ обычно записываются программы начальной инициализации (загрузки) систем, тестовые и диагностические программы и другое служебное программное обеспечение, которое не меняется в процессе эксплуатации систем. В микропроцессорных системах, управляющих определенными объектами с исполь

19

ОСНОВЫ МИКРОПРОЦЕССОРНОЙ ТЕХНИКИ

зованием фиксированных или редко изменяемых программ, для их хранения также обычно используется ПЗУ (память ROM - Read-Only Memory) или репрограммируемое ПЗУ (память EEPROM - Electrically Erased Programmable Read-Only Memory или флэш-память).

Остальные устройства являются внешними и подключаются к системе с помощью интерфейсных устройств (ИУ), реализующих определенные протоколы параллельного или последовательного обмена. Такими внешними устройствами могут быть клавиатура, монитор, внешние запоминающие устройства (ВЗУ), использующие гибкие или жесткие магнитные диски, оптические диски (CD-ROM), магнитные ленты и другие виды носителей информации, датчики и преобразователи информации (аналого-цифровые или цифроаналоговые), разнообразные исполнительные устройства (индикаторы, принтеры, электродвигатели, реле и другие). Для реализации различных режимов работы к системе могут подключаться дополнительные устройства - контроллеры прерываний, прямого доступа к памяти и другие, реализующие необходимые специальные функции управления.

Данная структура соответствует архитектуре Фон-Неймана, предложенной этим ученым в 1940-х годах для реализации первых моделей цифровых ЭВМ. Ниже будут рассмотрены и другие варианты процессорных архитектур.

Системная шина содержит несколько десятков (в сложных системах более 100) проводников, которые в соответствии с их функциональным назначением подразделяются на отдельные шины - адреса А, данных D и управления С. Шина А служит для передачи адреса, который формируется микропроцессором и позволяет выбрать необходимую ячейку памяти ОЗУ (ПЗУ) или требуемое ИУ при обращении к внешнему устройству. Шина D служит для выборки команд, поступающих из ОЗУ или ПЗУ в УУ микропроцессора, и для пересылки обрабатываемых данных (операндов) между микропроцессором и ОЗУ или ИУ (внешним устройством). По шине С передаются разнообразные управляющие сигналы, определяющие режимы работы памяти (запись или считывание), интерфейсных устройств (ввод или вывод информации) и микропроцессора (запуск, запросы внешних устройств на обслуживание, информация о текущем режиме работы и другие сигналы).

Рис. 1.4. Типовая структура микропроцессорной системы

ОБЩАЯ СТРУКТУРА И ПРИНЦИПЫ ФУНКЦИОНИРОВАНИЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ

Разрядность шины данных обычно соответствует разрядности операндов, обрабатываемых микропроцессором. Поэтому чаще всего шина D содержит 8, 16 или 32 линии для передачи соответствующих разрядов данных и команд. В ряде последних моделей микропроцессоров используется шина D с расширенной разрядностью, чтобы обеспечить одновременную передачу нескольких команд или операндов. Например, 32-разряд-ные микропроцессоры Pentium имеют 64-разрядную шину данных.

Разрядность шины адреса определяет максимальный объем адресуемой процессором внешней памяти. Например, 16-разрядная шина А обеспечивает адресацию памяти объемом до 64 Кбайт, а 32-разрядная шина-до 4 Гбайт. Процессоры Pentium II, Pentium 111, Pentium IV имеют 36-разрядную шину адреса, обеспечивающую обращение к памяти объемом до 64 Гбайт. Отметим, что в ряде микропроцессоров, например в Pentium, вместо младших разрядов адреса формируются сигналы выборки соответствующих байтов (сигналы байтной выборки BEi, где i - номер байта), которые позволяют организовать хранение байтов в отдельных банках памяти.

Во многих микропроцессорных системах передача адреса и данных сопровождается посылкой контрольных битов четности, которые обеспечивают выявление возможных ошибок, возникающих в процессе обмена. При этом обычно реализуется побайтный контроль четности, при котором каждый байт адреса или данных сопровождается дополнительным (9-м) контрольным битом, поступающим на отдельный вывод микропроцессора.

В некоторых системах для уменьшения числа необходимых линий связи и соответствующих выводов и контактов используется мультиплексирование линий адреса и данных. В таких системах для передачи адреса и данных используются одни и те же линии связи, на которые сначала выдается адрес, а затем поступают данные. Например, 16-разрядные микроконтроллеры семейства MCS-196, выпускаемые компанией Intel, имеют мультиплексированную 16-разрядную шину адреса данных AD. Обмен информацией по мультиплексированной шине AD требует введения отдельного регистра для хранения адреса в процессе пересылки данных. При этом требуется также дополнительное время для реализации обмена, что несколько снижает производительность системы.

Разрядность шины управления С определяется организацией работы системы, возможностями реализации различных режимов ее функционирования, используемыми методами контроля микропроцессора и других устройств. Поэтому набор передаваемых по шине С управляющих сигналов является индивидуальным для каждой модели микропроцессора. Имеется ряд управляющих сигналов, которые используются в большинстве микропроцессорных систем. К ним относятся сигналы начального запуска (RESET), сигналы, задающие режим работы памяти (чтение - RD, запись - WR), сигналы, необходимые для реализации прерываний и ряд других. В простых системах для передачи управляющих сигналов может использоваться всего несколько линий, а в сложных системах число этих линий составляет несколько десятков.

В процессе функционирования микропроцессорной системы реализуются следующие основные режимы ее работы:

• выполнение основной программы;

• вызов подпрограммы;

• обслуживание прерываний и исключений;

• прямой доступ к памяти.

Рассмотрим основные принципы реализации этих режимов.

Выполнение основной программы. В этом режиме процессор выбирает из ОЗУ очередную команду программы и выполняет соответствующую операцию. Команда представляет собой многоразрядное двоичное число (рис. 1.5), которое состоит из двух частей (полей) - кода опера-

Код операции (КОП) код адресации операндов (КАД)

Рис. 1.5. Формат типовой команды микропроцессора

21

ОСНОВЫ МИКРОПРОЦЕССОРНОЙ ТЕХНИКИ

ции (КОП) и кода адресации операндов (КАД). Код операции КОП задает вид операции, выполняемой данной командой, а код адресации КАД определяет выбор операндов (способ адресации), над которыми производится заданная операция. В зависимости от типа микропроцессора команда может содержать различное число разрядов (байтов). Например, команды процессоров Pentium содержат от 1 до 15 байтов, а большинство процессоров с RlSC-архитек-турой использует фиксированный 4-байтный формат для любых команд.

Для хранения адреса очередной команды служит специальный регистр процессора -программный счетчик PC (Program Counter), содержимое которого автоматически увеличивается на 1 после выборки следующего байта команды. Таким образом, обеспечивается последовательная выборка команд в процессе выполнения программы. При выборке очередной команды содержимое PC поступает на шину адреса, обеспечивая считывание из ОЗУ следующей команды выполняемой программы. При реализации безусловных или условных переходов (ветвлений) или других изменений последовательности выполнения команд выполняется загрузка в PC нового содержимого, в результате чего производится переход к другой ветви программы или подпрограмме.

В процессорах Pentium и предыдущих моделях микропроцессоров компании «Intel» (8086, 80186, 80286, 386, 486 и ряде других) реализуется сегментная организация памяти. При этом адрес выбираемой команды определяется содержимым двух регистров -указателя команды EIP, указывающего положение команды в сегменте программ, и сегментного регистра CS, который задает начальный (базовый) адрес этого сегмента. Регистры IP и CS выполняют функции программного счетчика PC, и различные виды передачи управления в программе реализуются путем изменения их содержимого.

Принятая из ОЗУ команда поступает в регистр команд, входящий в состав УУ процессора. Затем производится дешифрация команды, в процессе которой определяется вид выполняемой операции (расшифровка КОП) и формируется адрес необходимых операндов (расшифровка КАД). В соответствии с кодом поступившей команды УУ процессора генерирует последовательность микрокоманд, обеспечивающих выполнение заданной операции. Каждая микрокоманда выполняется в течение одного машинного такта - периода тактовых импульсов, задающих рабочую частоту всех внутренних узлов и блоков микропроцессора. Таким образом, тактовая частота микропроцессора определяет время выполнения отдельных микрокоманд, последовательность которых обеспечивает получение необходимого результата операции (поступившей команды).

Для выполнения каждой поступившей команды требуется определенное количество командных циклов и тактов. Командным циклом называется промежуток времени, требуемый для выполнения обращения к ОЗУ или внешнему устройству с помощью системной шины. Обычно реализация такого цикла занимает от 2 до 4 системных тактов (периодов синхросигналов шины), которые требуются для установки требуемого адреса, выдачи сигналов, определяющих вид цикла - чтение или запись, получения сигнала готовности к обмену (от памяти или внешних устройств) и собственно передачи данных или команд. При современной технологии изготовления системных плат частота синхросигналов шины обычно составляет десятки мегагерц (типичные значения 25, 33, 50, 66, 75,100, 133 МГц).

При выполнении каждой команды в первых циклах производится ее выборка из ОЗУ по адресу, который задается содержимым программного счетчика PC. Последующая дешифрация выбранной команды определяет необходимое число циклов для ее последующего выполнения. Если для выполнения команды не требуется считывание операндов из памяти (внешних устройств) или запись в память (вывод на внешние устройства) результатов операции, то такая команда выполняется за один цикл. При считываний операндов из памяти (внешних устройств) или записи результата в память (вывод на внешние устройства) требуется выполнение дополнительных циклов чтения (ввода) или записи (вывода). В зависимости от разрядности обрабатываемых операндов и разряд

ОБЩАЯ СТРУКТУРА И ПРИНЦИПЫ ФУНКЦИОНИРОВАНИЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ

ности используемой системной шины число циклов, необходимых для выполнения команд, может быть различным: от 1 (выборка команды) до 4-5 (зависит от команды, разрядности шин и операндов).

Машинным (процессорным) тактом в микропроцессорных системах является длительность периода тактовых сигналов Tt, которая задается тактовой частотой микропроцессора Ft= 1/Tt. При выполнении операций, не требующих обращений к системной шине, (эта частота определяет производительность микропроцессора. Для современных микропроцессоров частота Ft достигает 1 ГГц и более (последние модели микропроцессоров Pentium, AMD К7, Alpha и другие). Таким образом, обработка информации внутри процессора (без обращения к системной шине) производится значительно быстрее, чем обмен по шине. Если тактовая частота микропроцессора отличается от частоты обмена по системной шине, то вывод данных на шину реализуется с помощью промежуточной буферной памяти, в которой хранятся данные, посылаемые микропроцессором на системную шину. Данные выбираются из буферной памяти и поступают на системную шину с частотой, соответствующей скорости обмена по этой шине.

Текущее состояние процессора при выполнении программы определяется содержимым регистра состояния SR (State Register, в микропроцессорах Pentium данный регистр называется EFLAGS). Этот регистр содержит биты управления, задающие режим работы процессора, и биты признаков (флаги), указывающие характеристики результата выполненной операции:

N - признак знак (старший бит результата), N = 0 - при положительном результате, N = 1 -при отрицательном результате;

С - признак перенос, С = 1, если при выполнении операции образовался перенос из старшего разряда результата;

V - признак переполнения, V = 1, если при выполнении операций над числами со знаком произошло переполнение разрядной сетки процессора;

Z - признак нуля, Z = 1, если результат операции равен нулю.

Некоторые микропроцессоры фиксируют также другие виды признаков: признак четности результата, признак переноса между тетрадами младшего байта. Специальные виды признаков устанавливаются по результатам операций над числами, представленными в формате с «плавающей точкой».

Вызов подпрограммы. Обращение к подпрограмме реализуется при поступлении в микропроцессор специальной команды CALL (в некоторых процессорах эта команда имеет мнемоническое обозначение JSR - Jump-to-SubRoutine), которая указывает адрес первой команды вызываемой подпрограммы. Этот адрес загружается в PC, обеспечивая в следующем командном цикле выборку первой команды подпрограммы. Предварительно выполняется процедура сохранения в специальном регистре или ячейке памяти текущего содержимого PC, где хранится адрес следующей команды основной программы, чтобы обеспечить возвращение к ней после выполнения подпрограммы. Возврат к основной программе реализуется при поступлении команды RETURN (мнемоническое обозначение RET), завершающей подпрограмму. По этой команде сохранявшееся содержимое PC снова загружается в программный счетчик, обеспечивая выполнение команды, которая в исходной программе следовала за командой CALL.

Особенность этой процедуры состоит в том, что большинство микропроцессоров обеспечивают возможности вложения подпрограмм, т. е. реализуют при выполнении подпрограммы вызов новой подпрограммы с последующим возвращением к предыдущей подпрограмме (рис. 1.6). При вложении нескольких подпрограмм требуется сохранение нескольких промежуточных значений содержимого PC и последовательная загрузка этих значений в PC при возврате к предыдущим подпрограммам и к основной программе.

Для реализации этой процедуры используется стек-специальная память магазинного типа, работающая по принципу «последний пришел - первый ушел» (стек типа LIFO — «Last In-First Out»). Существуют различные варианты реализации стека.

ОСНОВЫ МИКРОПРОЦЕССОРНОЙ ТЕХНИКИ

Основная программа Подпрограмма 1 Подпрограмма 2

Рис. 1,6. Последовательный вызов (вложение) подпрограмм

Регистровый стек (рис. 1.7, а) реализуется с помощью реверсивных сдвиговых регистров. Каждая команда CALL вызывает ввод в стек очередного содержимого PC. По команде RETURN направление сдвига изменяется и производится извлечение из стека последнего поступившего содержимого PC. Таким образом обеспечивается выполнение вложенных подпрограмм. Возможное число вложенных подпрограмм определяется глубиной стека, т. е. разрядностью используемых регистров сдвига. Если число вложений превышает глубину стека, первые из введенных в стекзначений PC теряются, т. е. возврат к основной программе не будет обеспечен. Поэтому при использовании регистрового стека необходим строгий контроль за числом вложений. Такая реализация стека применяется в системах, решающих задачи с ограниченным числом вложенных подпрограмм (обычно не более 10-20).

Значительно более широкие возможности вложения подпрограмм обеспечивает реализация стека в ОЗУ (рис.1.7, б). В этом случае часть ОЗУ выделяется для работы в качестве стека. Адресация к ячейкам стека производится с помощью специального регистра - указателя стека SP (Stack Pointer), который вводится в состав УУ процессора. Регистр SP содержит адрес верхней заполненной ячейки стека, в которой хранится значение PC, записанное при выполнении команды CALL. При поступлении новой команды CALL содержимое SP автоматически уменьшается на 1, адресуя следующую, еще незаполненную ячейку стека. Полученный адрес SP-1 выдается на шину А, а на шину D поступает содержимое PC, которое должно сохраняться в стеке. Таким образом, производится последовательное заполнение ячеек стека «снизу-вверх», при этом SP всегда адресует вершину стека. По команде RETURN текущее содержимое SP выдается на шину А, и по шине D производится считывание с вершины стека последнего записанного значения PC. После этого содержимое SP увеличивается на 1, адресуя предыдущее значение PC, хранящееся в стеке. Так как ОЗУ обычно имеет значительный объем, то для размещения стека можно выделить достаточно большое количество ячеек памяти, обеспечивая необходимый уровень вложения подпрограмм.

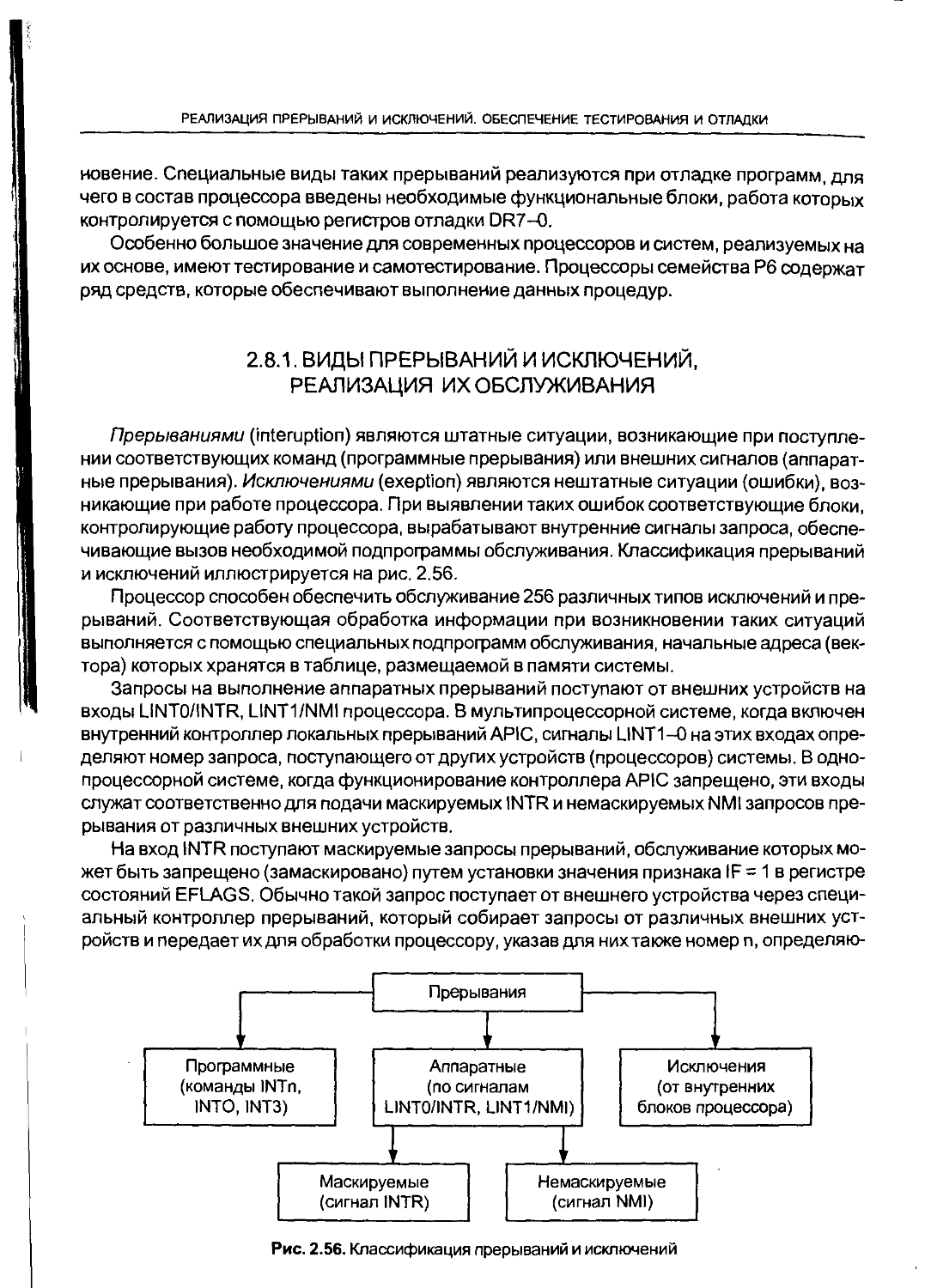

Обслуживание прерываний и исключений. При работе микропроцессорной системы часто возникают ситуации, когда требуется прервать выполнение текущей программы и перейти к подпрограмме, обеспечивающей необходимую реакцию системы на создавшиеся обстоятельства. Такие ситуации называются прерываниями или исключениями в зависимости от причин, вызывающих их возникновение.

ОБЩАЯ СТРУКТУРА И ПРИНЦИПЫ ФУНКЦИОНИРОВАНИЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ

после (RETURN)

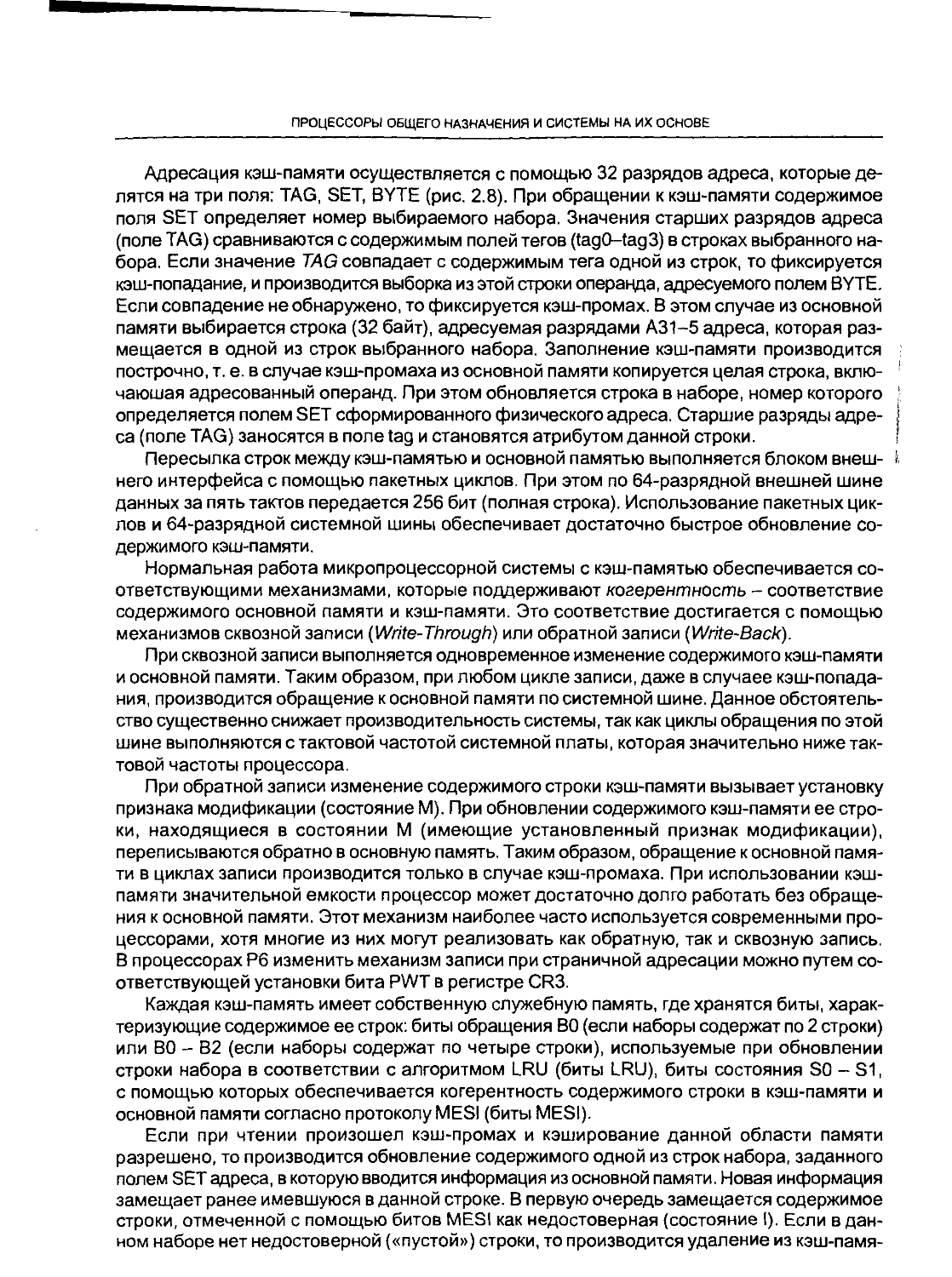

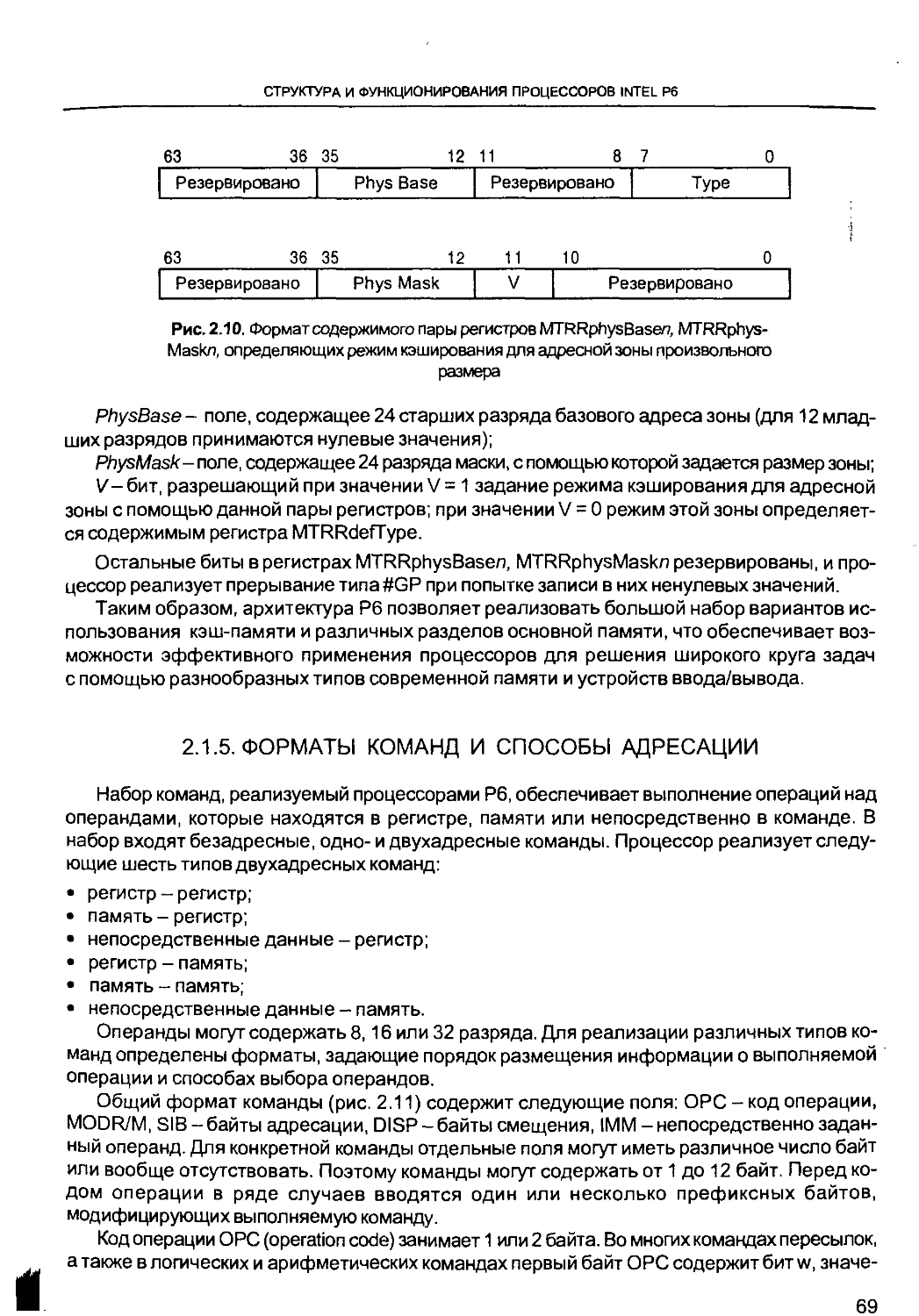

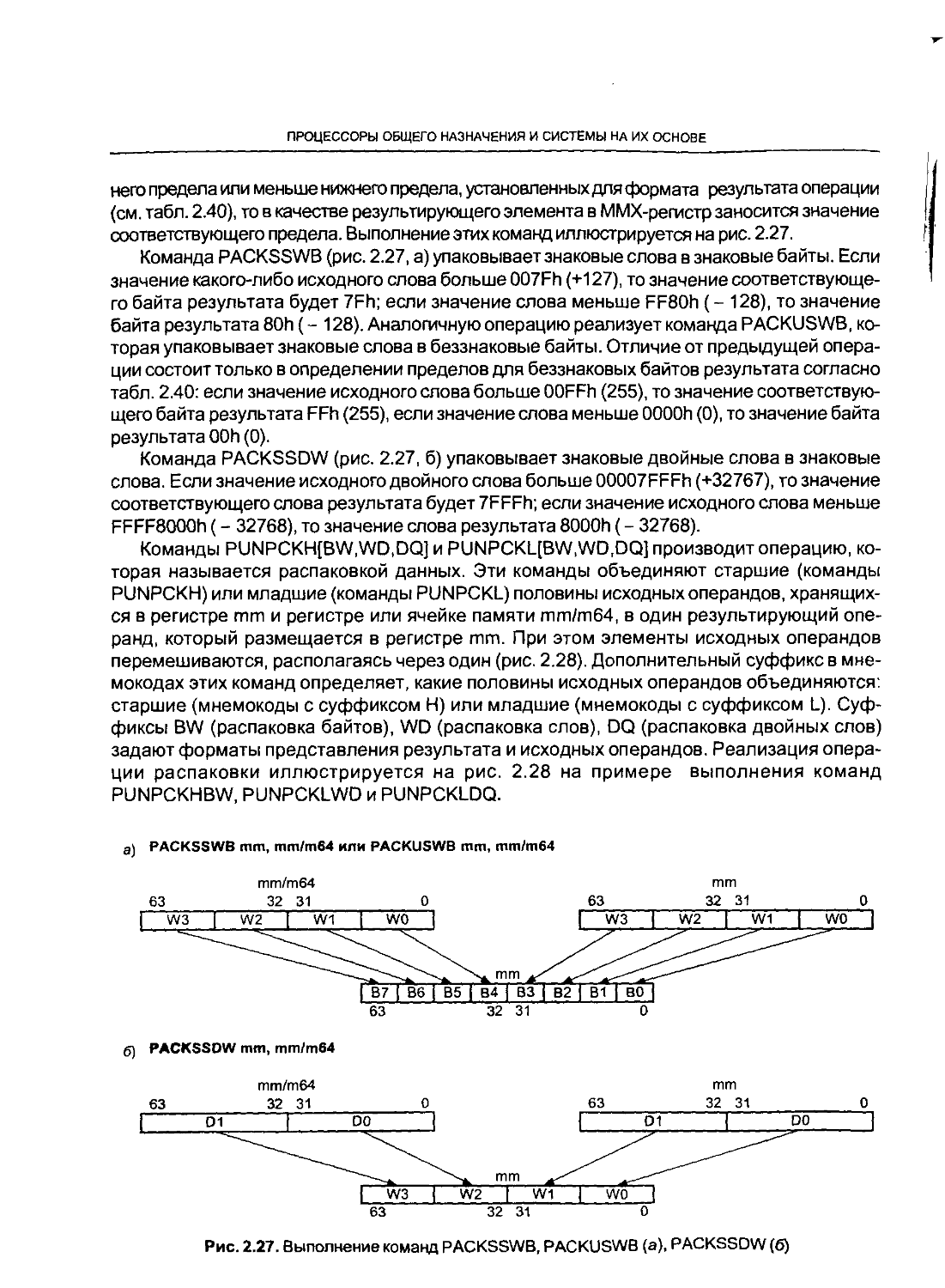

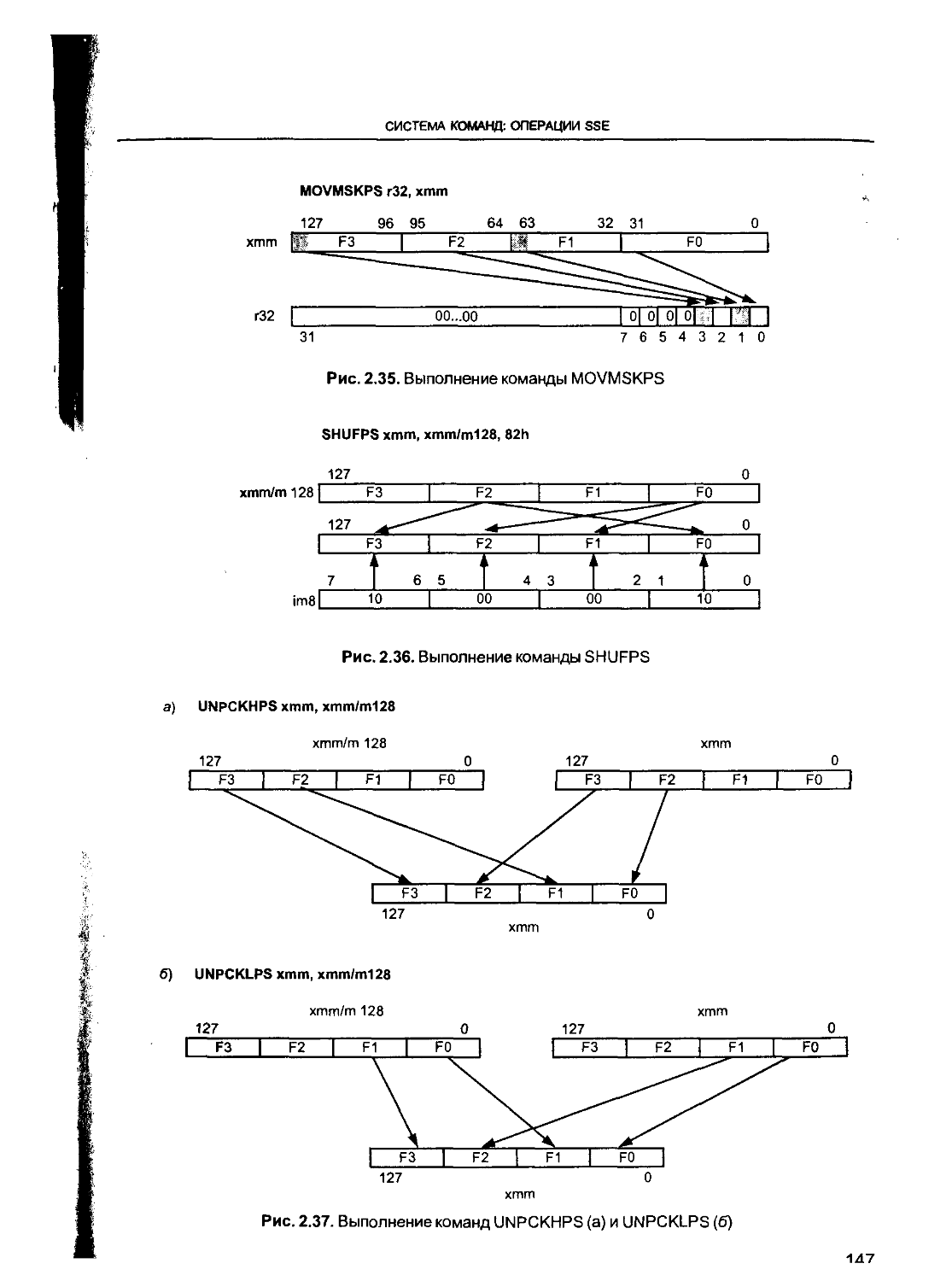

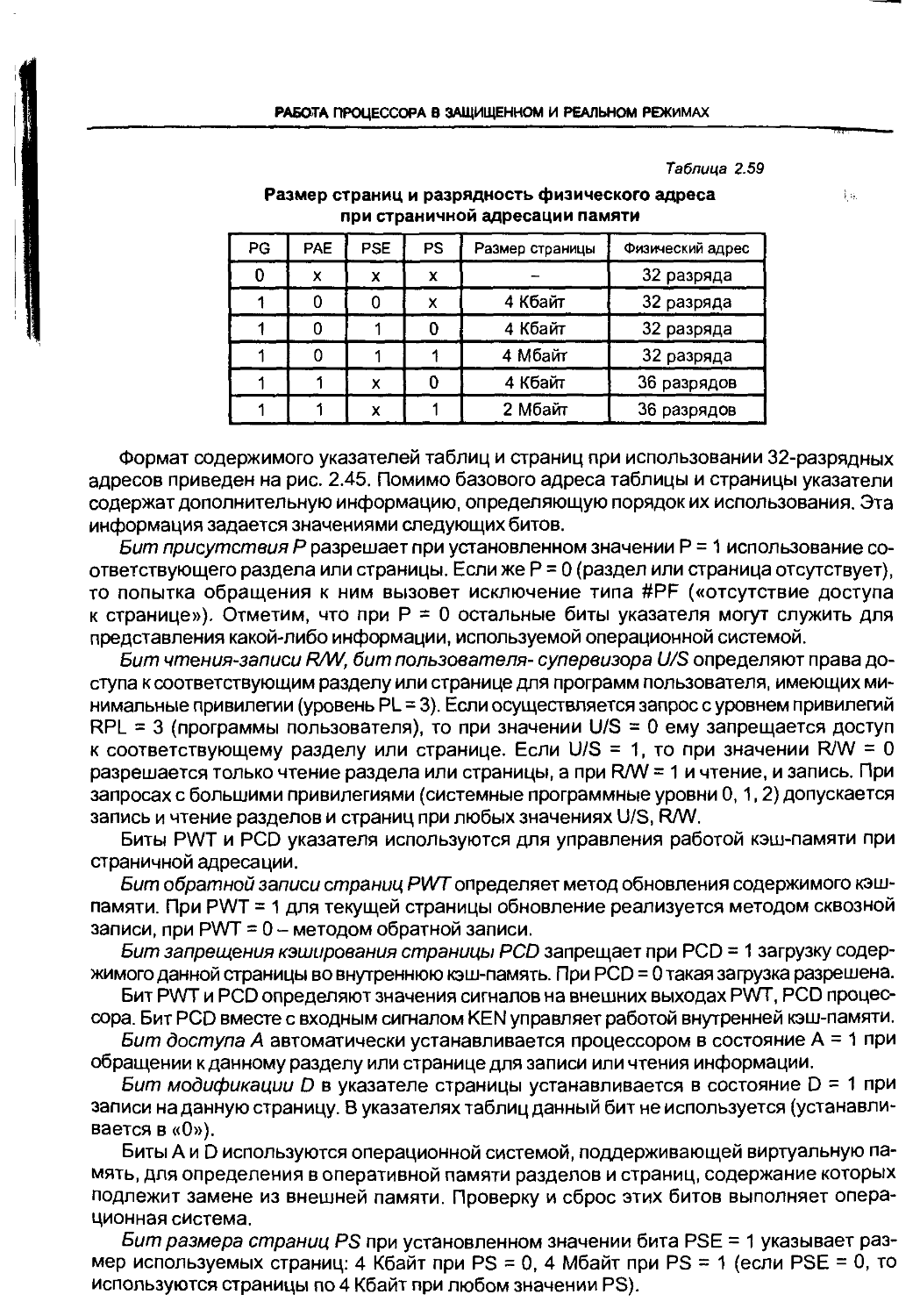

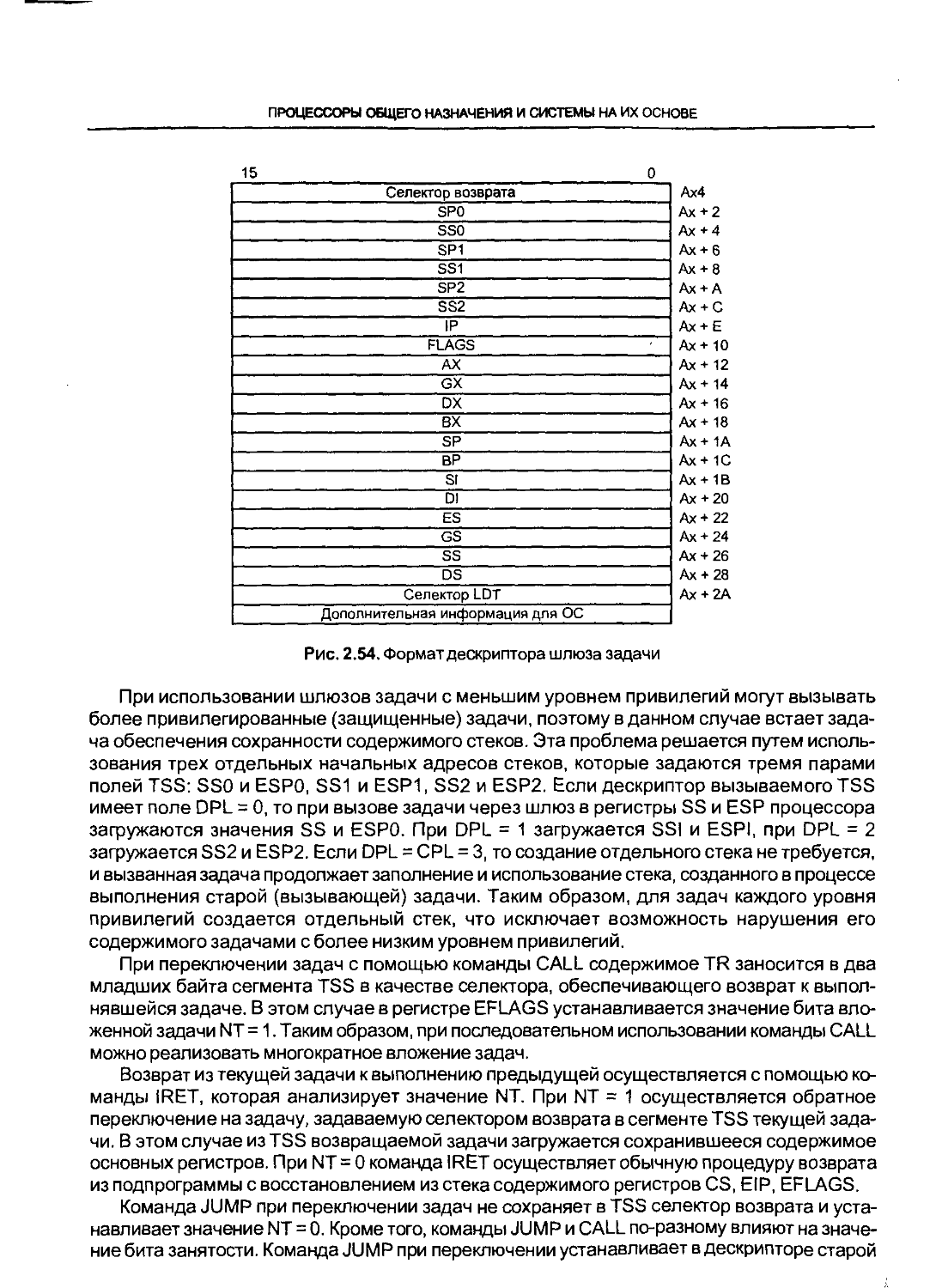

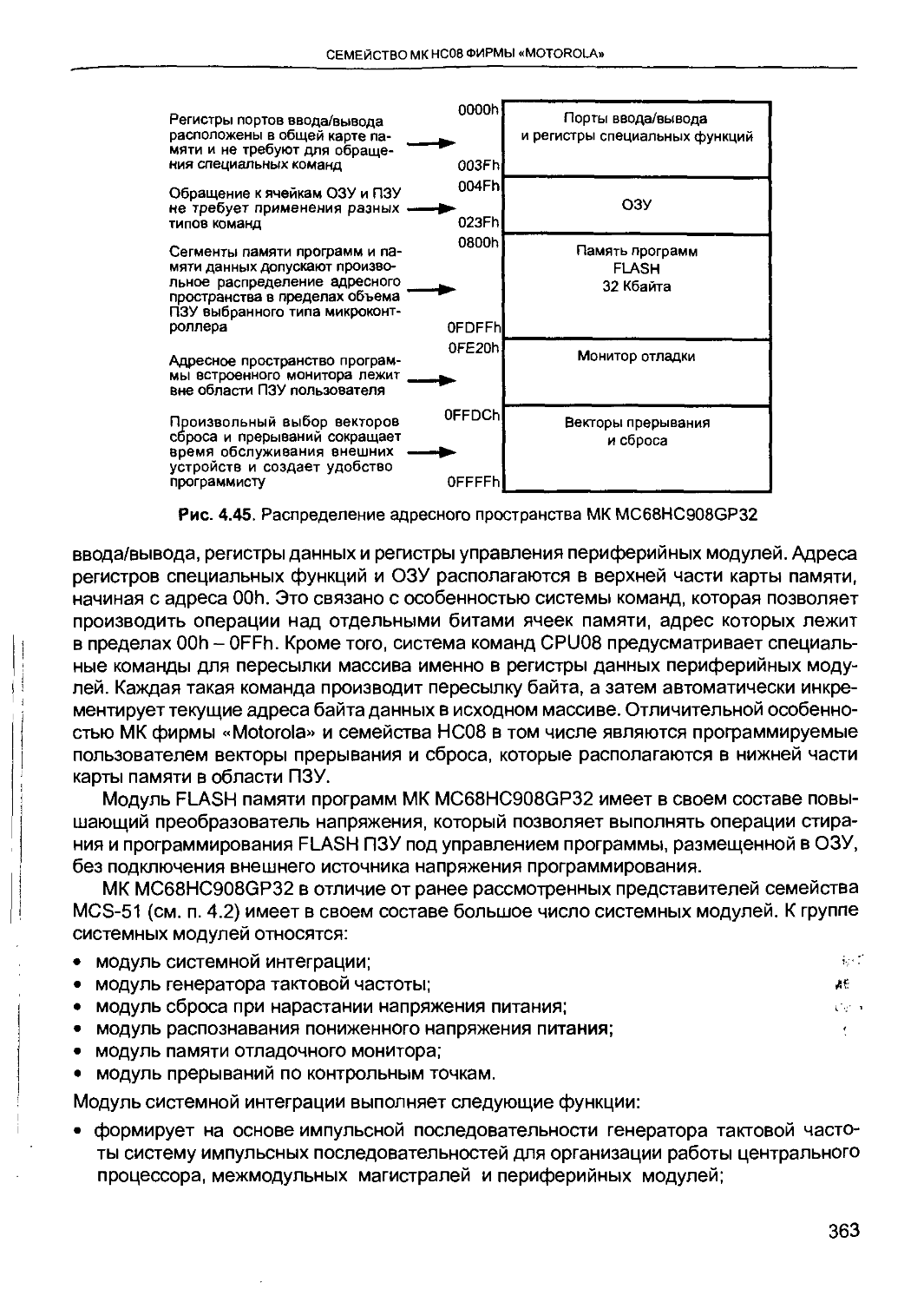

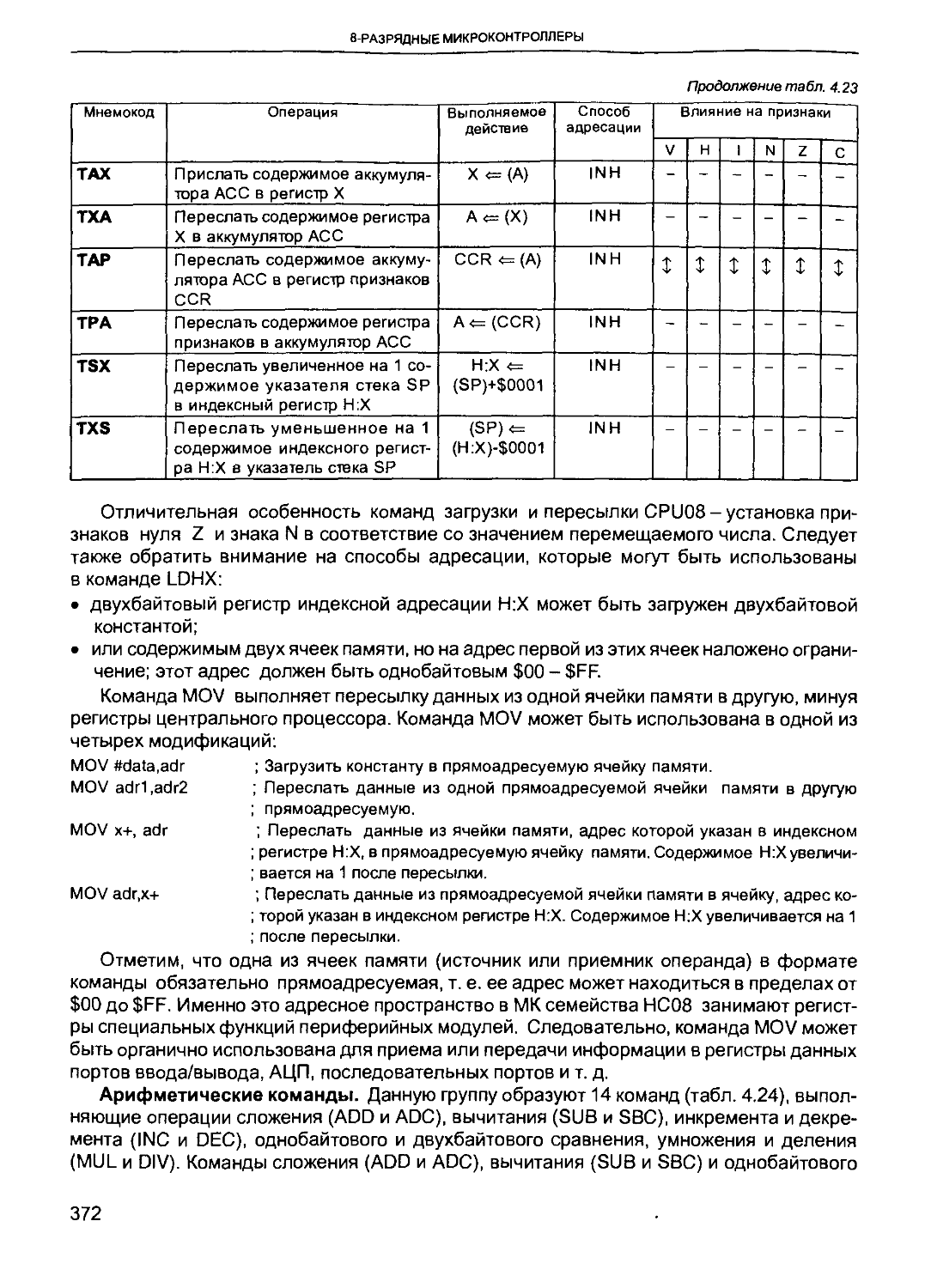

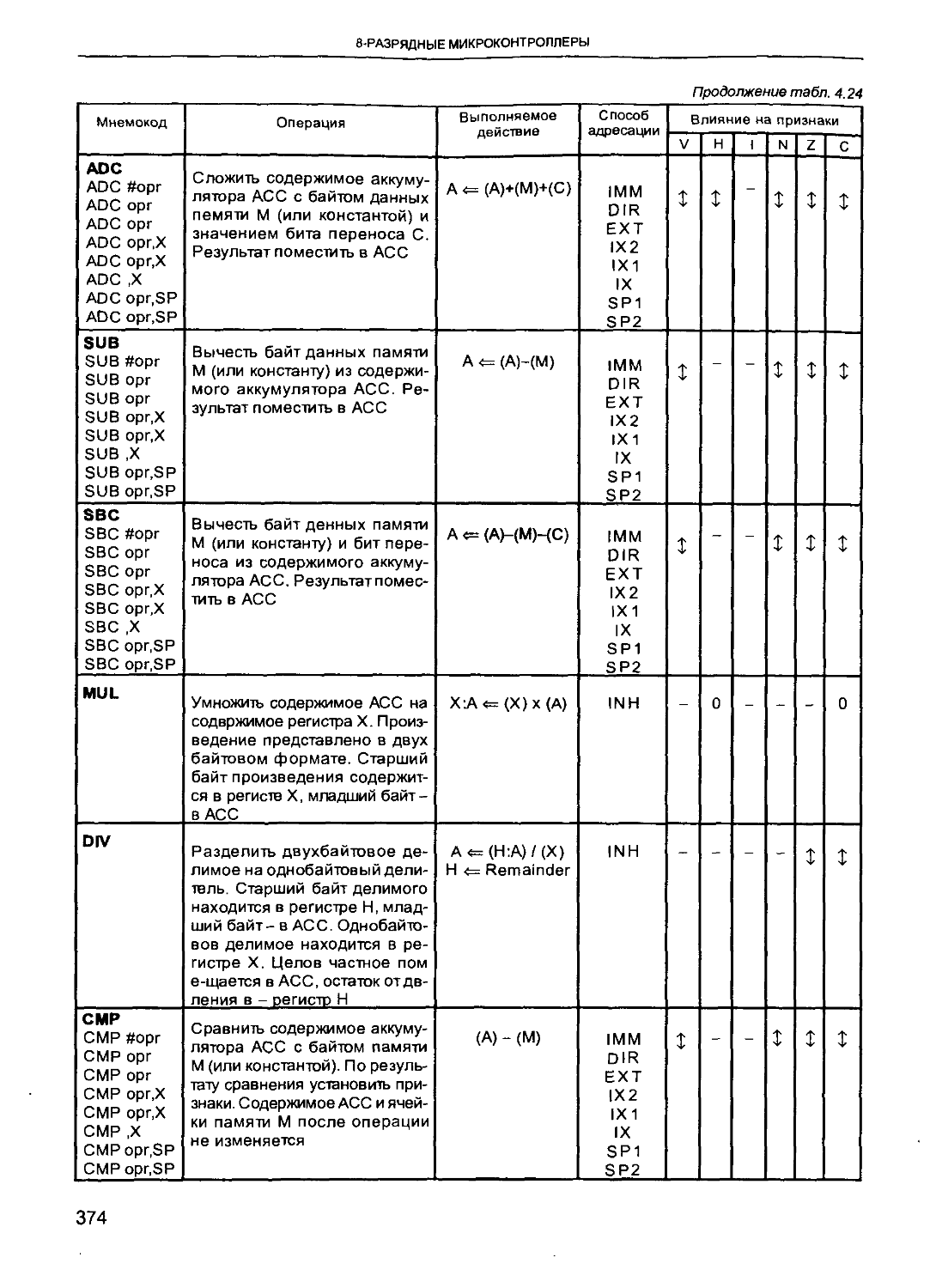

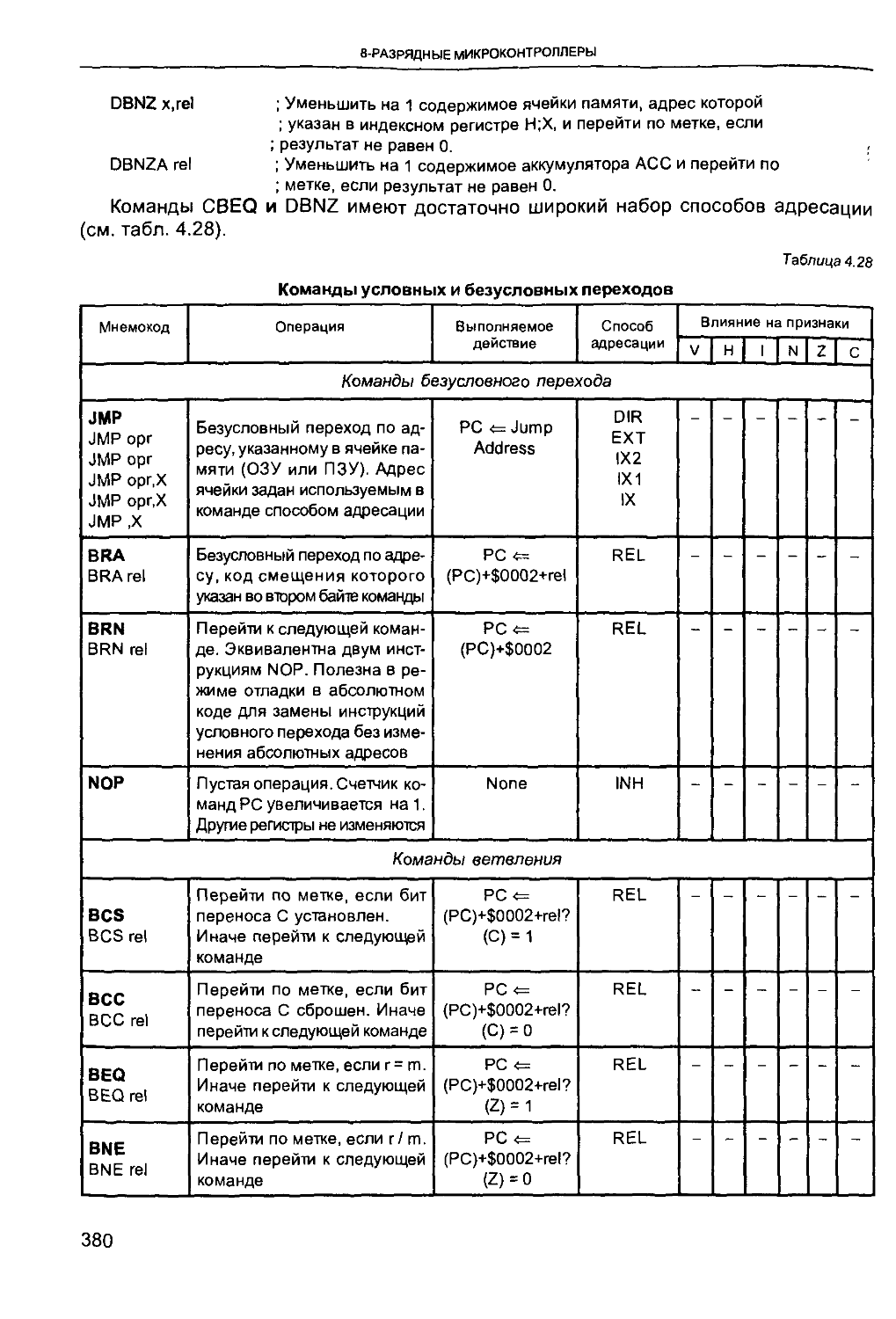

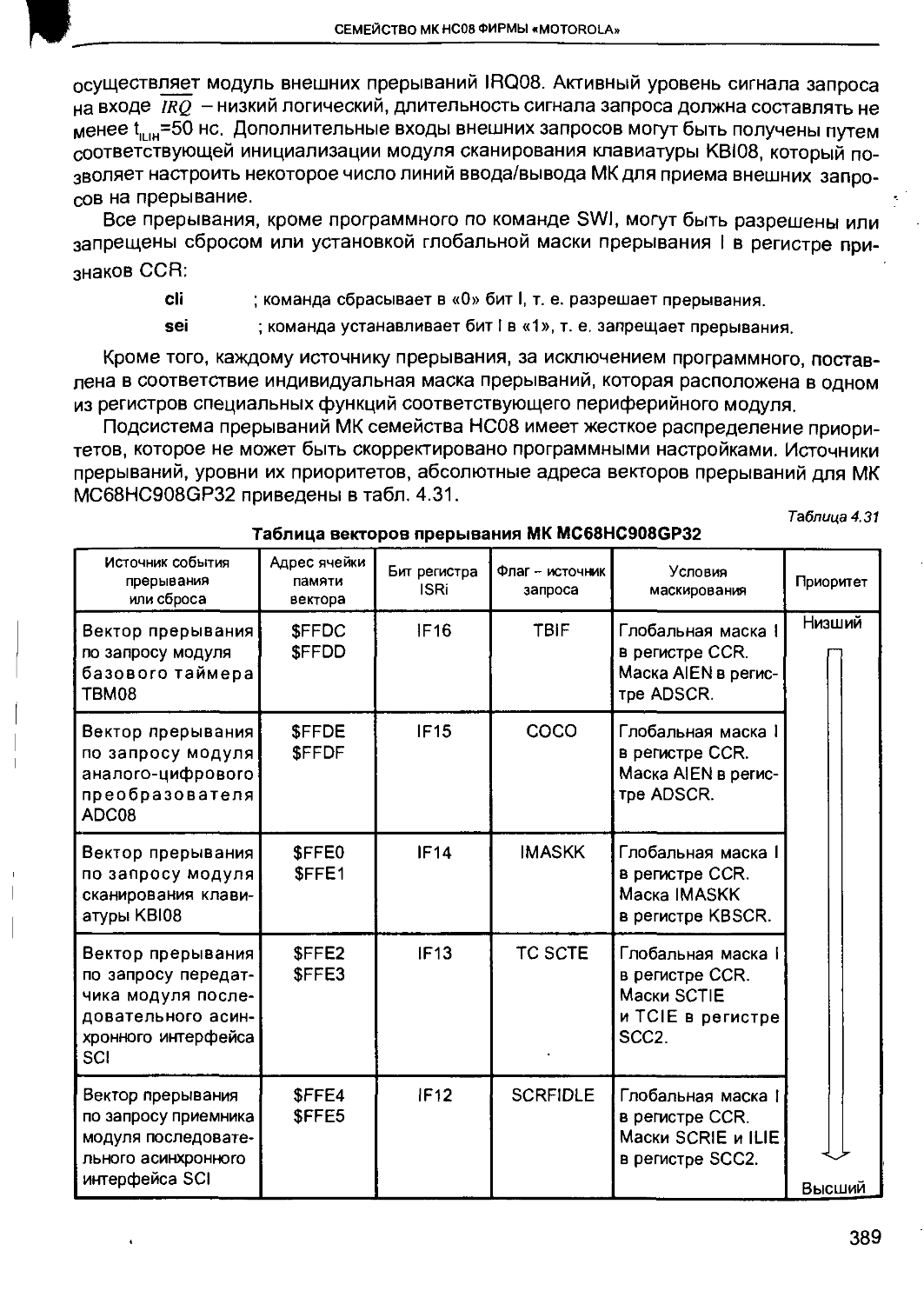

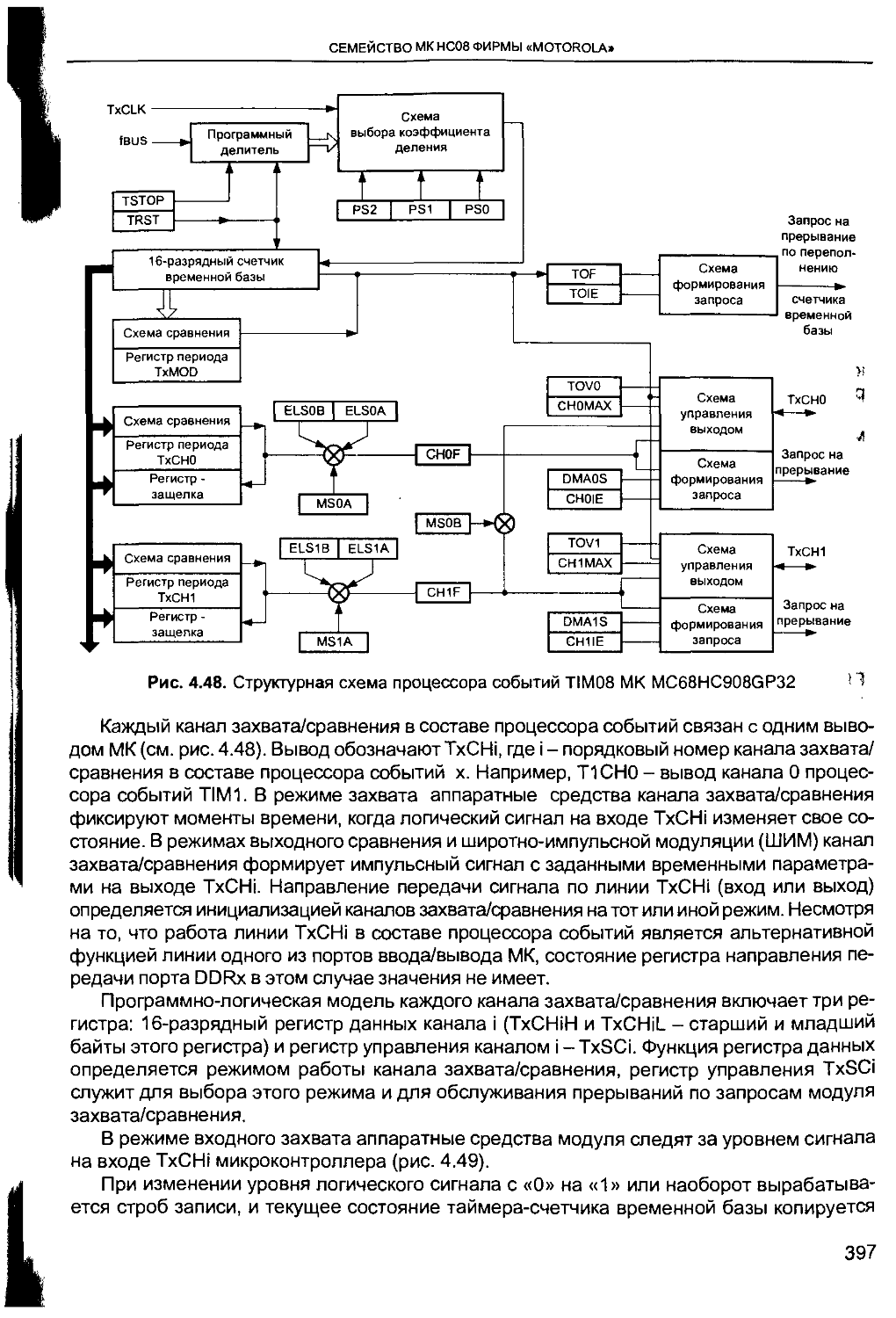

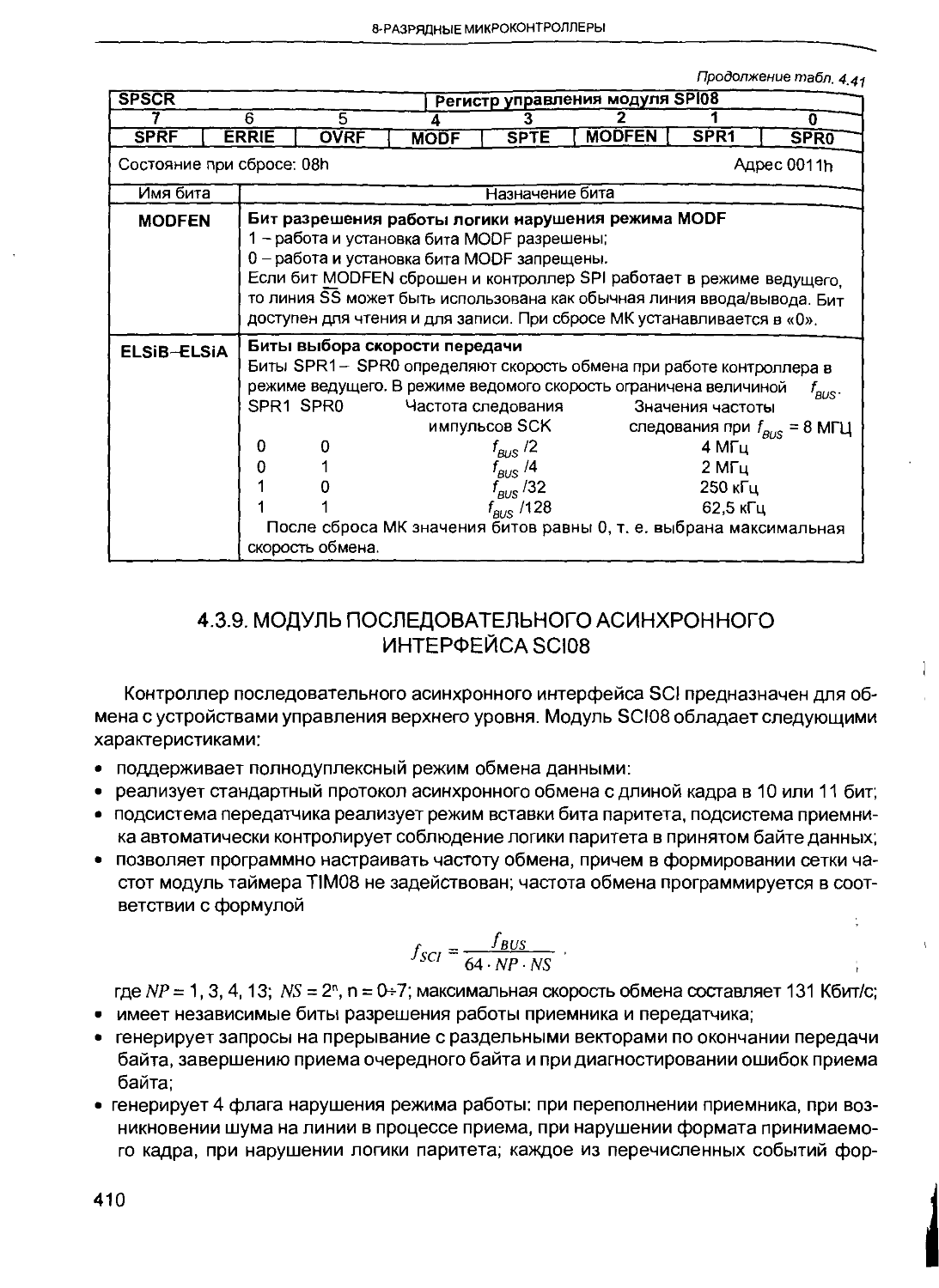

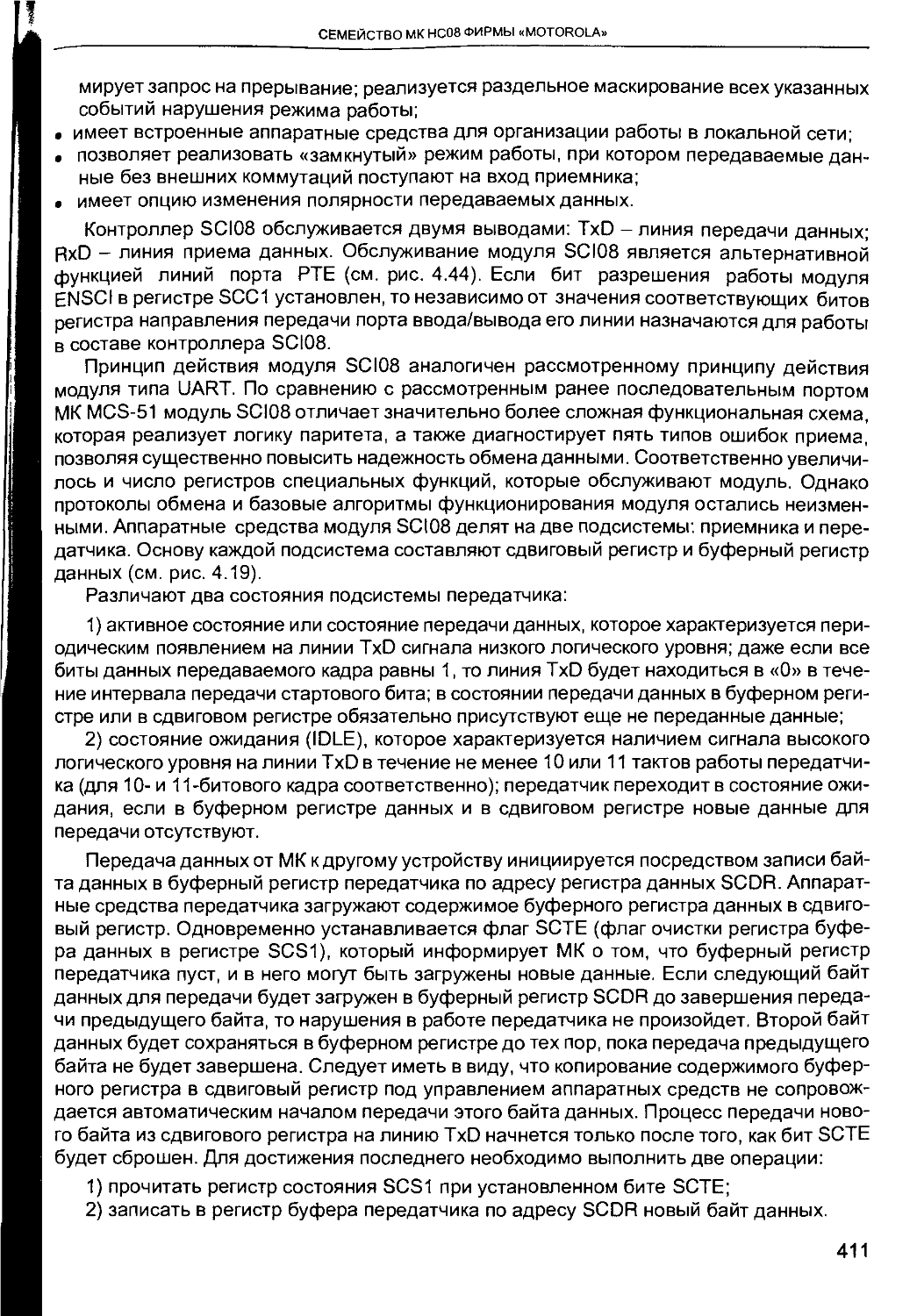

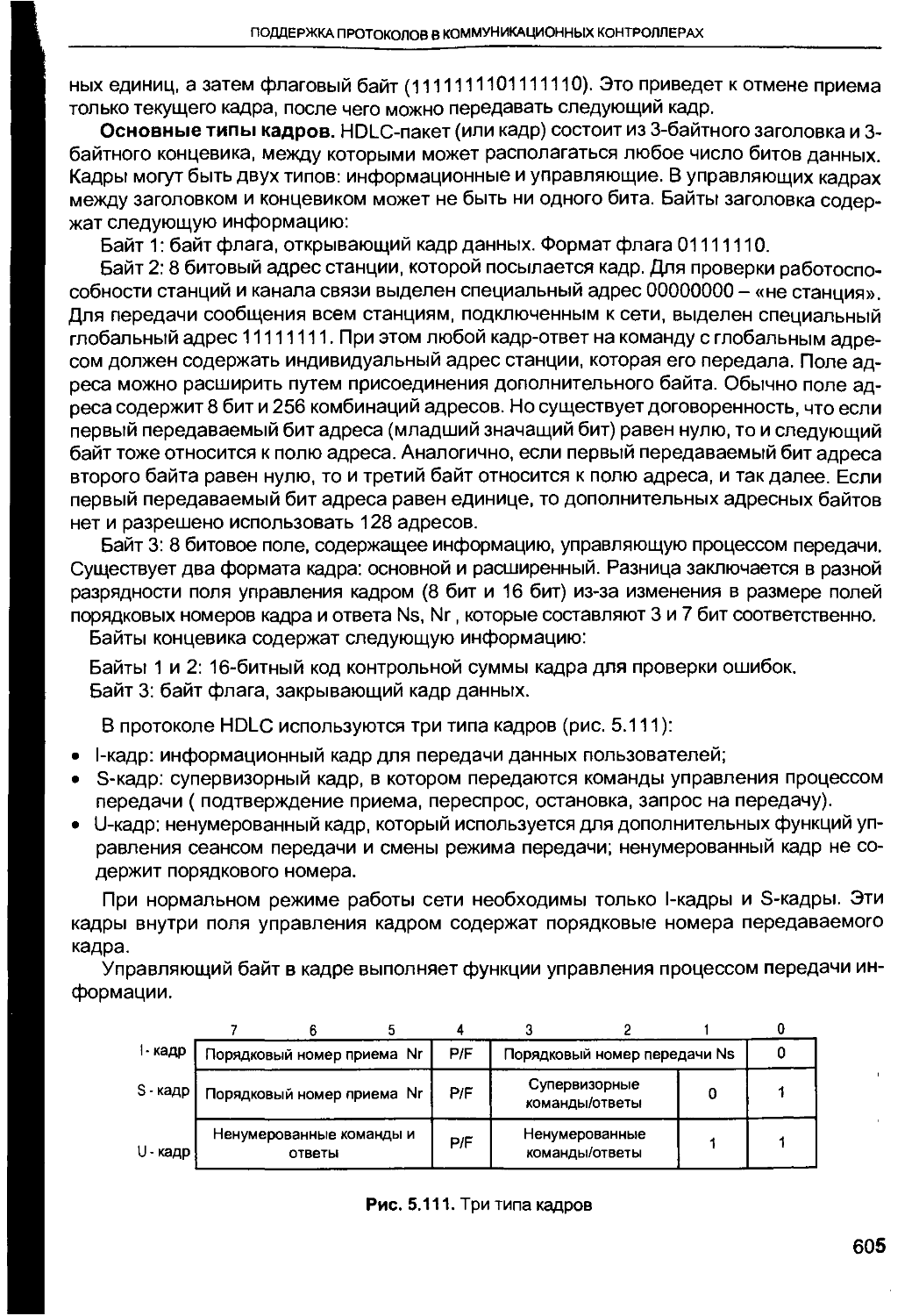

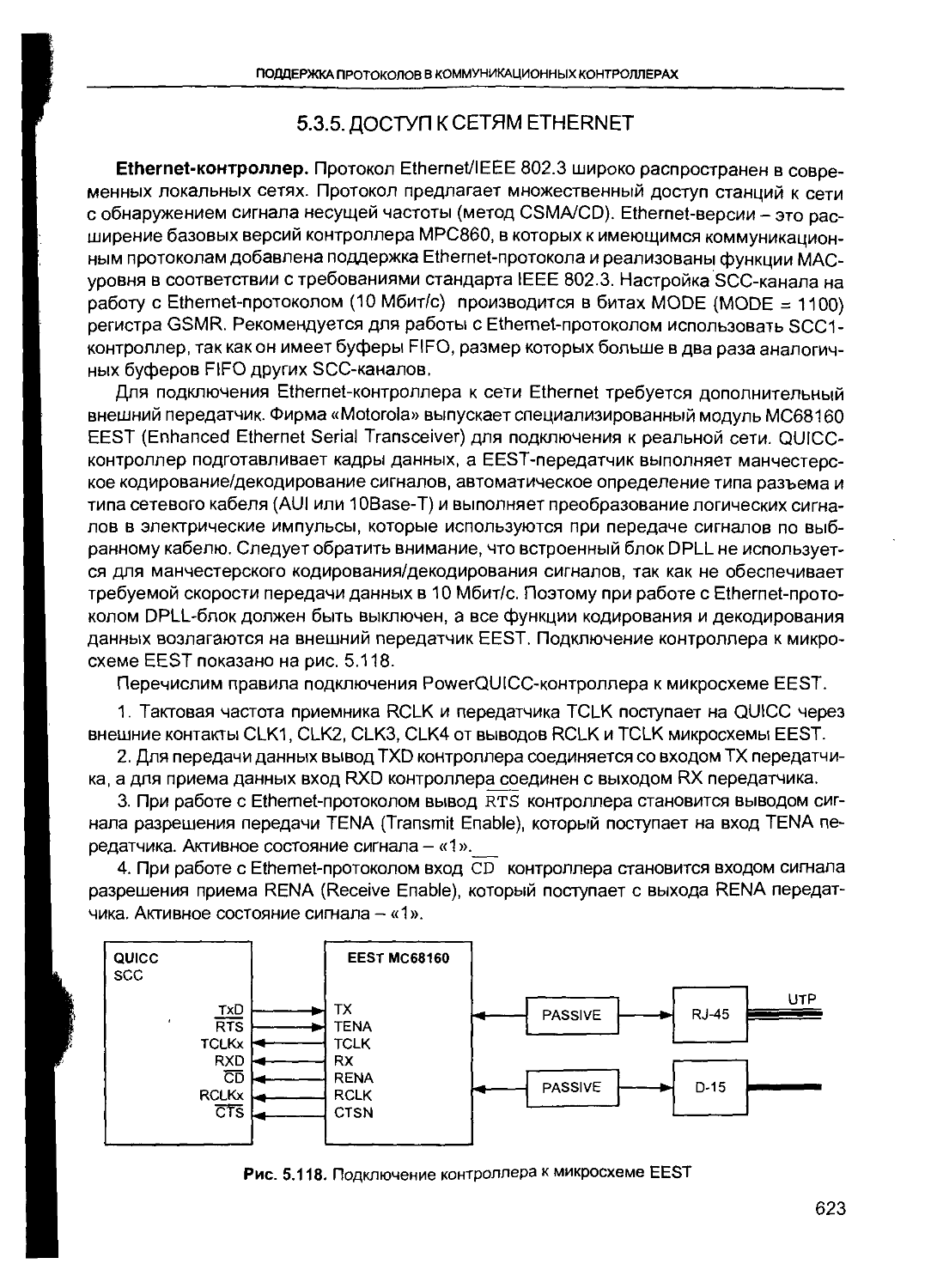

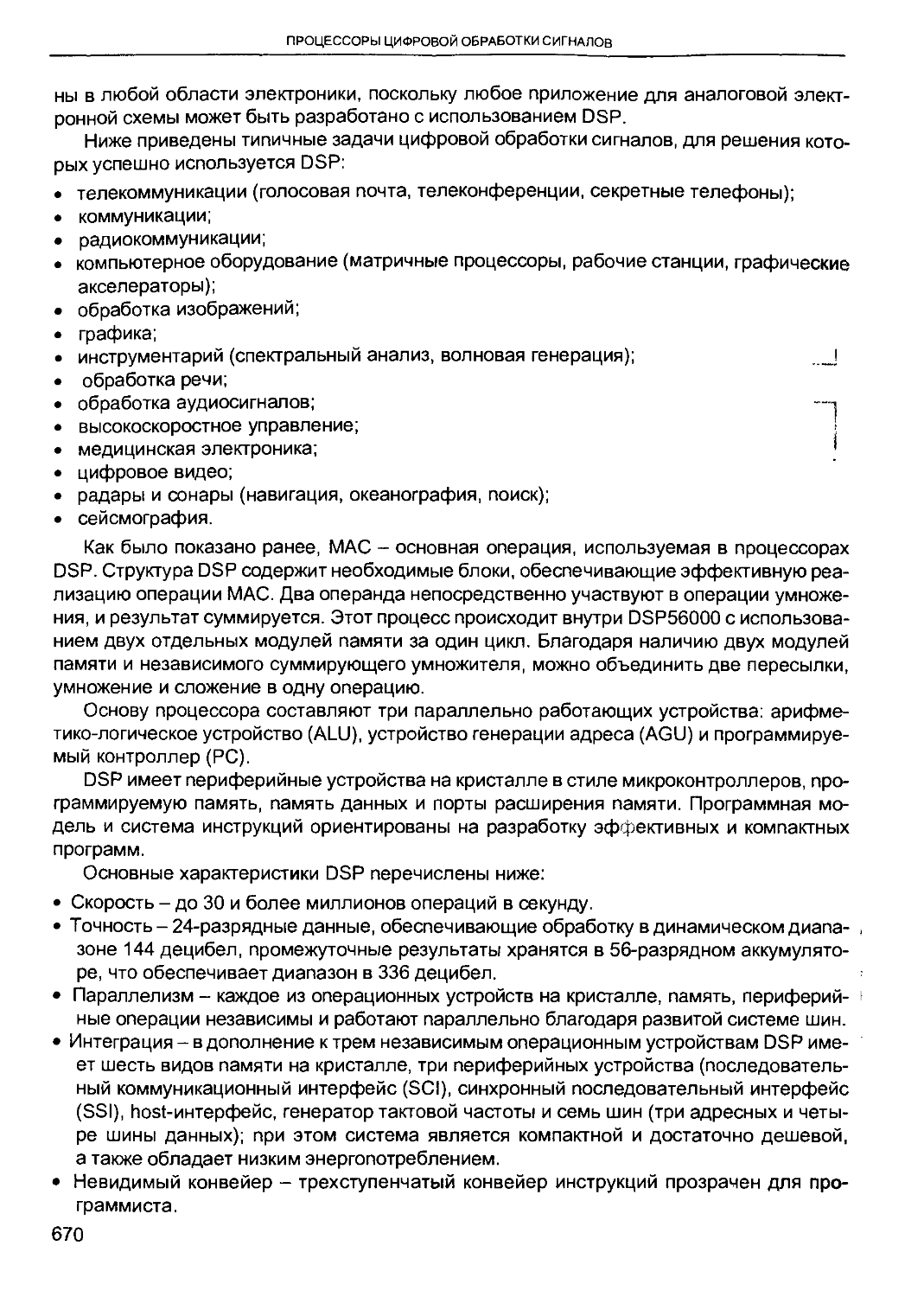

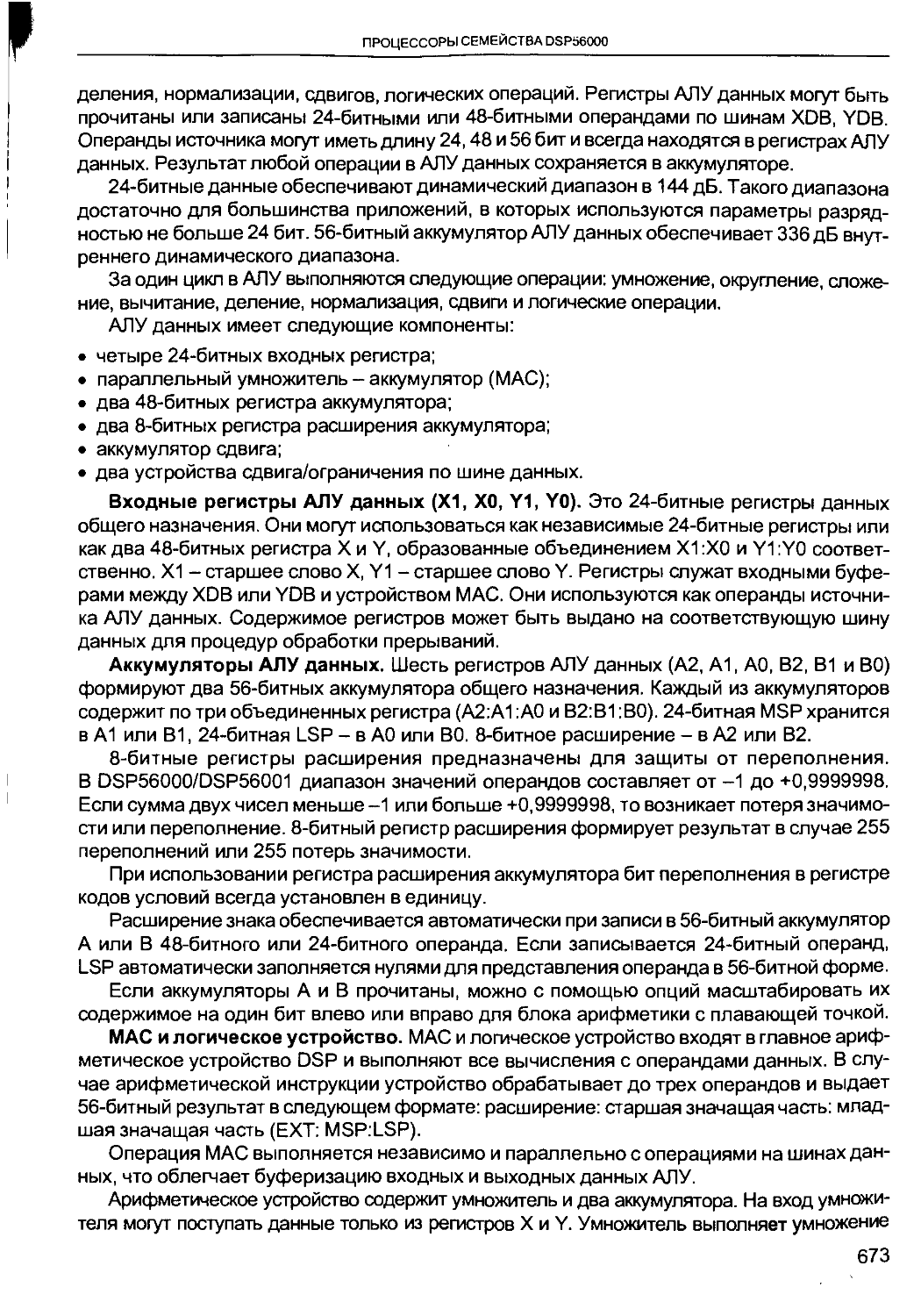

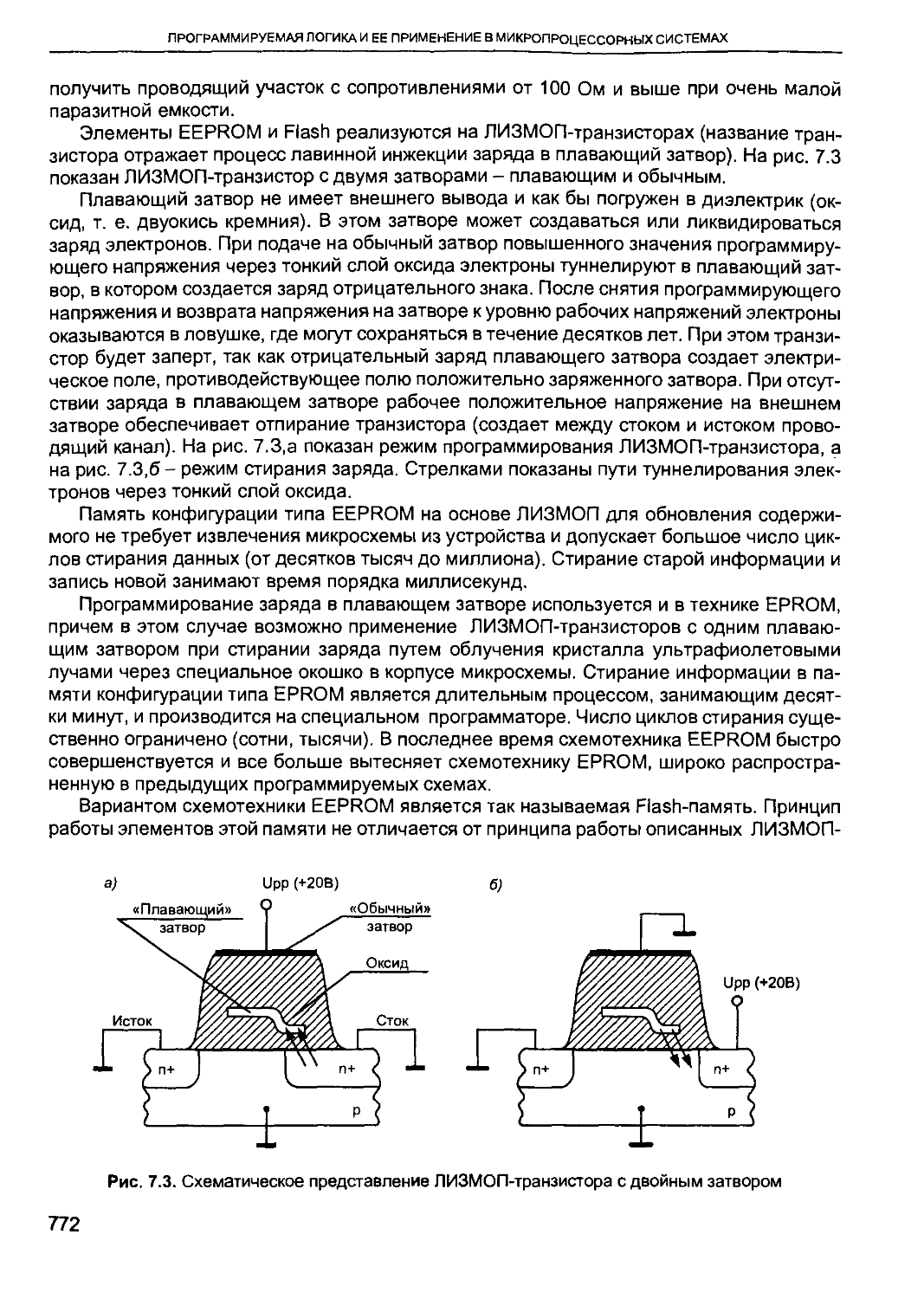

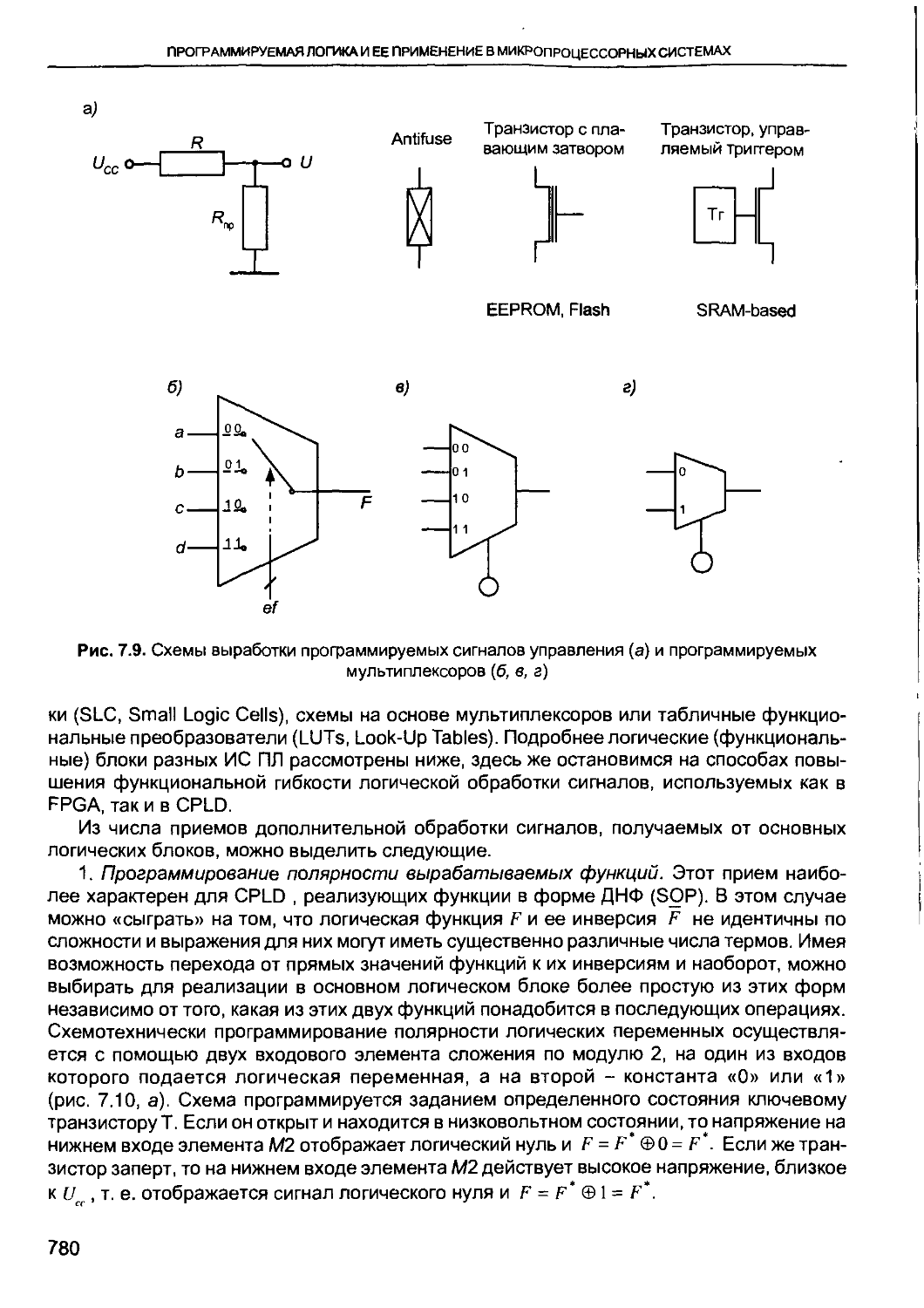

Рис. 1.7. Варианты реализации стека: регистровый стек (а) и стек, реализуемый в ОЗУ (б)