Author: Шпак Ю.А.

Tags: блоки обработки данных процессоры программирование язык программирования c

ISBN: 978-5-7931-0842-3

Year: 2011

Text

ИЗДАНИЕ

2 ИЗДАНИЕ

на языке

ЛД для AVRnPIC

I v-и микроконтроллеров

Программирование

на языке С для AVR и PIC

микроконтроллеров

Издание 2-е, переработанное и дополненное

Киев, “МК-Пресс”

СПб, “КОРОНА-ВЕК"

2011

ББК 32.973-04

Ш83

УДК 004.312

Ш83 Программирование на языке С для AVR и PIC микроконтролле-

ров. Изд. 2-е, переработанное и дополненное./ Сост. Ю.А. Шпак

— К.: “МК-Пресс”, СПб.: “КОРОНА-ВЕК”, 2011. —544 с., ил.

ISBN 978-5-7931-0842-3 (“КОРОНА-ВЕК”)

ISBN 978-966-8806-67-4 (“МК-Пресс”)

В книге рассмотрено программирование на языке С микроконтроллеров AVR

с использованием компиляторов WinAVR и CodeVisionAVR, а также микрокон-

троллеров PIC с использованием компиляторов CCS-PICC, mikroC и С30/32. Крат-

ко рассмотрена архитектура и аппаратное обеспечение как традиционных вось-

миразрядных микроконтроллеров AVR и PIC, так и новых семейств ATxmega,

PIC24 и PIC32. Дано описание средств программной разработки, включая эмуля-

цию программ с помощью AVR Studio и MPLAB. Кратко рассмотрен стандартный

синтаксис языка С и директивы препроцессора, а также особенности программи-

рования на этом языке для микроконтроллеров. Книга содержит программные

примеры на С, а также — справочник с описанием системы ассемблерных команд

микроконтроллеров AVR (включая ATxmega) и PIC (включая PIC24).

ББК 32.973-04

Программирование на языке С для

AVR и PIC микроконтроллеров

Издание 2-е, переработанное и дополненное

Подписано в печать 06.08.2010. Формат 70 х 100 1/16.

Бумага газетная. Печать офсетная. Усл. печ. л. 44,1. Уч.-изд. л. 28,6.

Тираж 1000 экз. Заказ 350

СПД Савченко Л.А., Украина, г.Киев, тел./ф.: (044) 362-04-38; e-mail: info@mk-press.com.

Свидетельство о внесении субъекта издательского дела в Государственный реестр издателей,

производителей и распространителей издательской продукции: серия ДК №51582 от 28.11.2003г.

ISBN 978-5-7931-0842-3 (“КОРОНА-ВЕК”)

ISBN 978-966-8806-67-4 (“МК-Пресс”)

©“МК-Пресс”, 2011

Краткое оглавление

3

Краткое оглавление

Часть I. Архитектура микроконтроллеров AVR.......................15

Глава 1. Восьмиразрядные микроконтроллеры AVR....................16

Глава 2. Семейство AVR ATxmega...................................97

Часть II. Компиляторы и средства разработки для

МИКРОКОНТРОЛЛЕРОВ AVR.......................................... 140

Глава 3. Компилятор WinAVR.................................... 141

Глава 4. Среда разработки AVR Studio............................146

Глава 5. Среда разработки CodeVisionAVR.........................158

Глава 6. Программаторы для микроконтроллеров AVR................175

Часть III. Архитектура микроконтроллеров PIC....................184

Глава 7. Восьмиразрядные микроконтроллеры PIC...................185

Глава 8. Семейство PIC18F.......................................219

Глава 9. Семейство PIC24........................................231

Глава 10. Семейство PIC32.......................................248

Часть IV. Компиляторы и средства разработки для

микроконтроллеров PIC...........................................260

Глава 11. Компилятор CCS-PICC................................. 261

Глава 12. Эмуляция и отладка программ в среде MPLAB.............275

Глава 13. Компилятор mikroC.....................................282

Глава 14. Компиляторы СЗО и С32.................................294

Глава 15. Программаторы для микроконтроллеров PIC...............297

ЧАСТЬ V. ЯЗЫК С И ДИРЕКТИВЫ ПРЕПРОЦЕССОРА.......................302

Глава 16. Основы языка С........................................303

Глава 17. Функции и макросы языка С для различных компиляторов..361

Часть VI. Программные примеры для микроконтроллеров AVR............412

Глава 18. Примеры для компилятора WinAVR...........................413

Глава 19. Примеры для компилятора CodeVisionAVR....................430

Часть VII. Программные примеры для микроконтроллеров PIC...........435

Глава 20. Примеры для компилятора CCS-PICC......................436

Глава 21. Примеры для компилятора mikroC...........................446

Глава 22. Примеры для компилятора СЗО..............................453

Глава 23. Примеры для компилятора С32...........................470

Часть VIII. Приложения.............................................477

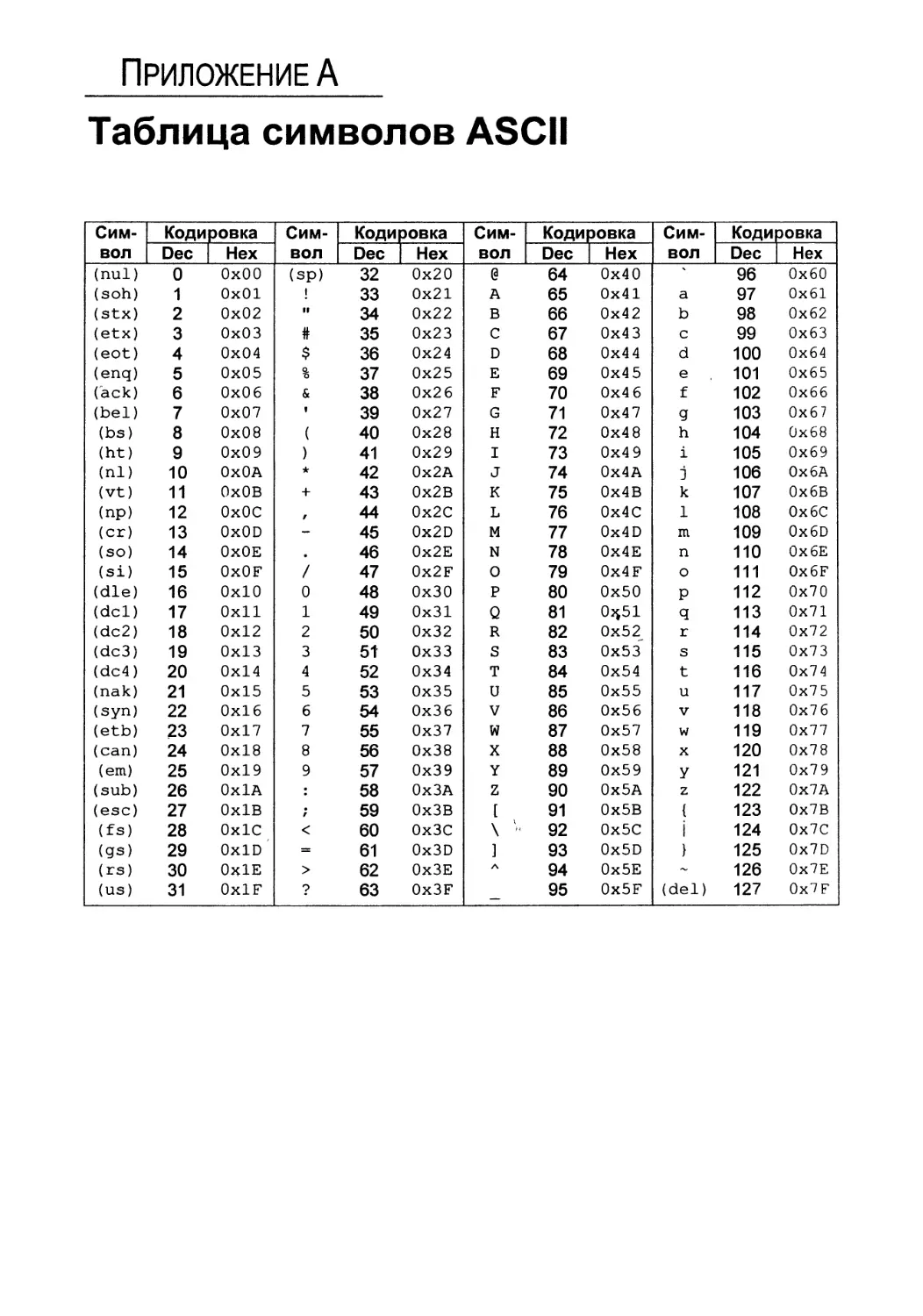

Приложение А. Таблица символов ASCII...............................478

Приложение Б. Преобразование из одной системы счисления в другую...479

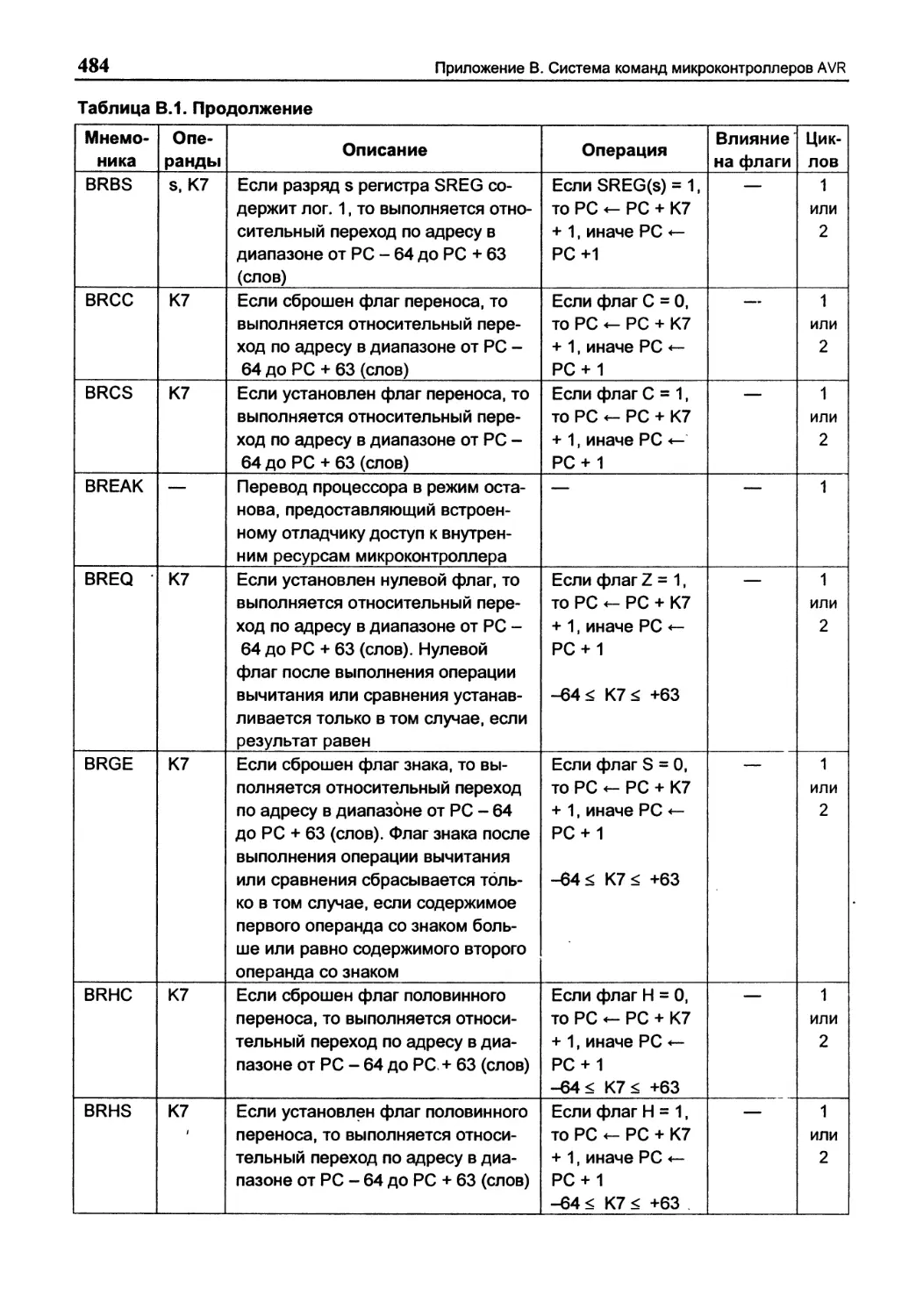

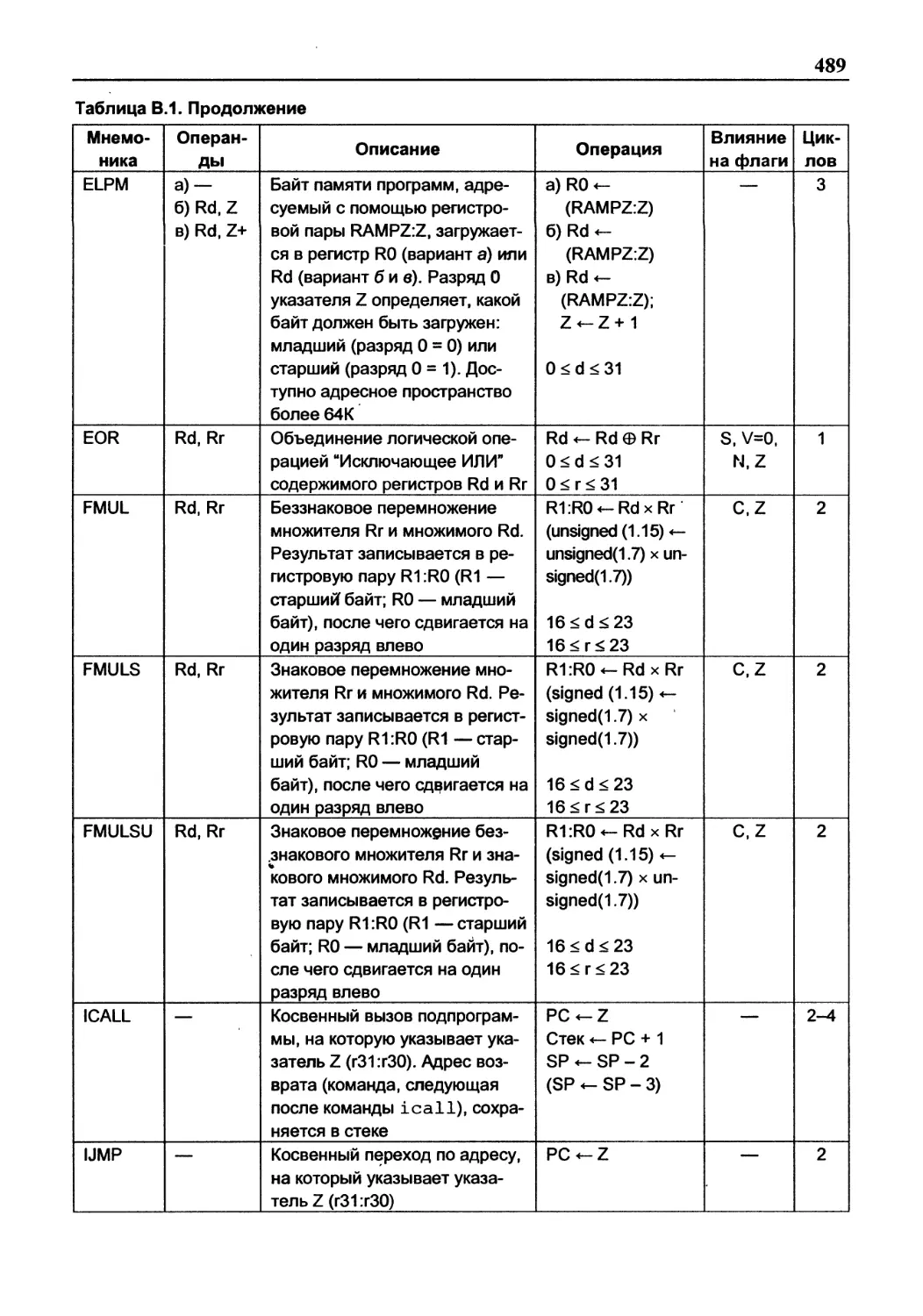

Приложение В. Система команд микроконтроллеров AVR.................482

Приложение Г. Система команд микроконтроллеров PIC.................498

Приложение Д. Область ввода/вывода микроконтроллеров AVR ATxmega А.519

4

Содержание

Предисловие ко 2чиу изданию.........................13

Введение............................................14

ЧАСТЬ I. АРХИТЕКТУРА МИКРОКОНТРОЛЛЕРОВ AVR 15

Глава 1. Восьмиразрядные микроконтроллеры AVR.......................16

Семейства восьмиразрядных микроконтроллеров AVR..................18

Отладочная плата.................................................19

Платы STK500 и STK600......................................... 19

Схема базового монтажа...........................................21

Структура микроконтроллеров AVR..................................22

Организация памяти.............................................22

Память SRAM.................................................23

Память программ.............................................33

Память данных типа EEPROM.................................. 34

Порты..........................................................36

Подтягивающее сопротивление.................................37

Регистры управления портом..................................39

Таймеры/счетчики...............................................39

T/C0........................................................40

T/C1........................................................41

T/C2....'...................................................47

Сторожевой таймер..............................................48

Обработка прерываний...........................................49

Управление прерываниями.....................................52

Сброс..........................................................54

“Спящие”режимы процессора......................................55

Последовательный ввод/вывод....................................56

Приемопередатчик UART.......................................57

Приемопередатчик USART......................................60

Синхронная передача данных по интерфейсу SPI................65

Работа приемопередатчика USART в режиме SPI.................69

Синхронная передача данных по интерфейсу I2C (TWI)..........70

Универсальный последовательный интерфейс US1................75

Модули последовательного ввода/вывода в семействах AT90S, ATtiny

и ATmega....................................................79

Аналого-цифровое преобразование................................80

Встроенный аналоговый компаратор...............................86

Программирование памяти..........................................87

Разряды предохранения..........................................89

Параллельное программирование................................ 89

Переход в режим параллельного программирования..............91

Очистка кристалла...........................................91

Программирование и чтение памяти программ...................92

Программирование разрядов блокировки и предохранения........93

Последовательное программирование..............................93

Технология picoPower.............................................96

Содержание

5

Глава 2. Семейство AVR ATxmega....................................97

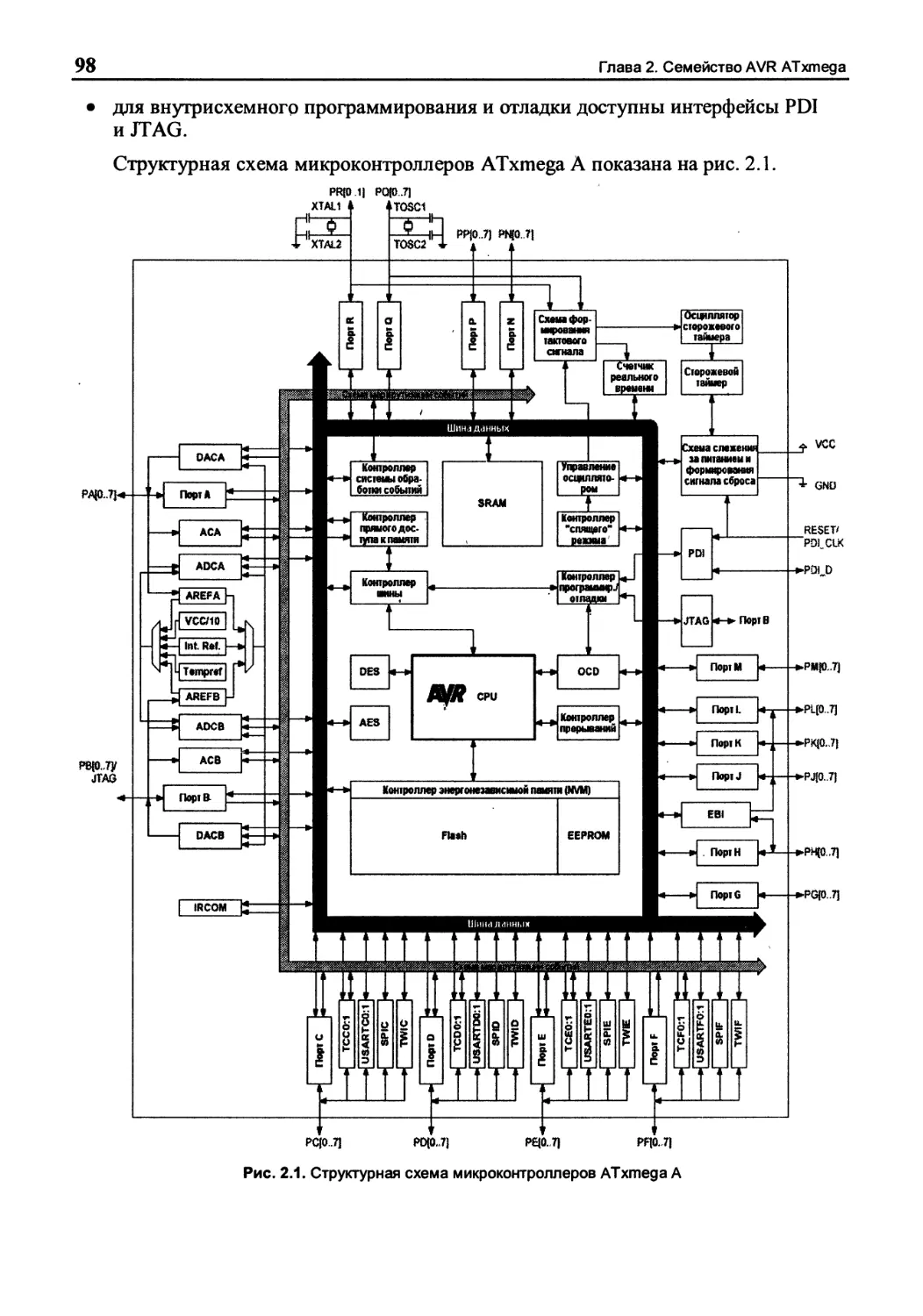

Обзор возможностей микроконтроллеров ATxmega а..................97

Организация памяти семейства ATxmega............................99

Область ввода/вывода семейства ATxmega......................100

Арбитраж шины данных........................................100

Память программ,............................................101

Контроллер прямого доступа к памяти............................102

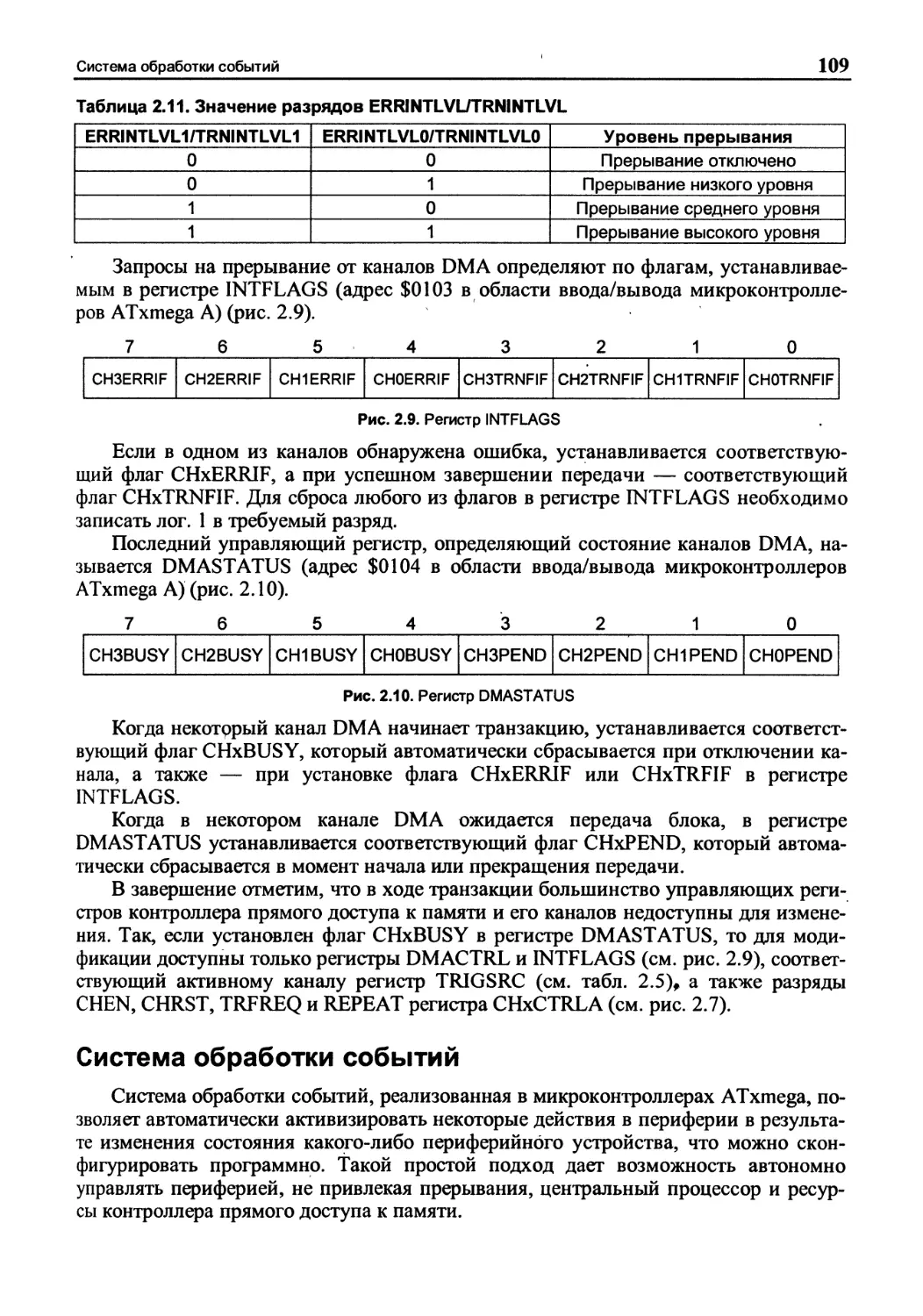

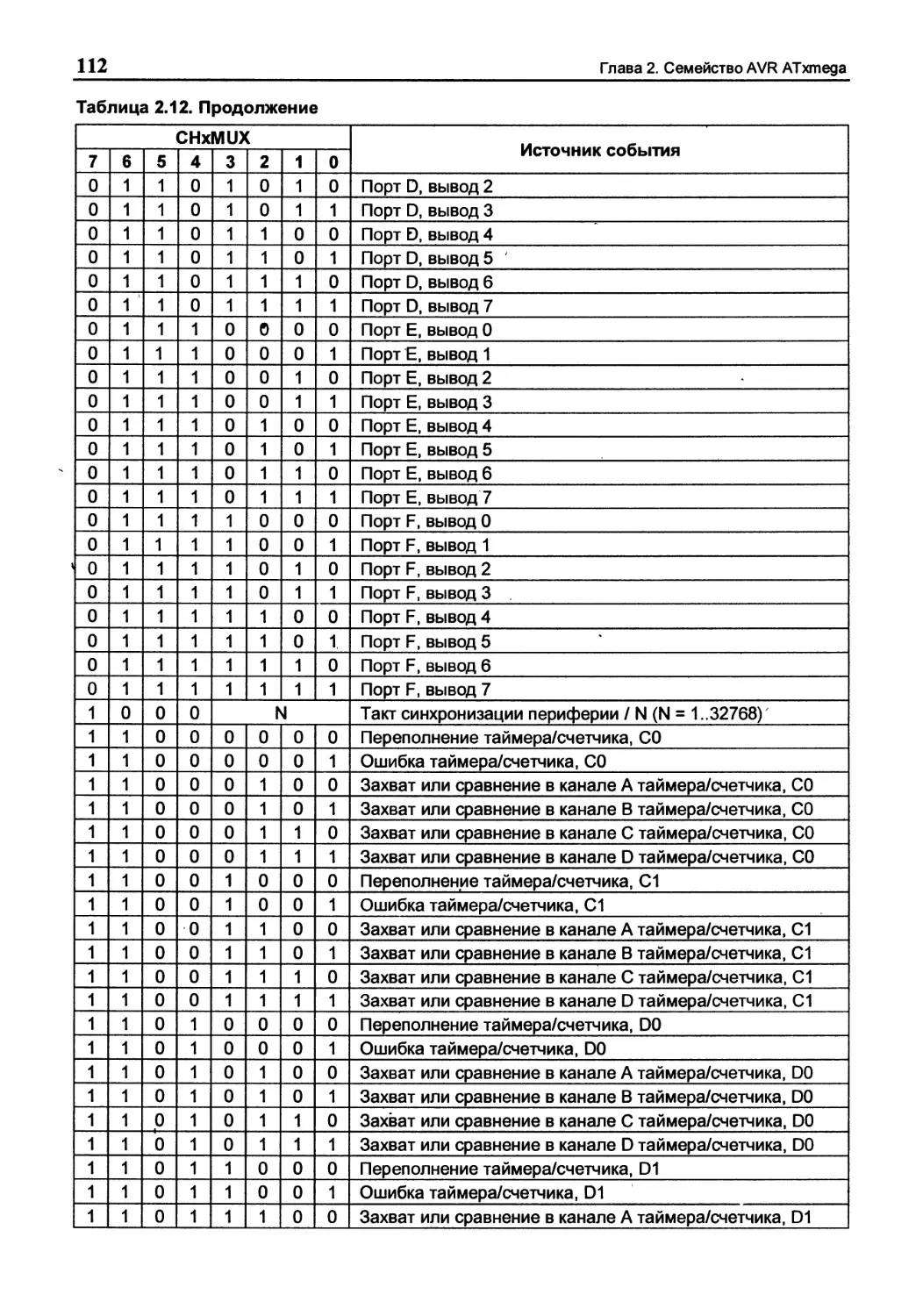

Система обработки событий......................................109

Генерирование событий вручную...............................114

Фильтрация..................................................114

Квадратурный дешифратор.....................................115

Система синхронизации..........................................117

Выбор источника тактового сигнала системной синхронизации...120

Счетчики реального времени.....................................122

Счетчик RTC............................................... 123

Счетчик RTC32...............................................123

Модуль питания от батареи......................................123

Обработка прерываний...........................................124

Немаскируемые прерывания....................................125

Регистр управления контроллером прерываний..................125

Аналого-цифровое преобразование................................126

Конфигурирование АЦП........................................127

Выбор разрешения преобразования...........................127

Выбор очередности преобразований в каналах................127

Выбор режима измерения....................................127

Выбор опорного напряжения.................................129

Выбор коэффициента деления частоты тактирования...........130

Результаты измерения........................................130

Прерывание от АЦП...........................................130

ЦИФРО-АНАЛОГОВОЕ ПРЕОБРАЗОВАНИЕ............................... 131

Начало преобразования.......................................132

Ограничения на время преобразования.........................133

АНАЛОГОВЫЙ КОМПАРАТОР......................................... 134

Режимы работы компаратора...................................135

Средства шифрования............................................136

Модуль шифрования AES.......................................137

Модуль обмена данными по инфракрасному каналу..................138

ЧАСТЬ II. КОМПИЛЯТОРЫ И СРЕДСТВА РАЗРАБОТКИ ДЛЯ

МИКРОКОНТРОЛЛЕРОВ AVR 140

Глава 3. Компилятор WinAVR................................141

Глава 4. Среда разработки AVR Studio......................146

Эмуляция................................................148

Окно Memory.............................................151

Окно Register............................................152

Окно Watch..............................................152

Отладка программы.......................................152

6

НАСТРОЙКА ПАРАМЕТРОВ ИМИТАТОРА...........................153

Создание проекта и компиляция программы..................153

Компиляция проекта.....................................156

Глава 5. Среда разработки CodeVisionAVR....................158

КОМПИЛЯЦИЯ И ПОСТРОЕНИЕ ПРОЕКТА..........................159

Создание проекта с помощью мастера CodeWizardAVR.........164

Сохранение и открытие проекта CodeWizardAVR............171

Создание новых файлов с исходным кодом...................172

Отладка программы........................................173

Использование терминала................................174

Глава 6. Программаторы для микроконтроллеров AVR...........175

Программные средства для программирования микроконтроллеров.179

Программирование устройства в среде A VR Studio 4......179

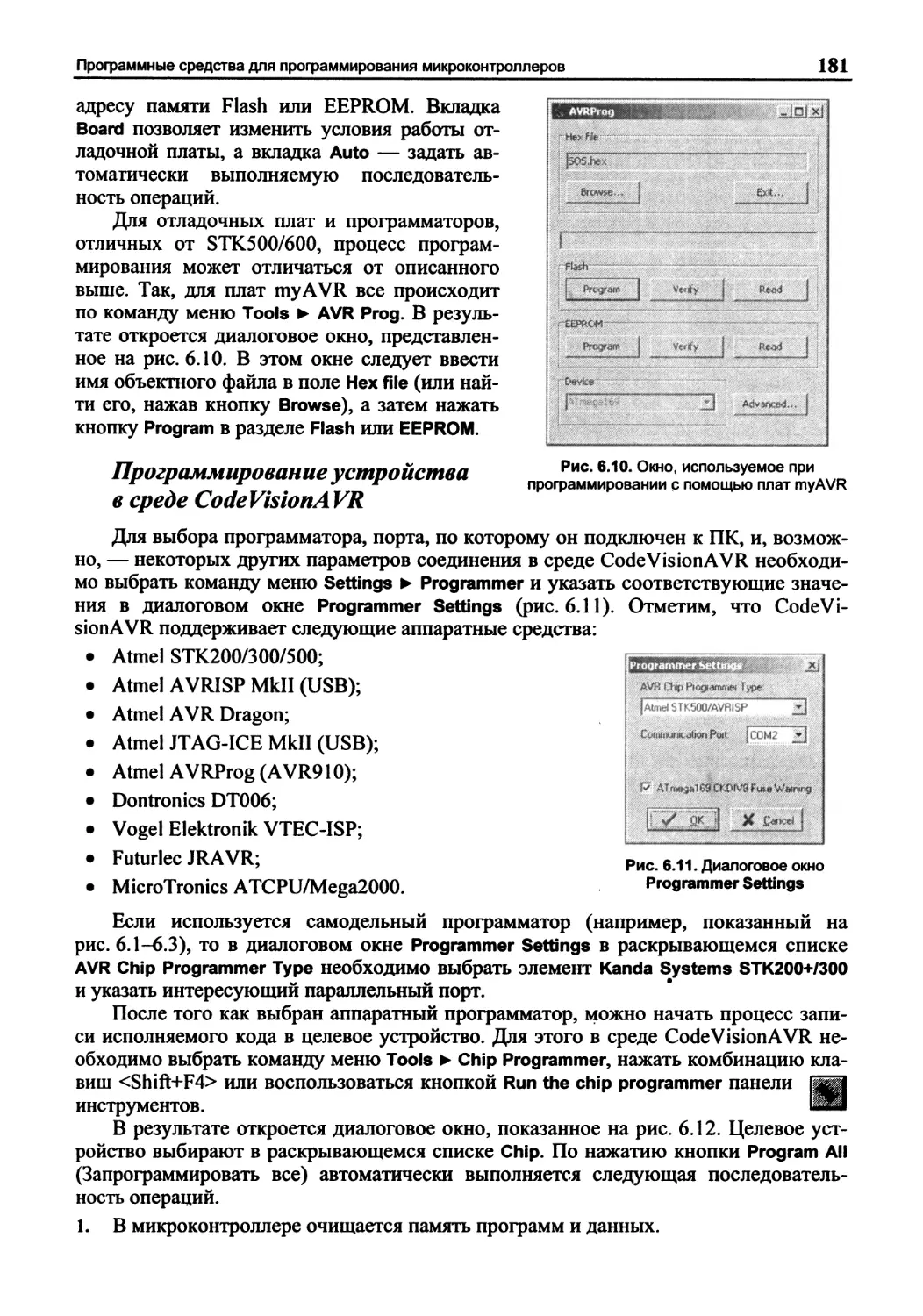

Программирование устройства в среде CodeVisionAVR......181

ЧАСТЬ III. АРХИТЕКТУРА МИКРОКОНТРОЛЛЕРОВ PIC 184

Гдава 7. Восьмиразрядные микроконтроллеры PIC.....................185

Общие аспекты архитектуры восьмиразрядных

МИКРОКОНТРОЛЛЕРОВ PIC....................................... 186

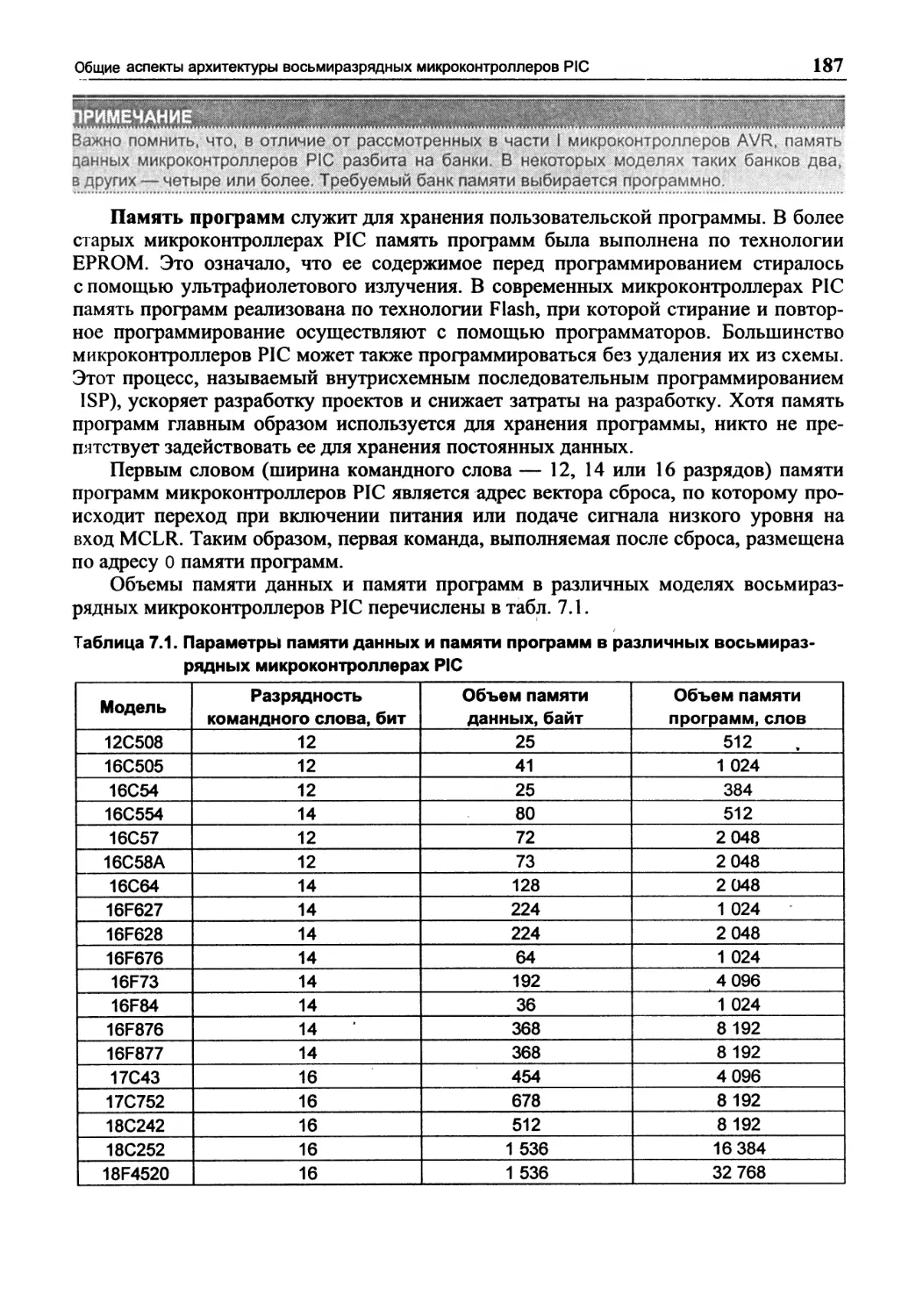

Организация памяти...........................................186

Организация тактирования.....................................188

Порты........................................................190

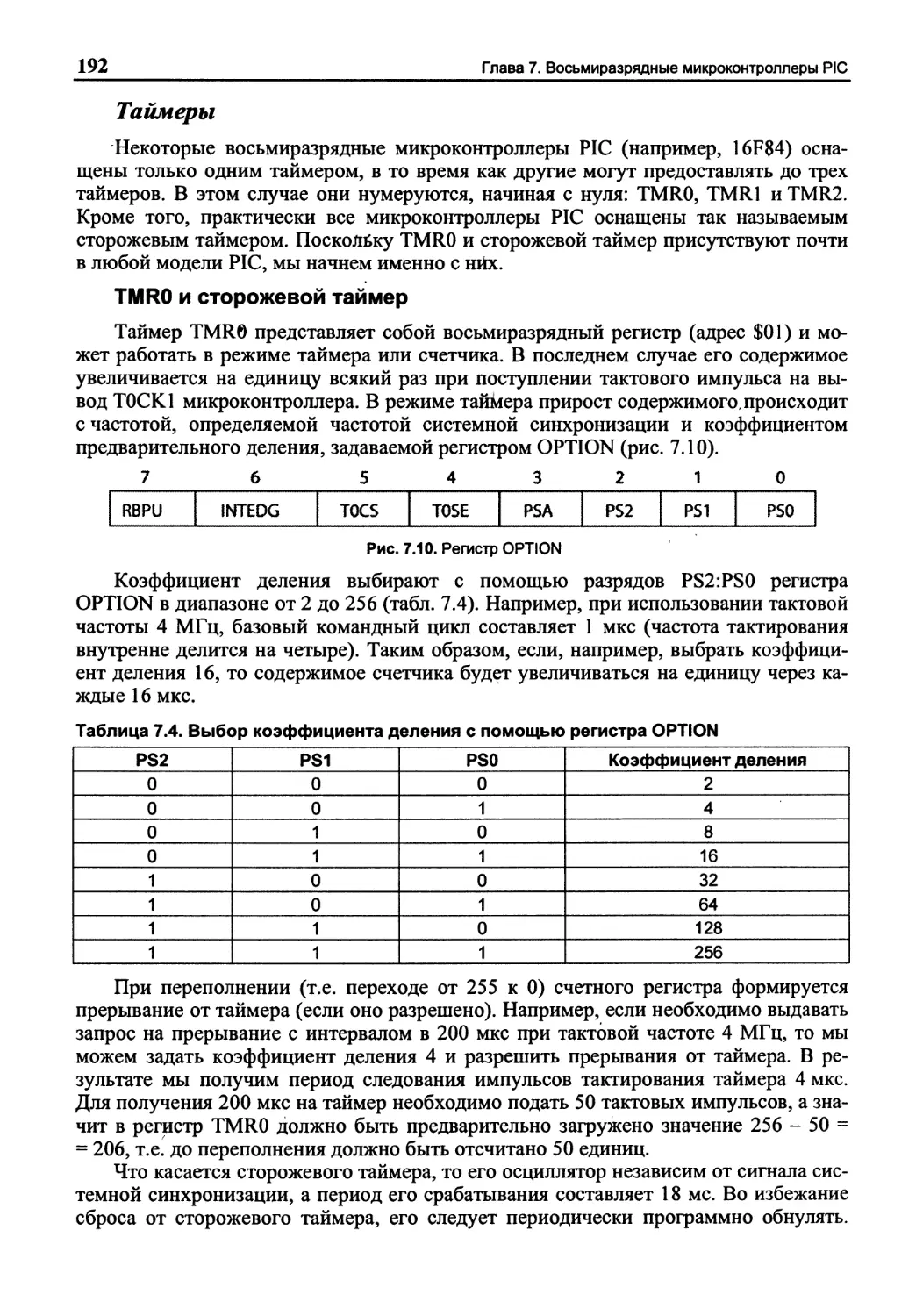

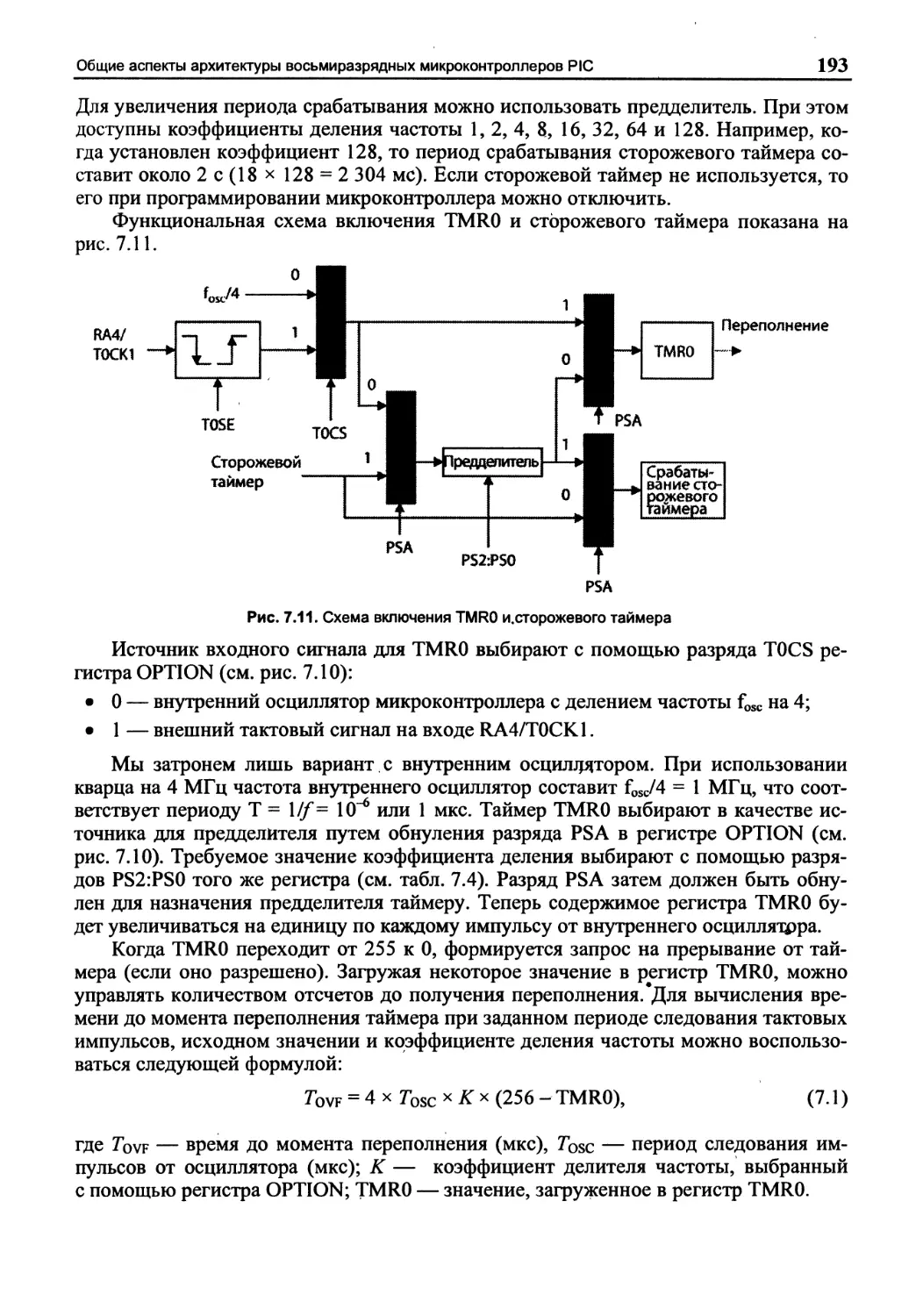

Таймеры......................................................192

TMR0 и сторожевой таймер...................................192

TMR1.......................................................194

TMR2.......................................................195

Модуль ССР.................................................197

Обработка прерываний.........................................198

Микроконтроллеры серии Р1С17Сх.............................199

Микроконтроллеры серии Р1С18Сх.............................200

Сброс........................................................202

Последовательный обмен данными...............................202

Приемопередатчик USART.....................................203

Синхронная передача данных по интерфейсу SPI...............204

Синхронная передача данных по интерфейсу 12С...............206

Аналого-цифровое преобразование..............................207

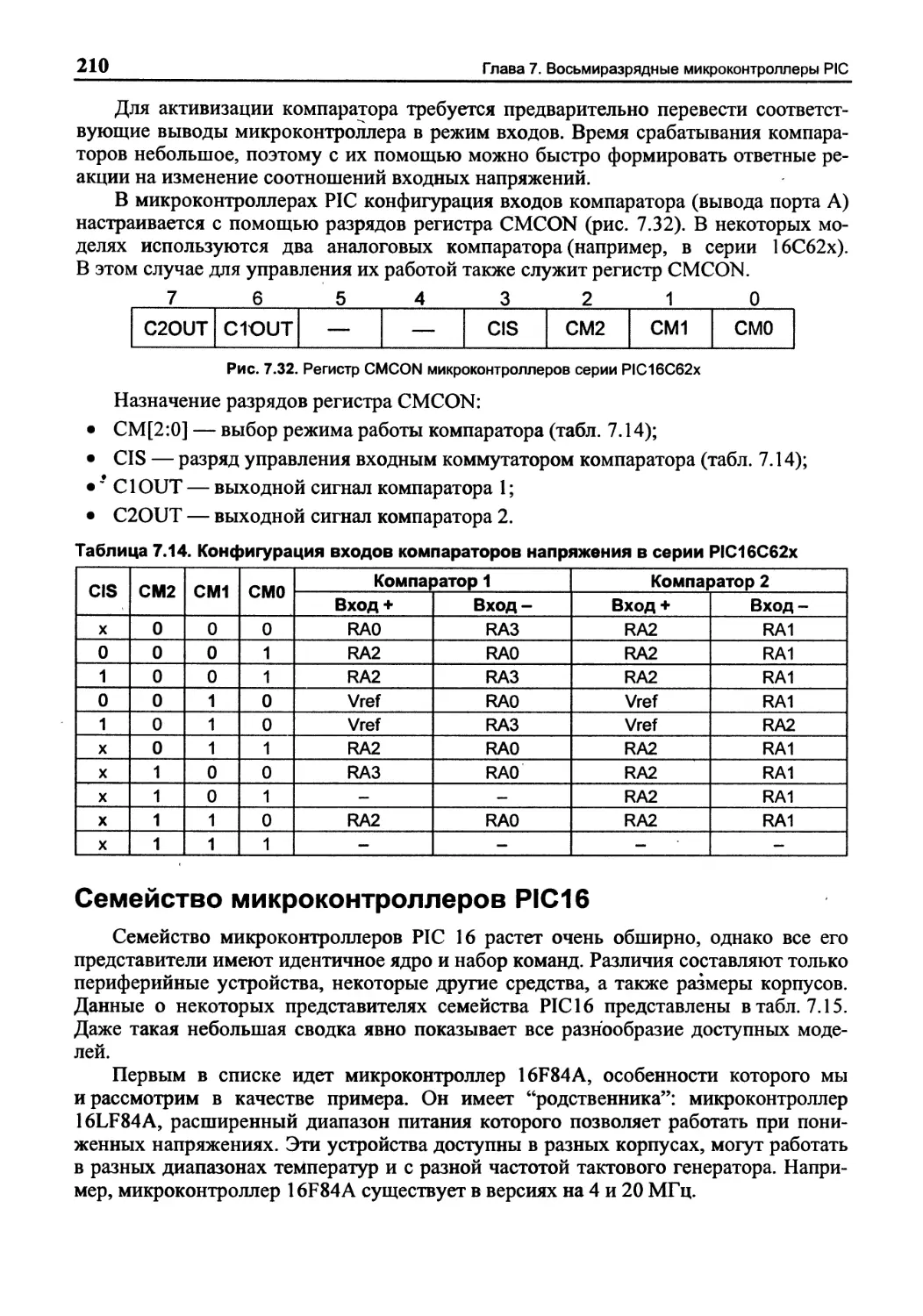

Встроенный аналоговый компаратор...........................209

Семейство микроконтроллеров PIC16...............................210

Микроконтроллер 16F84A.......................................211

Регистр состояния.............................,............212

Организация памяти.........................................213

Слово конфигурации.........................................215

Память EEPROM..............................................215

Микроконтроллеры серии 12F50X...................................216

Содержание 7

Глава 8. Семейство PIC18F.........................................219

Организация памяти..............................................221

Конфигурационные регистры....................................222

Организация тактирования........................................225

Внутренний осциллятор........................................226

Переключение источника тактирования...................................................... 226

Таймеры.........................................................227

TMR0.........................................................227

TMR1.........................................................228

TMR3.........................................................228

АЦП:............................................................229

Обработка прерываний............................................229

Глава 9. Семейство PIC24..........................................231

Порты...........................................................234

Таймеры.........................................................236

Прерывания......................................................236

Вложение прерываний..........................................238

Системные прерывания.........................................239

Окно Program Space Visibility...................................239

Интерфейс SPI...................................................240

ПортРМР.........................................................241

АЦП.............................................................241

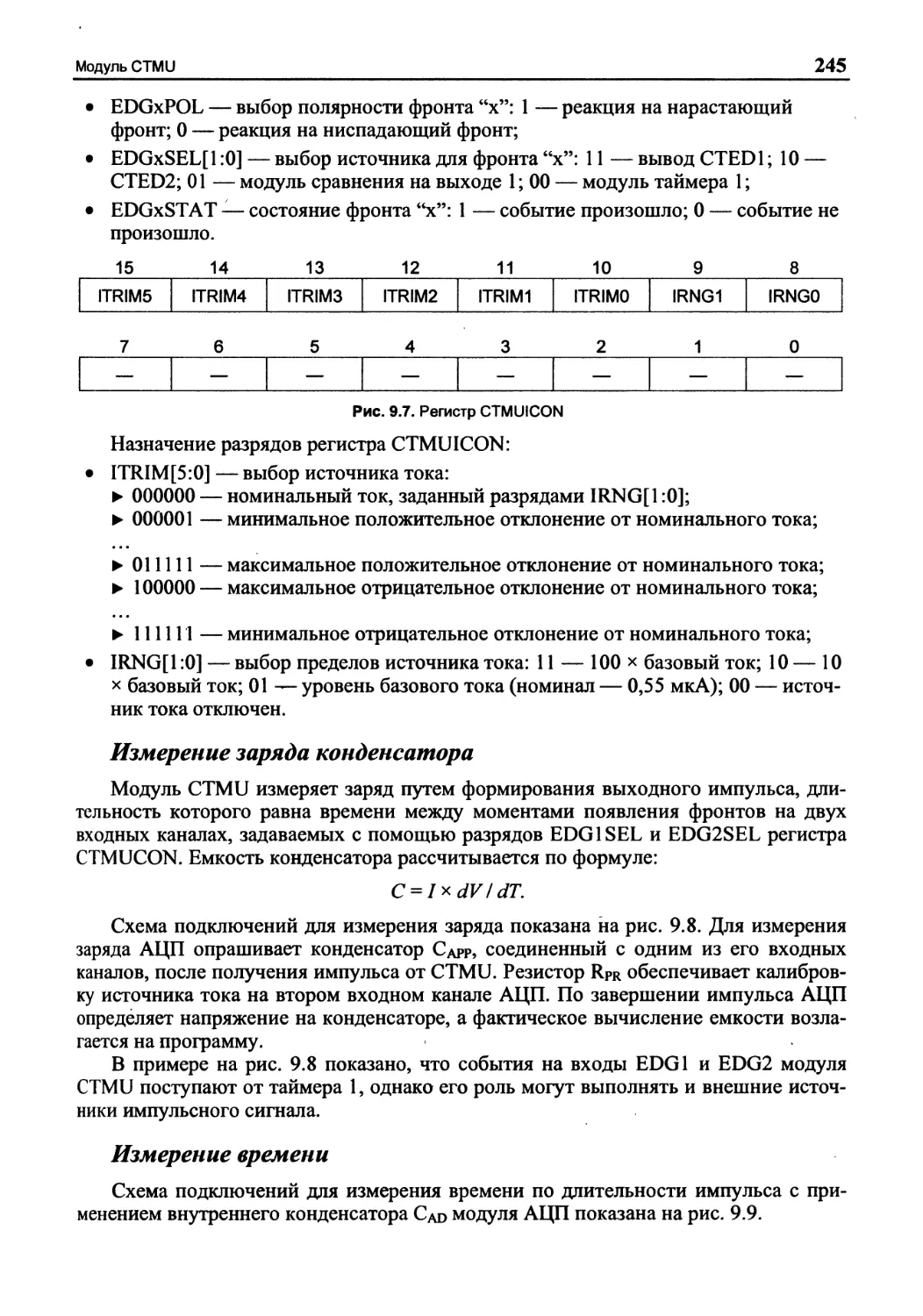

МОДУЛЬ CTMU.....................................................244

Измерение заряда конденсатора................................245

Измерение времени............................................245

Формирование импульсных последовательностей и задержек.......246

Глава 10. Семейство PIC32.........................................248

Порты...........................................................250

Таймеры.........................................................251

Системная шина..................................................251

Организация памяти..............................................252

Прерывания и исключения.........................................254

Система тактирования............................................258

Интерфейс SPI...................................................258

ПортРМР.........................................................258

АЦП.............................................................259

Модуль сравнения на выходе......................................259

ЧАСТЬ IV. КОМПИЛЯТОРЫ И СРЕДСТВА РАЗРАБОТКИ ДЛЯ

МИКРОКОНТРОЛЛЕРОВ PIC 260

Глава 11. Компилятор CCS-PICC...............................261

Создание проектов CCS-PICC вручную........................261

Создание проектов CCS-PICC с помощью PIC wizard..........265

Создание проектов CCS-PICC с помощью PIC24 Wizard.........271

Открытие и добавление в проект файлов с исходным кодом....272

КОМПИЛЯЦИЯ ПРОЕКТА.......................................272

8

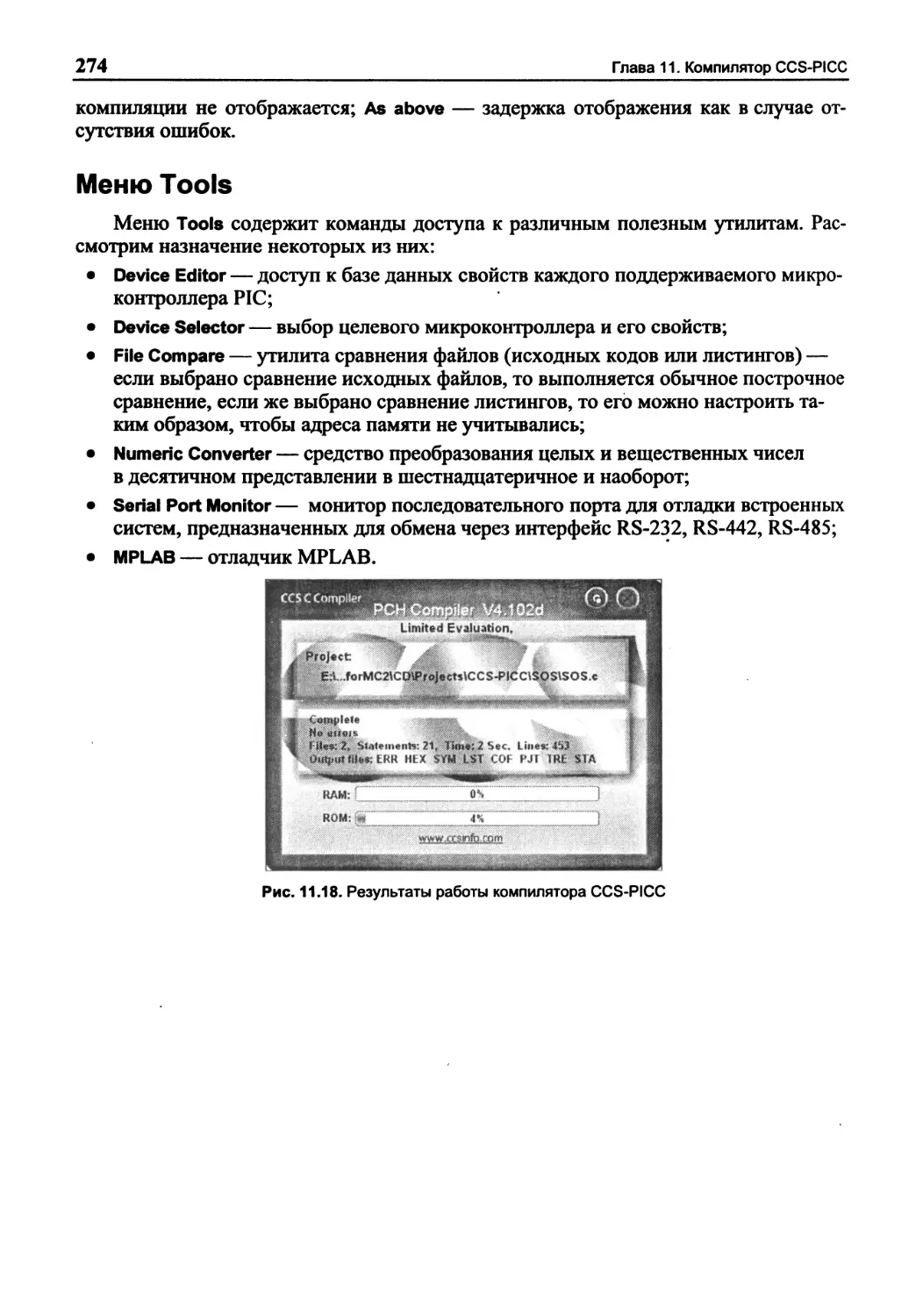

Меню Tools..............................................274

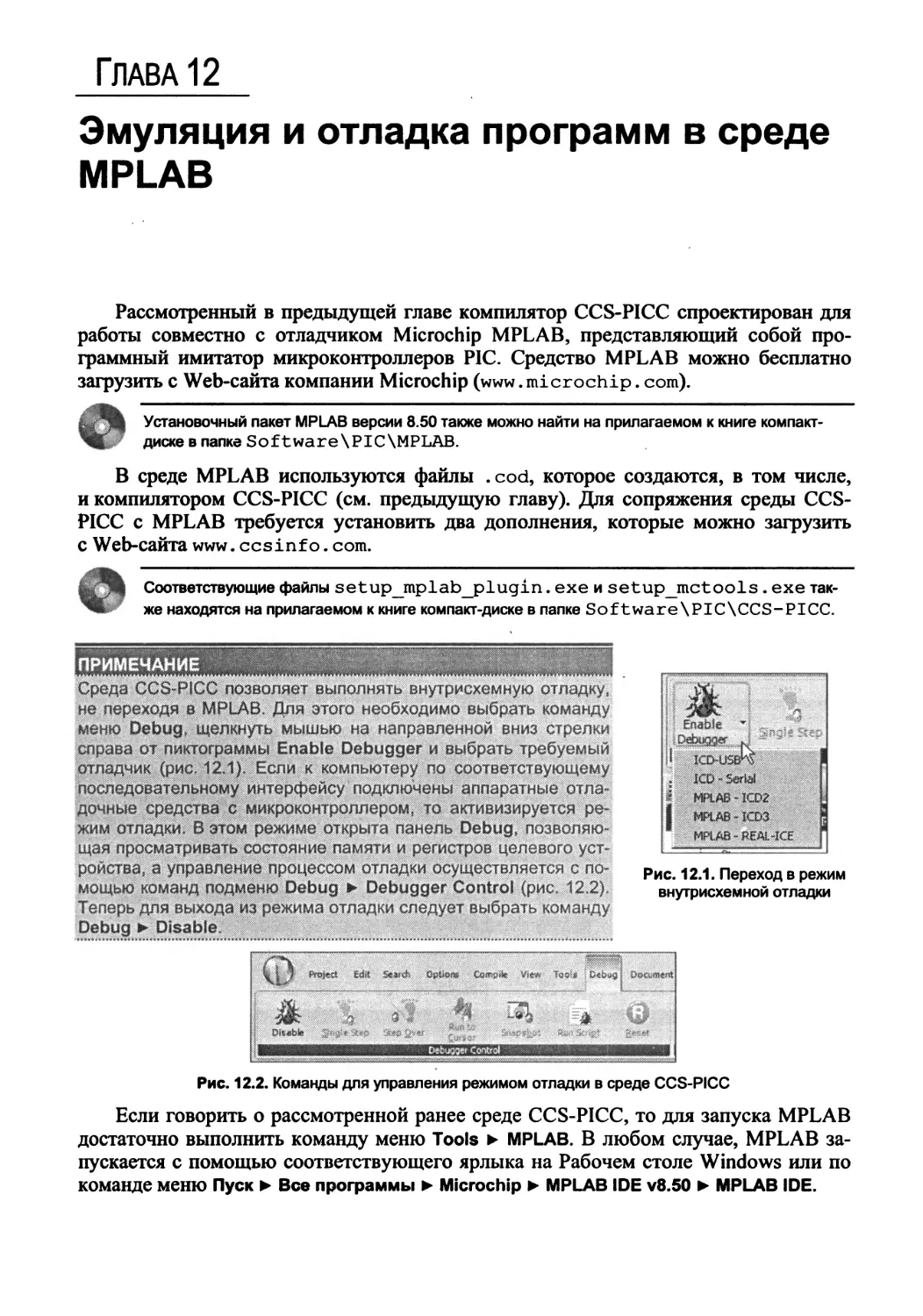

Глава 12. Эмуляция и отладка программ в среде MPLAB.......275

Рабочая область и проект MPLAB..........................276

Компиляция под управлением MPLAB........................277

Настройка режима отладки/эмуляции.......................277

Работа в режиме отладки/эмуляции........................279

ОКНА ОТЛАДЧИКА........................................ 280

Глава 13. Компилятор mikroC............................. 282

Создание проекта mikroC.................................283

Компиляция проекта......................................285

Добавление в проект файлов с исходным кодом.............287

Эмуляция выполнения программы...........................288

вспомогательные инструменты среды mikroC................290

Глава 14. Компиляторы СЗО и С32...........................294

Компилятор СЗО..........................................294

Компилятор С32..........................................296

Глава 15. Программаторы для микроконтроллеров PIC.........297

Программные средства для программирования микроконтроллеров.298

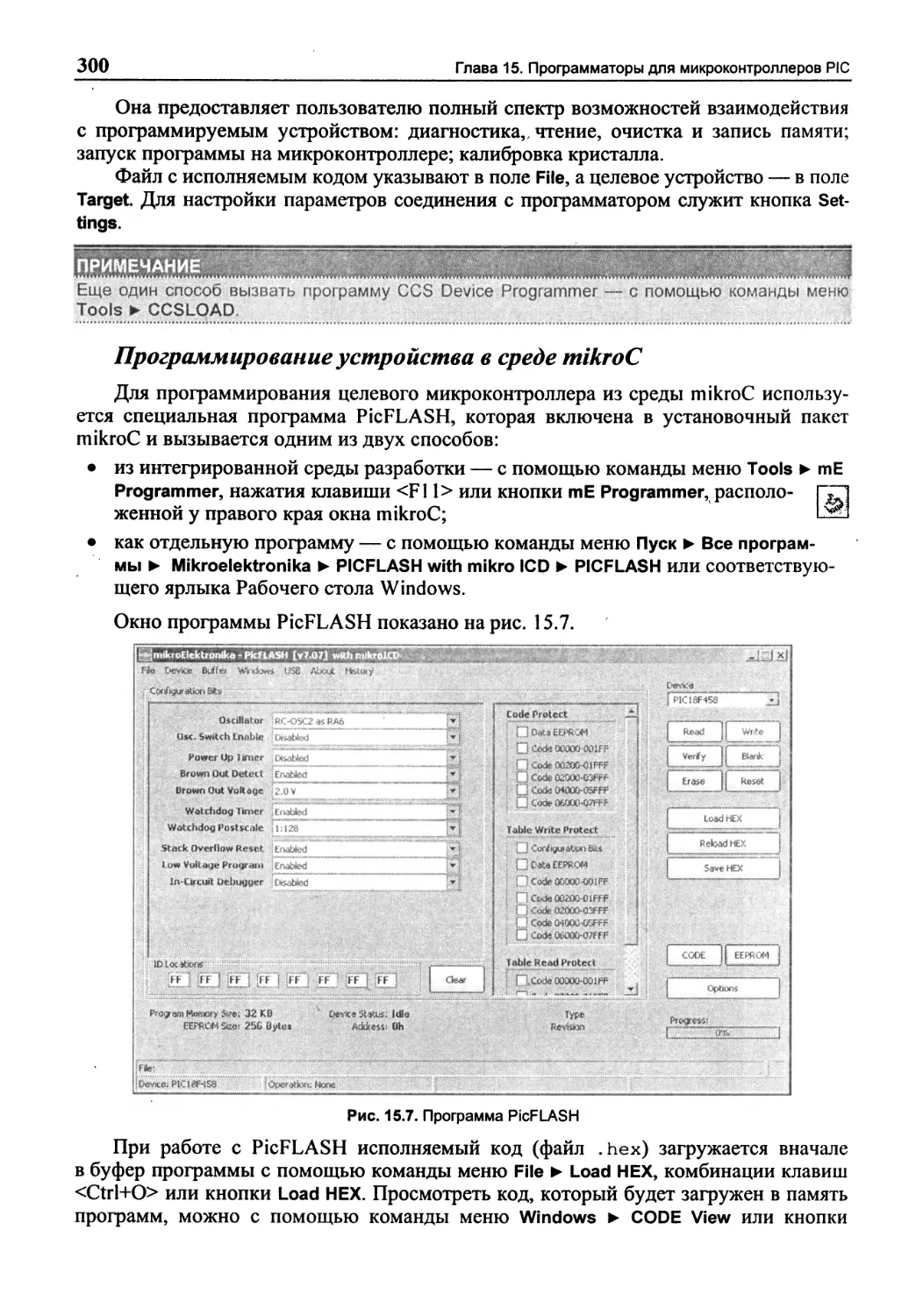

Программирование устройства в среде mikroC............300

ЧАСТЬ V. ЯЗЫК С И ДИРЕКТИВЫ ПРЕПРОЦЕССОРА 302

Глава 16. Основы языка С........................................303

Вводные понятия...............................................303

Структура программы на С......................................304

Типы данных, переменные, константы............................306

Правила преобразований из одной системы счисления в другую.308

Тип char...................................................309

Пользовательские типы......................................309

Переменные.................................................310

Область видимости переменных.............................310

Константы..................................................311

Перечислимые типы..........................................311

Приведение типов...........................................312

Оператор sizeof............................................312

Функции.......................................................312

Возвращаемые значения......................................313

Прототипы функций..........................................314

IGiaccbi памяти при объявлении локальных переменных........314

Рекурсия...................................................315

Структуры.....................................................316

Указатели и адреса переменных.................................318

Передача в функции параметров по ссылке....................318

Указатели на структуры.....................................319

МАССИВЫ И СТРОКИ..............................,...............320

Содержание

9

Строки.........................................................321

Многомерные массивы...................................>...... 321

Операторы ветвления...............................................321

Оператор if-else...............................................322

Условные выражения.............................................322

Оператор switch-case...........................................322

Циклические конструкции...........................................323

Конструкция while............................................ 323

Конструкция for.............................................. 324

Конструкция do-while...........................................324

Организация бесконечных циклов............................... 325

Операторы break и continue.....................................325

Стандартные функции ввода/вывода..................................325

Ввод/вывод символов с помощью функций getcharQ и putcharQ......326

Функции вывода строк puts 0 и printfO..........................327

Функции ввода строк gets 0 и scanfO.......................... 328

Директивы препроцессора...........................................329

Директива ^include.............................................329

Директива ^define..............................................329

Директивы условной компиляции............................,.....331

Директива tterror..............................................333

Директива ftpragma компилятора CodeVisionA VR..................333

Директивы, характерные для компилятора CCS-PICC................333

Директива #bit...............................................334

Директива #byte..............................................334

Директива #case..............................................334

Директива ^device............................................334

Директива #fiise.............................................335

Директива #locate............................................336

Директива #org...............................................336

Директива #opt...............................................337

Директива #priority..........................................337

Директива #reserve...........................................338

Директива #rdm...............................................338

Директива #type..............................................338

Директива #use delay........................................*338

Директива #use xxxio.........................................338

Директива #use i2c...........................................339

Директива #use rs232.........................................340

Директива #zero_ram..........................................341

Обработка прерываний..............................................341

Обработка прерываний в среде WinAVR............................341

Обработка прерываний в среде CodeVisionAVR.....................343

Обработка прерываний в среде CCS-PICC..........................343

Обработка прерываний в среде mikroC............................345

Обработка прерываний в среде С30............................... 345

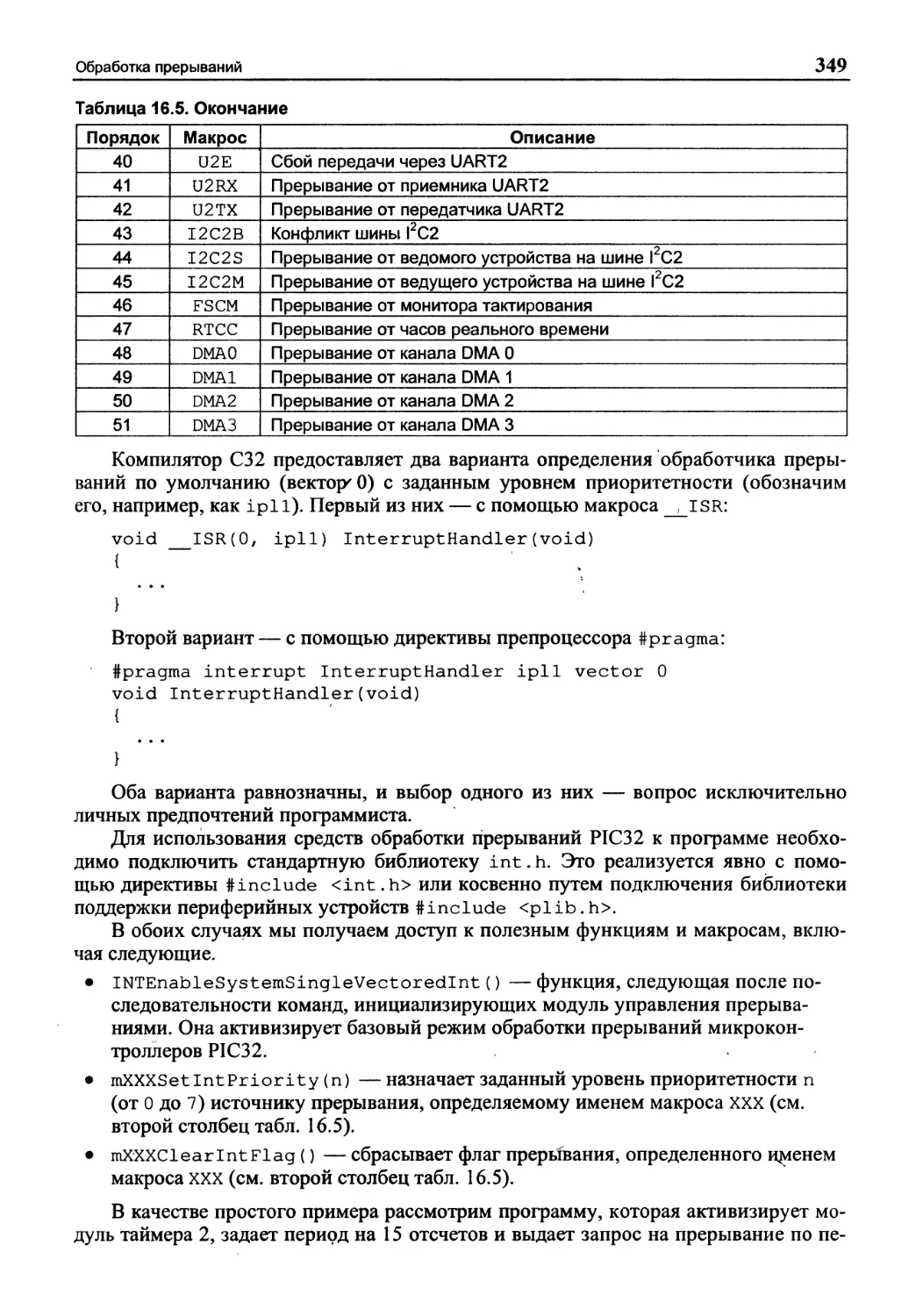

Обработка прерываний в среде С32............................... 347

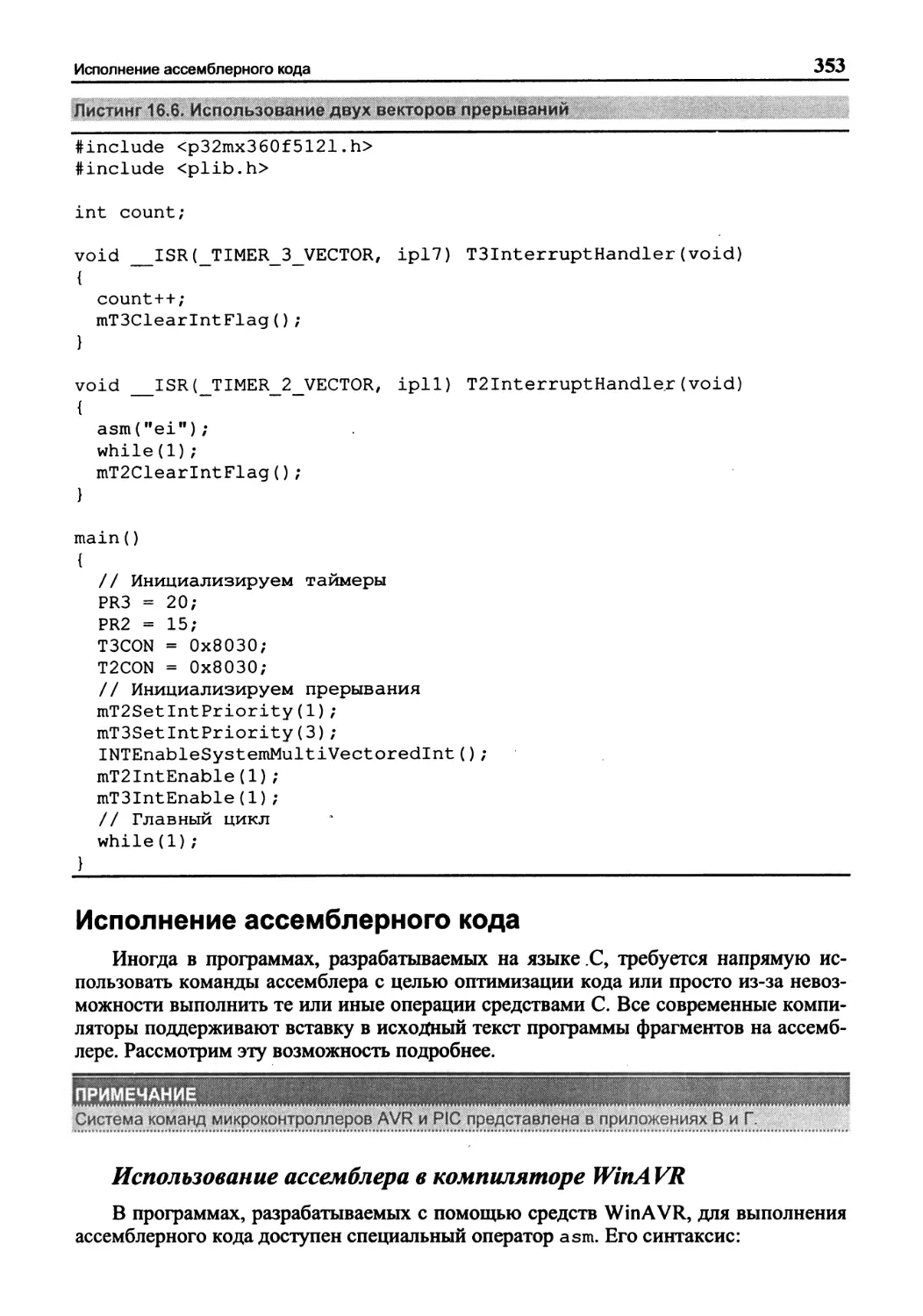

Исполнение ассемблерного кода.....................................353

Использование ассемблера в компиляторе WinAVR..................353

10

Ассемблерный код.............................................354

Входные и выходные операнды..................................355

Резервирование регистров.....................................356

Использование ассемблера в компиляторе CodeVisionAVR............358

Использование ассемблера в компиляторе CCS-PICC.................358

Использование ассемблера в компиляторе mikroC...................359

Использование ассемблера в компиляторах СЗО и С32...............360

Глава 17. Функции и макросы языка С для различных компиляторов. 361

Стандартные функции языка С.......................................361

Функции для работы со строками..................................363

Функции для работы с символами..................................365

Функции для работы со случайными числами........................367

Функции для работы с памятью....................................367

Функции и макросы компилятора WinAVR..............................368

Математические макросы и функции................................368

Функции для работы со строками..................................369

Функции для работы с символами..................................373

Макросы и функции для организации ввода/вывода..................373

Функции управления микроконтроллером............................378

Макросы для работы со сторожевым таймером.......................379

Функции для работы со случайными числами........................380

Функции для работы с памятью....................................380

Макросы для обработки прерываний................................381

Макросы и функции для работы с памятью EEPROM...................382

Функции и макросы компилятора CodeVisionAVR.......................383

Математические макросы и функции................................383

Функции для работы со строками................................................................. 384

Функции для работы с символами..................................387

Функции управления микроконтроллером............................387

Функции для организации ввода/вывода............................387

Функции для работы с памятью....................................388

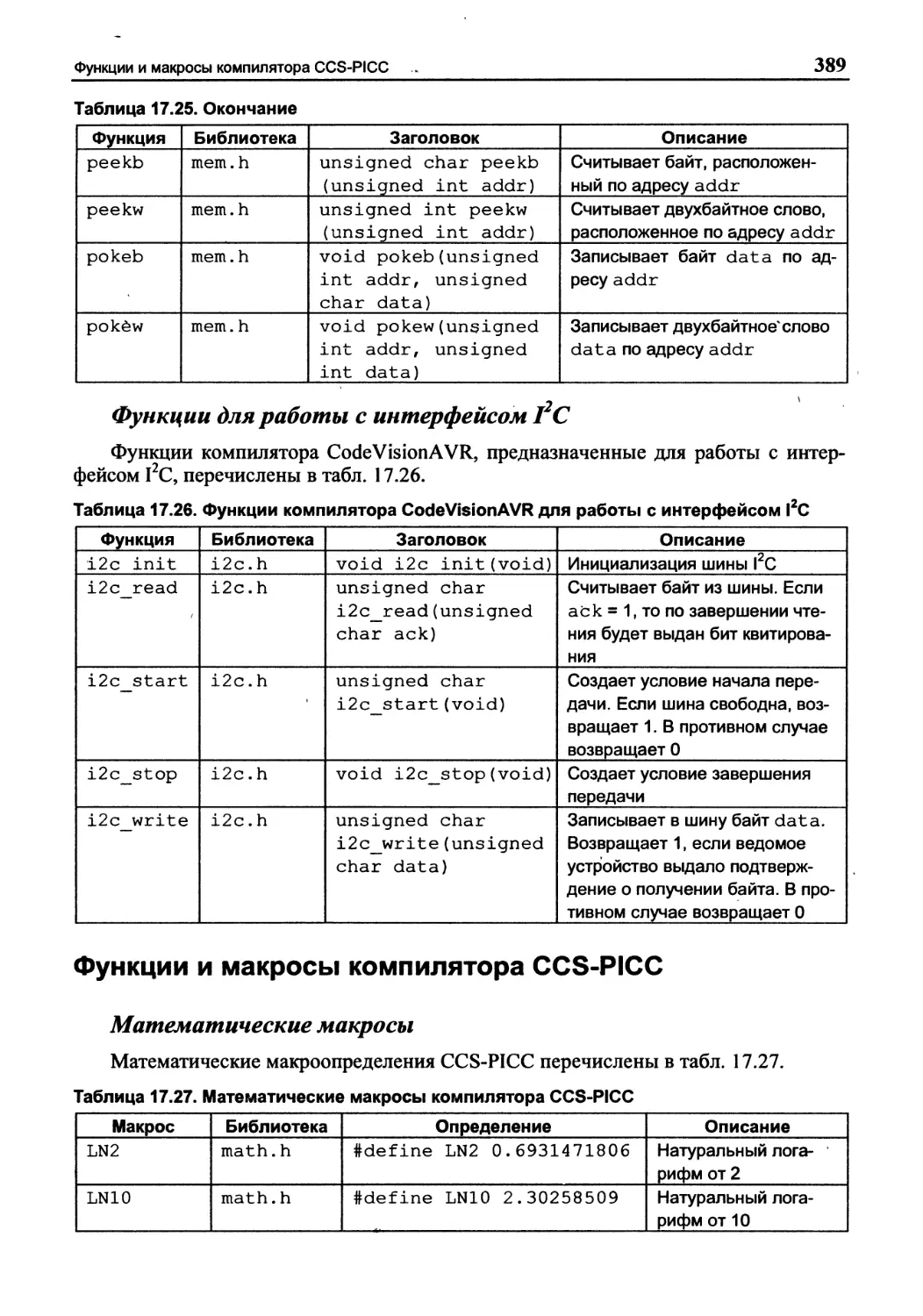

Функции для работы с интерфейсом 12С............................389

Функции и макросы компилятора CCS-PICC............................389

Математические макросы..........................................389

Функции для работы со строками..................................390

Функции для организации ввода/вывода............................391

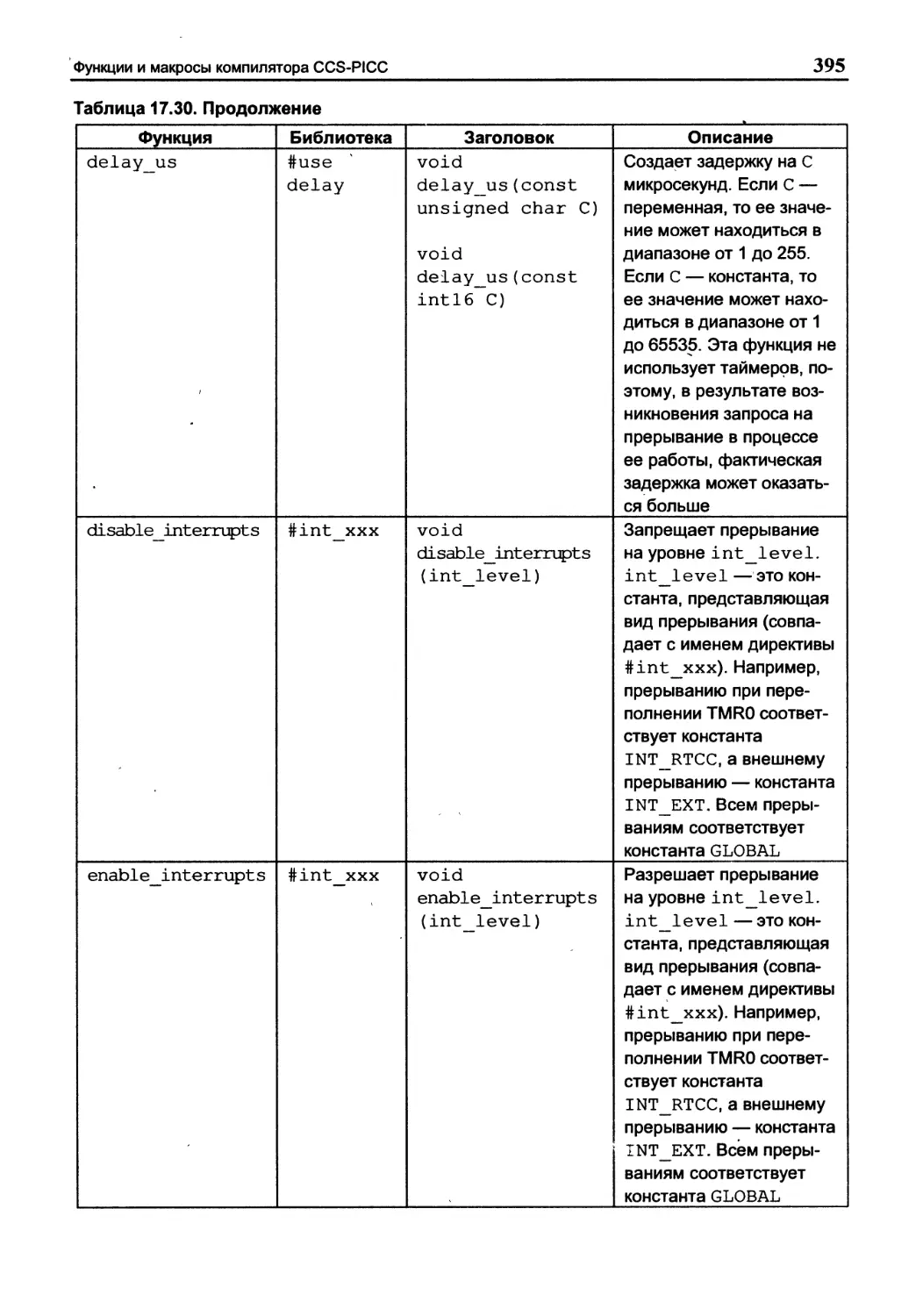

Функции управления микроконтроллерам............................394

Функции для работы с таймерами и модулем ССР....................396

Функции для работы с разрядами и памятью........................398

Функции для работы с памятью EEPROM.............................400

Функции для работы с интерфейсом SPI............................401

Функции для работы с интерфейсом PSP............................402

Функции для работы с интерфейсом fC........................... 402

Функции для работы с аналоговыми сигналами......................403

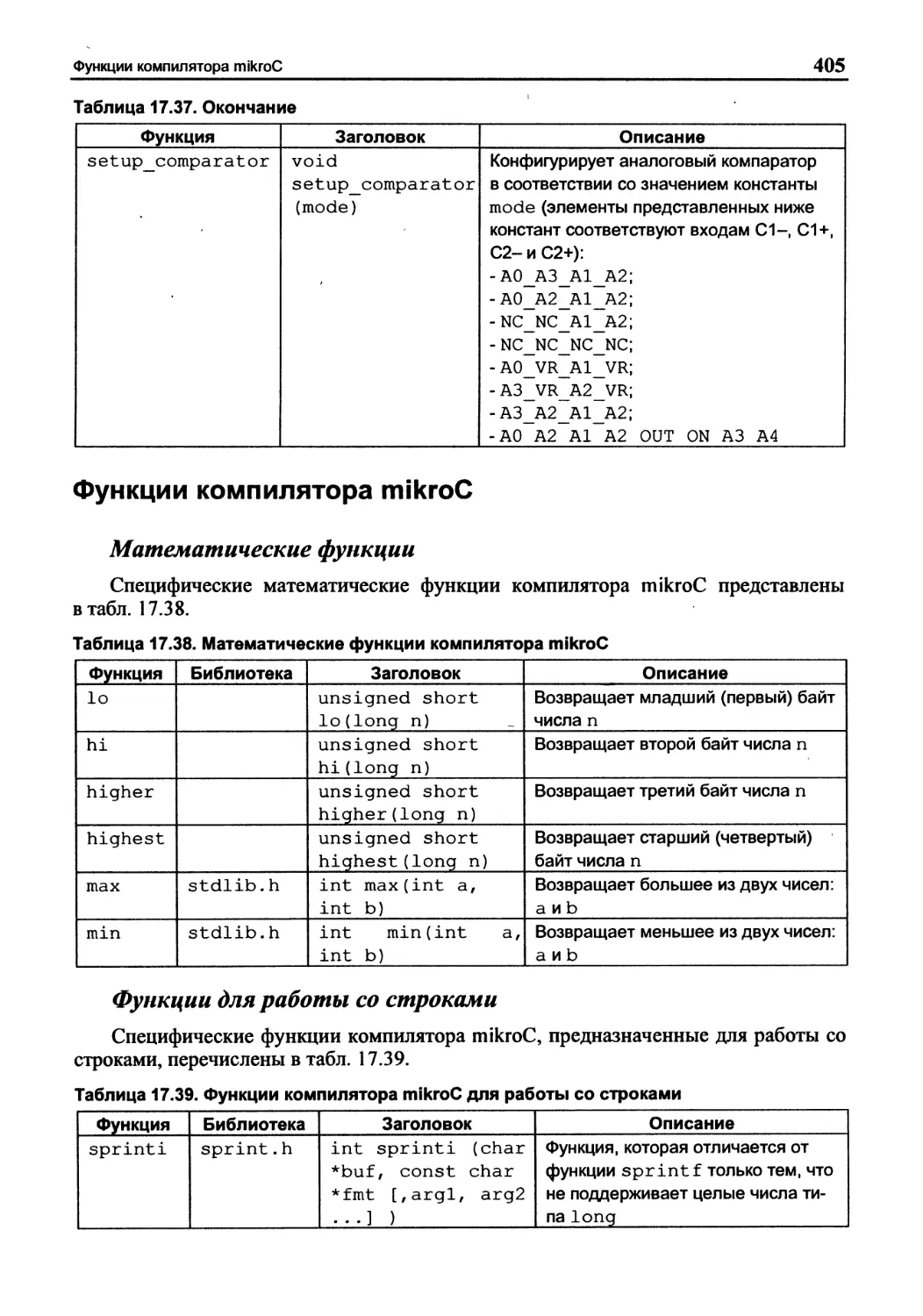

Функции компилятора mikroC........................................405

Математические функции..........................................405

Функции для работы со строками..................................405

Функции преобразований..........................................407

Функции управления микроконтроллером.......................... 407

Содержание

11

Функции для работы с периферийными устройствами.......408

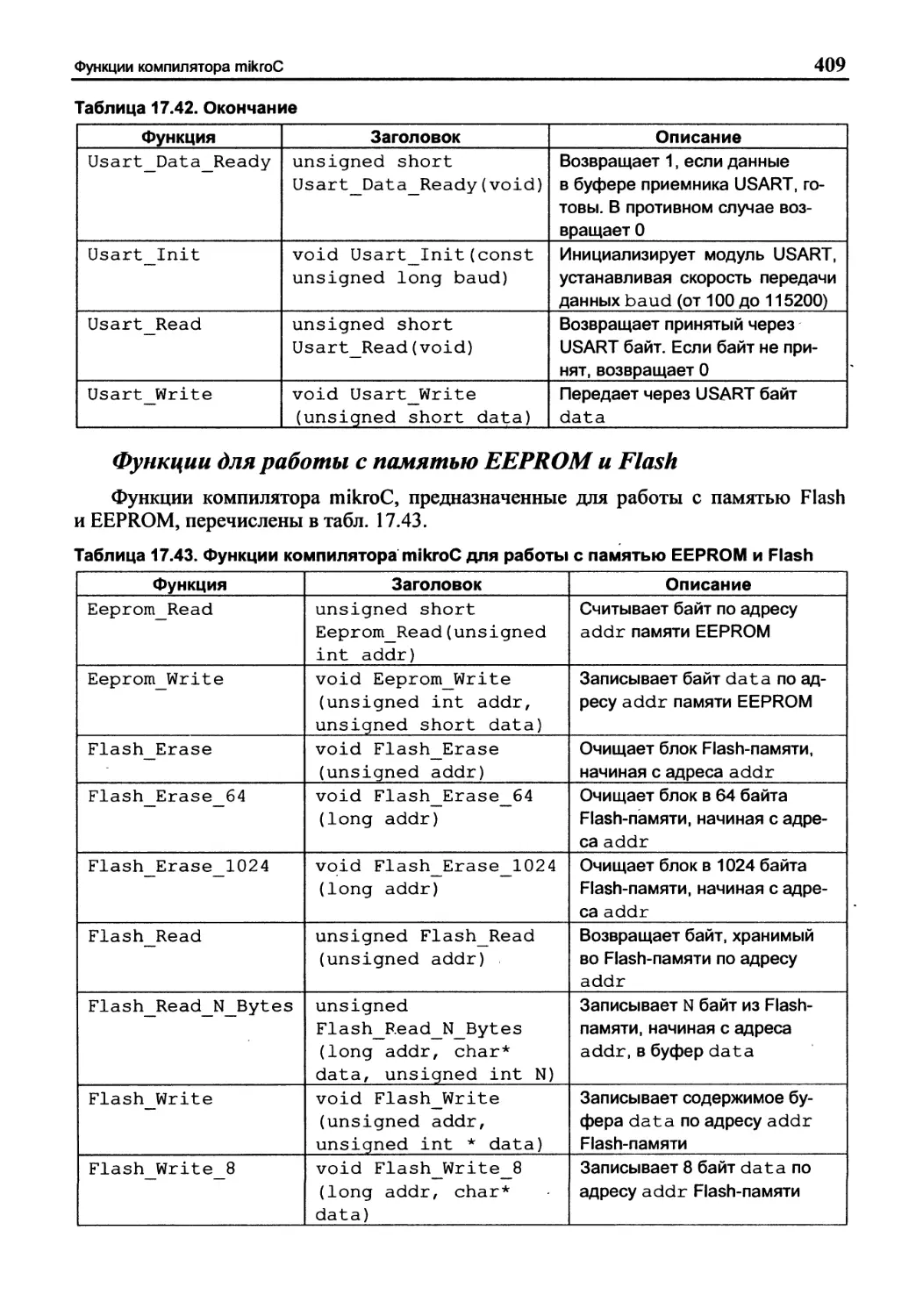

Функции для работы с памятью EEPROM и Flash...........409

Функции для работы с интерфейсом 12С..................410

Функции для работы с интерфейсом SPI...................410

ЧАСТЬ VI. ПРОГРАММНЫЕ ПРИМЕРЫ ДЛЯ

МИКРОКОНТРОЛЛЕРОВ AVR 412

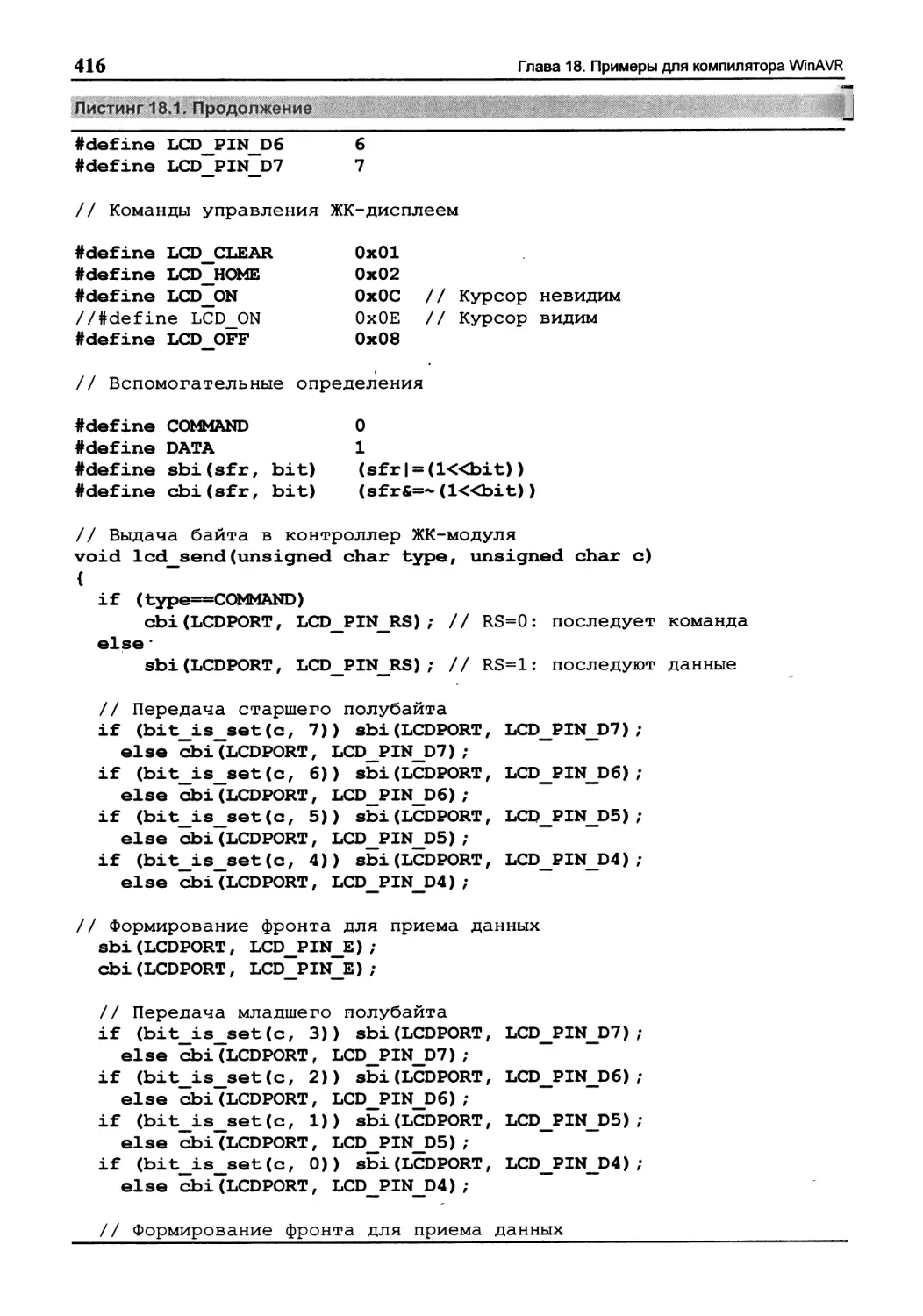

Глава 18. Примеры для компилятора WinAVR.................413

Управление ЖК-дисплеем.................................413

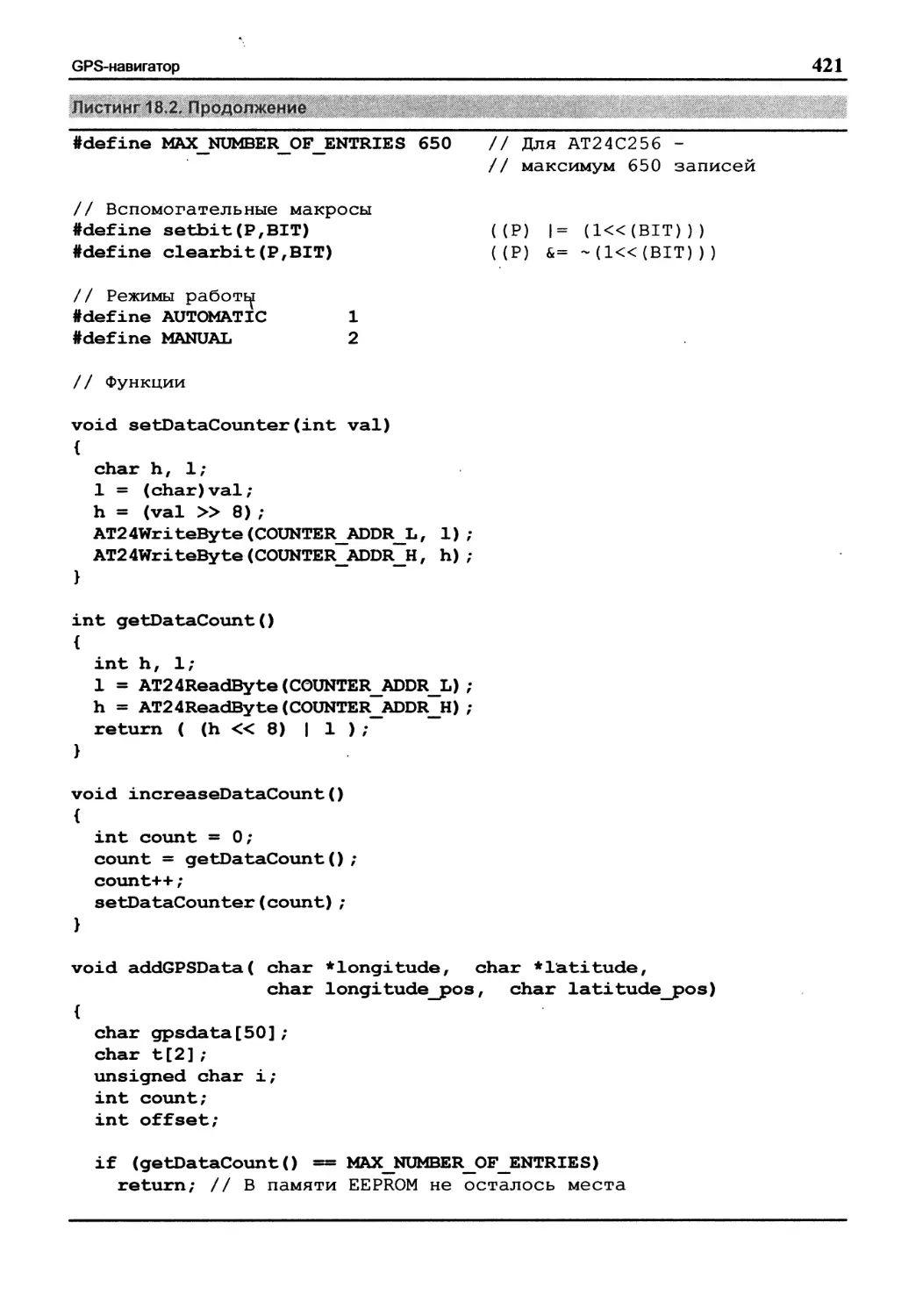

GPS-навигатор..........................................418

Глава 19. Примеры для компилятора CodeVisionAVR..........430

Управление аналого-цифровым преобразованием............430

Измерение температуры..................................433

ЧАСТЬ VII. ПРОГРАММНЫЕ ПРИМЕРЫ ДЛЯ

МИКРОКОНТРОЛЛЕРОВ PIC 435

Глава 20. Примеры для компилятора CCS-PICC.................436

Отображение состояния выводов порта.................... 436

Управление частотой мерцания светодиодов с помощью различных

ТАЙМЕРОВ.................................................437

Управление светофорами на перекрестке....................438

Обмен данными в режиме PSP...............................442

Контроль предельной скорости вращения двигателя..........444

Глава 21. Примеры для компилятора mikroC...................446

Игральные “кости”........................................446

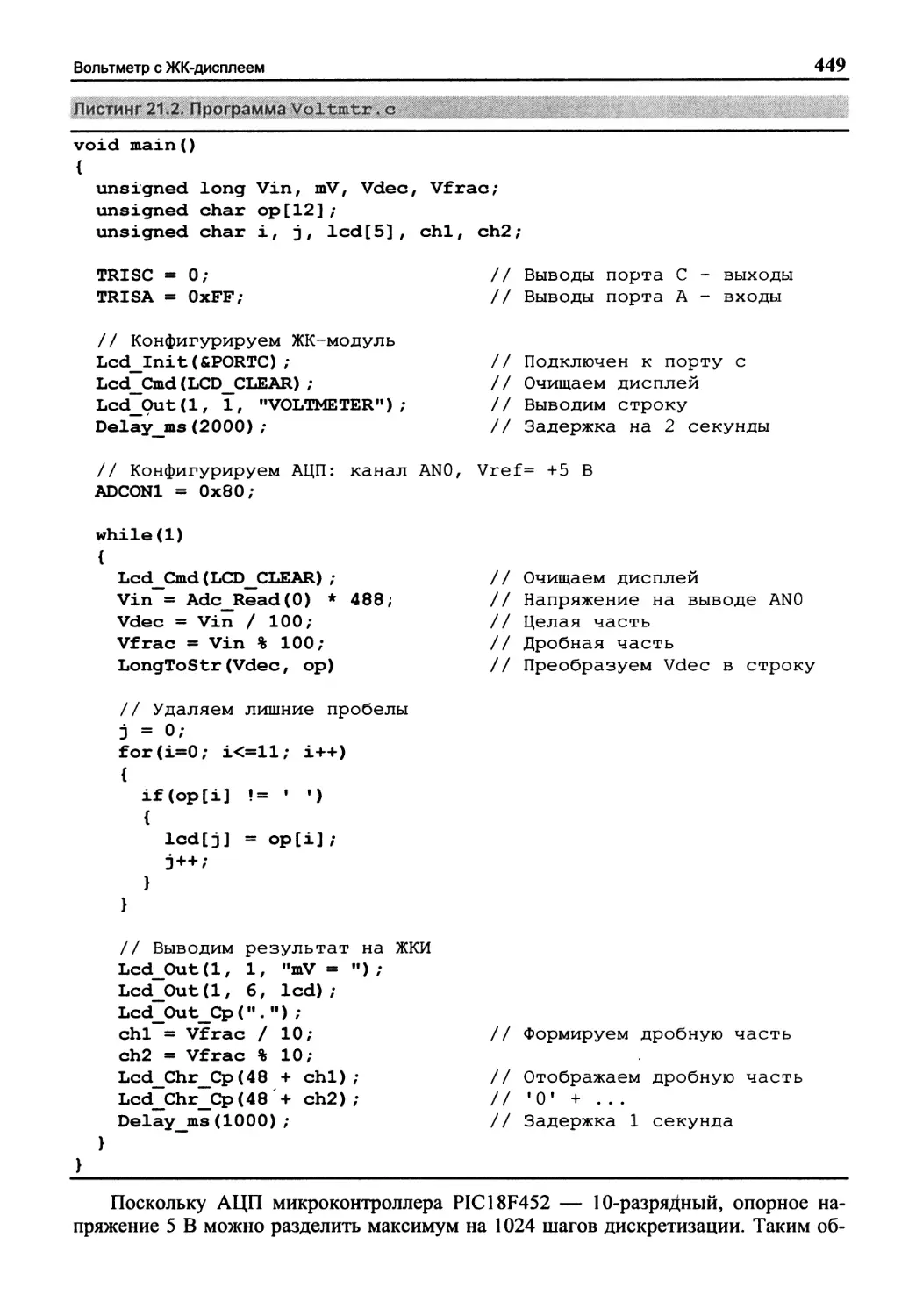

Вольтметр с ЖК-дисплеем..................................448

Калькулятор............................................ 450

Глава 22. Примеры для компилятора СЗО......................453

Использование порта РМР..................................453

Небольшая библиотека функций для доступа к ЖК-модулю...453

Расширенное управление ЖК-дисплеем.....................456

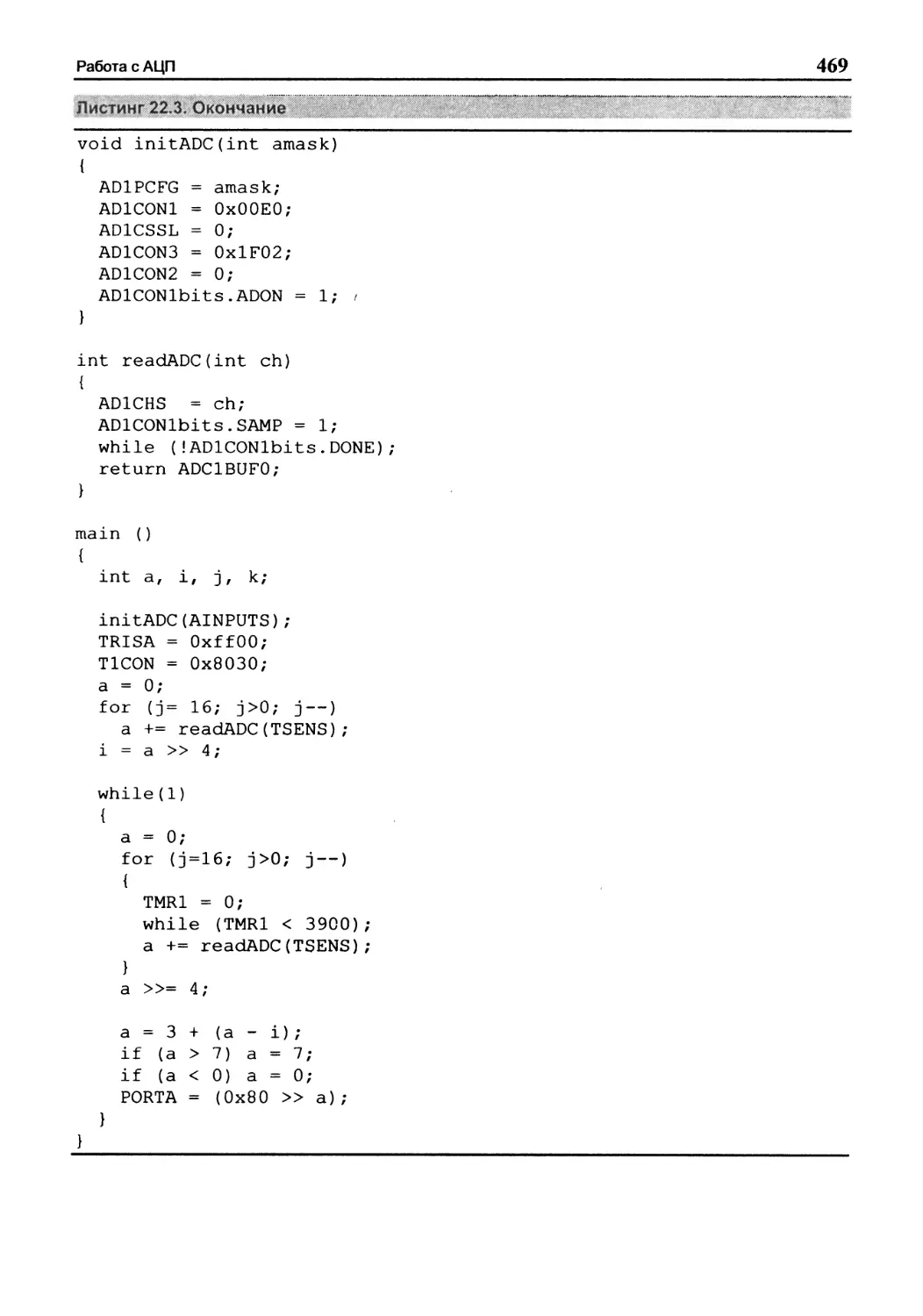

Работа с АЦП.............................................460

Считывание уровня напряжения с потенциометра...........461

Измерение температуры..................................465

Глава 23. Примеры для компилятора С32......................470

Работа с интерфейсом SPI.................................470

Работа с модулем UART....................................473

ЧАСТЬ VIII. ПРИЛОЖЕНИЯ 477

Приложение А. Таблица символов ASCH......................478

Приложение б. Преобразование из одной системы счисления

в другую.................................................479

12

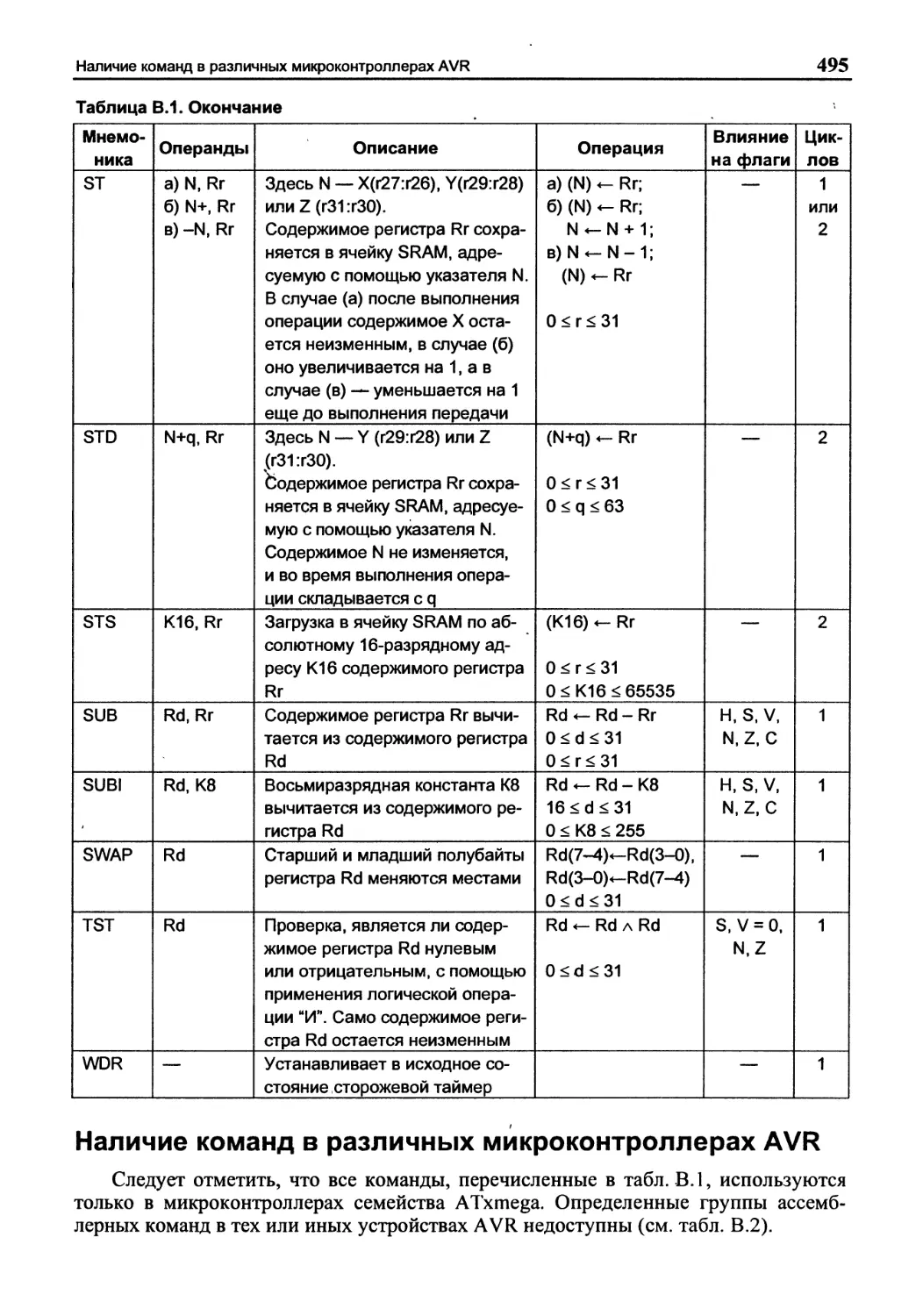

Приложение В. Система команд микроконтроллеров AVR..........482

Наличие команд в различных микроконтроллерах AVR..........495

Команды по категориям................................... 497

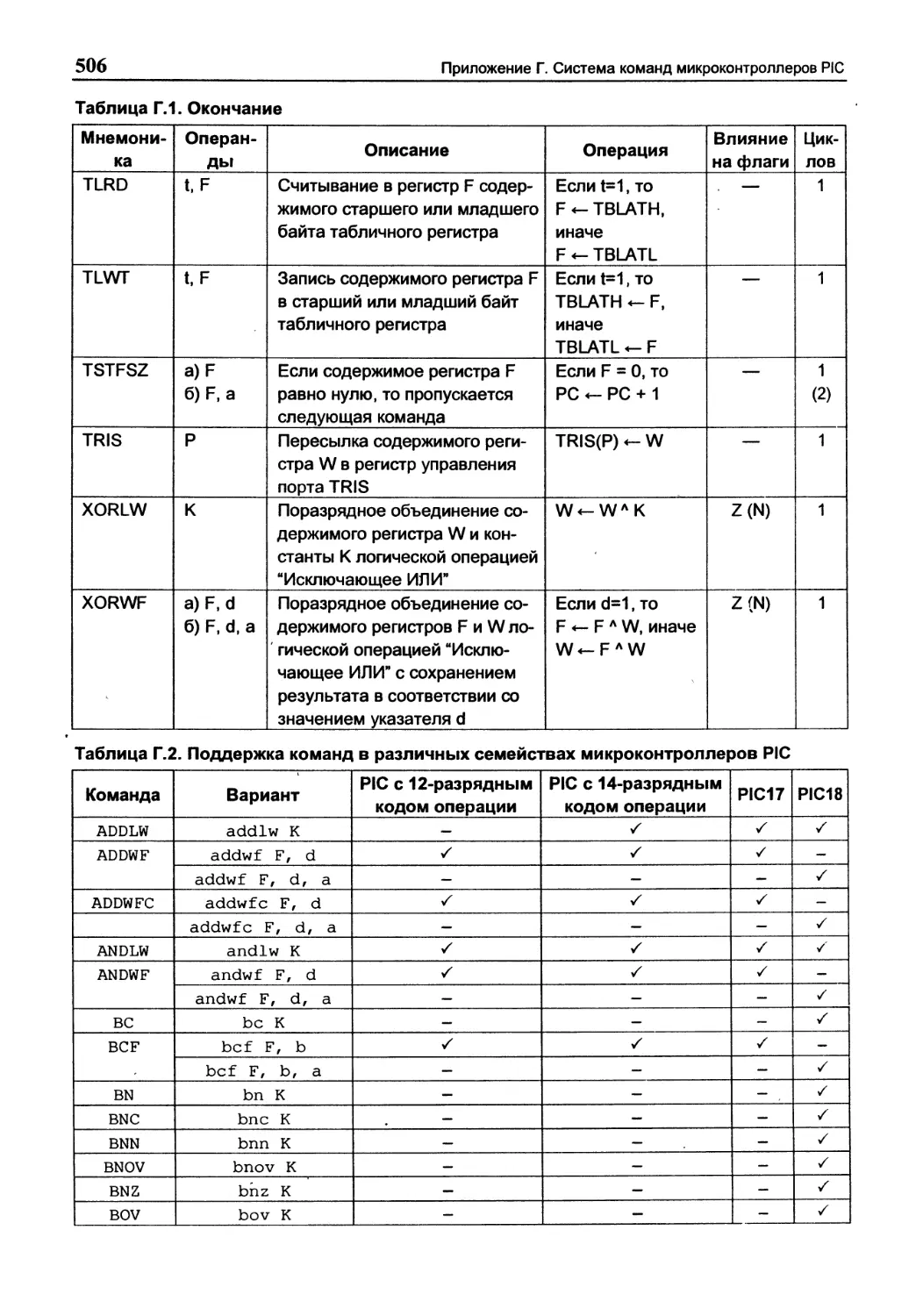

Приложение Г. Система команд микроконтроллеров PIC..........Д98

Команды восьмиразрядных микроконтроллеров.................498

Команды по категория*!..................................509

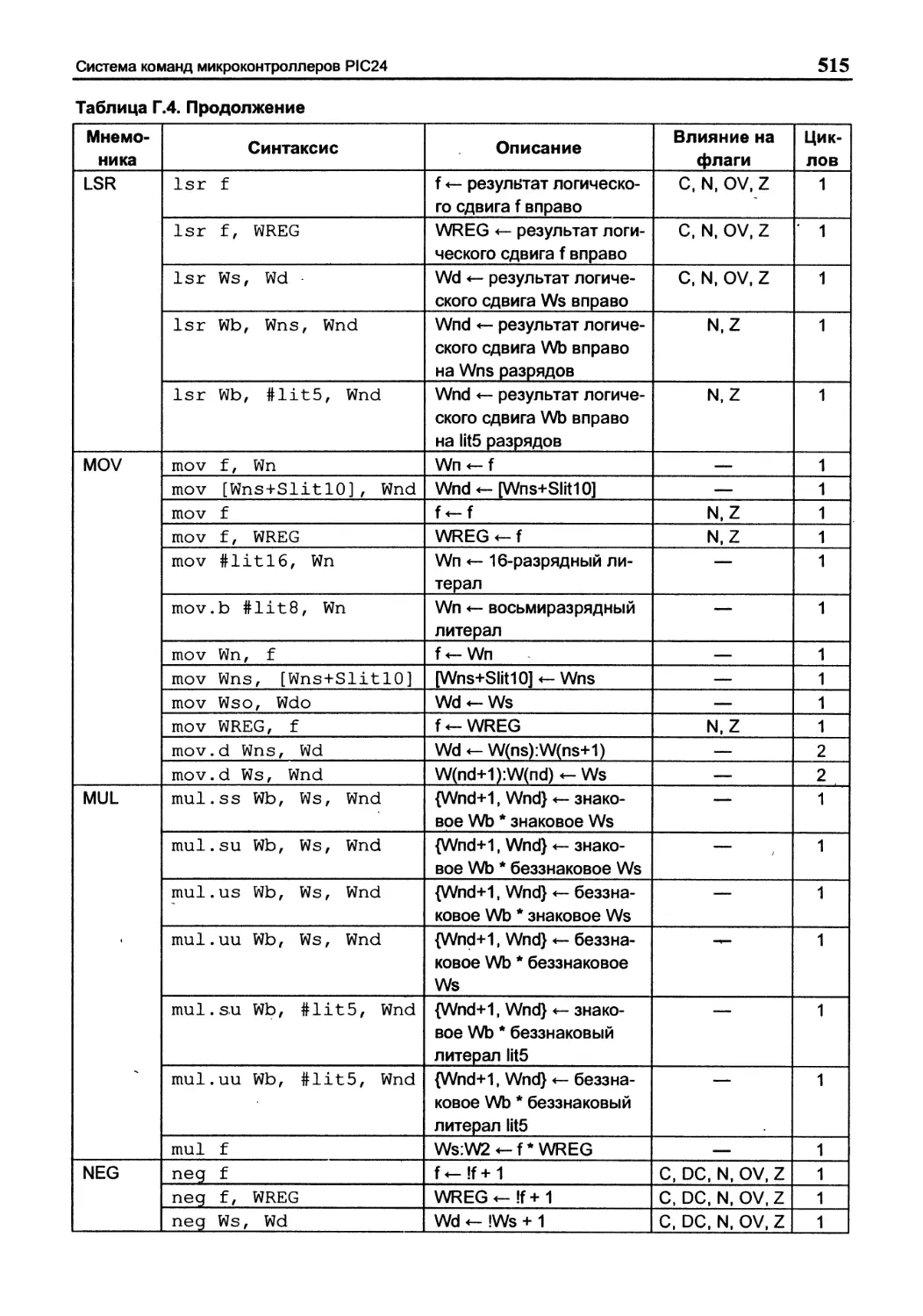

Система команд микроконтроллеров' PIC24...................510

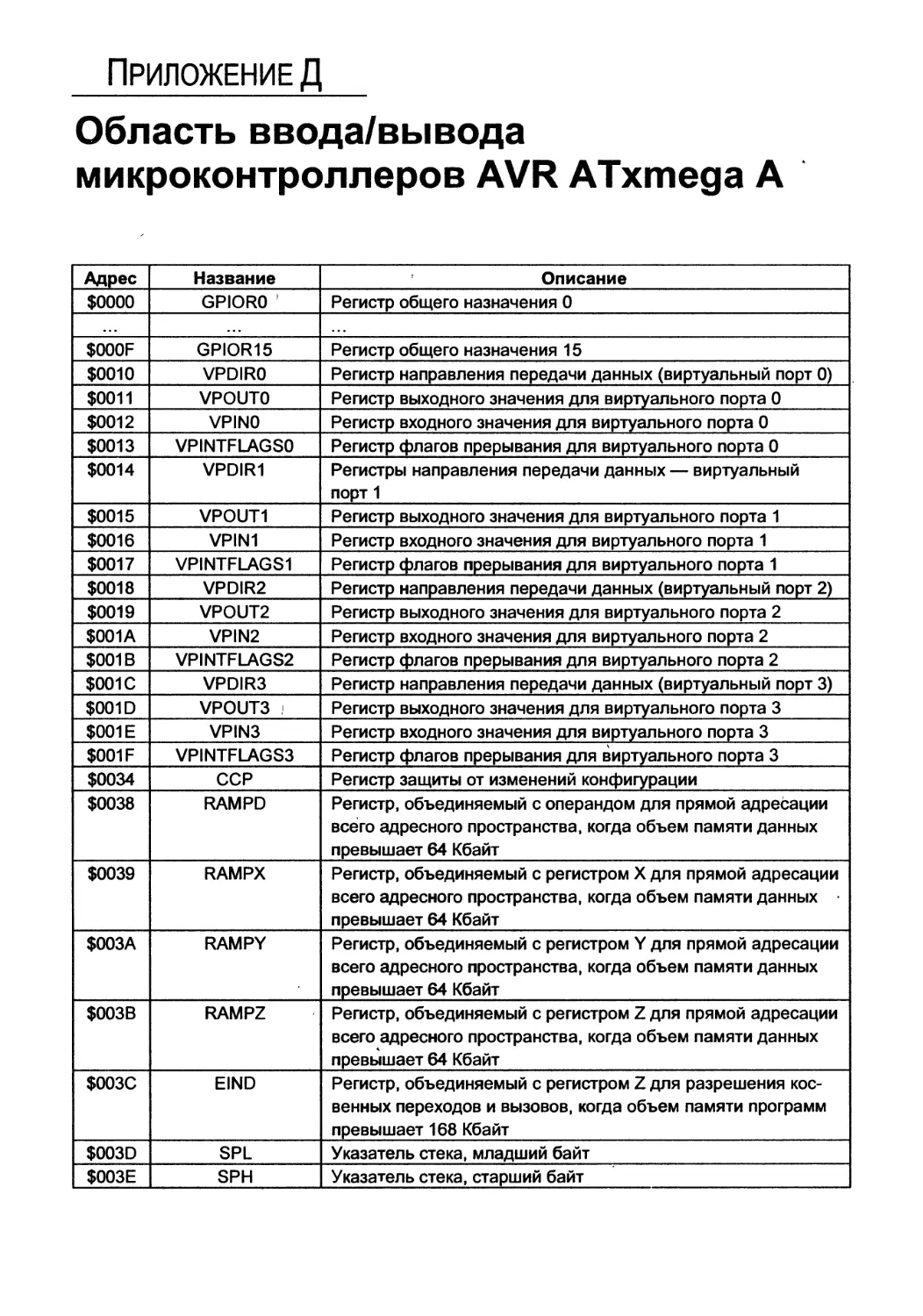

Приложение Д. Область ввода/вывода микроконтроллеров

AVR ATxmega а...............................................519

Список литературы.........................................532

Содержимое прилагаемого к книге компакт-диска.............533

Предисловие ко 2-му изданию

13

Предисловие ко 2-му изданию

Второе издание книги “Программирование на языке С для AVR и PIC микро-

контроллеров”, по сравнению с первым, претерпело ряд существенных изменений

и дополнений:

• в описании восьмиразрядной архитектуры микроконтроллеров AVR и PIC были

учтены особенности современных устройств от компаний Atmel и Microchip;

• рассмотрено новое семейство микроконтроллеров AVR ATxmega;

• кратко затронуты основные аспекты новых технологий PIC24 и PIC32;

• кроме компилятора WinAVR, для микроконтроллеров AVR рассмотрена среда

разработки CodeVisionAVR;

• дано описание современной версии среды разработки CCS-PICC;

• кроме компилятора CCS-PICC, для микроконтроллеров PIC рассмотрена среда

разработки mikroC, а также — новые компиляторы СЗО и С32, рассчитанные на

16-разрядную технологию PIC24 и 32-разрядную PIC32, соответственно;

• кратко затронуты разновидности программаторов для AVR и PIC;

• перечислены основные библиотечные функции и макроопределения языка С

компиляторов WinAVR, CodeVisionAVR, CCS-PICC и mikroC;

• даны примеры программ для всех рассмотренных в книге компиляторов;

• рассмотрена система команд микроконтроллеров ATxmega и PIC24.

Следует отметить, что с учетом критических отзывов, высказанных читателями

в отношении примеров программ, представленных в первом издании книги, соста-

вители постарались использовать проекты из достоверных источников. Со списком

литературы, использованной в процессе работы над этим изданием, можно ознако-

миться в конце книги. Кроме перечисленных первоисточников, в работе над мате-

риалом также использовались официальные документы Atmel и Microchip.

14

Введение

Однокристальные микроконтроллеры находят широкое применение в самых

разнообразных сферах: от измерительных приборов, фотоаппаратов и видеокамер,

принтеров, сканеров и копировальных аппаратов до изделий электронных развлече-

ний и всевозможной домашней техники.

Со времени появления первых микропроцессоров в 1970-х годах их сложность

постоянно возрастала за счет появления новых аппаратных решений и добавления

новых команд, предназначенных для решения новых задач. Так постепенно сложи-

лась архитектура, получившая впоследствии название CISC (Complex Instruction Set

Computers — компьютеры co сложным набором команд). В дальнейшем обозначи-

лось и нашло активное развитие еще одно направление: архитектура RISC (Reduced

Instruction Set Computers — компьютеры с сокращенным набором команд). Именно

к этой архитектуре относятся микроконтроллеры AVR от компаний Atmel и PIC от

компании Microchip, которым посвящена эта книга.

На заре возникновения микропроцессоров разработка программного обеспече-

ния происходила исключительно на том или ином языке ассемблера, ориентирован-

ном на конкретное устройство. По сути, такие языки представляли собой символь-

ные мнемоники соответствующих машинных кодов, а перевод мнемоники в машин-

ный код выполнялся транслятором. Однако главный недостаток ассемблерных язы-

ков заключается в том, что каждый из них привязан к конкретному типу устройств

и логике его работы. Кроме того, ассемблер сложен в освоении, что требует доста-

точно больших усилий для его изучения, которые, к тому же, оказываются потра-

ченными впустую, если впоследствии потребуется перейти на использование мик-

роконтроллеров других производителей.

Язык С, являясь языком высокого уровня, лишен подобных недостатков и мо-

жет использоваться для программирования любого микропроцессора, для которого

есть компилятор с языка С. В языке С все низкоуровневые операции, выполняемые

компьютерами, представлены в виде абстрактных конструкций, позволяющих раз-

работчикам сосредоточиться на программировании одной лишь логики, не заботясь

о машинном коде. Изучив язык С, можно легко переходить от одного семейства

микроконтроллеров к другому, тратя гораздо меньше времени на разработку.

В этой книге рассмотрены основы программирования на языке С микрокон-

троллеров AVR с использованием компиляторов WinAVR и CodeVisionAVR, а так-

же микроконтроллеров PIC с использованием компиляторов CCS-PICC, C3O/32

и mikroC. Надеемся, представленные здесь программные проекты помогут читателю

быстро и легко освоить азы программирование микроконтроллеров для конкретных

областей применения.

Желаем успехов в освоении вселенной под названием “Программирование мик-

роконтроллеров”. Надеемся, эта книга станет хорошим подспорьем в преодолении

нелегкого пути проб и ошибок.

Через тернии к звездам...

ЧАСТЬ I

Архитектура

микроконтроллеров

AVR

Глава 1

Восьмиразрядные микроконтроллеры

AVR

Все восьмиразрядные микроконтроллеры AVR спроектированы для работы

в составе очень производительной, маломощной архитектуры RISC. Микропроцес-

соры первого поколения обладали жестко “прошитой” логикой декодирования ко-

манд. В то время технология создания запоминающих устройств сильно “хромала”

по сравнению с технологией изготовления процессоров, т.е. более скоростным про-

цессорам приходилось долго ожидать считывания следующей команды для декоди-

рования из медленнодействующего запоминающего устройства. Поэтому, с целью

эффективного использования этого периода ожидания, возникла идея заполнить

время до поступления следующей команды.

В результате возникли команды, которые выполняли последовательно несколь-

ко внутрипроцессорных операций до тех пор, пока не поступала следующая внеш-

няя команда. Так появились процессоры CISC (Complex Instruction Set Computer —

компьютер co сложным набором команд). Типичными представителями этой архи-

тектуры процессоров являются семейства 80x86 и процессор Pentium компании Intel

или семейства 680x0 компании Motorola.

Практически все процессоры CISC работают по принципу микропрограммиро-

вания, т.е. каждая машинная команда последовательно обрабатывается микропро-

граммой, которая выполняется внутри кристалла процессора. Однако, если'взгля-

нуть на существующие программы через призму статистики, то обнаружится, что из

большого набора команд процессоров CISC (у некоторых типов — свыше 300) ис-

пользуется только небольшая, постоянно повторяющаяся часть в размере около 20

процентов. В дополнение к этому, комплексную программу можно зачастую заме-

нить несколькими эффективными командами, которые в состоянии справиться

с поставленной задачей быстрее.

Со временем изготовителям модулей памяти удалось резко-сократить время

доступа, в результате чего в середине 1980-х годов произошел возврат “к истокам”,

и была разработана архитектура RISC. Возникли компьютеры с сокращенным набо-

ром команд, у которых команды, как и в процессорах первых поколений, снова де-

кодировались посредством “жесткой прошивки”.

Перечислим характерные особенности архитектуры RISC:

• как следует из самого названия, самой примечательной особенностью является

ограниченное количество эффективных команд;

• отсутствие классического накапливающего сумматора в пользу большего числа

равноправных рабочих регистров;

• организация диапазонов памяти по Гарвардской модели;

• единый интерфейс с запоминающими устройствами за счет исключительного

применения команд вида “Загрузка/Сохранение”;

17

• обработка почти всех команд в течение единственного машинного такта;

• оптимизация аппаратного обеспечения и набора команд с целью применения

программирования на языках высокого уровня.

Поначалу использование архитектуры RISC было ограничено мощными ком-

пьютерами, выступающими в роли рабочих станций, однако вскоре были открыты

преимущества этой архитектуры для однокристальных микроконтроллеров, что до-

казывают устройства AVR компании Atmel.

Представители семейства AVR обладают ограниченным набором высокоэффек-

тивных команд (от 89 до 135, в зависимости от модели). Благодаря особой архитек-

туре микропроцессоров AVR, исключен ярко выраженный недостаток обычных

процессоров, у которых все арифметические и логические операции выполняются

исключительно в так называемом накапливающем сумматоре. Вследствие этого, как

правило, после завершения собственно вычислительных операций требуются опе-

рации обращения к вспомогательным регистрам или промежуточным запоминаю-

щим устройствам. У микроконтроллеров AVR этот недостаток отсутствует, по-

скольку в вычислениях, кроме накапливающего сумматора, задействованы 32 рав-

ноправных рабочих регистра, напрямую связанных с арифметико-логическим уст-

ройством (АЛУ).

Микроконтроллеры AVR работают по Гарвардской архитектуре, что подразу-

мевает разделение памяти для программ и данных. Они используют одноступенча-

тую конвейерную обработку. Это означает, что во время выполнения команды вы-

полняется загрузка следующей команды из памяти программ (рис. 1.1). Благодаря

этому, достигается возможность выполнения команды в течение одного тактового

цикла.

Рис. 1.1. Конвейерная обработка при выборке и выполнении команды в 8-разрядных

микроконтроллерах AVR

Первая команда программы выполняется на один тактовый цикл дольше, чем та

же команда в другом месте программы, поскольку в этом случае выборка не может

быть осуществлена параллельно с выполнением предыдущей команды.

В микроконтроллерах AVR используются несколько команд загрузки/сохране-

ния, с помощью которых к переменным и константам можно обратиться в различ-

ных режимах адресации.

У большинства обычных процессоров и контроллеров такт, сгенерированный

кварцевым осциллятором, делится на заранее заданный коэффициент для получения

собственно системного такта. Так, например, в контроллере 8051, работающем

с частотой кварца 12 МГц, при внутреннем коэффициенте деления минимальное

18

Глава 1. Восьмиразрядные микроконтроллеры AVR

время выполнения команд составляет всего лишь одну секунду, причем “минималь-

ное время” в данном случае подразумевает, что для выполнения некоторого количе-

ства команд потребуется больше времени. Однако в случае с микроконтроллерами

AVR такого не происходит. В них действительно почти все команды выполняются

в течение одного периода частоты кварцевого генератора, что, например, при мак-

симально допустимой частоте 12 МГц означает всего лишь 83,33 нс. Другими сло-

вами, достигается быстродействие до 12 MIPS (Million Instructions Per Second),

т.е. 12 миллионов выполненных команд в течение одной секунды! И, за немногими

исключениями, микроконтроллеры AVR действительно обрабатывают любую ко-

манду в течение единственного системного такта.

После того как в однокристальных микроконтроллерах для выполнения про-

грамм все больше начали использоваться языки высокого уровня (прежде всего,

язык программирования С), архитектура AVR была оптимизирована для эффектив-

ного взаимодействия аппаратного и программного обеспечения, написанного на

языках высокого уровня. К примеру, микроконтроллеры AVR специально для рабо-

ты с указателями предоставляют в распоряжение программиста команды с функ-

циями автоматического инкремента и декремента.

Семейства восьмиразрядных микроконтроллеров AVR

Компания Atmel предоставляет обширный набор восьмиразрядных микрокон-

троллеров AVR, разбитых на несколько семейств в соответствии с их характеристи-

ками и областью применения. Рассмотрим основные семейства:

• AT90S — “классические” микроконтроллеры AVR, которые в данное время

компанией Atmel для использования не рекомендуются, и заменимы другими,

более современными устройствами:

► AT90S1200 и AT90S2313 — на ATtiny2313;

► AT90S2323 и AT90S2343 — на ATtiny25;

► AT90S4433 — на ATmega8;

► AT90S4414 и AT90S8515 — на ATmega8515;

► AT90S8535 — на ATmega8535;

• ATtiny — привлекательные по цене микроконтроллеры с урезанным количест-

вом каналов ввода-вывода и уменьшенной памятью, что позволяет снизить по-

требление энергии и размеры корпуса;

• ATmega — высокопроизводительные устройства с достаточным объемом памя-

ти и набором каналов ввода-вывода, что позволяет применять йх в самых раз-

нообразных сферах;

• ATxmega — новое семейство микроконтроллеров AVR с расширенными ресур-

сами и возможностями, наподобие контроллера прямого доступа к памяти, сис-

темы обработки событий, высокоскоростных ЦАП и АЦП и др.

Компания Atmel предоставляет и другие семейства микроконтроллеров AVR,

ориентированные на какие-либо специфические задачи: применение в автомобилях,

управление ЖК-дисплеями и осветительными приборами, организация подключе-

ний по интерфейсу CAN и USB и др. Хотя все эти сферы, безусловно, интересны,

рассмотрение подобных устройств выходит за тематические рамки данной главы,

посвященной только общим архитектурным аспектам микроконтроллеров AVR. За

дополнительной информации обращайтесь к специализированным изданиям или на

Web-сайт компании Atmel (www. atmel. com).

Отладочная плата

19

В этой главе мы рассмотрим общие аспекты архитектуры семейств AT90S, АТ-

tiny и AT mega, а в следующей — особенности нового семейства ATxmega микро-

контроллеров AVR.

Отладочная плата

Сам по себе микроконтроллер ничего не может. Он требует определенной схе-

мы базового монтажа, которая обычно состоит из кварцевого генератора и несколь-

ких конденсаторов. Без этого микроконтроллер просто не начнет выполнять про-

грамму, которую, впрочем, тоже необходимо каким-то образом в него записать. От-

сюда возникает потребность в каком-либо программаторе — специальном адаптере

для переноса исполняемого кода с компьютера в память микроконтроллера. Кроме

того, если требуется использовать последовательный интерфейс, на арену выходит

преобразователь логического уровня (например, МАХ232) и соответствующий

разъем (например, RS232).

Таким образом, у нас есть две возможности:

• приобрести по отдельности все компоненты для базового монтажа и подключе-

ния программатора и собрать все вручную;

• обзавестись готовой отладочной платой, что гораздо проще.

В типичную отладочную плату уже интегрирован интерфейс программирова-

ния, несколько кнопок и светодиодов. Кроме того, такие платы зачастую реализуют

какой-либо последовательный интерфейс.

Платы STK500 и STK600

Компания Atmel предлагает хорошо продуманные, приемлемые по цене отла-

дочные платы (например, STK500 и STK600) и множество дополнительных модулей

расширения к ним. Так, плата STK500 (рис. 1.2) предоставляет:

• разъемы для установки процессоров в корпусах DIP с числом выводов 8, 20, 28

и 40;

• низковольтное программирование через интерфейс SPI (в том числе микрокон-

троллеров, установленных во внешнем устройстве);

• высоковольтное программирование (с доступом к любым разрядам конфигура-

ции);

• встроенный источник питания: вход — постоянное напряжение 10.. 15 В; 0,5 А;

выход — устанавливается из среды программирования (по умолчанию — 5 В);

• встроенный источник опорного напряжения;

• тактовый генератор, частота которого устанавливается из среды программиро-

вания (до 3,68 МГц) или внешним кварцевым резонатором;

• формирователь сигналов интерфейса RS232;

• восемь кнопок и светодиодов;

• связь с ПК по интерфейсу RS232.

Вместе с платой поставляются кабели для подключения. Все порты процессо-

ров, кнопки и светодиоды выведены на разъемы и могут быть соединены в произ-

вольном порядке. Плата STK500 поддерживает все микроконтроллеры AVR се-

20

Глава 1. Восьмиразрядные микроконтроллеры AVR

мейств ATtiny и ATmega, кроме ATmega 103. Возможно программирование любых

микроконтроллеров AVR, установленных во внешнем устройстве.

Рис. 1.2. Отладочная плата STK500

Возможности новой отладочной платы STK.600 (рис. 1.3) гораздо шире:

• стабилизированный источник питания с программно управляемым выходным

напряжением;

• преобразователи уровней сигналов RS232, LIN и CAN;

• разъемы интерфейсов USB (Device), mini-USB (host), RS-232, CAN;

• программно управляемый источник опорного напряжения;

• восемь кнопок и светодиодов;

• источник тактовых сигналов с регулируемой частотой до 32 МГц;

• связь с ПК п<? интерфейсу USB.

Рис. 1.3. Отладочная плата STK600

Вместе с платой поставляются кабели для подключения. Плата STK600 под-

держивает все микроконтроллеры AVR семейств ATtiny, ATmega, ATxmega, а так-

же — новые 32-разрядные устройства семейства AVR32 UC3 (в этой книге не рас-

сматриваются).

Существуют и другие отладочные платы для микроконтроллеров AVR (как от

компании Atmel, так и от сторонних разработчиков), перечислять которые мы здесь

не будем. Другими словами, предоставляем право выбора подходящего комплекта

самому читателю.

Схема базового монтажа

21

Схема базового монтажа

Любой микроконтроллер AVR должен быть включен в некоторую базовую схе-

му, иначе он просто не будет работать. Пример такой схемы для устройства АТ-

mega8 показан на рис. 1.4.

Рис. 1.4. Схема базового монтажа для микроконтроллера АТтедав

В данном случае используются следующие компоненты:

• конденсатор С1 — 100 нФ;

• конденсаторы С7 и С8 — по 22 пФ;

• кварц на 3,686 МГц (или на 4, 8, 16 МГц).

Микроконтроллер АТтеда8, как и все другие, по умолчанию сконфигурирован на работу от

внутреннего тактового генератора, из-за чего внешний кварц он просто проигнорирует. Для

переключения на внешнее тактирование необходимо установить соответствующие конфигу-

рационные разряды предохранения (fuse bits), которые рассматривают позже в этой же главе.

Питание микроконтроллера можно обеспечить напрямую от сети через стаби-

лизирующий сетевой блок или (что более удобно и безопасно) — с помощью любо-

го блока питания на 9.. 12 В. Для этого потребуется стабилизатор напряжения, кото-

рый можно легко включить в базовую схему согласно рис. 1.5.

сз

С2

& OW -

I £1 ..

ей

Рис. 1.5. Схема включения стабилизатора напряжения

22

Глава 1. Восьмиразрядные микроконтроллеры AVR

В данном случае используются следующие компоненты:

• IC1 —стабилизатор напряжения 5 В (7805);

• электролитический конденсатор С1 — 10 мкФ (соблюдайте правильную поляр-

ность!);

• конденсаторы С2 и СЗ — на 100 нФ;

• диод D1 — 1N4001.

Этот стабилизатор преобразовывает входное напряжение в диапазоне 9.. 12 В

в требуемое микроконтроллерам AVR напряжение питания 5 В. Кроме того, данная

схема отчасти предохраняет устройство от возможных перенапряжений.

Структура микроконтроллеров AVR

В общем случае структура всех восьмиразрядных микроконтроллеров AVR со-

ответствует схеме, показанной на рис. 1.6.

Рис. 1.6. Обобщенная структура восьмиразрядных микроконтроллеров AVR

Процессорное ядро включает в себя систему управления (счетчик команд

и схема декодирования команд, извлекаемых из памяти программ) и операционное

устройство, отвечающее за выполнение арифметических и логических операций.

Операционное устройство, как правило, состоит из арифметико-логического уст-

ройства (АЛУ), накапливающего сумматора и нескольких вспомогательных регист-

ров. В классической программе почти половина всех команд — это команды пере-

сылки для передачи данных от вспомогательных регистров к накапливающему сум-

матору и обратно. В микроконтроллерах AVR накапливающий сумматор становится

не столь критически важным, благодаря применению 32-х рабочих регистров, свя-

занных с блоком АЛУ. В результате арифметические и логические операции могут

быть выполнены в течение единственного такта.

Операции АЛУ можно разделить на три основные категории: арифметические,

логические и поразрядные. Каждой из этих категорий соответствуют мощные ко-

манды. Новые микроконтроллеры AVR имеют также аппаратные умножители в ари-

фметическом блоке АЛУ.

Организация памяти

В запоминающих устройствах, соответствующих классической концепции фон

Неймана, данные и команды хранятся в одной памяти. В противоположность этому,

память по Гарвардской архитектуре, используемой в восьмиразрядных микрокон-

троллерах AVR, состоит из нескольких компонентов. В данном случае разделены

память команд и память данных, т.е. обращение к командам осуществляется незави-

симо от доступа к данным.

Структура микроконтроллеров AVR

23

В микроконтроллерах AVR отдельные сегменты памяти отличаются также

и физической реализацией.

• Внутренняя память для энергозависимых данных (т.е. данных, которые будут

потеряны после отключения рабочего напряжения) представляет собой статиче-

скую память RAM (SRAM). Ее преимущество заключается в том, что отпадает

всякая необходимость во внутренней регенерации как в случае с некоторыми

другими процессорами, которые используют динамическую память. По этой

причине микроконтроллеры AVR могут работать с тактами вплоть до 0 Гц.

В дополнение к этому, некоторые микроконтроллеры AVR для увеличения объ-

ема обрабатываемых данных могут работать с подключаемой внешней памятью

SRAM. Для этого, однако, приходится жертвовать выводами портов.

• Для данных, которые должны сохраниться после отключения рабочего напря-

жения, в распоряжении имеется память EEPROM (Electrically EPROM — элек-

трически стираемое ППЗУ), данные в которую можно записывать непосредст-

венно во время выполнения программы. Для области EEPROM также не обяза-

тельно программирующее устройство.

• Память программ реализована на основе программируемой и электрически сти-

раемой Flash-технологии. Во всех восьмиразрядных микроконтроллерах AVR

она — 16-разрядная (двухбайтная) и всегда встроена в кристалл. Расширение

памяти программ с помощью блоков EPROM или Flash невозможно.

Память SRAM

Статическое ОЗУ (SRAM) микроконтроллеров AVR семейств AT90S, ATtiny

и ATmega представляет собой блок со сквозной адресацией, состоящий из двух или

трех (в зависимости от модели микроконтроллера) подобластей (рис. 1.7). Самый

верхний адрес внутренней памяти SRAM, обозначенный на рис. 1.7 как “RamEnd”,

зависит от построения ОЗУ соответствующего микроконтроллера. Размеры SRAM

для различных восьмиразрядных микроконтроллеров AVR показаны в табл. 1.1.

В ряде микроконтроллеров можно увеличивать пространство памяти SRAM пу-

тем подключения внешних блоков вплоть до 64 Кбайт, однако для этого приходится

пожертвовать выводами портов А и С, которые в таком случае применяются в каче-

стве шин передачи данных и адресов.

Таблица 1.1. Размеры памяти SRAM восьмиразрядных микроконтроллеров AVR

Микроконтроллер Объем памяти SRAM, байт Адрес “RamEnd”

AT90S1200 — $005F

AT90S2313 128 $00DF

AT90S2323 128 $00DF

AT90S2343 128 $00DF

AT90S4414 256 $015F

AT90S4433 128 $00DF

AT90S8515 512 $025F

AT90S8535 512 $025F

ATtiny 11 — $005F

ATtiny 12 — $005F

ATtiny 13А 64 $009F

ATtiny 15L — $005F

ATtiny2313 128 $00DF

Глава 1. Восьмиразрядные микроконтроллеры AVR

Таблица 1.1. Продолжение

Микроконтроллер Объем памяти SRAM, байт Адрес “RamEnd”

ATtiny24 128 $00DF

ATtiny25 128 $00DF

ATtiny26 128 $00DF

ATtiny261 128 $00DF

ATtiny28L 128 $00DF

ATtiny44A 256 $015F

ATtiny45 256 $015F

ATtiny461 256 $015F

ATtiny48 256 , $015F

ATtiny84 512 $025F

ATtiny85 512 $025F

ATtiny861 512 $025F

ATtiny88 512 $025F

ATmega128 4096 $105F

ATmega1280 8192 $205F

ATmega1281 8192 $205F

ATmega1284P 16384 $405F

ATmega16 1024 $045F.

ATmega16A 1024 $045F

ATmega162 1024 $045F

ATmega164P 1024 $045F

ATmega165P 1024 $045F

ATmega168 1024 $045F

ATmega168P 1024 $045F

ATmega169 1024 $045F

ATmega2560 8192 $205F

ATmega2561 8192 $205F

ATmega32A 2048 $085F

ATmega324PA 2048 $085F

ATmega325 2048 $085F

ATmega325P 2048 $085F

ATmega3250 2048 $085F

ATniega3250P 2048 $085F

ATmega328P 2048 $085F

ATmega48PA 512 $025F

ATmega64 4096 $105F

ATmega640 8192 $205F

ATmega644 4096 $105F

ATmega644P 4096 $105F

ATmega645 4096 $105F

ATmega6450 4096 $105F

ATmega8 1024 $045F

ATmega8515 512 $025F

ATmega8535 512 $025F

ATmega88PA 1024 $045F

Структура микроконтроллеров AVR

25

(б

ш

1

ш

ш

co

о

Ф

$3F

$ЗЕ

$3D

$ЗС

$ЗВ

SREG

_______SEU________1

SPL t •>

(зарезервировано)

QI ms к 2

Адреса

0 SRAM

$FFFF

"т- Внешнее ОЗУ *)Т- —

RamEnd+1

Ram End

m

о

₽•

$04

$03

$02

$01

$00

(зарезервировано;

(зарезервировано

зарезервировано

зарезервировано

^зарезервировано'

Внутреннее ОЗУ *)

$1F.

$1Е

$1D

$1С

$1В

$1А

$19

r 31 =£er Z старший.-)

гЗО =Per Z младший

r29 = Per.Y старший»)

г 28 =Per.Y младший»)

г 27 = Per X старший»)

г 26 =Per X младший»)

Per, вв/выв 63

Per. ввУвыв 62

Per, вв/выв. 61

Область ввода/вывода

Per. вв./выв 1

Per. ввУвыв. 0

г 25

Ill

$060

$05F

$020

$01F

$04

$03

$02

$01

$00

Область регистров

Х4.

£2

И

Ы

г 1

г0

1000

ф

«

о

ф

7

1

*) В некоторых микроконтроллерах AVR отсутствует

Рис. 1.7. Организация памяти SRAM микроконтроллеров AVR семейств AT90S, ATtiny и ATmega

Регистровый файл

Самая нижняя область памяти SRAM образует регистровый файл с 32 рабочими

регистрами, которые все связаны с АЛУ и доступ к которым может быть выполнен

в течение единственного такта системной синхронизации. Это означает, что за вре-

мя такта в арифметико-логическое устройство вводятся два операнда из регистрово-

го файла, выполняется операция, а результат запоминается в регистре назначения

(рис. 3.3).

Такт системной

синхронизации ф

Общее время выполнения

команды

Обращение АЛУ к

регистру-операнду

Выполнение операции АЛУ

Сохранение результата

в памяти

Рис. 1.8. Диаграмма выполнения однотактной операции

Хотя рабочие регистры с физической точки зрения не являются ячейками памя-

ти, им, как показано на рис. 1.7, поставлены в соответствие 32 самых нижних адреса

от $00 до $1F в памяти SRAM, поэтому их можно адресовать как обычные ячейки.

26

Глава 1. Восьмиразрядные микроконтроллеры AVR

Регистры двойной длины X, Y и Z

Шесть рабочих регистров от R26 до R31 могут применяться в качестве регист-

ров двойной длины X, Y и Z шириной 16 бит с возможностью доступа к обеим по-

ловинам (рис. 1.9).

15 0

Регистр X |7 0 |7 _0j

15 R27 ($1В) R26 ($1A) 0

Регистр Y lz_ 0|7 _oj

15 R29 ($1D) R28($1C) 0

Регистр Z U_ 0 |7 —ll

R31 ($1F) R30 ($1E)

Рис. 1.9. Структура регистров двойной длины X, Y и Z

Благодаря специальным командам, их можно использовать в качестве указате-

лей, что при косвенной адресации позволяет очень эффективно обращаться

к ячейкам памяти SRAM. Дополнительно к этому, с помощью регистра Z из памяти

программ можно извлекать восьмиразрядные константы.

Область ввода/вывода семейств AT90S, ATmega и ATtiny

В этой области памяти SRAM размещены все регистры для программирования,

управления и сигнализации о всех периферийных функциях восьмиразрядных мик-

роконтроллеров AVR. Типичный их набор для микроконтроллеров семейств AT90S,

ATmega и ATtiny перечислен в табл. 1.2. В некоторых моделях часть указанных

в табл. 1.2 регистров может отсутствовать или размещаться в области ввода/вывода

по другим адресам. Кроме того, в современных микроконтроллерах область вво-

да/вывода может превышать адрес $5F в пространстве SRAM. Например, в ATmega-

640 она завершается адресом 0x1 FF. В любом случае, всегда сверяйтесь с техниче-

ским описанием конкретного микроконтроллера.

Таблица 1.2. Область ввода/вывода восьмиразрядных микроконтроллеров AVR

Адрес Название Функция

$3F ($5F) SREG Регистр состояния

$3E ($5E) SPH Указатель стека, старший байт

$3D ($5D) SPL Указатель стека, младший байт

$30 ($5C) OCRO Регистр сравнения на выходе таймера/счетчика Т/СО

$3B ($5B) GIMSKnon GICR Общий регистр маски прерываний или общий регистр управле- ния прерываниями

$3A ($5A) GIFR Общий регистр флагов прерываний

$39 ($59) TIMSK Регистр маски прерываний таймера/счетчика

$38 ($58) TIFR Регистр флагов прерываний от таймеров/счетчиков

$37 ($57) SPMCR Регистр управления операциями начальной загрузки из памяти программ

$36 ($56) TWCR Регистр управления двухпроводным интерфейсом l2C (TWI)

$35 ($55) MCUCR Регистр общего управления микроконтроллером

$34 ($54) MCUSR (MCUCSR) Регистр, содержащий информацию об источнике сброса микро- контроллера

$33 ($53) TCCRO Регистр управления таймером/ счетчиком Т/СО

$32 ($52) TCNTO Счетный регистр таймера/счетчика Т/СО (8 бит)

$31 ($51) OSCCAt Регистр калибровки осциллятора

$30 ($50) SFIOR Регистр специальных функций ввода-вывода

$2F ($4F) TCCR1A Регистр управления А таймера/счетчика Т/С1

Структура микроконтроллеров AVR

27

Таблица 1.2. Продолжение

Адрес Название Функция

$2Е ($4Е) TCCR1B Регистр управления В таймера/счетчика Т/С1

$2D($4D) TCNT1H Счетный регистр Т/С1, старший байт

$2С ($4С) TCNT1L Счетный регистр Т/С1, младший байт

$2В($4В) OCR1AH Регистр сравнения А таймера/счетчика Т/С1, старший байт

$2А ($4А) OCR1AL Регистр сравнения А таймера/счетчика Т/С1, младший байт

$29 ($49) OCR1BH Регистр сравнения В таймера/счетчика Т/С1, старший байт

$28 ($48) OCR1BL Регистр сравнения В таймера/счетчика Т/С1, младший байт

$27 ($47) ICR1H Регистр захвата на входе таймера/счетчика Т/С1. младший байт

$26 ($46) ICR1L Регистр захвата на входе таймера/счетчика Т/С1, старший байт

$25 ($45) TCCR2 Регистр управления таймера/счетчика Т/С2

$24 ($44) TCNT2 Счетный регистр таймера/счетчика Т/С2

$23 ($43) OCR? Регистр сравнения на выходе таймера/счетчика Т/С2

$22 ($42) ASSR Регистр состояния асинхронного режима работы таймера/счет- чика Т/С2

$21 ($41) WDTCR Регистр управления сторожевым таймером

$20 ($40) UBRRH или UCSRC Регистр скорости передачи данных через USART (старший байт) или регистр управления и состояния USART

$1F($3F) EEARH Регистр адреса EEPROM, старший байт

$1Е($ЗЕ) EEAR(L) Регистр адреса EEPROM, младший байт

$1D($3D) EEDR Регистр данных EEPROM

$1С ($ЗС) EECR Регистр управления EEPROM

$1В($ЗВ) PORTA Регистр данных порта А

$1А ($ЗА) DDRA Регистр направления передачи данных порта А

$19 ($39) PINA Выводы порта А

$18 ($38) PORTB Регистр данных порта В

$17 ($37) DDRB Регистр направления передачи данных порта В

$16 ($36) PINB Выводы порта В

$15 ($35) PORTC Регистр данных порта С

$14 ($34) DDRC Регистр направления передачи данных порта С

$13 ($33) PINC Выводы порта С

$12 ($32) PORTD Регистр данных порта D

$11 ($31) DDRD Регистр направления передачи данных порта D

$10 ($30) PIND Выводы порта D

$0F ($2F) SPDR или USIDR Регистр ввода/вывода данных через интерфейс SPI или регистр данных универсального последовательного интерфейса

$0Е ($2Е) SPSR или USISR Регистр состояния интерфейса SPI или регистр состояния уни- версального последовательного интерфейса

$0D ($2D) SPCR или USICR Регистр управления интерфейсом SPI или регистр управления универсальным последовательным интерфейсом

$0С ($2С) UDR Регистр данных UART

$0В ($2В) USR или UCSRA Регистр состояния UART или регистр А управления и состояния USART 7

$0А ($2А) UCR или UCSRB Регистр управления UART или регистр В управления и состоя- ния USART

$09 ($29) UBRR или UBRRL Регистр скорости передачи данных через UART или регистр ско- рости передачи данных через USART (младший байт)

$08 ($28) ACSR Регистр управления и состояния аналогового компаратора

$07 ($27) ADMUX Регистр выбора мультиплексора АЦП

$06 ($26) ADCSR(A) Регистр (А) управления и состояния АЦП

$05 ($25) ADCH Регистр данных АЦП, старший байт

$04 ($24) ADCL Регистр данных АЦП, младший байт

$03 ($23) TWDR Регистр данных интерфейса l2C (TWI)

28

Глава 1. Восьмиразрядные микроконтрЬллеры AVR

Таблица 1.2. Окончание

Адрес Название Функция

$02 ($22) TWAR Регистр адреса (подчиненного устройства) для передачи данных по интерфейсу гС (TWI)

$01 ($21) TWSR Регистр состояния интерфейса lzC (TWI)

$00 ($20) TWBR Регистр скорости передачи данных по интерфейсу lzC (TWI)

ПРИМЕЧАНИЕ

Li 1»:» kt А .1к А >' 1 А. к. i »k A k k k kf a kkiikk' *» frrt kk tk if *k Art '«? k kVkkk; kkk'^kkkk kkk ?:.y. ik. .tk kk?:?kk k 1 kk?;?; ’Л ;k<

Ячейкам в области ввода/вывода назначены адреса с $00 по $3F, которые должны приме-

няться в случае использования специальных ассемблерных команд in, out, sbi, obi,

sbis и sbiс. Если регистр ввода/вывода адресуется как ячейка в памяти SRAM в целом, то

к адресу ввода/вывода необходимо добавить $20, Так, например, регистру состояния SREG

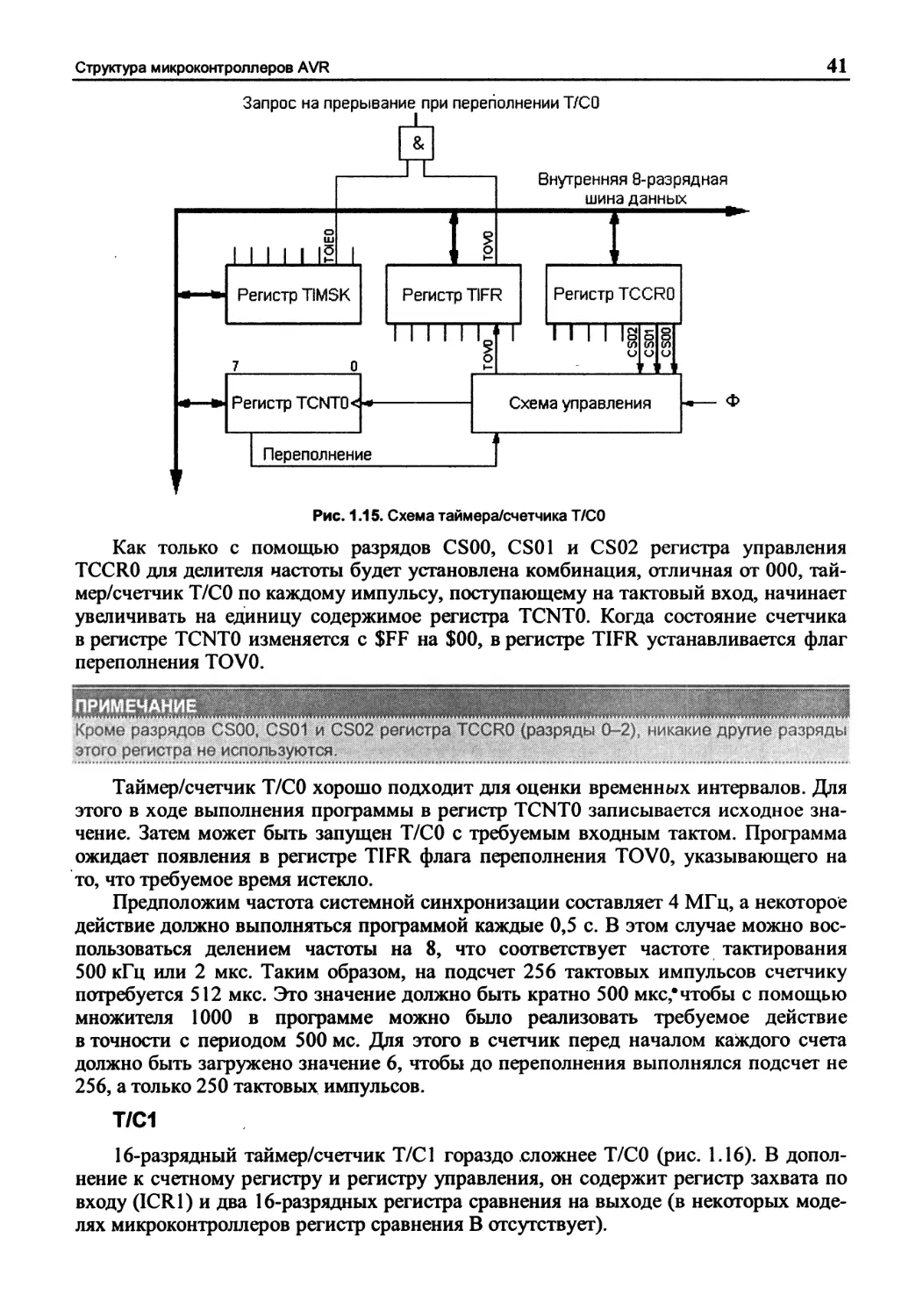

соответствует адрес $3F внутри области ввода/вывода и адрес $5F относительно всей памя-

ти SRAM.

Как видим, к регистрам ввода/вывода относятся регистры разрешения/запрета

отдельных прерываний, а также указатель стека, регистры состояния для указания

результатов арифметических и логических операций, регистры управления работой

многочисленных компонентов аппаратного обеспечения и периферии (порты, тай-

мер, UART/USART, интерфейсы SPI и I2C (TWI), аналоговый компаратор, стороже-

вой таймер, режимы пониженного энергопотребления), а также регистры для обра-

щения к памяти EEPROM.

Для доступа к регистрам ввода/вывода лучше всего использовать ассемблерные

команды ввода/вывода микроконтроллеров AVR: in и out. Команда оис выдает

один байт из одного из 32-х рабочих регистров в регистр ввода/вывода, а команда

in считывает байт из одного регистра ввода/вывода в один из 32-х рабочих регист-

ров.

У регистров ввода/вывода в области с $00 по $1F ($20..$3F) отдельные разряды

могут быть изменены напрямую с помощью ассемблерных команд sbi и cbi. Кро-

ме того, содержимое отдельных разрядов этих регистров может быть напрямую оп-

рошено с помощью ассемблерных команд sbis и sbiс (Система команд микрокон-

троллеров AVR рассматривается в приложении В).

Регистр состояния SREG

Регистр состояния SREG содержит разряды условий (флаги) микроконтролле-

ров AVR (рис. 1.10). Он располагается в области ввода/вывода по адресу $3F ($5F),

доступен для чтения и записи и после подачи сигнала сброса инициализируется ну-

лями.

Разряд 76543210

$3F($5F) I i |t|h|s|v|n|z|c|

Рис. 1.10. Регистр состояния SREG микроконтроллеров AVR

В микроконтроллерах AVR для обозначения результата выполнения операций

используются восемь различных разрядов условий. Все они могут быть проверены

с помощью ассемблерных команд, определяющих последующий ход выполнения

программы (например, brcs, brhc, brtc, brie и т.д.).

При входе в подпрограмму обработки прерывания рекомендуется сохранить ре-

гистр состояния и суова его восстановить при выходе для того, чтобы после возвра-

та в прерванную программу работать с корректными битами условий.

Значения отдельных разрядов условий (флагов) в микроконтроллерах AVR:

Структура микроконтроллеров AVR

29

• С —- указывает на переполнение (перенос) после выполнения арифметической

или логической операции;

• Z — всегда устанавливается в 1, если результат арифметической или логиче-

ской операции равен нулю, и обнуляется, если результат операции не равен ну-

лю;

• N — указывает на отрицательный результат после выполнения арифметической

или логической операции;

• V — флаг переполнения при вычислениях в дополнительных кодах (арифмети-

ка кодов с дополнением до двух); устанавливается в 1, если при выполнении

соответствующей операции происходит переполнение, в противном случае —

обнуляется;

• S — связь флагов N и V с помощью операции “Исключающее ИЛИ”; флаг знака

может применяться для определения фактического результата арифметической

операции;

• Н — указывает на переполнение в младшем полубайте (разряды 0...3 байта дан-

ных); устанавливается в 1, когда происходит перенос из младшего полубайта

в старший, в противном случае — обнуляется;

• Т — флаг копирования, предназначенный для свободного использования про-

граммистом (например, в качестве буфера);

• I — общее разрешение прерываний. Если прерывания должны быть разрешены,

то устанавливается в 1.

Регистр управления микроконтроллером MCUCR

Регистр MCUCR содержит разряды управления общими функциями микрокон-

троллера. Наряду с разрешением доступа к внешней памяти SRAM, он также управ-

ляет “спящим” режимом и характером срабатывания внешних прерываний. Регистр

MCUCR находится в области ввода/вывода ро адресу $35 ($55). Он доступен для

чтения и записи, а после подачи сигнала сброса инициализируется нулями.

Набор, обозначение и последовательность разрядов в этом регистре может от-

личаться в зависимости от модели микроконтроллера, поэтому рассмотрим их

в общем виде. Точные обозначения уточняйте по техническому описанию устройст-

ва.

• SRE (External SRAM Enable) — если этот разряд установлен в 1, то разрешен

доступ к внешней памяти SRAM (при наличии таковой);

• SRW (External SRAM Wait State) — если этот разряд установлен в 1, то в после-

довательность обращения к внешней памяти SRAM будет добавлено состояние

ожидания продолжительностью один системный такт. Если разряд SRW содер-

жит 0, то доступ к внешней памяти SRAM выполняется за два обычных такто-

вых цикла.

• SE (Sleep Enable) — этот разряд должен быть установлен в 1 для того, чтобы

сделать эффективной ассемблерную команду sleep. Если он содержит 0, то по-

сле выполнения команды sleep центральный процессор (ЦП) останется актив-

ным. Во избежание непреднамеренного перевода процессора в ждущий режим

или в режим пониженного энергопотребления непосредственно перед выполне-

нием команды sleep рекомендуется установить разряд SE в 1.

• SM (Sleep Mode) — выбор между различными состояниями пониженного энер-

гопотребления.

30

Глава 1. Восьмиразрядные микроконтроллеры AVR

• ISC11 и ISCIO (Interrupt Sense Control 1) — определяют способ активизации

обработки внешнего прерывания 1, когда в регистре SREG установлен флаг 1,

а в регистре GIMSK (GICR) — разряд INT1: по нарастающему или ниспадаю-

щему фронту сигнала, или же по уровню лог. 0 на выводе INT1. Возможные

комбинации ICS11 и ICS10 показаны в табл. 1.3. Если разряды ISC11 и ISC10

должны быть изменены, то вначале необходимо запретить прерывание 1, обну-

лив разряд INT1 в регистре GIMSK (GICR). В противном случае непреднаме-

• ренное изменение этих разрядов может привести к вызову внешнего прерыва-

ния 1.

Таблица 1.3. Выбор способа активизации прерывания INT1

ISC11 ISC10 Описание

0 0 Прерывание возникает по уровню лог. 0 на входе INT1

0 1 Эта комбинация в некоторых моделях микроконтроллеров AVR не исполь- зуется, в то время как в других означает прерывание по любому измене- нию логического уровня на входе INT1

1 0 Прерывание возникает по ниспадающему фронту сигнала на входе INT1

1 1 Прерывание возникает по нарастающему фронту сигнала на входе INT1

• ISC01 и ISCOO (Interrupt Sense Control 0) — устанавливают способ активизации

внешнего прерывания 0, когда в регистре SREG будет установлен флаг I, а в ре-

гистре GIMSK (GICR) — разряд INTO: по нарастающему или ниспадающему

фронту сигнала, или же по уровню лог. 0 на выводе INTO. Возможные комбина-

ции ICS01 и ICS00 показаны в табл. 1.4.

Таблица 1.4. Выбор способа активизации прерывания INTO

ISC01 ISC00 Описание

0 0 Прерывание возникает по уровню лог. 0 на входе INTO

0 1 Эта комбинация в некоторых моделях микроконтроллеров AVR не ис- пользуется, в то время как в других означает прерывание по любому из- менению логического уровня на входе INTO

1 0 Прерывание возникает по ниспадающему фронту сигнала на входе INTO

1 1. Прерывание возникает по нарастающему фронту сигнала на входе INTO

Если разряды ISC01 и ISC00 должны быть изменены, то сначала необходимо

запретить прерывание INTO, обнулив разряд INTO в регистре GIMSK (GICR).

В противном случае непреднамеренное изменение этих разрядов может привести

к вызову внешнего прерывания 0.

Внутренняя память SRAM

Данные и переменные, используемые в программах, как правило, хранятся во

внутренней памяти SRAM микроконтроллеров AVR (т.е. в области с адресами выше

$005F). К этим данным можно обращаться из программы прямо или косвенно.

В памяти SRAM также размещается стек (если только он не реализован аппаратно).

На рис. 1.11 символически показаны графики синхронизации при обращении

к внутренней памяти SRAM.

Внешняя память SRAM

Если объема внутренней памяти SRAM недостаточно, то в некоторых микро-

контроллерах AVR его можно увеличить до 64 Кбайт путем подключения внешних

Структура микроконтроллеров AVR

31

блоков памяти. Для этого в регистре MCUCR следует установить в 1 разряд SRE,

в результате чего порты А и С будут выступать в качестве шины адреса и шины

данных, а выводы 7 и 6 порта D — в качестве управляющих сигналов чтения /RD и,

соответственно, записи /WR для внешней памяти SRAM (рис. 1.12), независимо от

того, какие направления передачи данных установлены для этих портов в соответ-

ствующих регистрах направления передачи данных.

Такт системной

синхронизации Ф

Внутренняя шина адреса—

Внутренняя шина данных

Внутренний сигнал /RD

Чтение из

SRAM

Т1

АО п

<D£7

Запись в

SRAM

Т1

Т2

АО п

DO 7

X

Внутренний сигнал /WR

Рис. 1.11. Синхронизация при обращении к внутренней памяти SRAM

Рис. 1.12. Пример подключения внешнего блока памяти для расширения статической памяти SRAM

до 32 Кбайт

Дальнейшее обращение к внешней статической памяти может осуществляться

с помощью тех же команд, что и при обращении к внутренней памяти. При обраще-

32

Глава 1. Восьмиразрядные микроконтроллеры AVR

нии к адресам SRAM, которые находятся в области внутренней статической памяти,

передача данных выполняется автоматически как во внутреннюю память SRAM, так

и из нее, даже при установленном в 1 разряде SRE. В этом случае управляющие

сигналы чтения /RD и записи ZWR остаются неактивными на протяжении всего цик-

ла. Обращение к внешней памяти будет выполнено только тогда, когда адрес будет

больше, чем “RarnEnd”, а также если в регистре управления MCUCR будет установ-

лен в 1 разряд SRE.

На тот случай, если используемые внешние блоки статической памяти окажутся

недостаточно быстродействующими для циклов записи/чтения микроконтроллера

AVR, установив разряд SRW (разряд 6) в регистре MCUCR, можно активизировать

состояние ожидания. Благодаря введению этого дополнительного состояния дли-

тельностью в один такт системной синхронизации, длина сигналов передачи данных

и команд /RD и, соответственно, /WR увеличивается, чтобы предоставить достаточ-

но времени для передачи данных блокам памяти, работающим медленнее.

Благодаря чрезвычайно коротким маршрутам прохождения сигналов внутри

кристалла, обращение к внутренней памяти RAM в значительной степени более

свободно от сбоев, чем обращение к внешней памяти через шину. Если при этом

принять во внимание, что из-за подсоединения внешнего запоминающего устройст-

ва теряются 18 выводов, то следует тщательно взвешивать: действительно ли под-

соединение внешней памяти — это наилучшее решение для данного случая приме-

нения. Кроме того, многие современные восьмиразрядные микроконтроллеры пре-

доставляют довольно большие объемы внутренней памяти SRAM, поэтому при не-

хватке памяти в текущей модели, возможно, имеет смысл выбрать какую-либо дру-

гую модель AVR.

Стек

Стек служит для хранения адресов возврата при вызове подпрограмм, а также

для передачи параметров в подпрограммы. Кроме того, зачастую в стеке, как

в буфере, временно хранятся переменные и промежуточные результаты. Реализация

стека в разных моделях микроконтроллеров AVR может отличаться. Возможные ва-

рианты:

• стек размещается во внутренней или внешней памяти SRAM на выбор разра-

ботчика;

• стек всегда находится во внутренней памяти SRAM;

• аппаратный стек (например, в микроконтроллере AT90S1200). В этом.случае он

ограничен жестко заданным числом уровней. При выполнении ассемблерной

команды г call или при поступлении запроса на прерывание все адреса, вве-

денные в аппаратный стек, смещаются на один уровень вниз (адрес, помещен-

ный до этого на уровень 2, теряется, а находящийся на уровне 1 перемещается

на уровень 2; адрес, ранее записанный на уровне 0, будет перемещен на уровень

1). После этого соответствующий адрес возврата помещается на уровень 0 аппа-

ратного стека. При выходе из обычной подпрограммы или подпрограммы обра-

ботки прерывания адрес, находящийся на нулевом уровне, извлекается в счет-

чик команд как адрес возврата, и все уровни аппаратного стека перемещаются

на одну позицию вверх (уровень 1 — на уровень 0, уровень 2 — на уровень 1).

Если глубина аппаратного стека составляет, например, три уровня, то при глу-

бине вложения вызовов 4 (и более) подпрограмм необходимо соблюдать осторож-

Структура микроконтроллеров AVR

33

ность, поскольку в этом случае теряется адрес возврата, введенный в память пер-

вым, вследствие чего возврат становится невозможным!

Большинство восьмиразрядных микроконтроллеров AVR используют восьми-

или 16-разрядный указатель стека, состоящий из одного регистра SP или двух вось-

миразрядных регистров SPH и SPL. Их адреса в области ввода/вывода $ЗЕ ($5Е)

и $3D ($5D). Указатель стека после подачи сигнала сброса обнуляется, и доступен

для чтения и записи.

Указатель стека позволяет обращаться к сегменту данных в области, зарезерви-

рованной для стека, и должен быть инициализирован до начала выполнения про-