Author: Шахнова В.А.

Tags: полупроводниковые устройства микроэлектроника справочник технологические процессы издательство радио и связь микропроцессорные комплекты

ISBN: 5-256-00372-0

Year: 1988

Similar

Text

МИКРОПРОЦЕССОРЫ

и

МИКРОПРОЦЕССОРНЫЕ

КОМПЛЕКТЫ

ИНТЕГРАЛЬНЫХ

МИКРОСХЕМ

Шина адреса и данных

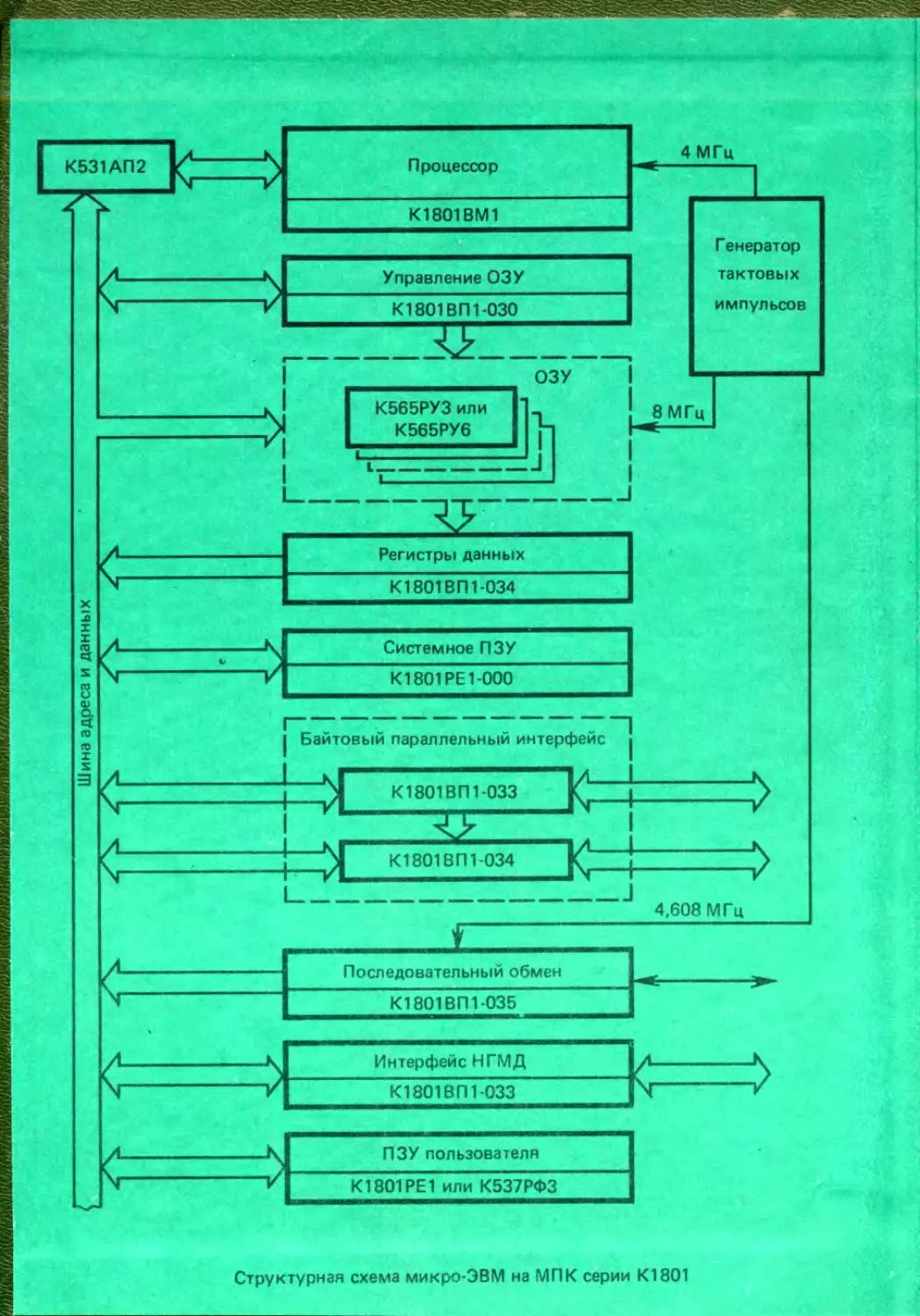

Структурная схема микро-ЭВМ на МПК серии К1801

Организация 16-разрядного процессора на микросхемах серии КМ1804

СПРАВОЧНИК

МИКРОПРОЦЕССОРЫ

И

МИКРОПРОЦЕССОРНЫЕ

КОМПЛЕКТЫ

ИНТЕГРАЛЬНЫХ

МИКРОСХЕМ

В ДВУХ ТОМАХ

ТОМ 1

Под редакцией В. А. ШАХНОВА

©

МОСКВА „РАДИО И СВЯЗЬ,,

1988

ББК 32.852

М59

УД К 681.325.5— 181.4 : 621.3.049.771.14 (03)

Рецензент: Чл.-корр. АН СССР Л. Н. Преснухин

Редакция литературы по электронной технике

Микропроцессоры и микропроцессорные комплекты

М59 интегральных микросхем: Справочник. В 2 т. / В.-Б. Б.

Абрайтис, Н. Н. Аверьянов, А. И. Белоус и др.; Под

ред. В. А. Шахнова. — М.: Радио и связь, 1988. — Т. 1.—

368 с.: ил.

ISBN 5-256-00372-0

Приведены классификация микропроцессоров и микропроцессорных комп

лектов больших интегральных микросхем и сведения о микропроцессорных

комплектах универсального назначения. Приводятся данные о структуре и

системах команд микропроцессоров, временных соотношениях сигналов, при-

меры использования микропроцессоров в аппаратуре.

Для инженерно-технических работников, разрабатывающих электронную

управляющую и вычислительную аппаратуру

2403000000-019

М 046(01 )-88 ,06-87

ББК 32.852

ISBN 5-256-00372-0 (Т. 1)

ISBN 5-256-00371-2

;ё) Издательство «Радио и связь». 1988

Содержание тома 1

Предисловие редактора..................6

Глава 1. Общие сведения о микро-

процессорных микросхемах

(В. А. Шахнов)

1.1. Терминология......................7

1.2. Система обозначений...............8

1.3. Условия эксплуатации.............10

1.4. Система параметрон...............11

1.5. Классификация микропроцессоров

и микропроцессорных комплектов микро-

схем .................................16

Глава 2. Микропроцессоры серий

К145ИК18, К145ИК19

(Л. С. Бойчун, В. П. Захаров,

Ю. М. Польский)

2.1. Микросхема К745ИК1801-2 .... 21

2.2. Микросхема К145ИК1807 .... 23

2.3. Микросхемы К145ИК1809 и

К145ИК1810 .....................26

2.4. Микросхема К145ИК1812 .... 33

2.5. Микросхема К145ИК1814 .... 38

2.6. Микросхема К145ИК1901 .... 40

2.7. Микросхема К145ИК1906 .... 41

2.8. Микросхема К145ИК1907 .... 44

2.9. Микросхема К145ИК1908 .... 47

2.10. Микросхема К145ИК1914 .... 50

2.11. Микросхема К145ИК1915 .... 52

Глава 3. Микропроцессорный комп-

лект серии КР580

(А. В. Кобылинский, А. И. Заика,

Г. П Липовецкий. И. П. Обуховский,

В. М. Калатинец, Н. Н. Аверьянов,

В А. Темченко. Л. В. Проценко,

Г. В. Латвийский, А. Н. Фионик,

Н. Л. Трунина — § 3.1—3.7, 3.15;

А. И. Третяк, В. И. Фирсов,

Г. Ю. Немеровский — § 3.8—3.12;

Г. Г. Нестеренко. А. В. Поветин,

А. М. Могилевский, А. С. Кусин —

§ 3.13, 3.14)

3.1. Микросхема КР580ВМ80А .... 55

3.2. Микросхема КР580ВВ51А .... 67

3.3. Микросхема КР580ВИ53 .... 76

3.4. Микросхема КР580ВВ55А .... 82

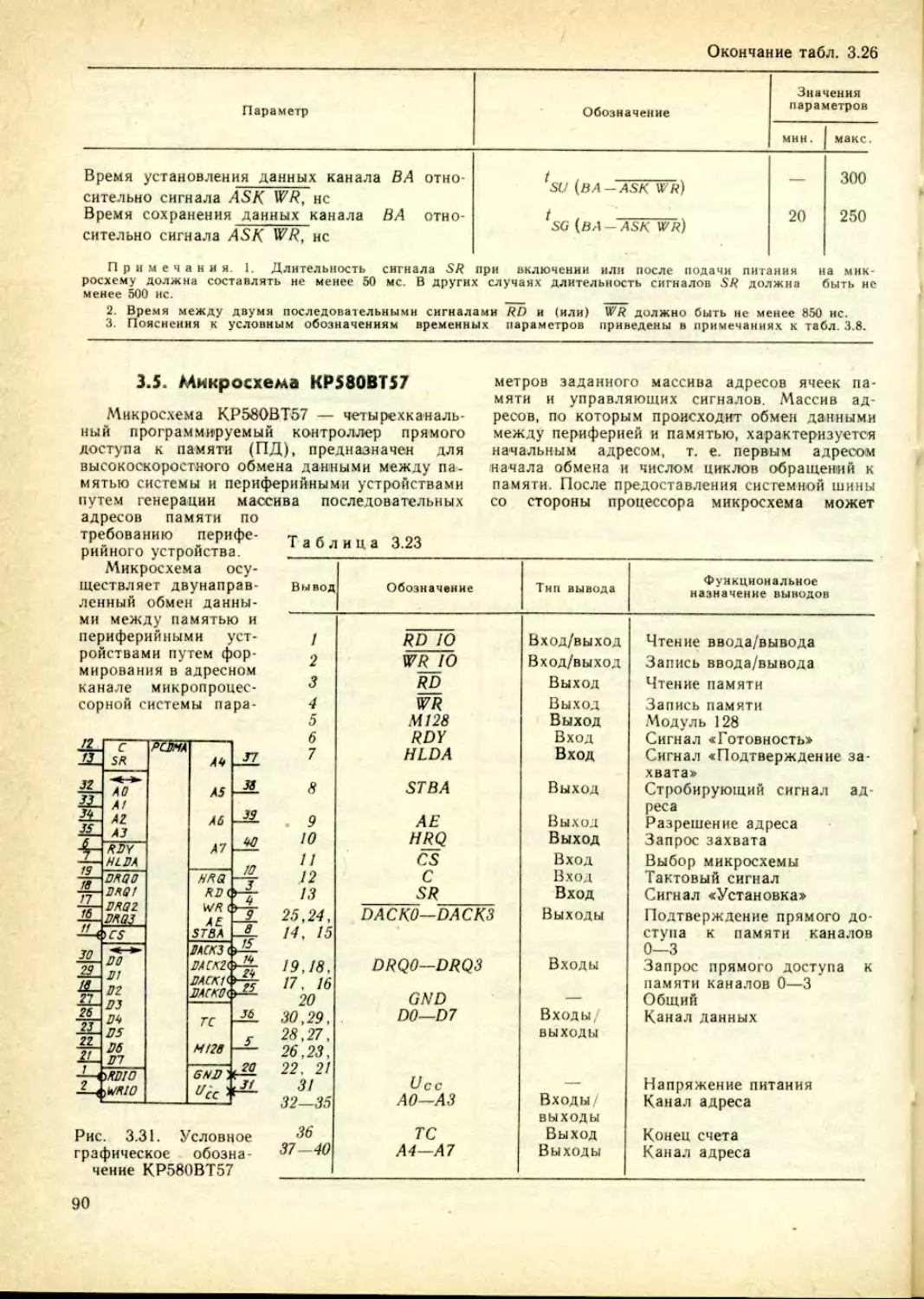

3.5. Микросхема КР580ВТ57 .... 90

3.6. Микросхема КР580ВН59 .... 99

3.7. Микросхема КР580ВВ79 .... 108

3.8. Микросхема КР580ВА93 . . .117

3.9. Микросхема КР580ВГ75 .... 122

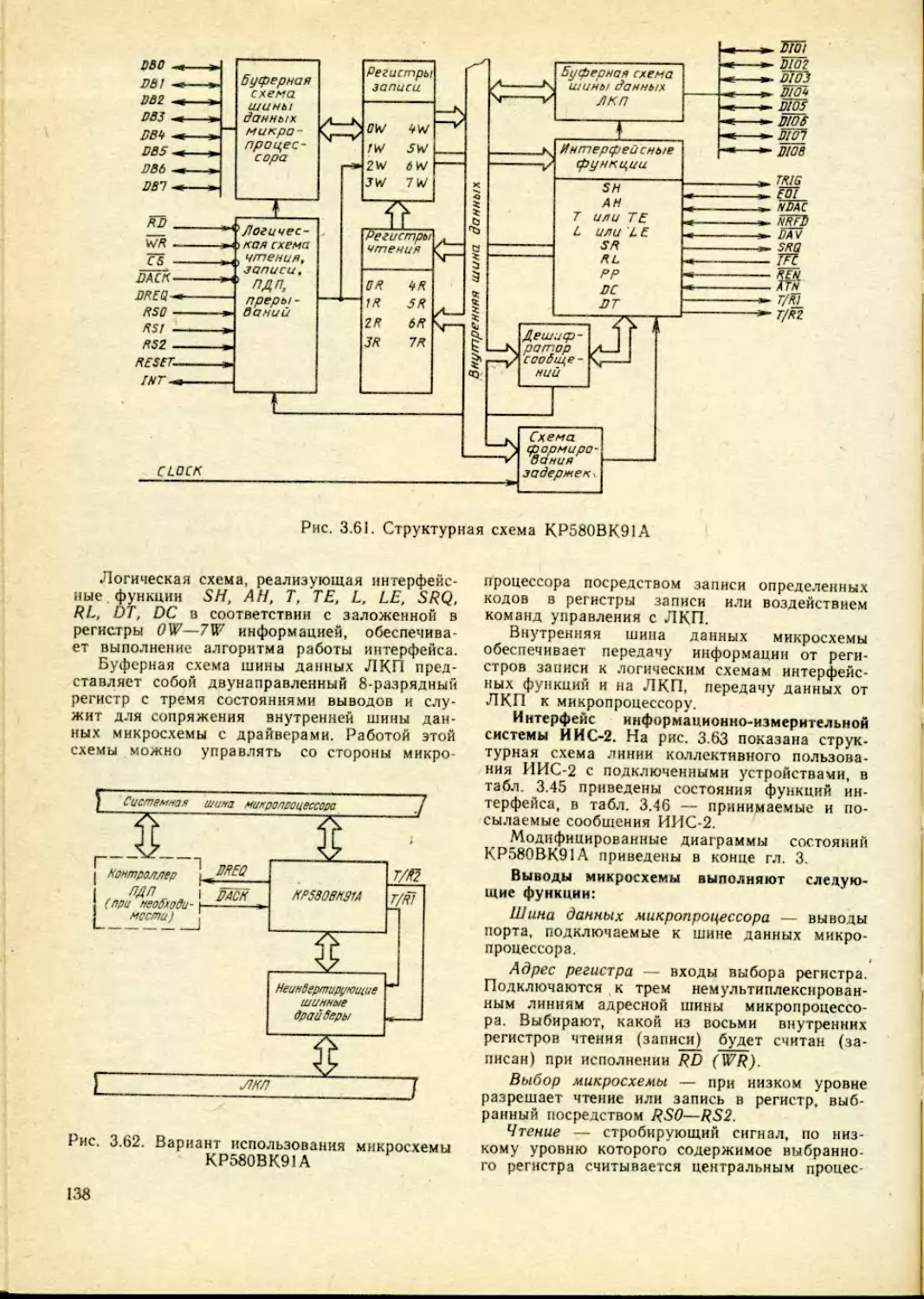

3.10. Микросхема КР580ВК91А .... 136

3.11. Микросхема КР580ГФ24 .... 157

3.12. Микросхемы КР580ВК28 и

КР580ВК38.........................160

3.13. Микросхемы КР580ИР82 и

КР580ИР83.........................163

3.14. Микросхемы КР580ВА86 и

КР580ВА87.........................166

3.15. Рекомендации по применению . . 169

Глава 4. Микропроцессорный комп-

лект серии КР581

(И. Е. Лобов, В. Т. Никифоровский,

Б. Л. Толстых, Н. Н. Тонких,

В. С. Хорошунов)

4.1. Микросхема КР581ИК1..........172

4.2. Микросхема КР581ИК2..........176

4.3. Микросхемы КР581РУ1, КР581РУ2

и КР581РУЗ........................179

4.4. Микросхема КР581ВЕ1..........181

Глава 5. Микропроцессорный комп-

лект серии К583

(Э. П. Калошкин, А. Ф. Кузнечиков,

Д. С. Сержанович, А. В. Силин)

5.1. Микросхема К583ВС1...........185

5.2. Микросхема К583ИК1...........189

5.3. Микросхема К583КП1 . . г . . 193

5.4. Микросхема К583ВМ1...........196

5.5. Микросхема К583ХЛ1...........200

5.6. Микросхема К583ВГ1 203

5.7. Микросхема К583ВА1 . . . 205

5.8. Микросхема К583ВА2...........208

5.9. Микросхема K583BA3...........209

5.10. Микросхема К583ВА4...........212

5.11. Рекомендации по применению . . 213

Глава 6. Микропроцессорный комп-

лект серии К584

(А. И. Белоус, А. Ф. Кузнечиков,

Д. С. Сержанович, А. И. Сухопарое)

6.1. Микросхема К584ВМ1............214

6.2. Микросхема К584ВУ1 222

6.3. Микросхема К584ВГ1 225

6.4. Микросхема К584ВВ1............229

6.5. Рекомендации по применению . . 233

3

Глава 7. Микропроцессорный комп-

лект серии КР587

(К). И. Борщенко, В. Л. Дшхунян,

Э. Е. Иванов, И. Р. Машевич,

В. В. Теленков)

7.1. Микросхема КР587ИК2............234

7.2. .Микросхема КР587ИК1...........242

7.3. .Микросхема КР587ИКЗ ... 246

7.4. Рекомендации по применению . . 252

Глава 8. Микропроцессорный комп-

лект серии К588

(В. А. Бобков. П. П. Гойденко,

Б. И. Чернуха, Д. И. Черняковский)

8.1. Микросхема К588ВС2............253

8.2. Микросхема К588ВУ2............262

8.3. Микросхема К588ВР2............265

8.4. Микросхема К588ВГ1 267

8.5. Микросхема К588ВЛ1 271

8.6. Микросхема К588ИР1............273

8.7. Микросхема К588ВГ2............275

8.8. Микросхема К588ВТ1 ..........277

Глава 9. Микропроцессорный комп-

лект серии К589

(А. И. Березенко, С. Е. Калинин,

Л. Н. Корягин)

9.1. Микросхема К589ИК02 ... 281

9.2. Микросхема К589ИК03 287

9.3. Микросхема К589ИК01 290

9.4. Микросхема К589ИК14 297

9.5. Микросхема К589ИР12 301

9.6. Микросхема К589АП16 и К589АП26 304

9.7. .Микросхема К589ХЛ4 305

Глава 10. Микропроцессорный комп-

лект серии К1800

(ВБ. Б. Абрайтис, А.-В. В. Пятраускас,

С. Ю. Седаускас)

10.1. Микросхема К1800ВС1..........310

10.2. Микросхема К1800ВУ1..........316

10.3. Микросхема К1800ВБ2..........324

10.4. Микросхема К1800ВТЗ..........328

10.5. Микросхема К1800ВЛ4..........335

10.6. Микросхема К1800РП6..........338

10.7. Микросхема К1800ВЛ7..........344

10.8. Микросхема KI800BP8..........346

10.9. Микросхема К1800РП16 .... 350

10.10. Рекомендации по применению . . 353

Приложение I. Корпуса микропроцессор-

ных микросхем (Л. И. Якушкина) . 359

Приложение 2. Краткие сведения о мик-

ропроцессорных микросхемах, не вошед-

ших в том 1 справочника (В. .4. Шахнов) 3(56

Содержание тома 2

Предисловие

Глава 11. Микропроцессорный комп-

лект серии KI80I

11.1. Микросхема KI801BM1

11.2. Микросхема КМ1801ВМ2

113. Микросхема KMI801BM3

11.4 Микросхема К1801ВП1-30

11.5. Микросхема K1801BI11-33

11.6. Микросхема К1801ВП1-34

11.7. Микросхема К1801ВП1-35

11.8. Микросхема КР1801РЕ2

11.9. Микросхема К573РФЗ

11.10. Рекомендации по применению

Глава 12. Микропроцессорный комп-

лект серии КР1802

12.1. Микросхема KP1802BCI

12.2. Микросхема КР1802ИР1

12.3. Микросхема KP1802BPI

12.4. Микросхема КР1802ВР2

12.5. Микросхема КР1802ВРЗ

12.6. .Микросхема КМ1802ВР4

12.7. Микросхема КМ1802ВР5

12.8. Микросхема КР1802ИМ1

12.9. Микросхема КР1802ИП1

12.10. Микросхема KPI8O2BB1

4

12.11. Микросхема KPI802BB2

12.12. Микросхема КР1802КП1

12.13. Микросхема KPI802BB3

Глава 13. Микропроцессорный к

лект серии КМ 1804

13.1. Микросхема КМ1804ВС1

13.2. Микросхема KMI804BC2

13.3. Микросхема КМ1804ВР1

13.4. Микросхема KMI804BP2

13.5. Микросхемы КМ1804ВУ1 и

КМ 1804ВУ2

13.6. Микросхема КМ1804ВУЗ

13.7. Микросхема КМ1804ВУ4

13.8. Микросхема КМ1804ВП1

13.9. Микросхема КМ1804ВРЗ

13.10. Микросхема КМ1804ВА1

13.11. Микросхема KMI804BA2

13.12. Микросхема KMI804BA3

13.13. Микросхема КМ1804ИРЗ

13.14. Микросхема КМ1804ГГ1

13.15. Микросхема КМ1804ВУ5

13.16. Микросхема КМ1804ВЖ1

13.17. Микросхема КМ1804ИР1

13.18. Микросхема КМ1804ИР2

13.19. Рекомендации по применению

Глава 14. Микропроцессорный комп-

лект серии К А1808

14.1. Микросхема KAI808BMI

14.2. Микросхема КА1808ИР!

14 3. Микросхема КА1808ВВ I

14.4. Микросхема КА1808ВУ1

14.5. Рекомендации по применению

Глава 15. Микропроцессорный комп-

лект серии К1809

15.1. Микросхема К1809ВВ I

152. Микросхема К1809ВВ2

15.3. Микросхема КМ1509КП1

Глава 16. Микропроцессорный комп-

лект серии КМ1810

16.1. Микросхема КМ1810ВМ86

16.2. Микросхема KP18I0BH59A

16.3. Микросхема КР1810ВБ89

16 4. Микросхема КР1810ВГ88

16.5. Микросхема КР1810ГФ84

16.6. Рекомендации по применению

Глава 17. Микропроцессорный комп-

лект серии К1811

17.1 Микросхема КН 181 IBMI

17.2. Микросхемы КН1811ВУ1.

КН1811ВУ2. КН 1811 ВУЗ

17.3. Микросхема KMI81IBTI

17.4. Соединение микросхем серии

КН181 I

Глава 18. Микропроцессор

серии КМ1813ВЕ1

Глава 19. Микропроцессоры

серии K18I4

Глава 20. Однокристальные микро-

ЭВМ серии КР1816

Приложение 1. Корпуса микропроцессор-

ных микросхем

Приложение 2 Краткие сведения о до-

полнительных микропроцессорных комп

лектах микросхем, не вошедших в спра

ВОЧНИК

Приложение 3. Краткие сведения о мик-

росхемах запоминающих устройств, при-

меняемых в микропроцессорных систе-

мах

Приложение 4. Цифровые (логические)

микросхемы, применяемые в микропро-

цессорных системах

Предисловие редактора

Перевод экономики страны на интенсивный путь развития, как указано в реше-

ниях XXVII съезда КПСС, невозможен без создания и массового применения высоко-

эффективных систем, машин и приборов, технологических процессов и автоматизиро-

ванных производств на их основе. Важную роль при этом призваны сыграть автома-

тизированные системы управления и широкое использование промышленных роботов,

оснащенных самыми современными электронными устройствами на основе последних

достижений микроэлектроники: больших интегральных схем микропроцессоров, запо-

минающих устройств и др. Особая роль в решении этой грандиозной задачи принад-

лежит микропроцессорной технике. Как подчеркивается в «Основных направлениях

экономического и социального развития СССР на 1986—1990 годы и на период до

2000 года», необходимо «широко внедрять гибкие переналаживаемые производства и

системы автоматизированного проектирования, автоматические линии, машины и обо-

рудование со встроенными средствами микропроцессорной техники...», что позволит

применять в народном хозяйстве в больших масштабах высокопроизводительные энер-

го- и материалосберегающие технологии, значительно повысит надежность производи-

мой техники и качество выпускаемой продукции.

Широкую популярность микропроцессоры получили благодаря своим высоким

функциональным возможностям и эксплуатационным характеристикам, придавшим

средствам вычислительной техники и автоматики качественно новые свойства: появи-

лись и получили широкое распространение микрокалькуляторы. микроЭВМ, персональ-

ные ЭВМ. интеллектуальные роботы, системы автоматизированного проектирования и

конструирования. Такие характеристики микропроцессоров как малые габариты, масса,

потребляемая мощность позволили применять их в областях, в которых использование

традиционных средств вычислительной техники было принципиально невозможным.

Важным является также то, что микропроцессоры позволили сделать реальной пер-

спективу, когда вычислительная техника, компьютеры станут такими же привычным

для всех понятием, как телевизор или радиоприемник.

Разнообразие микропроцессоров, различающихся технологией изготовления, архи-

тектурой, техническими характеристиками, конструктивным оформлением ставит перед

разработчиками средств вычислительной техники непростую задачу выбора определен-

ного типа микропроцессора, оптимального для тех или иных применений. Решение

такой задачи возможно, если у разработчика имеются полные сведения о выпускаемых

промышленностью микропроцессорах и микропроцессорных комплектах микросхем.

В 1982 г. издательство «Радио и связь» выпустило справочник «Микропроцессор-

ные комплекты интегральных схем Состав и структура». Многочисленные отзывы чи-

тателей, поступившие в издательство, содержали большое число предложений по его

содержанию. В частности, предлагалось описания работы микросхем дополнить вре-

менными диаграммами, принести системы команд и микрокоманд, конкретные рекомен-

дации по применению и т. п. Все эти предложения были учтены при подготовке к изда-

нию настоящего справочника. Для удобства пользования справочником все микро-

процессорные комплекты микросхем расположены в порядке возрастания номеров со-

ответствующих серий. В приложениях к т. 1 и 2 приведены общие виды корпусов мик-

ропроцессорных микросхем в порядке возрастания их номеров.

Содержащиеся в справочнике сведения соответствуют действовавшим ко времени

подготовки рукописи к изданию государственным стандартам и техническим услови-

ям на микросхемы. Наряду с этим необходимо особо отметить, что справочник не за-

меняет официальные документы (ГОСТ. ТУ и аналогичные технические документы),

устанавливающие требования к интегральным микросхемам и определяющие их каче-

ство, поэтому в конкретных разработках следует руководствоваться нормативными

документами.

В А. U/ахнов

Глава 1

Общие сведения о микропроцессорных микросхемах

1.1. Терминология

Интегральная микросхема (микросхема) —

микроэлектронное изделие, выполняющее опре-

деленную функцию преобразования и обработ-

ки сигнала и имеющее высокую плотность упа-

ковки электрически соединенных элементов

(или элементов и компонентов) и (или) крис-

таллов, которое с точки зрения требований к

испытаниям, приемке, поставке и эксплуата-

ции рассматривается как единое целое.

Элемент интегральной микросхемы — часть

микросхемы, реализующая функцию какого-

либо электрорадиоэлемента, которая выпол-

нена нераздельно от кристалла или подлож-

ки и не может быть выделена как самостоя-

тельное изделие с точки зрения требований к

испытаниям, приемке, поставке и эксплуата-

ции (к электрорадиоэлементам относятся

транзисторы, диоды, резисторы, конденсаторы

и др.).

Компонент интегральной микросхемы

часть микросхемы, реализующая функции ка-

кого-либо электрорадиоэлемеита. которая мо-

жет быть выделена как самостоятельное из-

делие с точки зрения требований к испытани-

ям, приемке, поставке и эксплуатации.

Полупроводниковая интегральная микро-

схема микросхема, все элементы и межэле-

ментные соединения которой выполнены в

объеме и на поверхности полупроводника.

Кристалл интегральной микросхемы —

часть полупроводниковой пластины, в объеме

и на поверхности которой сформированы эле-

менты полупроводниковой микросхемы, меж-

элементные соединения и контактные пло-

щадки».

Аналоговая интегральная микросхема —

микросхема, предназначенная для преобразо-

вания и обработки сигналов, изменяющихся

по закону непрерывной функции.

Цифровая интегральная микросхема —

микросхема, предназначенная для преобразо-

вания и обработки сигналов, изменяющихся

по закону дискретной функции.

Корпус интегральной микросхемы — часть

конструкции микросхемы, предназначенная

для ее защиты от внешних воздействий и сое-

динения с внешними электрическими цепями

посредством выводов.

Степень интеграции интегральной микро-

схемы — показатель степени сложности ми-

кросхемы. характеризуемый числом содержа-

щихся в ней элементов и компонентов.

Степень интеграции микросхемы определя-

ется по формуле K=lg.V, где К — коэффици-

ент. определяющий степень интеграции, округ-

ляемый до ближайшего большего целого чис-

ла; N — число входящих в микросхему эле-

ментов и компонентов.

Серия интегральных микросхем — сово-

купность типов микросхем, которые могут вы-

полнять различные функции, имеют единое

конструктивно-технологическое исполнение и

предназначены для совместного применения.

Микропроцессорная интегральная микро-

схема — микросхема, выполняющая функцию

микропроцессора (микроконтроллера) или его

части.

Микропроцессорная секция — микропро-

цессорная интегральная микросхема, реали-

зующая часть микропроцессора (микроконт-

роллера) и обладающая средствами простого

функционального объединения с однотипны-

ми или другими микропроцессорными секция-

ми для построения законченных микропро-

цессоров, микроконтроллеров или микро-ЭВМ.

Однокристальный микропроцессор (ОМП) —

микропроцессор, выполненный в виде боль-

шой интегральной схемы.

Однокристальная микро-ЭВМ (ОЭВМ) —

микро-ЭВМ, выполненная в виде большой ин-

тегральной схемы.

Однокристальная микросистема управ-

ляющая микропроцессорная система, выпол-

ненная в виде одной большой интегральной

микросхемы.

Микропроцессорный комплект интеграль-

ных микросхем — совокупность микропроцес-

сорных и других интегральных микросхем,

совместимых по архитектуре, конструктивно-

му исполнению и электрическим параметрам

и обеспечивающих возможность совместного

применения.

Микропроцессорный набор — совокупность

микропроцессорных и других интегральных

микросхем микропроцессорного комплекта

ИС, номенклатура и количество которых не-

обходимы и достаточны для построения кон-

кретного изделия вычислительной или управ-

ляющей техники.

Секционированный микропроцессорный

комплект — микропроцессорный комплект, со-

стоящий из микропроцессорных секций.

Комплект однокристального микропроцес-

сора — микропроцессорный комплект микро-

схем, в котором каждое из основных функцио-

нальных устройств, включая микропроцессор,

выполнено в виде одной большой интеграль-

ной микросхемы с встроенным системным ин-

терфейсом.

Микропроцессор — программно-управляе-

мое устройство, осуществляющее процесс об-

работки цифровой информации и управле

7

ния им, построенное на одной или несколь-

ких интегральных микросхемах.

Центральный микропроцессор — микропро-

цессор, непосредственно осуществляющий

процесс обработки данных в однопроцессор-

ной системе или организацию работы неодно-

родной мультипроцессорной системы.

Периферийный микропроцессор (сопроцес-

сор) — микропроцессор, выполняющий под

управлением центрального микропроцессора

определенную функцию в микропроцессорной

системе.

Специализированный микропроцессор —

микропроцессор, структура которого опти-

мизирована для решения определенного клас-

са задач.

Арифметический микропроцессор спе-

циализированный микропроцессор, структура

которого оптимизирована для выполнения

арифметических операций.

Разрядность микропроцессора число

разрядов регистров арифметического логиче-

ского устройства (АЛУ) микропроцессора.

Адресное пространство микропроцессора —

совокупность адресов внутренних регистров,

внутренних ЗУ и регистров периферийных

устройств, для обращения к которым доста-

точно содержимого регистра адреса микро-

процессора.

Оперативное запоминающее устройство

(ОЗУ) — внутреннее запоминающее устрой-

ство, обеспечивающее возможность оператив-

ного изменения информации, используемое для

записи, хранения и выдачи информации, в том

числе во время выполнения программы, и име-

ющее длительность цикла обращения, соизме-

римую с длительностью цикла выполнения

микропроцессором основных операций.

Постоянное запоминающее устройство

(ПЗУ) — запоминающее устройство с неиз-

меняемым содержимым памяти.

Программируемое постоянное запоминаю-

щее устройство (ППЗУ) — постоянное запо-

минающее устройство, в которое информация

заносится однократно потребителем не в сос-

таве изделия и не может быть впоследствии

изменена.

Репрограммируемое постоянное запоми-

нающее устройство (РИЗУ) постоянное за-

поминающее устройство, в котором информа-

ция может неоднократно изменяться при по-

мощи специальных средств стирания и записи.

Энергонезависимое оперативное запоми-

нающее устройство — оперативное запомина-

ющее устройство, в котором информация со-

храняется при отключении электропитания.

Магистраль совокупность соединитель-

ных линий и схем, обеспечивающих требуе-

мые параметры передаваемых по линиям элек-

трических сигналов, по которым информация

передается от одного или одного из несколь-

ких источников информации к одному из не-

скольких или к нескольким приемникам.

Двунаправленная магистраль — маги-

страль, по линиям связи которой сигналы мо-

гут передаваться в любом направлении, но не

одновременно.

Однонаправленная магистраль — маги-

страль, по каждой из линий связи которой

сигналы могут передаваться только в одном

направлении.

Базовый кристалл микросхемы — кристалл

интегральной микросхемы с определенным на-

бором сформированных в нем не соединен-

ных между собой двоичных логических эле-

ментов и (или) узлов из них, используемый

для создания интегральных микросхем путем

изготовления избирательных межэлементных

соединений.

Матричная микросхема — интегральная

микросхема, изготовленная путем соединения

элементов базового кристалла микросхемы

между собой и с контактными площадками

по индивидуальной схеме.

Регистр общего назначения (РОИ) — про-

граммно доступный для пользователя регистр

микропроцессора.

1.2. Система обозначений

Приведенные в справочнике микропроцес-

сорные интегральные микросхемы относятся к

группе полупроводниковых приборов, услов-

ное обозначение которых состоит из четырех

элементов: первый элемент — цифры 1 или 5;

второй элемент - двух- или грехзначное чис-

ло (например, 814 или 89); третий элемент —

две буквы, обозначающие подгруппу и вид

микросхемы (табл. 1.1); четвертый элемент

порядковый номер разработки микросхемы по

функциональному признаку в данной серии.

Условное обозначение серии микропроцес-

сорных интегральных микросхем состоит из

двух элементов: первый элемент — цифра 1

или 5. второй элемент — двух- или трехзнач-

ное число.

Г а 6 л и и а 1.1

Подгруппа Вид Обозна- чение

Генераторы Гармонических сигналов Прямоугольных сигналов Линейно изменяющихся сигналов Сигналов специальной формы Шума Прочие ГС гг гл ГФ ГМ гп

Детекторы Амплитудные Импульсные Частотные Фазовые Прочие ДА ДИ ДС Дф дп

Коммутато- ры и ключи Тока Напряжения Прочие кт КН КП

8

Продолжение табл. 1.1

Продолжение табл. 1.1

( ( 1 f А Подгруппа Вид Г J Подгруппа а * О х Вид Обозна- чение

Логические элементы Элемент И Элемент ИЛИ Элемент НЕ Элемент И — ИЛИ Элемент И — НЕ Элемент ИЛИ — НЕ Элемент И—НЕ/ИЛИ— НЕ Элемент И—ИЛИ — НЕ Элемент И—ИЛИ— НЕ/И — ИЛИ Элемент ИЛИ—НЕ/ИЛИ Расширители Прочие ли лл лн лс - дд Схемы ис ЛЕ точников др вторичного электрони др тания ЛК ЛМ лд ЛП Выпрямители Преобразователи Стабилизаторы напряже ния непрерывные Стабилизаторы тока Стабилизаторы напря- жения импульсные Схемы управления им- пульсными стабилизато- рами напряжения Схемы источников вто- ричного электропитания Прочие ЕВ ЕМ ЕН ЕТ ЕК ЕУ ЕС ЕН

Многофунк аномальные схемы Модуляторы Наборы эле ментов Преобразо- ватели сиг налов Аналоговые Цифровые Комбинированные Цифровые (в том числе программируемые) мат рины Аналоговые матрицы Комбинированные (ана- логовые и цифровые) матрицы Прочие Амплитудные Частотные Фазовые Импульсные Прочие Диодов Транзисторов Резисторов Конденсаторов Комбики рованные Функциональные Прочие Частоты Длительности Напряжения (тока) Мощности Уровня (соглаеователи) Аналого-цифровые Цифро-аналоговые Синтезаторы частоты Делители частоты ана- логовые Умножители частоты аналоговые Код — код Прочие XА Схемы за- держки X К ХМ Пассивные Активные Прочие БМ БР БП

хн XT Схемы срав- ни нения МА Амплитудные (уровня сигнала) Временные Частотные Компараторы напряже- ния Прочие С А СВ СС СК СП

МФ ми МП нд нт |_]р Триггеры НЕ * НК НФ НП ПС Тина У-К (универсаль- ные) Типа R-S (с раздельным запуском) Типа D (с задержкой) Типа Т (счетные) Динамические Шмидта Комбинированные (ти пов D Т. R-S-Т и т. п ) Прочие ТВ ТР ТМ ТТ ТД ТЛ тк ТП

пд пн пм ПУ ПА НВ ПЛ v ПК Усилители ПЕ ПР ПП Высокой частоты Промежуточной частоты Низкой частоты Широкополосные Импульсных сигналов Повторите.'! и Считывания и воспро- изведения 11ндикации Постоянного тока Операционные Д иффе ренина льн ые Ирочие У в УР УН УК УИ УЕ УЛ УМ УТ УД УС УН

Продолжение табл. 1.1

Окончание табл. 1.1

Подгруппа Вид Обоз и а чение

Верхних частот ФБ

Фильтры Нижних частот ФН

Полосковые ФЕ

Режекторные ФР

Прочие Ф11

Импульсов прямоуголь- АГ

ной формы Импульсов специальной АФ

Формирова- формы АА

тел и Адресных токов

Разрядных токов АР

Прочие АП

Фоточувст- Матричные ЦМ

вительные Линейные ЦЛ

схемы с за рядовой Прочие ЦП

связью

Матрицы оперативных запоминающих устройств Матрицы постоянных за- поминающих устройств Оперативные запомина- РМ РВ

РУ

ющие устройства Постоянные запоминаю- РТ

ющие устройства с воз- можностью однократно- го программирования РЕ

Схемы за Постоянные запоминаю-

поминающих щие устройства (масоч-

устройств ные) Запоминающие устрой- РЦ

ства на НМД Постоянные запоминаю- щие устройства с воз- можностью многократ- ного электрического пе- РР

репрограммирования Постоянные запоминаю- РФ

щие устройства с ульт-

рафиолетовым стирани- ем и электрической за-

писью информации Ассоциативные запоми- нающие устройства Прочие РА

РП

Регистры ИР

Сумматоры ИМ

Полусумматоры ИЛ

Счетчики HEJ

Схемы циф- Шифраторы ИВ

ровых уст- Дешифраторы ИД

ройств Комбинированные Арифметико-логические устройства Прочие ик ИА ИП

Подгруппа Вид Обозна- чение

Микро-ЭВМ ВЕ

Микропроцессоры ВМ

Микропроцессорные сек ВС

НИИ

Схемы микропрограмм- ВУ

ного управления Функциональные расши- ВР

рители Схемы синхронизации ВБ

Схемы управления пре- рыванием ВН

Схемы вы- Схемы управ, “ния вво ВВ

числитель- дом выводом (схемы ин-

ных средств терфейса) Схемы управления па- ВТ

мятью

Функциональные преоб- ВФ

разователи информации Схемы сопряжения с .ма- В А

гистралью Времязадающие схемы ВП

Микрокалькуляторы ВХ

Контроллеры ВГ

Комбинированные схемы вк

Специализированные схе вж.

МЫ

Прочие ВП

Условное обозначение микросхем, выпуска-

емых для широкого применения. содержит

дополнительный индекс «К», который ставит-

ся впереди всех элементов обозначения мик-

росхем. Буквы «К». «КМ» и «КР» в начале

условного обозначения микросхем характери-

зуют условия их приемки на заводе-изготови-

теле.

В состав микропроцессорного комплекта

интегральных микросхем могут входить как

сами микропроцессорные микросхемы опреде-

ленной серии, так и микросхемы других се-

рий. придающие комплекту новые качества и

расширяющие его возможности.

1.3. Условия эксплуатации

Микропроцессорные микросхемы сохраня-

ют свои параметры в пределах норм, установ-

ленных техническими условиями на микросхе-

мы конкретных типов, в процессе воздействия

и после воздействия на них различных эксплу-

атационных факторов. В табл. 1.2 приводятся

условия эксплуатации микросхем, сведения о

которых содержатся в настоящем справоч-

нике.

Общими техническими условиями устанав-

ливается минимальная наработка микропро-

10

Таблица 1.2

Сери я Интервал рабочих температур, °C Многократ- ное цикличе- ское измене ниетемпера- туры. °C Относитесь мая влаж- ность ВОЗ ДУ ха 98% при темпера- туре. °C Атмосферное давление. Па Вибрация с ускоре- нием 10g в диапа- зоне частот. Гц Много- кратные удары с ускоре- нием. g Линейная нагрузка с ускоре- нием. g

К145ИК18. -10 +- +55 —10 + +55 25 6,7 -102 •+ 3-10= 1 -600 75 25

К145ИК19 КР580 — 10 + +70 — 10 + +70 25 6,7-102+-3-10s 1 600 75 50

KP58I — 10 + +70 — 10 +- +70 25 6.7-IQ2 + 3- 10r 1-600 75 50

К583 — 10 +- +70 — 10 +- +70 25 6,7-102-+3-10E 1—600 75 50

К584 — 10 +• +70 — 10 +- +70 35 6.7- IO2 + 310е 1-2000 75 50

КР587 -45 +- +70 —45 +- +70 25 6.7-102 4-3-IO5 1-600 75 25

К588 — 10 -+ +70 — ГО +- +70 35 6.7 -102+-3 -10s 1 —2000 75 50

К589 — 10 + +70 — 10 +- +70 25 6.7 102 +- 3 - 10E 1-600 75 50

К1800 — 10 +- +70 -10 + +75 25 6.7 IO2-+3-10s 1—600 75 50

К1801 — 10 + +-75 —10+- +75 25 6.7 IO2 + 310E 1-600 75 50

КР1802 -I0+- +70 — 10 +- +70 25 6.7 102 + 3-10 1-600 75 50

КМ 1804 —10+- +70 - 10 +- +70 35 6.7 I02-+3-Ю6 1 —600 75 50

КА 1808 —25 +- +55 —25 +- +55 35 6.7 102 л-З Ю- 1- 600 75 50

К1809 -60+- +85 —60 +- +85 35 6,7 102 + 3- 10е 1-600 75 25

КМ1810 — 10 +- +70 — 10 + +70 35 6.7- 102-+ 3-1 О5 1 -600 75 50

КН1811 — 10 +- +70 — 10 +-. +70 35 6.7 I02 + 3 10' 1—600 75 50

K.MI813 — 10 +- +70 — 10 + +70 35 6,7-102-+3-10s 1-600 75 50

К1814 -10 +- +55 - Ю+- +55 25 6.7 I02 4-3-10= 1 -600 75 50

КР1816 — 10 +• +70 — 10 +- +70 25 6.7 102 + 3-10= 1—600 75 50

цессорных микросхем не менее 10 000 или

15 000 ч, а в облегченных режимах — 25 000 ч.

Минимальная наработка конкретных микро-

схем в соответствующих условиях и режимах

эксплуатации гарантируется в технических

условиях на поставку этих типов микросхем.

В упаковке предприятия-изготовителя или

в составе аппаратуры, а также в комплекте

ЗИП микропроцессорные микросхемы могут

храниться не менее 6 лет. Условия и срок

хранения устанавливаются в технических ус-

ловиях на поставку конкретных типов микро-

схем.

1.4. Система параметров

Ниже приводится перечень электрических

и других параметров микропроцессорных мик-

росхем, их буквенное международное (отече-

ственное) обозначение и определение, уста-

новленные ГОСТ 19480—74 и другими норма-

тивными документами.

Параметры, имеющие размерность напря-

жения:

Максимальное входное напряжение Ui „ал

(U„s ,„ах) — наибольшее значение входного

напряжении, при котором изменения параме-

тров интегральной микросхемы соответствуют

заданным значениям.

Минимальное входное напряжение Uimiu

— наименьшее значение входного

напряжения, при котором изменения параме-

тров интегральной микросхемы соответствуют

заданным значениям.

Помехоустойчивость при низком уровне

.Ml(1/°i,om) абсолютное значение разности

между максимальным входным напряжением

низкого уровня и максимальным выходным

напряжением низкого уровня интегральной

микросхемы.

Помехоустойчивость при высоком уровне

Л4и (l/'пом) — абсолютное значение разности

между минимальным входным напряжением

высокого уровня и минимальным выходным

напряжением высокого уровня интегральной

микросхемы.

Напряжение i-ro источника питания инте-

гральной микросхемы 6+с , (4Л, ,) значение

напряжения i-ro источника питания, обеспе-

чивающего работу интегральной микросхемы

в заданном режиме; i — порядковый номер

источника. 1= 1-5-4.

Пороговое напряжение высокого уровня

интегральной микросхемы (4/'п<,р) наимень-

шее значение напряжения высокого уровня на

входе интегральной микросхемы, при кото-

ром происходит переход интегральной микро-

схемы из одного устойчивого состояния в дру-

гое.

Пороговое напряжение низкого уровня ин-

тегральной микросхемы (47° пор) — наиболь-

шее значение напряжения низкого уровня на

входе интегральной микросхемы, при котором

происходит переход интегральной микросхе-

мы из одного устойчивого состояния в дру-

гое.

Напряжение инжектора при заданном то-

ке инжектора U<; .

II

Входное напряжение интегральной микро-

схемы значение напряжении на

входе интегральной микросхемы в заданном

режиме.

Входное напряжение высокого уровня ин-

тегральной микросхемы С/|н((/'||х)—значение

напряжения высокого уровня на входе инте-

гральной микросхемы.

Входное напряжение низкого уровня инте-

гральной микросхемы L!il(U°i,x) значение

напряжения низкого уровня на входе инте-

гральной микросхемы

Минимальное входное напряжение низкого

уровня интегральной микросхемы (7ц>п1П

(6/°»жИ|.п) наименьшее положительное или

наибольшее отрицательное значение напряже-

ния из допустимого диапазона входных нап-

ряжений низкого уровня интегральной микро-

схемы.

Максимальное входное напряжение низко-

го уровня интегральной микросхемы Uu.mii

— наибольшее положительное или

наименьшее отрицательное значение напряже-

ния из допустимого диапазона входных нап-

ряжений низкого уровня интегральной микро-

схемы.

Минимальное входное напряжение высоко-

го уровня интегральной микросхемы Uni mi,.

(U*«ж п.,,.) - наибольшее положительное или

наибольшее отрицательное значение напряже-

ния из допустимого диапазона входных нап-

ряжений высокого уровня интегральной мик-

росхемы.

Максимальное входное напряжение высо-

кого уровня интегральной микросхемы L1, и

{Ulai max) — наибольшее положительное или

наименьшее отрицательное значение напряже-

ния из допустимого диапазона входных нап-

ряжений высокого уровня интегральной мик-

росхемы.

Выходное напряжение интегральной мик-

росхемы Uo(UKl,ix) — значение напряжения

на выходе интегральной микросхемы в задан-

ном режиме.

Выходное напряжение низкого уровня ин-

тегральной микросхемы вых).

Выходное напряжение высокого уровня

интегральной микросхемы Ь'о н (l/'нмх).

Максимальное выходное напряжение низ-

кого уровня интегральной микросхемы

Uoi. . (1/° ню т.н) -- наибольшее положи-

тельное или наименьшее отрицательное зна-

чение напряжения из допустимого диапазона

выходных напряжений низкого уровня инте-

гральной микросхемы.

Минимальное выходное напряжение высо-

кого уровня интегральной микросхемы

(l/'iMxmin) наименьшее положительное

или отрицательное значение напряжения из

допустимого диапазона выходных напряже-

ний высокого уровня интегральной микросхе-

мы.

Параметры, имеющие размерность тока:

Ток инжектора для схем I1V1 1а

(/инж) — значение тока в цепи вывода пита-

ния, необходимое для работы микросхемы в

заданном режиме.

Ток потребления I г с{1 пит) — значение то-

ка, потребляемого микросхемой от источни-

ков питания в заданном режиме.

Динамический ток потребления интеграль-

ной микросхемы /его (/..>▼- дин) ток по-

требления микросхемы в режиме переключе-

ния.

Ток потребления при низком уровне вы-

ходного напряжения /<< /. (/° ,i„T).

Ток потребления при высоком уровне вы-

ходного напряжения /< < н (/’нот).

Ток потребления в состоянии «выключено»

(для схем с тремя устойчивыми состояниями

на выходе) /ссг (/пот-вык.т) - ток потребле-

ния микросхемы при закрытом состоянии вы-

хода.

Входной ток /т (/нх) значение тока, про-

текающего во входной цепи интегральной ми-

кросхемы в заданном режиме.

Входной ток низкого уровня интегральной

микросхемы /jl(/uhx) значение входного

тока при напряжении низкого уровня на вхо-

де микросхемы.

Входной ток высокого уровня интеграль-

ной микросхемы /)н(/ *«х) — значение тока

при напряжении высокого уровня на входе

микросхемы.

Ток утечки /ь(/>т) значение тока в цепи

интегральной микросхемы при закрытом сос-

тоянии цепи и заданных режимах на осталь-

ных выводах.

Ток утечки на входе интегральной микро-

схемы /1.1 (/>т-их) — значение тока во вход-

ной цепи микросхемы при закрытом состоя-

нии входа и заданных режимах на остальных

выводах.

Ток утечки низкого уровня на входе инте-

гральной микросхемы li n. (/°ут нх) - гок

утечки интегральной микросхемы во входной

цепи при входных напряжениях в диапазоне,

соответствующем низкому уровню, и при за

данных режимах на остальных выводах.

Ток утечки высокого уровня на входе ин-

тегральной микросхемы /ь |и (/')т. »х) ток

утечки интегральной микросхемы во входной

цепи при входных напряжениях в диапазоне,

соответствующем высокому уровню, и при за-

данных режимах на остальных выводах.

Выходной ток интегральной микросхемы

1и (/вых) — значение тока, протекающего в

пени нагрузки микросхемы в заданном режи-

ме.

Выходной ток низкого уровня интеграль-

ной микросхемы /от (/° вы х) значение вы-

ходного тока при напряжении низкого уровня

на выходе микросхемы.

Выходной ток высокого уровня интеграль-

ной микросхемы /он(/'аых) — значение вы-

ходного тока при напряжении высокого уров-

ня на выходе микросхемы.

12

Выходной ток в состоянии «выключено»

/oz (/вых-иыкл) — выходной ток микросхемы

с тремя состояниями на выходе при выклю-

ченном состоянии выхода.

Выходной ток низкого уровня в состоянии

«выключено» /о ZL (/°вы». пыкл) — выходной

ток в состоянии «выключено» микросхемы при

подаче на измеряемый выход заданного на-

пряжения низкого уровня.

Выходной ток высокого уровня в состоя-

нии «выключено» /огн (/'вых. выкл) — выход-

ной ток в состоянии «выключено» микросхе-

мы при подаче па измеряемый выход задан-

ного напряжения высокого уровня.

Ток утечки на выходе интегральной микро-

схемы /1_о(/ут- вых) — значение тока в вы-

ходной цепи микросхемы при закрытом сос-

тоянии выхода и заданных режимах на ос-

тальных выводах.

Ток утечки низкого уровня на выходе ин-

тегральной микросхемы /lol (/°>т. вых) — ток

утечки интегральной микросхемы в выходной

цепи при закрытом состоянии выхода, при

выходном напряжении в диапазоне, соответ-

ствующем низкому уровню, и при заданных

режимах на остальных выводах.

Ток утечки высокого уровня на выходе ин-

тегральной микросхемы /тон (/'ут- вых) —

ток утечки интегральной микросхемы в вы-

ходной цепи при закрытом состоянии выхода,

при выходном напряжении в диапазоне, соот-

ветствующем низкому уровню, и при задан-

ных режимах на остальных выводах.

Ток короткого замыкания интегральной

микросхемы /Оя(/к-а) — значение выходного

тока при закороченном выходе.

Параметры, имеющие размерность мощно-

сти:

Потребляемая мощность интегральной ми-

кросхемы Рсс(Рпт) — значение мощности,

потребляемой микросхемой ст источников пи-

тания в заданном режиме.

Динамическая потребляемая мощность ин-

тегральной микросхемы Рссо (Спот, дин)

значение потребляемой мощности микросхе-

мы в заданном динамическом режиме.

Максимальная потребляемая мощность ин-

тегральной микросхемы (РсСтах(Р пот max) —

значение мощности, потребляемой микросхе-

мой, при максимальном напряжении питания.

Рассеиваемая мощность интегральной мик-

росхемы Plot (Руис) — значение мощности.

' рассеиваемой микросхемой, работающей в за-

данном режиме.

Параметры, имеющие размерность времени:

Время задержки импульса интегральной

микросхемы /а(/зд) интервал времени меж-

ду фронтами входного и выходного импуль-

сов микросхемы, измеренный на заданном

уровне напряжения или тока.

Среднее время задержки распространения

сигнала логической интегральной микросхемы

(/чд.р ср) — интервал времени, равный полу-

сумме времен задержки распространения сиг-

нала при включении и выключении логической

интегральной микросхемы.

Время перехода при включении интеграль-

ной микросхемы Ithl (/|0) — интервал вре-

мени, в течение которого напряжение на вы-

ходе микросхемы переходит от высокого

уровня к низкому, измеренный на уровнях 0,1

и 0,9 или на заданных значениях напряжения.

Время перехода при выключении инте-

гральной микросхемы /ггя(/01) — интервал

времени, в течение которого напряжение на

выходе микросхемы переходит от низкого

уровня к высокому, измеренный на уровнях

0,1 и 0,9 или на заданных значениях напря-

жения.

Время выбора интегральной микросхемы

/ся(/»..ч) — интервал времени между подачей

на вход сигнала выбора микросхемы и полу-

чением на выходе сигналов информации.

Время сохранения сигнала интегральной

микросхемы /г(/с») — интервал времени меж-

ду окончанием двух заданных входных сиг-

налов микросхемы на разных входах.

Время хранения информации интегральной

микросхемы /sc(/xp) — интервал времени, в

течение которого микросхема в заданном ре-

жиме эксплуатации сохраняет информацию.

Время установления сигнала интегральной

микросхемы /su(/yc) — интервал времени

между началами двух заданных входных сиг-

налов микросхемы на разных входах.

Время цикла интегральной микросхемы

tcr(ta) — длительность периода сигнала на

одном из управляющих входов, в течение ко-

торого микросхема выполняет одну из функ-

ций.

Время восстановления интегральной мик-

росхемы tngc (/вое) интервал времени меж-

ду окончанием заданного сигнала на выводе

микросхемы и началом заданного сигнала

следующего цикла.

Длительность сигнала интегральной микро-

схемы /„• (т).

Длительность сигнала низкого уровня ин-

тегральной микросхемы /h-l(t°) — интервал

времени от момента перехода сигнала инте-

гральной микросхемы из состояния высокого

уровня в состояние низкого уровня до момен-

та его перехода из состояния низкого уровня

в состояние высокого уровня, измеренный на

заданном уровне напряжения.

Длительность сигнала высокого уровня ин-

тегральной микросхемы /и-н(т’) интервал

времени от момента перехода сигнала из сос-

тояния низкого уровня в состояние высокого

уровня до момента перехода его из состоя-

ния высокого уровня в состояние низкого

уровня, измеренный на заданном уровне на-

пряжения.

Период следования импульсов тактовых

сигналов интегральной микросхемы Тс (Тт) —

интервал времени между началами или окон-

чаниями следующих друг за другом импуль-

сов тактовых сигналов интегральной микро-

схемы, измеренный на заданном уровне нап-

ряжения.

Параметры, имеющие размерность частоты:

Частота следования импульсов тактовых

сигналов интегральной микросхемы /с(?т).

13

Частота генерирования интегральной мик-

росхемы (/г).

Параметры, имеющие размерность сопро-

тивления:

Входное сопротивление интегральной мик-

росхемы Rt(RBx) — величина, равная отно-

шению приращения входного напряжения ин-

тегральной микросхемы к приращению актив-

ной составляющей входного тока при задан-

ном значении частоты сигнала.

Выходное сопротивление интегральной

микросхемы Ro(Raux) — величина, равная

отношению приращения выходного напряже-

ния интегральной микросхемы к вызвавшему

его приращению активной составляющей вы-

ходного тока при заданном значении частоты

сигнала.

Сопротивление нагрузки интегральной ми-

кросхемы Rl(R„) — суммарное активное со-

противление внешних цепей, подключенных к

выходу микросхемы.

Параметры, имеющие размерность емкости:

Входная емкость интегральной микросхе-

мы Ci (Сях) — величина, равная отношению

емкостной реактивной составляющей входного

тока интегральной микросхемы к произведе-

нию круговой частоты на синусоидальное

входное напряжение микросхемы при задан-

ном значении частоты сигнала.

Выходная емкость интегральной микросхе-

мы Со(Свых) — величина, равная отноше-

нию емкостной реактивной составляющей вы-

ходного тока интегральной микросхемы к

произведению круговой частоты на вызванное

им выходное напряжение при заданном зна-

чении частоты сигнала.

Емкость входа/выхода интегральной мик-

росхемы Ci/o (Сах1аых) — значение емкости

объединенного входа/выхода, равное отноше-

нию емкостной реактивной составляющей

входного/выходного тока микросхемы к про-

изведению круговой частоты на синусоидаль-

ное входное/выходное напряжение при задан-

ном значении частоты сигнала.

Емкость нагрузки интегральной микросхе-

мы Сг.(Сп) — суммарная емкость внешних

цепей, подключенных к выходу микросхемы.

Прочие параметры:

Разрядность слова адреса пл(па) — число

разрядов в адресном слове.

Разрядность слова данных по(пл) — чис-

ло разрядов в слове данных.

Разрядность слова команды (микрокоман-

ды) nNS, пМкв(Пк, Пмк) — число разрядов в

слове команды (микрокоманды).

Число команд (микрокоманд) Qns, Qmxs

(Q, Qmk) — общее число команд (микроко-

манд), реализуемых микросхемой.

Коэффициент функциональной мощности

команды (микрокоманды) для выполнения

операции формата регистр — регистр Кип

(Крр) — минимальное число команд (микро-

команд), необходимых для реализации опера-

ции формата регистр — регистр для слов дан-

ных.

Коэффициент функциональной мощности

команды (микрокоманды) для выполнения

операции формата регистр — память Кпм

(Крп) — минимальное число микрокоманд

(команд), необходимых для реализации опе-

рации формата регистр — память для слов

данных при непосредственной адресации па-

мяти.

Коэффициент функциональной мощности

команды (микрокоманды) для выполнения

операции умножения двух слов Л'.мру(Кумн)—

минимальное число микрокоманд (команд),

необходимых для реализации операции умно-

жения двух слов данных микросхемы.

Коэффициент объединения по выходу

Ксо(Коп, вых) — максимально допустимое

число объединяемых выходов, по которым

реализуется логическая функция.

Нагрузочная способность У (Д') — пара-

метр микросхемы, который в зависимости от

схемотехнических особенностей может харак-

теризоваться либо значениями выходных то-

ков, либо коэффициентом разветвления по вы-

ходу, либо значением емкости нагрузки.

Понятия и их обозначения, характерные для

микропроцессорных микросхем

Данные D (Д) — информация, представ-

ленная в формализованном виде и предназна-

ченная для обработки ее техническими сред-

ствами или уже обработанная ими.

Канал В (КН) — совокупность средств

для передачи сигналов между источником и

приемником.

Операция ОР (ОП) — нахождение некото-

рой величины в результате выполнения дей-

ствия, указанного командой программы, над

одной или несколькими величинами.

Микрооперация МО (МОП) — элементар-

ная операция, выполняемая за один такт ра-

боты микросхемы.

Команда NS (К) — код, определяющий

действия микросхемы при выполнении отдель-

ных операций.

Микрокоманда MNS (МК) — код одной

или нескольких микроопераций, выполняемых

за один такт работы микросхемы.

Регистр команд PGNS (РК) — регистр, в

котором хранится текущая команда програм-

мы.

Регистр микрокоманды RGMNS (РМК) —

регистр, в котором хранится текущая микро-

команда микропрограммы.

Адрес А (А) — код, который указывает

устройство или элемент данных, используе-

мые при выполнении операции.

Прямой доступ к памяти DMA (ПД) —

режим работы, разрешающий внешним уст-

ройствам вводить в память данные или извле-

кать их, минуя процессор и не прерывая вы-

полнение программы.

Операции:

Сложение ADD (СД).

Вычитание DEC (ВЧ).

Умножение МРУ (УМН).

14

Деление DIV (ДЛ).

Логическая операция LC (Л) — операция,

при выполнении которой каждый разряд ре-

зультата формируется как итог логических

действий над одноименными разрядами опе-

рандов.

Сдвиг SH (СД) — процесс смещения ма-

шинного слова или его части на заданное чис-

ло разрядов.

Сдвиг влево SL (СДЛ).

Сдвиг вправо 5/? (СД11).

Арифметический сдвиг AS (АСД) — сдвиг,

при котором смещаются все разряды машин-

ного слова (за исключением знаковых).

Логический сдвиг LS (ЛСД) — сдвиг, при

котором смещаются все разряды машинного

слова, включая знаковые.

Циклический сдвиг RS (ЦСД) — логиче-

ский сдвиг, в процессе которого информация,

выводимая с одного конца сдвигающего уст-

ройства, вводится в освобождающиеся разря-

ды на другом его конце.

Инкремент 1 1NC1 (+1) — операция сло-

жения 1 с операндом.

Инкремент 2 INC2 (+2) — операция сло-

жения 2 с операндом.

Декремент 1 DEC1 (—1) — операция вы-

читания 1 из операнда.

Декремент 2 DEC2 (—2) — операция вы-

читания 2 из операнда.

Инкремент 1/Декремент 1 INC1IDEC1

(+1/—1) — операция сложения 1 с операн-

дом или вычитания 1 из операнда.

Сигналы:

Синхронизация S (С) — сигнал, иницииру-

ющий одновременное выполнение операций

различными функциональными частями интег-

ральной микросхемы.

Стробирующий сигнал STB (СТР) — сиг-

нал, инициирующий или фиксирующий опре-

деленный этап выполнения операции.

Запрос RQ (3) — сигнал, запрашиваю-

щий о возможности выполнения операции.

Разрешение Е (Р) — сигнал, разрешаю-

щий выполнение операции.

Установка CLR (УСТ) — сигнал установ-

ки элементов и функциональных частей интег-

ральной микросхемы в определенное состоя-

ние.

Останов HLT (ОСТ) — сигнал, останавли-

вающий выполнение операции.

Повтор RP (НВТ) — сигнал, инициирую-

щий или фиксирующий повторение операции.

Готовность RDY (ГТ) — сигнал, свиде-

тельствующий о готовности интегральной мик-

росхемы к выполнению операции.

Ожидание WAIT (ЖД) — сигнал, свиде-

тельствующий об ожидании поступления на

интегральную микросхему определенных сиг-

налов.

Пуск STR (ИСК) — сигнал, инициирую-

щий начало выполнения операции.

Продолжение CNT (ПРД) — сигнал, ини-

циирующий продолжение операции.

Чтение R (ЧТ) — сигнал, свидетельствую-

щий о чтении информации или устанавливаю-

щий интегральную микросхему в режим чте-

ния информации.

Запись W (ЗП) — сигнал, свидетельству-

ющий о записи информации или устанавлива-

ющий интегральную микросхему в режим за-

писи информации.

Выбор микросхемы CS (ВМ) — сигнал,

инициирующий выбор данной интегральной

микросхемы для участия в выполнении опе-

рации.

Прием IP (ПМ) — сигнал, инициирующий

прием информации или свидетельствующий о

приеме информации.

Выдача ОР (ВД) — сигнал, инициирую-

щий выдачу информации или свидетельствую-

щий о выдаче информации.

Квитирование «Выдано» ОРА (КВ) — сиг-

нал, сопровождающий выданную информа-

цию.

Квитирование «Принято» /РА (КП) — сиг-

нал, свидетельствующий об окончании прие-

ма информации.

Тактовый импульс CLC (ТИ) — периоди-

ческий импульсный сигнал, инициирующий ин-

тегральную микросхему к выполнению очеред-

ной операции.

Начало выполнения команды (микрокоман-

ды) BGNS, BGMNS (НК. НМК) — сигнал,

инициирующий исполнение команды (микро-

команды).

Перенос С (ПС) — сигнал, возникающий,

когда результат сложения в о^ной цифровой

позиции двух или более чисел равен основа-

нию позиционной системы счисления или пре-

вышает его.

Конец команды (микрокоманды) ENDNS,

ENDMNS (КК, КМК) — сигнал, свидетельст-

вующий об окончании исполнения команды

(микрокоманды).

Переполнение OW (ПП) — сигнал, свиде-

тельствующий о получении результата, выхо-

дящего за пределы диапазона представления

чисел.

Расширение ЕХР (РШ) — сигнал, свиде-

тельствующий о получении результата с вы-

падающим разрядом из разрядной сетки.

Знак НВ (ЗН) — сигнал, свидетельствую-

щий о знаке результата.

Равенство нулю ZR (PH) — сигнал, сви-

детельствующий о равенстве результата нулю.

Состояние ST (СС) — сигнал, свидетельст-

вующий о состоянии результата после выпол-

нения операции.

Маскирование Л( (МС) — сигнал, пред-

назначенный для выделения определенных

разрядов в машинном слове.

Прерывание 1НТ (ПР) — сигнал, по кото-

рому осуществляется временное прекращение

выполнения вычислительным устройством пос-

ледовательности команд одной программы с

целью выполнения последовательности ко-

манд другой программы.

Ответ ASU7 (ОТВ) — сигнал ответа уст-

ройства, находящегося в режиме подчинения,

о том, что информация готова к передаче или

принята.

15

Передача TF (ПЧ) — сигнал, инициирую-

щий передачу информации или свидетельству-

ющий о ее передаче.

Подтверждение ЛСК (П) — сигнал инте-

гральной микросхемы, подтверждающий ранее

выданный сигнал.

Канал занят BSY (КЗТ) — сигнал, свиде-

тельствующий о том, что ка'нал занят инфор-

мацией.

Управление V (У) — сигнал, инициирую-

щий выполнение определенных операций.

Задатчик DR (ЗД) — сигнал задающего

устройства исполнительному устройству.

Исполнитель PF (ИСП) — сигнал испол-

нительного устройства задающему устройству.

Зависание HG (ЗВС) — сигнал, свидетель-

ствующий об отсутствии реакции определен-

ного устройства по истечении заданного вре-

мени после поступления запроса.

Ведущий /MS (ВДШ) — сигнал ведущего

устройства, инициирующего выполнение опре-

деленной операции.

Ведомый SV (ВДМ) — сигнал ведомого

устройства, находящегося в режиме подчине-

ния при выполнении определенной операции.

Приоритет Р (ПТ) — сигнал, указываю-

щий очередность выполнения команд или про-

грамм при их одновременном поступлении.

Авария сети питания PNB (ДСП) — сиг-

нал, свидетельствующий о выходе напряже-

ния питающей сети за пределы допусков.

Авария источника питания PSB (АИП) —

сигнал, свидетельствующий о выходе напря-

жения источника питания (тока источника пи-

тания) за пределы допусков.

При образовании буквенных обозначений

производных параметров используется следу-

ющая форма записи:

xyi. kj,

где X — буквенное обозначение параметров;

У, Z подстрочные индексы буквенных обоз-

начений входных и (или) выходных сигналов,

приведенные на условных графических обоз-

начениях соответствующих микросхем; I. J —

цифровые индексы соответствующих входов и

(или) выходов, равные 0, 1. 2....н; л —

число входов и (или) выходов.

Таблица 1.3

Символ Определение

LH

HL

7.Н

//Z

Z.Z

ZL

Переход из состояния низкого уров-

ня в состояние высокого уровня

Переход из состояния высокого уров-

ня в состояние низкого уровня

Переход из состояния «выключено»

в состояние высокого уровня

Переход из состояния высокого уров

ня в состояние «выключено»

Переход из состояния низкого уров

ня в состояние «выключено»

Переход из состояния «выключено»

в состояние низкого уровня

Для обозначения производных динамиче-

ских параметров используется следующая

форма записи:

fAl (В, C—D, Е),

где /А — вид временного параметра; / — по-

рядковый номер параметра. /=1, 2..... п;

В наименование сигнала или вывода в со

ответствии с условным графическим обозна

чением микросхемы, относительно которого

ведется отсчет данного вида параметра; С —

направление перехода сигнала В: D наиме-

нование сигнала или вывода в соответствии с

условным графическим обозначением микро-

схемы, до которого ведется отсчет данного

вида параметра; Е направление перехода

сигнала D.

Для символов С, Е используются обозна-

чения в соответствии с табл. 1.3. Первый ин-

декс в буквенном обозначении символов С и

Е опускается; при этом используется сокра-

щенная форма записи временных параметров:

t Л( В-D}, t л-

1.5. Классификация

микропроцессоров

и микропроцессорных комплектов

микросхем

Приведенные в справочнике микропроцес-

сорные интегральные микросхемы могут быть

классифицированы по следующим признакам.

По технологии изготовления — микропро-

цессоры, полученные на основе:

р-МДП-технологии — серии К145ИК18,

К145ИК19. KI814;

п-МДП-технологии — серии КР580, КР581,

К1801, К1809, КМ1810, КН1811, КМ1813,

КР1816;

КМДП-технологии — серии КР587, К588;

ТТЛДШ-технологни—серии К589, К.Р1802.

КМ 1804;

И2Л-технологи и — серии К583, К584,

КА 1808;

ЭСЛ-технологии — серия К1800.

По типу архитектуры микропроцессоры

можно разделить на секционные и однокрис-

тальные, а также однокристальные микро-

ЭВМ.

Секционный микропроцессор предназначен

для обработки нескольких разрядов данных

(часть микропроцессора); он обладает сред-

ствами достаточно простого функционально-

го объединения с однотипными или другими

микропроцессорными секциями для построе-

ния законченных микропроцессоров и микро-

ЭВМ. Управление таким микропроцессором

осуществляется микропрограммным способом.

К секционным М11К микросхем следует отнес-

ти серии К583, К584, КР587. К589, К1800,

КР1802, КМ 1804.

Однокристальный микропроцессор — про-

граммно управляемое устройство с фиксиро-

ванной системой команд, осуществляющее

16

процесс обработки цифровой информации с

фиксированной разрядностью и управления

им, построенное на одной интегральной мик-

росхеме. Как правило, для расширения функ-

циональных возможностей однокристального

микропроцессора его дополняют другими ти-

пами микросхем. Однокристальный микропро-

цессор является ядром МПК. К однокристаль-

ным микропроцессорам следует отнести серии

КР580, КР581, К588. K180I. KAI808. КМ1810.

КН181 I.

Однокристальная микро-ЭВМ микросхе-

ма. содержащая кроме микропроцессора с

фиксированной разрядностью оперативную и

(или) постоянную память. К однокристаль-

ным микро-ЭВМ следует отнести серии

К145ИК18. К145ИК19, КМ1813. К1814.

КР1816.

По назначению различают универсальные

и специализированные микропроцессоры. Уни-

версальные МП могут быть использованы в

различных видах вычислительной техники и

цифровой автоматики. На специализирован-

ных МП может быть построен лишь опреде-

ленный класс аппаратуры. К универсальным

следует отнести МПК серий КР.г>80. КР581.

К583. К584. КР587. К588. К589. К1800.

К1801. КР1802, КМ1804. К1809, КМ1810.

КП1811. КМ1813, КР1816. к специализирован-

ным — К145ИК18. К145ИК19. КЛ18О8. K18I4.

По разрядности данных, обрабатываемых

микросхемой, все МПК можно разделить на:

2-разрядные — серия К589;

4-разрядные—серии К145ИК18. К145ИК19,

К584, КР587, К1800, KMI804. KI8I4;

8-разрядные — серии КР580. К583. КР1802.

KPI816, KM18I3;

lb-разрядные серии КР581. К588, KI8OI.

KI809, KMI810. КН1811.

По виду обрабатываемой информации мик-

ропроцессоры могут быть разделены на циф-

ровые и аналоговые. В цифровых МП прием,

обработка и выдача информации ведутся в

цифровой форме. В аналоговых МП информа-

ция поступает на вход в аналоговой форме, а

затем преобразуется в цифровую и в таком

виде обрабатывается микропроцессором. Ре-

зультаты обработки преобразуются в анало-

говую форму и поступают на выход. Из рас-

смотренных в справочнике аналоговым сле-

дует считать МП серии КМ1813. все осталь-

ные — цифровые.

По виду временной организации работы

микропроцессорные комплекты микросхем

подразделяются на синхронные и асинхрон-

ные. В синхронных МП начало и конец вы-

полнения команд задаются устройством уп-

равления. Время выполнения команд при

этом не зависит от их вида и величин опе-

рандов.

В асинхронных микропроцессорах начало

выполнения каждой следующей команды оп-

ределяется по сигналу фактического оконча-

ния выполнения предыдущей операции.

По числу одновременно выполняемых про-

грамм микропроцессоры разделяются на одно-

и много- или мультипрограммные. В одно-

программных МП выполняется одна програм-

ма, переход к исполнению следующей прог-

раммы происходит после завершения преды-

дущей. В много- или мультипрограммных

микропроцессорах одновременно выполняют-

ся несколько программ.

Глава 2

Микропроцессоры серий К145ИК18, К145ИК19

Микропроцессоры серий К145ИК18,

К145ИК19 принадлежат к разряду специали-

зированных однокристальных микро-ЭВМ.

«поведение» которых однозначно определяет-

ся хранимой в ПЗУ программой. Главная

программа хранится в ПЗУ команд. Управля-

ющие сигналы, обеспечивающие выполнение

элементарных действий над обрабатываемой

информацией, находятся в ПЗУ микрокоманд.

Между главной программой и микроко-

мандами образован уровень синхропрограмм.

которые обрабатывают информацию в микро-

схеме с привязкой к временным интервалам,

вырабатываемым счетчиком тактов.

Использование выходов разной кратности

счетчика тактов позволяет строить различные

системы временной адресации, в которых

обеспечивается синхронизация потоков управ-

ляющей и обрабатываемой информации. Та-

кая структура микросхем серии KI45 позво-

ляет хорошо адаптироваться к внешним уст-

ройствам по формату команд и временным

характеристикам.

Все микросхемы серии KI45 по степени

универсальности их использования подразде-

ляются на две группы: специализированные,

работающие по программе, занесенной во

внутреннюю память микросхемы при ее изго

товлении, и широкого применения, программа

работы которых заносится во внешнее ЗУ и

может изменяться самим пользователем (в

случае применения ОЗУ или НПЗУ) или по

картам-заказам, составленным пользователем

(в случае применения ПЗУ).

Характерной особенностью К145ИК18 яв-

ляется наличие программно-аппаратных

средств, обеспечивающих функции универсаль-

ного микроконтроллера с пространственно-

временной адаптацией к параметрам внешних

устройств.

Микросхема К145ИК19, обладая возмож-

ностями К145ПК18. имеет дополнительные ап-

' 17

парадные средства для удобства отсчета точ-

ного времени и управления внешними устрой-

ствами, но с более коротким форматом ко-

манд (меньшее число портов ввода/вывода.

меньше выходов временных интервалов Д);

число разрядов регистров оперативной памя-

ти равно 64.

Обобщенная структурная схема микро-

схем серии К145 с наиболее характерными

связями приведена на рис. 2.1.

В состав микросхем входят:

три блока постоянной памяти: ПЗУ ко-

манд (ПК), емкость К145ИК18 128 19-би-

товых слов, К145ИК19 128 20-битовых

слов; ПЗУ синхропрограмм (ПС), емкость

К145ИК18 — 32X6X3X5 бит [блоки по 32

5-битовых слова, адресуемые 18-ю варианта-

ми (6X3) комбинаций составляющих времен-

ного адреса Ej и Д*|. емкость К145ИК19 —

16Х5Х2ХЮ бит; ПЗУ микрокоманд (ПМК).

емкость К145ИК18 — 40 26-битовых слов,

К145ИК19 — 32 16-битовых слова;

блок оперативной памяти (ОН или ОЗУЧ

два динамических сдвиговых регистра, ем-

кость К145ИК18 — 36 4-битовых слов.

К145ИК19 16 4-битовых слов;

арифметико-логическое устройство X, ис-

полняющее мИкроприказы выходного слова

ПМК, указывающего возможные источники

или приемники для выполнения операций в

АЛУ и пересылок в блоке оперативной памя

ти. В составе АЛУ имеются регистры общего

назначения: К145ИК18 — два регистра емко-

стью 1X4 бит и 3X4 бит, К145ИК19 — четы-

ре регистра, емкость каждого 4 бита. Второй

регистр имеет внешние входы в каждый раз-

ряд. стробируемые временным сигналом син-

хронизатора (В1 — для К145ИК18 и В2 —

для К145ИК19). Третий и четвертый регист-

ры (в К145ИК19) имеют внешние выходы;

регистры адреса: РАК. РАПС. РАМК.

РАОП;

регистры слова: РСК, РСПС, РС.МК;

регистр синхронизации PCX.

Коммутация связей верхнего уровня осу-

ществляется регистром РСК. Формат слова в

РСК состоит из четырех полей:

адресного поля — АП. которое может не-

посредственно указывать следующий адрес

блока памяти ПК или использоваться как па-

раметр при его вычислении;

Рис. 2.1. Обобщенная структурная схема

микросхем серий К145ИК18, К145ИК19

поля кода условия программного ветвле

ния в блоке ПК ПК'УС, указывающего на

способ формирования исполнительного адре-

са;

адресного поля синхропрограммы АСП,

входящего в состав полного адреса блока па-

мяти ПС;

поля кода модификации синхропрограм.

мы — IIKOM, составляющего совместно с

АСП полный адрес блока памяти ПС.

Регистр PCX выдает информацию о вре-

менном компоненте полного адреса операнда.

В структурной схеме микросхем серии

К145 дополнительными программно-аппарат-

ными средствами организован блок ввода/вы-

вода. который содержит:

входы Wil, WI2, устанавливающие соот-

ветствующие разряды регистра адреса РАК.

бит Т регистра состояния — признак включе-

ния клавиши, а также управляющие програм-

мным ветвлением. Эти входы стробируются

временным сигналом синхронизатора В4;

порты ввода (для К145ИК19 один, для

К145ИК18 — три 4-битовых регистра);

порты вывода (для К145ИК19 — два, для

К145ИК18 — шесть 4-битовых регистров).

Управление портами выполняется с ио

мощью шифратора матричного типа (для

К145ИК19 — шифратора данных размером

16X8 бит, для К145ИК18 ш фратора ад-

ресов данных размером 9X16 бит).

Синхронизатором микросхем является ре

гистр PCX счетчик тактов, формирующий

младшие разряды системы временной адреса-

ции (сигналы В,, Е,. Дь). Временная диаг-

рамма работы микросхем показана на рис. 2.2.

Более крупные элементы временной шкалы

или старшие разряды временной адресации

могут быть построены программистом систем

ного математического обеспечения

Синхронизирующие импульсы Bi, Ej, Д>, '

формируются на базе тактовых импульсов,

которые вырабатываются генератором четы

рех фазовых сигналов (Ф1—Ф4)- Период ра

боты генератора фаз определяет временной

интервал В, обработки и пересылки одного

двоичного разряда информационного слова.

Временной интервал соответствует дли

тельности обработки или пересылки четырех

двоичных разрядов информационного слова

тетрады, т. е. Ej —В14-В24-ВЗ +В4. Такие

временные интервалы удобны и для обработ-

ки информации в двоично-десятичном пред

ставлении. Число временных интервалов Е,

выбрано исходя из среднего числа микроко-

манд, необходимых для завершения обработ-

ки одной тетрады операнда. Например, для

работы с операндами с десятичной коррек-

цией достаточно три интервала Е,(Е1—Е3).

Совокупность интервалов Ej образует вре-

менной интервал Дь. Число временных интер-

валов Дк может определяться разрядностью

операндов и формой их представления. При

обработке данных в режиме с плавающей за-

пятой для 8-разрядной двоично-десятичной

мантиссы со знаком и 2-разрядного порядка

18

Рис. 2.2. Временная диаграмма работы микросхем серин К145ИК18, К145ИК19

со знаком необходимо иметь 12 временных

интервалов Дь.

Тактирование микросхем серии К145 осу-

ществляет внутренний 4-фазный генератор.

Встроенный синхронизатор микросхемы име-

ет период работы, равный 2s периодам рабо-

ты тактового генератора.

Циркуляция информации в ОП соответст

вует циклу работы синхронизатора. Это поз

воляет разработать математическое обеспече-

ние отсчета различных временных интервалов

с использованием стандартного кварцевого

резонатора с частотой 215 Гц.

Состав серии микросхем К145, их модифи-

кации. назначение и области применения при-

ведены в табл. 2.1.

Микросхемы серии К145 выполняются в

прямоугольном пластмассовом корпусе

Таблица 2.1

Модификация микро схем серии К145 Функциональное назначение Область применения

К745ИК1801-2 Микроконтроллер, обеспечивающий функ- ции управления и обработки данных при обмене информацией между последова- тельным однобитовым каналом связи про- граммируемого калькулятора типа «Электроника МК-54» в режиме прямого доступа и адресуемой памятью с произ- вольной выборкой Контрольно-измерительн ые комплексы

К145ИК1807 Микроконтроллер для программного уп- равления электробытовыми приборами, режимами, процессами, роботами Стиральные машины. печи СВЧ. холодильники, роботизи- рованные комплексы, автомати- зация технологических процес- сов

К145ИК1809, Эмуляторы центрального процессора 16- Микро-ЭВМ для сбора данных.

К145ИК1810 разрядной микро-ЭВМ индивидуального пользования, имеющие широкий набор команд и гибкую систему адресации с быстродействием 250 операций/с учебная микро-ЭВМ. програм мируемый микрокалькулятор

19

Окончание табл. 2.1

К145ИК1812 К145ИК1814 К145ИК1901 К145ИК1906 К145ИК1907 К145ИК1908 К145ИК1914 К145ИК1915 Микроконтроллер для управления узлами минитермопринтера при приеме информа- ции от вычислительных устройств на базе микросхемы К145ИК13 Микроконтроллер для управления диспле- ем. звуковым сигнализирующим устройст- вом и клавиатурой микрокалькулятора «Электроника МК-72» Микросхема для многофункциональных электронных часов с будильником и секун- домером Микроконтроллер в составе систем автома- тического управления (САУ) и регулиро- вания, обеспечивающий автоматическое из- менение параметров (режимов работы) управляемого объекта Микроконтроллер, работающий в режиме таймера, программатора, для управления технологическими процессами, оборудова- нием. бытовой электронной техникой с при- вязкой к реальному времени, выраженному в часах и минутах Микроконтроллер, работающий в режиме танмера/программатора. для управления технологическими процессами, оборудова- нием. бытовой электронной техникой с при- вязкой к реальному времени, выраженному в минутах и секундах Микроконтроллер, выполняющий функции автономного счетчика/таймера, для отсчета дискретных значений параметра с привяз- кой к реальному времени, выраженному в минутах и секундах Микроконтроллер для управления работой электропроигрывателя высшего класса Сервисное устройство к микро- калькуляторам типа «Электро- ника БЗ 34» «Электроника МК-49» В составе однокристальной микро-ЭВМ, совместно с цент- ральным процессором на базе микросхем К145ИК1819. К145ИК1810 Электронные часы типа «Элек- троника Гб 11»; система опо- вещения и сигнализации, уп- равления электро и радиоап паратурой и технологическим оборудованием по заданной временной программе Управление режимами работы бытовых магнитофонов. Мани- пуляторы, управляющие пере- мещением объекта или загруз- кой емкостей некоторыми ве- ществами Реле времени. электронные регламентаторы времени, уст- ройства управления кухонным комплексом, системы управле- ния технологическими процес- сами Электронные регламентаторы времени, реле времени, систе мы управления технологически- ми процессами Управление лентопротяжным механизмом магнитофона, контроль расхода ленты, теку щего времени, счетчики оборо- тов Электропроигрыватели выс- шего класса. Управление линей ными перемещениями по сиг- налам датчиков

244.48-5, некоторые их модификации выпуска-

ются в бескорпусном исполнении с понижен-

ным напряжением питания. Условное обозна-

чение бескорпусных микросхем К745.

При эксплуатации микросхем необходимо

применять методы защиты их от воздействия

статического электричества. Допустимое зна-

чение статического потенциала, воздействую-

щего на любой из выводов микросхемы, не

более 30,0 В.

Замену микросхем при ремонте аппарату-

ры, установку их в контактные приспособле-

ния и извлечение из этих приспособлений сле-

дует производить при отсутствии напряжений

на выводах

Подключение любых электрических цепей

ко всем незадействованным выводам заире

щается.

Микросхемы в блоках аппаратуры, предназ-

наченной для работы в условиях повышенной

влажности, необходимо покрывать двумя сло-

ями влагозащитного лака УР-231 или.ЭП-730.

Температура сушки лака не более 328 К

(55° С).

Электрические параметры микросхем се-

рий К145ИК18 и К145ИК19 приведены в

табл. 2.2, предельные электрические режимы

эксплуатации в диапазоне температур — в

табл. 2.3.

20

Таблица 2.2

Окончание табл. 2.3

Параметр Обозначение Значение параметров

К145ИК18 К145ИК19

X X s X ro 7. X 2 о X го X

Напряжение пита- ния. В Uoc 25,6 28.4 24,3 29,7

Напряжение низкого уровня тактовых сиг- налов. В UCL 25,6 28,4

Напряжение высоко- го уровня тактовых сигналов. В иСН 0 0.5

Входное напряжение низкого уровня, В “lL 8.5 28.4 8,5 30,0

Входное напряжение высокого уровня, В Выходное напряже- ние низкого уровня на выходах. В: UlH 0 2.0 0 2,0

SYN. RG UOL 9,5 — 9.5 —

ORG. GN 9.5 — 9.5 —

CORI COR4 25.0 — 27.0 —

COSI — COS8 25.0 — 27,0 —

СО! - СО8 Выходное напряже- ние высокого уровня на выходах. В: 25,0 27,0

ST.V. RG UOH — 2,0 — 2,0

ORG. GN — 2,0 — 2,0

CORI — COR4 1 , 0 — 1 ,3

COS1 - COSS — 1 . o — 1 , з

COl COS » 1 . o — 1 . з 8.0

Ток потребления ди- намический, мА 'cco 2,0 —

Период следования импульсов тактовых сигналов, мкс Длительность им- пульсов тактовых сигналов на входах, мкс: TCLC 5 1 4

Uct Uc3 Pc 0 --- —— —•

Uc2, Uc« GNI, GN3 Сопротивление на грузки для выходов. кОм; 1 . 8 — — —

3,0 6,0

SYN. RG 1000 — 1000 —

ORG. GA 1 000 — 1000 —

CORI COR4 27 ^4 30 —

COSI COSS 27 — 30 —

COl— сов 27 30

Параметр Обозна- чен не Значения парамет- ров

1q max

Максимальный ток, вытека

ющий по общему выводу

при положительных напря

жениях на остальных выво-

дах, мА

Максимальная рассеива

емая мощность, мВт

Р tot

250,0

Примечание. Эксплуатация микросхем в

предельных режимах не допускается

2.1. Микросхема К745ИК1801-2

Микросхема К745ИК1801-2 предназначена

для управления обменом информацией между

программируемым калькулятором типа «Элек-

троника МК-54» и регистрами адресуемой па

мяти с произвольной выборкой.

Микросхема обеспечивает обработку дан-

ных при обмене информацией по однобитово-

му каналу связи в режиме прямого доступа.

Микросхема выпускается в бескорпусном ис-

полнении.

Условное графическое обозначение микро

схемы приведено на рис. 2.3, назначение вы-

водов в табл. 2.4.

Типовая схема включения К745ИК1801-2

показана на рис. 2.4.

Примечания. I Все напряжения отрица-

тельной полярности. 2. Поминальное значение напря-

жения питания К145ИК18 и К145ИК19 27,0 В.