Text

МИКРОПРОЦЕССОРЫ

И МИКРОКОМПЬЮТЕРЫ

MICROPROCESSORS/MICROCOMPUTERS

An Introduction

DONALD D. GIVONE

Associate Professor of Electrical Engineering

State University of New York at Buffalo

ROBERT P. ROESSER

Associate Professor of Electrical Engineering

University of Detroit

McGraw-Hill Book Company

New York St. Louis San Francisco Auckland Bogota

Dusseldorf Johannesburg London Madrid Mexico

Montreal New Delhi Panama Paris S3o Paulo

Singapore Sydney Tokyo Toronto

1980

Д. Гивоне, Р. Россер

Микропроцессоры

и микрокомпьютеры.

Вводный курс

Перевод с английского

В. С. ШТАРКМАНА и Т. А. ШАРГИНОЙ

под редакцией

В С. ШТАРКМАНА

МОСКВА «МИР» 1983

ББК 32.97

Г43

УДК 681.3

Гивоне Д., Россер Р.

Г46 Микропроцессоры и микрокомпьютеры: Вводный курс: Пер.

с англ.—М.: Мир, 1983.— 464 с., ил.

Систематическое и полное введение в логическую структуру и программирование

микропроцессоров, написанное американскими специалистами. Подробно рассмотрена

архитектура микропроцессоров, даны примеры программ и интерфейсов

Для программистов, работающих с вычислительными системами на основе микро-

процессоров, для студентов, изучающих ЭВМ и их математическое обеспечение.

2405000000-208

1 041(01)-83

19-83, ч. 1

ББК32.973

6Ф7.3

Редакция литературы по математическим наукам

© 1980 by McGraw-Hill, Inc. All rights reserved

© Перевод на русский язык, «Мир», 1983

ОТ РЕДАКТОРА ПЕРЕВОДА

Общепризнано, что микропроцессоры — это принципиальный шаг

в развитии средств электронной автоматики и обработки данных.

Микропроцессоры очень дешевы, компактны, обладают программным

управлением и отличаются высоким быстродействием. Такое соче-

тание свойств позволяет на единой технологической и схемотехни-

ческой базе, т. е. только за счет программирования, получить специа-

лизированные вычислительные устройства, пригодные для исполь-

зования в науке, на производстве, на транспорте, в медицине, в быту

и многих других сферах.

Применение микропроцессоров в различных системах, где требу-

ется сбор, передача, обработка и отображение информации, позволяет

подняться на принципиально новый уровень по таким показателям,

как надежность и простота обслуживания систем, с одной стороны,

а также полнота и сложность выполняемых ими функций, с другой.

На микропроцессорной базе созданы и выпускаются «миллион-

ными тиражами» так называемые персональные (в частности, «кухон-

ные») компьютеры, причем, как отмечают многие авторы, социальные

последствия этого явления, видимо, окажутся соизмеримыми с по-

явлением книгопечатания, конвейерного производства или автомобиля.

Нет ничего удивительного, что по микропроцессорам и микро-

ком пьютерахМ публикуется так много самых разнообразных книг.

Какое место среди них занимает эта книга?

Прежде всего нужно отметить, что авторы не требуют от читателя

предварительной подготовки ни в электронике, ни в программиро-

вании. Для чтения книги достаточно общих знаний по элементарной

физике и математике. Книга действительно является введением в

предмет. Но это введение фундаментальное, в нем рассматриваются

достаточно глубоко многие ключевые вопросы.

В отличие от других книг, здесь изложены основные понятия без

привязки к конкретным промышленным образцам микропроцессоров.

Книгу отличает четкость и методичность изложения, наличие упраж-

ОТ РЕДАКТОРА ПЕРЕВОДА

нений в каждой главе, прекрасное оформление графического мате-

риала. Особо стоит отметить, что авторам удается подвести читателя

к пониманию многих сложных и тонких проблем, излагая материал

просто и понятно на удачно подобранных примерах.

Эта книга будет несомненно полезной преподавателям и студентам

многих специальностей. Она будет также полезна широкому кругу

инженеров и научных работников, связанных с разработкой и приме-

нением микропроцессорных систем в вычислительных, измерительных

и управляющих комплексах.

В. Штаркман

ПРЕДИСЛОВИЕ

С момента изобретения интегральных схем в 1959 г. непрерывно

растет интерес к созданию электронных устройств, способных вы-

полнять сложные функции. Одним из наиболее впечатляющих резуль-

татов применения интегральной технологии явилось создание в 1971 г.

микропроцессора. Хотя первоначально микропроцессоры были всего

лишь «кристаллами» для карманных калькуляторов, очень быстро

стали понятны их огромные потенциальные возможности при ис-

пользовании в качестве «сердец» специализированных цифровых

процессоров, что объясняется прежде всего их низкой стоимостью

и способностью выполнять программы. По существу, центральное

обрабатывающее устройство цифрового компьютера оказалось за-

ключенным в одной большой интегральной схеме.

Цель данной книги — познакомить читателя с основными прин-

ципами построения компьютеров, и главным образом с функциони-

рованием и применением микропроцессоров и микрокомпьютеров.

В книге подробно рассматриваются те базовые понятия, которые

важны при проектировании большинства систем с микрокомпьютерами.

В число этих понятий входит архитектура микрокомпьютеров, струк-

тура памяти, средства ввода/вывода, интерфейсы и программирование.

Мы не предполагали, что читатель обладает предварительной подго-

товкой в области электронных вычислительных машин. Чтобы сделать

изложение замкнутым, были включены разделы по системам счис-

ления, булевой алгебре и электронным схемам. Предполагаются

только некоторые познания в электротехнике.

Вероятно, наиболее трудное для нас решение при написании книги

было связано с выбором микропроцессора для иллюстративных целей.

Поскольку мы руководствовались целью разъяснить основные прин-

ципы устройства и работы микрокомпьютера, нам показалось более

предпочтительным не привязывать изложение к какому-либо кон-

кретному микропроцессору, производимому промышленностью. Мы

надеемся, что при таком подходе микропроцессор сам по себе не за-

слонит фундаментальных принципов, на которых основаны микропро-

цессоры вообще. Можно было бы включить раздел по микропроцес-

сорам, имеющимся на рынке, но мы решили, что эти сведения лучше

получать от фирм-изготовителей.

8

ПРЕДИСЛОВИЕ

Материал книги соответствует односеместровому курсу для сту-

дентов как младших, так и старших курсов в институтах, готовящих

специалистов в области электроники или вычислительной техники.

Благодаря замкнутости изложения книга вполне годится для само-

стоятельного изучения. Вероятно, часть материала в гл. 2—4 сов-

падает с материалом, который студенты получают на предшествующих

курсах. Тем не менее материал в этих главах изложен достаточно

детально; это обеспечивает полноту изложения и делает книгу полез-

ной для читателей с различным уровнем подготовки. Естественно,

некоторые разделы в этих главах при чтении можно опустить.

Хотелось бы выразить благодарность многим людям, которые

помогали нам и вдохновляли нас во время работы над книгой. Осо-

бенно мы признательны нашим детям, которым не легко было понять,

почему родители, работая над книгой, не могут уделить им достаточно

времени. Мы надеемся, они будут вознаграждены тем, что наши до-

стижения «сегодня» сделают более светлым их «завтра». В заключение

мы выражаем нашу признательность г-же Мэрилин Хатчингс за кро-

потливую работу по перепечатке окончательного варианта рукописи.

Дональд Д. Г неоне

Роберт П. Россер

Глава I. МИКРОПРОЦЕССОРЫ И

МИКРОКОМПЬЮТЕРЫ: ОБЩИЕ СВЕДЕНИЯ

Микропроцессоры — это новые удивительные логические устрой-

ства, оказывающие заметное влияние на нашу жизнь. Микропроцес-

соры можно обнаружить в карманных калькуляторах, в кассовых

аппаратах магазинов, в бытовых и научных приборах, в оборудовании

контор, в медицинском оборудовании, в телеиграх — и это далеко

не полный перечень их применения. Более того, каждый день нахо-

дятся новые приложения и разрабатываются новые изделия на основе

микропроцессоров. Их потенциальное воздействие на нашу жизнь

почти не поддается воображению. Эта книга знакомит читателя с

функционированием микропроцессоров и более крупных систем,

содержащих в себе микропроцессоры. Для такого знакомства нужно

в определенном объеме осветить принципы проектирования логиче-

ских устройств, некоторые вопросы электроники и программирования.

Овладение соответствующими понятиями и принципами позволит

успешно пользоваться новыми логическими устройствами.

В этой главе сообщаются общие сведения о функционировании и

структуре микропроцессоров и микрокомпьютеров. По ходу изло-

жения вводится терминология. Цель главы — дать читателю возмож-

ность прочувствовать многочисленные относящиеся к микропроцес-

сорным системам понятия и их взаимосвязь. В последующих главах

они детализируются более конкретно. Однако общая картина, сложив-

шаяся по материалу этой главы, позволит читателю полнее осознать

устройство и работу микропроцессорных систем.

1.1. НОВАЯ ЭРА ВЫЧИСЛЕНИЙ

С 1951 года, когда был создан первый производимый промышлен-

ностью компьютер (Univac I), ЭВМ оказывают сильное влияние на

наше общество и образ жизни. Возникла новая отрасль промышлен-

ности. Такие термины, как «цифровые вычисления», «логическое

проектирование» и «программирование», стали научными и инженер-

ными понятиями. Однако широта этих понятий часто приводила к

расхождению интересов. Например, интересы одной группы специа-

листов лежали в использовании ЭВМ и программировании (область

программного обеспечения), другой — в создании ЭВМ (область ап-

паратуры). Хотя такое деление по интересам было, по-видимому,

10

ГЛ 1 МИКРОПРОЦЕССОРЫ и микрокомпьютеры

оправданным в отношении больших вычислительных машин, с мо-

мента появления миникомпьютеров в 1965 году проблемы, с которыми

сталкивались прикладные программисты и конструкторы машин,

стали переплетаться теснее. Миникомпьютеры уже не были всецело

предназначены для обработки данных и решения задач; зачастую

они входили как составные части в системы, требовавшие быстрого

принятия решения,— системы реального времени.

С появлением в 1971 году микропроцессоров расхождение инте-

ресов еще более уменьшилось. Началась эра программируемой ло-

гики. В эту эру понятия программирования и принципы проекти-

рования логических схем сблизились настолько, что их взаимопро-

никновение потребовало и от ученых, и от инженеров полного пони-

мания как принципов программирования, так и аппаратуры. Только

при этом условии можно было успешно использовать все заложенные

в микропроцессорах возможности. Мы видели свою цель именно

в том, чтобы осветить эти принципы и их взаимосвязь, и мы надеемся,

что читатель сможет составить себе достаточно полное представление

об устройстве и потенциальных возможностях микропроцессоров.

1.2. МИКРОПРОЦЕССОРЫ И МИКРОКОМПЬЮТЕРЫ

Поскольку книга посвящена микропроцессорам и микрокомпью-

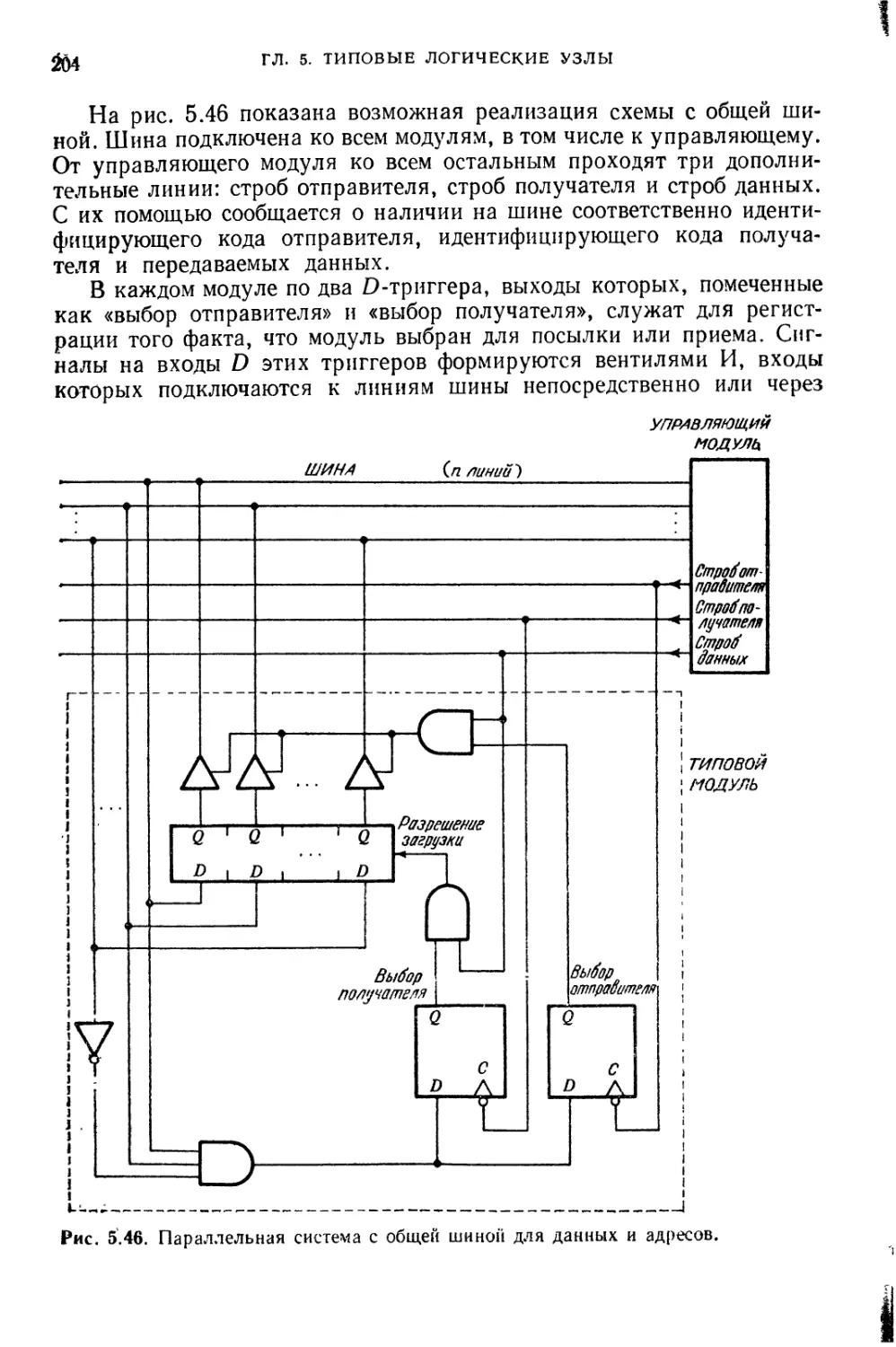

терам, начнем с определения этих двух терминов. Дать строгое, ис-

черпывающее определение практически невозможно, поскольку мик-

ропроцессоры и микрокомпьютеры связаны с динамично развиваю-

щейся технологией, и изменения технологии, возможно, вызовут из-

менения в определениях.

Одно из достижений технологии полупроводников заключается

в создании больших интегральных схем (БИС), т. е. схем, позволя-

ющих размещать большое число транзисторов, скажем 1000 или более,

на одной кремниевой подложке (на одном «кристалле»). Это называют

высокой степенью интеграции. Собственно, высокая степень инте-

грации и привела к микропроцессорам.

Микропроцессор, грубо говоря, это программируемое логическое

устройство, изготовленное по БИС-технологии. Как мы увидим в

дальнейшем, в конструкцию микропроцессора заложена большая

гибкость. Сам по себе он не может решить ту или иную конкретную

задачу. Чтобы решить задачу, его нужно запрограммировать и сое-

динить с другими устройствами. В их число обычно входят память

и устройства ввода/вывода. Вообще говоря, некоторая совокупность

соединенных друг с другом системных устройств, включающая мик-

рокомпрессор, память и устройства ввода/вывода, нацеленная на

выполнение некоторой четко определенной функции, называется

микрокомпьютером или микропроцессорной системой.

Хотя микрокомпьютеры обладают всеми свойствами обычных

ЭВМ, замечательная их особенность состоит в относительно низкой

1.3. ТИПОВАЯ СТРУКТУРА МИКРОКОМПЬЮТЕРА

11

стоимости и малом размере. Именно этому они обязаны своей попу-

лярностью и успехом. Большие ЭВМ и миникомпьютеры обладают,

конечно, большей вычислительной мощью, но не для всех приложений

эта мощь оказывается необходимой. Более того, стоимость больших

компьютеров и миникомпьютеров часто не позволяет включать их

в системы, где они могли бы многое дать. Микропроцессоры открывают

возможность для применения программируемых устройств в тех

логических системах, для которых фактор стоимости оказывается

важнее, чем скорость и разнообразие вычислений.

Каждый день открываются новые области приложений для мик-

ропроцессоров. В настоящее время они используются в контрольно-

измерительных приборах, в кассовых аппаратах магазинов, в интел-

лектуальных терминалах и карманных калькуляторах. Они оказы-

ваются жизненно важнььм элементом в управлении станками, хими-

ческими процессами, периферийными устройствами больших компью-

теров, в управлении уличным движением, сложными бытовыми элект-

роприборами и автомобилями. Наконец, в области развлечений и

досуга благодаря этим устройствам возникло новое хобби — строить

свои собственные компьютеры.

1.3. ТИПОВАЯ СТРУКТУРА МИКРОКОМПЬЮТЕРА

Типовая компьютерная система включает пять функциональных

блоков: устройство ввода, память, арифметическое устройство, уст-

ройство управления и устройство вывода. Пример такой системы при-

веден на рис. 1.1.

Физические компоненты и схемы, составляющие микрокомпью-

тер,— это его аппаратура (hardware). Аппаратура способна выпол-

нять только ограниченный набор элементарных операций. Все прочие

функциональные возможности микрокомпьютера достигаются про-

граммным путем. Программа — это определенным образом органи-

зованная совокупность элементарных машинных операций, называ-

емых командами или инструкциями, с помощью которых осуществ-

ляется обработка информации, или данных. Программы, написанные

для компьютера, образуют его программное обеспечение (software).

Программа и данные сначала накапливаются в памяти, куда они

поступают через устройство ввода. Затем отдельные команды про-

граммы одна за другой автоматически поступают в устройство управ-

ления, которое их расшифровывает и выполняет. Для выполнения

операции обычно требуется, чтобы данные поступили в арифметическое

устройство, содержащее все необходимые для их обработки схемы.

В процессе вычислений или после их завершения полученные резуль-

таты направляются в устройство вывода. Арифметическое устройство

и устройство управления вместе обычно называются центральным

процессорным устройством (ЦПУ) или центральным процессором

12

гл. 1 МИКРОПРОЦЕССОРЫ и микрокомпьютеры

----- Информационные сигналы

—---_ Сигналы управления и адресации

Рис. 1.1. Принципиальная организация компьютера.

(ЦП). Центральный процессор в микрокомпьютерной системе это и

есть микропроцессор.

Не только память, но и другие устройства ЭВМ способны хранить

информацию. Информация запоминается как содержимое групп дво-

ичных разрядов — битов — на запоминающих устройствах — ре-

гистрах. По существу, любую операцию в ЭВМ можно рассматривать

как серию передач информации между регистрами с возможным ее

преобразованием (например, сложением), выполняемым в процессе

передач. Группа двоичных цифр, обрабатываемых одновременно,

называется машинным словом, а число двоичных цифр, составляющих

слово, называется длиной слова. Слово является базовой логической

единицей информации в компьютере. Команды или данные обычно

состоят из одного или нескольких слов. Типичные микропроцессоры

имеют длину слова 4, 8, 12 или 16 двоичных разрядов. В силу особой

распространенности слово длиной 8 бит имеет специальное название —

байт.

Память

Запоминание больших объемов информации происходит в памяти,

или, точнее, в запоминающем устройстве (ЗУ). Этот функциональный

блок компьютера подразделяется на подблоки, называемые регист-

рами, каждый из которых способен хранить одно машинное слово.

Каждый такой регистр, или ячейка памяти, имеет свой адрес. Адрес —

1.3. ТИПОВАЯ СТРУКТУРА МИКРОКОМПЬЮТЕРА

13

это просто целое число, однозначно идентифицирующее ячейку. Слово,

хранящееся в ячейке, называют содержимым этой ячейки.

Итак, как данные, так и программа хранятся в памяти. Это важное

обстоятельство приводит к двум основным концепциям проектиро-

вания компьютеров. Первая заключается в том, что компьютер имеет

два отдельных и четко различающихся вида памяти. Программа

находится всегда в одной памяти, а данные — в другой. Машины,

спроектированные в соответствии с концепцией разделения памяти

на два вида, называют машинами гарвардского типа.

В соответствии со второй концепцией различие между программной

памятью и памятью для данных не проводится, и соответствующие

компьютеры называют машинами фон-Неймановского или принстон-

ского типа. В них программа может размещаться в любом месте общей

памяти, и задача программиста — следить за тем, чтобы данные и

программа обрабатывались по-разному. Преимущество второй кон-

цепции — в возможности трактовать программу как данные, что

позволяет компьютеру изменять свои собственные команды. Сущест-

вуют микропроцессоры, спроектированные в соответствии как с пер-

вой, так и со второй концепцией. В этой книге мы будем рассматривать

машины фон-Неймановского типа.

Благодаря низкой стоимости микропроцессоры часто предназна-

чаются для решения одной конкретной задачи. Большие универсаль-

ные ЭВМ постоянно перепрограммируются и поэтому могут решать

задачи широкого спектра. Микропроцессорам, специализированным

для одного конкретного приложения, такая гибкость не нужна. Од-

нажды написанная и отлаженная программа в дальнейшем обычно

не изменяется. Поэтому такие микрокомпьютеры часто имеют два

вида памяти: память, из которой возможно только считывание (ROM —

read-only memory), или постоянная память, и память со считыванием

и записью (RWM — read/write memory)?). Изменить информацию,

однажды записанную в постоянную память, сложно, если вообще

возможно. Память этого типа благодаря своей низкой стоимости ис-

пользуется для хранения программ и постоянных данных; изменяю-

щаяся информация хранится в памяти со считыванием и записью * 2 3).

Стало общепринятым память со считыванием и записью называть памятью с про-

извольной выборкой (RAM — random-access memory), несмотря на то что и память

только со считыванием также обладает произвольностью выборки. Термин «произволь-

ная выборка», или «произвольный доступ», соответствует тому факту, что обращение к

любой ячейке выполняется за одно и то же время.

2) В качестве русских эквивалентов сокращениям RAM, RWM и ROM часто ис-

пользуются ЗУПВ — запоминающее устройство с произвольной выборкой, ОЗУ —

оперативное запоминающее устройство и ПЗУ — постоянное запоминающее ус-

тройство.— Прим, перев.

3) Читателю следует обратить внимание на то, что из наличия постоянной памяти

не следует, что машина относится к гарвардскому типу. В машине фон-Нейманов-

ского типа ячейки ROM (только для считывания) могут появляться, где угодно в па-

мяти. Главное то, что микропроцессору «безразлично», откуда он получает информа-

цию - из ROM или RWM.

14

ГЛ 1. МИКРОПРОЦЕССОРЫ И МИКРОКОМПЬЮТЕРЫ

Арифметическое устройство

Обработка данных осуществляется главным образом в арифме-

тическом устройстве. Эта обработка включает как арифметические,

так и логические операции. В гл. 7 будет дано описание типичного

микропроцессора, и мы убедимся, что встроенные операции чрезвы-

чайно элементарны. Более сложные математические действия должны

выполняться с помощью программ, пользующихся встроенными

операциями.

Обычно главный регистр в арифметическом устройстве называ-

ется аккумулятором. В нем, как правило, находится один из операн-

дов перед выполнением операции, и в него же помещается ее резуль-

тат х). Арифметическое устройство часто содержит еще несколько

вспомогательных регистров, называемых рабочими; они упрощают

составление программы.

Арифметическое устройство содержит также признаковые биты,

или флажки. Эти биты содержат информацию, характеризующую

состояние микропроцессора, которое важно для выбора дальнейшего

пути вычислений. Например, может существовать флажок, указы-

вающий на нулевой результат операции. Программист может вос-

пользоваться проверкой этого флажка для принятия решения: если

некоторая операция дала нулевой результат, то будет выполнена одна

последовательность команд, в противном случае — другая. Флаж-

ковые биты, характеризующие результаты операций или каких-либо

проверок, часто размещаются вместе с другой важной информацией

о состоянии машины в специальном регистре, называемом словом

состояния программы (PSW — program status word).

Устройство управления

Устройство управления управляет работой компьютера. Оно

автоматически, последовательно по одной, получает команды из

памяти, декодирует каждую из них и генерирует необходимые для

ее выполнения сигналы. Для того чтобы получить команду из памяти,

устройство управления прежде всего должно знать ее адрес. Обычно

команды выбираются из последовательных ячеек памяти, и их ад-

реса указываются программным счетчиком, находящимся в устройстве

управления. Далее, чтобы иметь возможность декодировать и выпол-

нить текущую команду, ее нужно где-то запомнить. Этой цели в уст-

ройстве управления служит регистр команды.

Для того чтобы быть правильно проинтерпретированной устрой-

ством управления, команда должна иметь определенную структуру,

которую называют форматом команды. У микропроцессоров разных

и В микропроцессорах некоторых типов имеется несколько аккумуляторов, ис-

пользуемых в процессе вычислений и называемых регистрами общего назначения^

1.3. ТИПОВАЯ СТРУКТУРА МИКРОКОМПЬЮТЕРА

15

типов форматы команд различны. Однако есть информация, которая

должна присутствовать в команде в любом случае. Наиболее важное

значение имеет код операции и в некоторых командах адрес. Код

операции — это совокупность двоичных цифр, которые однозначно

определяют операцию, выполняемую в процессе интерпретации ко-

манды. Адресная часть команды (если она присутствует) указывает

на ячейки (например, в памяти), к которым нужно обратиться, вы-

полняя команду. Например, если выполняется операция сложения,

адресная часть команды может указывать на ячейку, где находится

второе слагаемое.

Очень важно, чтобы читатель полностью понимал различные

употребления слова «адрес» и различал адрес ячейки и ее содержимое.

В командах определенного формата существует адресная часть. Это

числовой указатель ячейки, связанной с операндом. Однако команда

сама находится в памяти и, следовательно, имеет связанный с ней

адрес. Как правило, этот адрес не совпадает с адресной частью в самой

команде.

Следующая функция устройства управления — это синхронизация

работы отдельных блоков компьютера. Она осуществляется с по-

мощью генератора тактовых импульсов, или тактового генератора.

Обработка команды занимает несколько периодов тактового генера-

тора. Вообще говоря, команду нужно выбрать из памяти, декоди-

ровать и затем выполнить. Выборка, декодирование и выполнение

распадаются на несколько временных интервалов. Каждый из этих

интервалов, включающих один или большее число периодов тактового

генератора, представляет собой так называемый машинный цикл.

Совокупное время, требуемое для выборки, декодирования и выпол-

нения команды, образует командный цикл, или цикл выполнения ко-

манды.

Устройства ввода/вывода

Последние два блока машины — это устройство ввода и устройство

вывода. Через эти устройства осуществляется контакт компьютера с

внешним миром. Они являются буферами для преобразования инфор-

мации с тех языков и тех скоростей, на которых работает компьютер,

к тем, которые воспринимает человек или другая связанная с компью-

тером система. Устройство ввода получает из внешнего мира данные

и команды, которые поступают в память. Устройство вывода получает

вычисленные результаты и передает их человеку-оператору или другой

системе.

Устройства ввода и вывода представляют собой периферийные

устройства машины. В качестве примера можно назвать перфолен-

точные считыватели/перфораторы и электрические пишущие машинки.

Точки контакта между устройствами ввода/вывода и микропроцес-

сором называются портами ввода/вывода. Порты ввода/вывода также

16

ГЛ. 1. МИКРОПРОЦЕССОРЫ И МИКРОКОМПЬЮТЕРЫ

имеют свои адреса, так что к одному микропроцессору может быть

подключено несколько устройств ввода/вывода.

Характерная особенность цифрового компьютера состоит в том,

что вся информация хранится и обрабатывается в дискретном виде,

т. е. в виде конечных чисел. Часто возникает необходимость со-

пряжения компьютера с другой, системой, не способной обрабаты-

вать дискретную информацию. Недискретная информация называется

аналоговой или непрерывной. В таких случаях приходится осуществ-

лять преобразование из цифровой формы в непрерывную и обратно.

Устройства ввода/вывода, осуществляющие соответствующие преоб-

разования, называются аналого-цифровыми и цифро-аналоговыми пре-

образователями .

На рис. 1.1 устройства ввода/вывода показаны подключенными

непосредственно к арифметическому устройству. Это не единственно

возможный способ подключения. Часто для достижения большей

производительности системы желательно позволить устройствам ввода/

вывода обращаться к памяти непосредственно, а не через арифмети-

ческое устройство. В таком случае говорят о прямом доступе к памяти

(DMA — direct memory access). Организация прямого доступа к

памяти будет рассмотрена в гл. 9.

Шины

Отдельные блоки микрокомпьютера связаны друг с другом с по-

мощью шин. Шина представляет собой совокупность линий, по ко-

торым передается информация от любого из нескольких источников

к любому из нескольких приемников. Одна из распространенных в

микрокомпьютерах структур шин представлена на рис. 1.2.

Рис. 1.2. Шины типичного микрокомпьютера.

1.4 ФУНКЦИОНИРОВАНИЕ МИКРОКОМПЬЮТЕРА

17

На рисунке представлены шины трех типов. Адресная шина одно-

направленная, т. е. информация по ней передается только в одном

направлении. Эта шина служит для передачи адреса от микропро-

цессора к памяти, вводному или выводному устройству. Шина данных

двунаправленная, т. е. информация по ней может передаваться в

обоих направлениях, и она служит для передачи данных. Наконец,

шина управления состоит из линий, по которым передаются тактовые,

синхронизирующие сигналы, а также информация о состоянии (ста-

тусе) устройств. Часть линий в управляющей шине однонаправлен-

ные, часть двунаправленные. Поэтому на рисунке направленность

этой шины никак не обозначена.

1.4. ФУНКЦИОНИРОВАНИЕ МИКРОКОМПЬЮТЕРА

В предыдущем разделе были рассмотрены функции отдельных

блоков компьютера. В этом разделе мы остановимся на взаимодей-

ствии блоков и на динамике информационных потоков.

Устройство управления в процессе функционирования проходит

через три фазы: выборка, декодирование и выполнение. После того

как программа и данные поступили в память, адрес первой выполня-

емой команды помещается в программный счетчик, и в устройстве

управления устанавливается фаза выборки. При этом содержимое

программного счетчика поступает на адресную шину, и тем самым

обеспечивается возможность выборки соответствующей команды из

памяти.

Команда, хранящаяся в ячейке с адресом, заданным на программ-

ном счетчике, посылается по шинам данных в регистр команды в уст-

ройстве управления. Поскольку команды в памяти располагаются

в последовательных ячейках, программный счетчик увеличивается на 1,

и на нем появляется адрес следующего слова в программе. Затем

устройство управления декодирует код операции только что получен-

ной команды. Если код операции показывает, что команда состоит

более чем из одного слова, фаза выборки повторяется нужное число

раз, чтобы выбрать команду целиком. При этом каждый раз увели-

чивается содержимое программного счетчика.

После выборки и декодирования всей команды устройство управ-

ления переходит в фазу выполнения. Оно генерирует управляющие

сигналы, и соответствующие схемы выполняют заданную в команде

операцию. Если в команде задан адрес операнда, устройство управ-

ления переходит к пересылке адресуемой информации между указан-

ной ячейкой и соответствующим блоком машины, например арифме-

тическим устройством или устройством вывода.

Для осуществления пересылки адресная часть команды передается

на адресную шину, подготавливая последующее появление адресу-

емой информации на шине данных. В конечном счете устройство

Управления обеспечивает фактическое выполнение заданной операции

18

гл. Т. МИКРОПРОЦЕССОРЫ И МИКРОКОМПЬЮТЕРЫ

и после ее завершения снова возвращается к фазе выборки, чтобы

получить из памяти следующую команду, адрес которой содержит

программный счетчик. Этот процесс повторяется до тех пор, пока

компьютер не получит указание остановиться.

В общем описанном выше случае команды выполняются после-

довательно в порядке их расположения в памяти. Однако в некоторых

случаях этот порядок желательно изменить, например в зависимости

от состояния флажковых битов. В этом случае адрес следующей ко-

манды может не быть адресом ячейки, следующей по порядку за ячей*

кой, откуда была взята текущая выполняемая команда. Команды,

в которых происходят такие изменения порядка выборки команд,

называются командами переходов, передач управления или ветвлений.

В этих командах адресная часть содержит адрес следующей ко-

манды, которую должно выбрать устройство управления, если по-

следовательность выборки изменяется. Поэтому, после того как уст-

ройство управления декодирует команду перехода и установит, что

Условия изменения порядка выполнены, оно Поместит адресную часть

выполняемой команды, содержащую адрес следующей команды, в

программный счетчик. Таким образом, после того как устройство

управления перейдет в фазу выборки, оно автоматически получит

йужную ему следующую команду.

1.5. ЕЩЕ ДВА ПОНЯТИЯ

Завершая краткий обзор микрокомпьютеров, остановимся еще

на двух понятиях, которые существенно расширяют их возможности.

Эти понятия стек и прерывание программы.

Стек

Мы уже говорили о том, что при помощи команд переходов можно

отходить от строго последовательного порядка выполнения команд.

Особый тип команды перехода, несколько отличающийся от рассмот-

ренных выше, позволяет многократно использовать некоторую спе-

циально выделенную группу команд, называемую подпрограммой.

В процессе выполняемых вычислений в главной программе может

потребоваться выполнить некоторое «подвычисление», оформленное

в виде подпрограммы. Компьютер должен передать управление из

главной программы на подпрограмму, выполнить соответствующее

«подвычисление» и затем осуществить возврат в главную программу

для продолжения работы. Чтобы осуществить такой возврат, необ-

ходимо сохранить значение программного счетчика, которое было до

перехода к подпрограмме. Это и делается в команде переход на под-

программу, а именно запоминается содержимое программного счет-

чика и затем передается управление. Для того чтобы восстановить

программный счетчик, используя запомненное значение, и обеспечить

1.5 ЕЩЕ ДВА ПОНЯТИЯ

19

возврат к главной программе, употребляется специальная команда

возврат из подпрограммы. Место, где запоминается содержимое про-

граммного счетчика, обычно представляет собой стек.

В общем случае стек — это совокупность регистров, которые

принимают и выдают информацию в соответствии с правилом «послед-

ним вошел, первым вышел» (LIFO — last-in first-out). Это означает,

что только вершина стека, где находится последний его элемент,

непосредственно доступна извне. В зависимости от конструкции ком-

пьютера стек может находиться в устройстве управления или быть

частью памяти.

Если стек может хранить несколько адресов (значений программ-

ного счетчика), мы получаем возможность выполнять вложенные

подпрограммы. Таким образом, из подпрограммы можно сделать

переход на другую подпрограмму или даже на саму себя — это на-

зывается рекурсией. Очевидно, что глубина вложений подпрограмм

зависит от емкости стека.

Прерывание программы

Во многих приложениях микропроцессоров возникает необходи-

мость прерывать процесс вычислений для обслуживания внешнего

устройства. Прерывание может происходить при поступлении в про-

цессор сигнала от внешнего устройства, требующего внимания. В от-

вет на это процессор должен приостановить выполнение текущей про-

граммы, запомнить состояние, в котором она была прервана (содер-

жимое различных регистров, включая программный счетчик), и затем

обслужить запрос внешнего устройства. Завершив обслуживание,

микропроцессор возвращается к приостановленному процессу вычис-

лений, воспользовавшись ранее запомненной информацией о состоянии

прерванной программы.

Понятие прерывания можно обобщить для случая нескольких

внешних устройств. В этом случае любое из устройств может прислать

свой запрос на внимание. Обработка запросов может либо следовать

правилу обслуживания «первым вошел — первым вышел», либо

некоторой приоритетной схеме в соответствии с приоритетом запросов.

При всех условиях способность обрабатывать прерывания может

оказаться очень мощным средством во многих приложениях микро-

процессоров. Поскольку при прерываниях нужно сохранять инфор-

мацию о текущем состоянии процессора, можно опять воспользо-

ваться стеком, т. е. сохранить в нем внутреннее состояние микропро-

цессора в момент поступления запроса, включая программный счет-

чик. В некотором смысле прерывание подобно переходу на подпро-

грамму, но этот переход проинициирован внешним сигналом, а не

командой в программе.

20

ГЛ- Г МИКРОПРОЦЕССОРЫ И МИКРОКОМПЬЮТЕРЫ

1.6. О ПОСЛЕДУЮЩИХ ГЛАВАХ

Предыдущие разделы содержали краткое изложение структуры

и функционирования микропроцессора и микрокомпьютера. После-

дующие главы посвящены более детальной проработке рассмотренной

структуры и многим возможным ее вариациям.

В гл. 2 рассматриваются системы счисления, употребляемые в

компьютерах, и методы выполнения арифметических действий в этих

системах счисления. Поскольку компьютер манипулируете числами,

эта глава необходима для понимания большей части материала по-

следующих глав.

Гл. 3 посвящена алгебре, которая может служить математической

моделью логических схем. Ее применение оказывается полезным при

проектировании логических схем и описании их поведения.

Базисные электронные схемы — главный предмет гл. 4. При

помощи этих схем реализуются различные логические функции,

введенные в гл. 3. Поскольку эти функции допускают несколько реа-

лизаций, существуют различные семейства логических элементов.

В гл. 4 проводится анализ достоинств и недостатков этих семейств

элементов. Представление о семействах элементов важно для понима-

ния электрических характеристик микропроцессоров и некоторых про-

блем, возникающих при соединении различных компонентов микро-

компьютера друг с другом.

В гл. 1 мы установили, что микрокомпьютер состоит из несколь-

ких типовых логических узлов. Регистры, например, встречаются

во всех функциональных блоках микрокомпьютера. Далее, при вы-

полнении машинных операций происходили передачи данных из

регистра в регистр. Для того чтобы осуществлять такие передачи,

нужно уметь ссылаться на отдельные регистры, участвующие в пере-

даче. Выбор соответствующих регистров осуществляется с помощью

типового логического узла, называемого дешифратором. Дешифра-

торы используются также для декодирования команды перед ее вы-

полнением.

В гл. 1 было также показано, что микропроцессорная система

включает как составную часть средства для выполнения арифмети-

ческих действий. Эти действия обычно выполняются с помощью сум-

маторов и вычитателей. Детальное изучение логики регистров, де-

шифраторов, сумматоров и вычитателей составляет предмет гл. 5.

Говоря о памяти микрокомпьютера, мы отмечали, что использу-

ются два вида памяти, а именно память с записью и считыванием и

память только со считыванием. В гл. 6 оба эти вида памяти изучаются

как с точки зрения их электронной структуры, так и с точки зрения

внешних характеристик. Более того, не все виды памяти с записью

и считыванием обладают возможностью произвольного доступа.

В гл. 6 рассматривается также память, доступ к которой осуществ-

ляется последовательно.

1.6. О ПОСЛЕДУЮЩИХ ГЛАВАХ 21

В гл. 7 и 8 вводится типовой (но гипотетический) микропроцессор.

На его примере продемонстрированы основные свойства выполняемых

микропроцессорами команд и объясняются главные принципы про-

граммирования для микропроцессоров. Введенный в этих двух главах

микропроцессор используется затем в гл. 9 и 10, где обсуждаются

вопросы проектирования микропроцессорной системы.

В гл. 9 рассматривается подключение к микропроцессору других

устройств. При подключении должна обеспечиваться совместимость

в отношении синхронизации, форматов данных и вида сигналов.

В общем случае для такой совместимости создаются вспомогательные

схемы, называемые интерфейсными. Некоторые понятия из этой

области изучаются в гл. 9.

В заключительной главе книги приводятся проекты трех микро-

процессорных систем. На них проиллюстрированы как области при-

менения микропроцессоров, так и использование материала, изложен-

ного в предыдущих главах*

Глава 2. СИСТЕМЫ СЧИСЛЕНИЯ

И АРИФМЕТИКА

По существу, компьютер — это устройство обработки информации.

Информация может быть числовой или нечисловой. Однако в обоих

случаях в машине она представляется цепочками из нулей и единиц,

и в конечном счете вся информация представляется в виде чисел не-

зависимо от того, как мы ее интерпретируем.

Эта глава содержит материал по двоичной системе счисления и

другим системам, тесно связанным с двоичной. Рассмотрены спо-

собы выполнения арифметических операций. В последнем разделе

показано, как нечисловая информация может быть также представ-

лена в виде цепочек нулей и единиц.

2.1. ПОЗИЦИОННЫЕ СИСТЕМЫ СЧИСЛЕНИЯ

Мы все знакомы с десятичной системой счисления. Однако это

не единственная система из тех, которые можно определить. На самом

деле, обычная десятичная система — это лишь одна из многих пози-

ционных систем счисления по основанию. В этих системах исполь-

зуется конечный набор различных символов. Каждый символ назы-

вается цифрой и обозначает некоторое количество. Число различных

символов в наборе называется основанием системы счисления. Чтобы

обозначить величины, большие тех, которым соответствуют индиви-

дуальные символы, цифры выписывают рядом, образуя число. Отно-

сительной позиции цифры в числе ставится в соответствие весовой

множитель.

Рассмотрим привычную десятичную систему. В ней только 10 раз-

личных цифровых символов: 0, 1, . . ., 9. Например, число 536.4

можно считать просто сокращенным обозначением полинома

5х 102+Зх Ю^бХ 1О°+4Х 10’1

Здесь цифра 5 входит с весом 100, цифра 3 — с весом 10, цифра 6 —

с весом 1, а цифра 4 — с весом 0,1.

Как обобщение этой идеи в позиционной системе счисления по

некоторому основанию число

N ^71 —1^71—2* • -dido * d_ 2’ • /я

2.1. ПОЗИЦИОННЫЕ СИСТЕМЫ СЧИСЛЕНИЯ

23

можно считать обозначением полинома

N = dn_1b“’' + dn_2b"-* + ... +d_mb~m

В этой общей форме — цифры, лежащие в диапазоне

п — число цифр левее разделительной, или позиционной, точки х),

т — число цифр правее точки, а b — основание системы счисления.

Таблица 2.1

Системы счисления

Основание Система счисления Цифровые символы

2 двоичная 0, 1

3 троичная 0, 1,2

4 четверичная 0, 1, 2, 3

5 пятеричная 0, 1, 2,3, 4

8 восьмеричная 0, 1. 2, 3, 4, 5, 6, 7

10 десятичная 0, 1, 2, 3, 4, 5, 6, 7, 8, 9

12 двенадцатеричная 0, 1,2, 3, 4, 5, 6, 7, 8, 9, А, В

16 шестнадцатеричная 0, 1, 2. 3, 4, 5, 6, 7, 8, 9, А, В, G,

D, Е, F

В табл. 2.1 перечислены наиболее употребимые системы счисле-

ния. Как правило, в системах с основанием, меньшим 10, в качестве

цифровых символов используются соответствующие первые цифры

десятичной системы; для систем же с основанием, большим 10, исполь-

зуются десятичные цифры с добавлением первых букв латинского

алфавита. В таблице указана также относительная упорядоченность

цифр в системах.

Из упомянутых систем три системы представляют особый интерес

при изучении вычислительной техники — это двоичная, восьмеричная

и шестнадцатеричная. Записи некоторых чисел в этих системах

выглядят следующим образом:

1011.1012

372.468

C65F.B316

По соглашению десятичный индекс, сопровождающий число, ука-

зывает основание системы счисления. Индекс опускается, когда зна-

чение основания ясно из контекста.

Х) В СССР и во многих других странах часто вместо точки используется раздели-

тельная запятая. Однако в связи с распространением единых языков программиро-

вания в качестве разделительного символа все шире входит в употребление точка.—

Tip им. ред.

24

ГЛ. 2 СИСТЕМЫ СЧИСЛЕНИЯ И АРИФМЕТИКА

Как и в десятичной системе, число представлено совокупностью

выписанных рядом цифр. Дробная и целая части располагаются

соответственно справа и слева от разделительной точки. В случае

двоичной системы цифры 0 и 1 называют битами как сокращение от

Wnary digi/s (двоичные цифры).

Таблица 2 2

Первые 32 числа в двоичной, восьмеричной

и шестнадцатеричной системах

и их десятичные эквиваленты

Десятичные Дбоичные Восьмеричные Шестнодцитери^р

0 0 0 0

1 1 1 1

2 10 2 2

3 11 3 3

4 100 4 4

5 101 5 5

6 по 6 6

7 111 7 7

8 1000 10 8

9 1001 11 9

10 1010 12 А

11 1011 13 В

12 1100 14 С

13 1101 15 D

14 1110 16 Е

15 1111 17 F

16 10000 20 10

17 10001 21 11

18 10010 22 12

19 10011 23 13

20 10100 24 14

21 10101 25 15

22 юно 26 16

23 10111 27 17

24 11000 30 18

25 11001 31 19

26 11010 32 1А

27 11011 33 1В

28 11100 34 1С

29 11101 35 1D

30 11110 36 1Е

31 11111 37 1F

2.2. ПРЕОБРАЗОВАНИЯ ЧИСЕЛ

25

В табл. 2.2 приведены представления первых 32 целых чисел в

двоичной, восьмеричной и шестнадцатеричной системах вместе с их

десятичными эквивалентами.

2.2. ПРЕОБРАЗОВАНИЕ ЧИСЕЛ ИЗ ОДНОЙ СИСТЕМЫ

СЧИСЛЕНИЯ В ДРУГУЮ

Одна из интерпретаций любого числа заключается в обозначаемой

этим числом величине. Бывает интересно найти конфигурацию сим-

волов в одной системе счисления, которая обозначает ту же вели-

чину, что и некоторая конфигурация в другой системе. Эти два числа

можно считать эквивалентными представлениями одной и той же

величины в разных системах счисления.

Перевод в десятичную систему

Прежде всего рассмотрим преобразование числа из недесятичной

позиционной системы в эквивалентную десятичную форму. Такое

преобразование легко получается простым вычислением значения

полинома, соответствующего числу. Это вычисление можно, напри-

мер, выполнить следующим образом:

1. Записываем число в виде полинома

1^Л-2 * ’ * ^0 • ^-1 * * ’^-//2 = 1‘^~dn_2bn 2 4“ • • •

+ dob° + rf-i^1 +

где b — основание системы, выраженное в десятичной форме. Для

тех систем, где цифры представляются буквами, последние при вы-

числении заменяются на десятичные эквиваленты, например Л = 10,

В=11, С= 12, ....

2. Вычисляем значение полинома, пользуясь десятичной арифме-

тикой.

Для иллюстрации перевода из двоичной системы в десятичную

систему рассмотрим двоичное число 1110.12- Записывая его в виде

полинома по степеням 2 (по степеням основания), получим

1110.12 = 1 х 23 -+ 1 х 22 -+ 1 х 21 -+ 0 х 2° -+ 1 х 2"1

=1x8+1x4+1x2+0x1+1x05

= 8 +- 4 + 2 0 + 0.5

= 14.51О

Таким образом, 14.5 есть десятичный эквивалент двоичного числа

1110.1.

26

ГЛ 2 СИСТЕМЫ СЧИСЛЕНИЯ И АРИФМЕТИКА

В качестве второго примера преобразуем в десятичную систему

шестнадцатеричное число D3F.4i6:

D3F.416 - D х 162 + 3 х 16l + F х 16° + 4 х 16"1

. = 13 x 162 + 3 x 161 + 15 x 16° + 4 x 16"J

*= 13 x 256 + 3 x 16 + 15 x 1 + 4 x 0.0625

= 3328 + 48 + 15 + 0.25

= 3391.251O

Перевод из десятичной системы

Перевод десятичного числа в эквивалентную форму в другой си-

стеме счисления чуть более сложен. В процессе преобразования при-

ходится порознь обрабатывать целую и дробную части числа.

Рассмотрим сначала преобразование целого десятичного в

систему счисления с основанием b (Ь — целое положительное число).

Поскольку число в системе с основанием b можно записать в виде

полинома по степеням Несоответствующими цифрами в качестве коэф-

фициентов, мы получаем

= + (2.1)

Теперь нужно найти цифры d0» удовлетворяющие выпи-

санному уравнению. Для этого разделим обе части (2.1) на Ь. По-

лучим целое частное

дг; = 4^-2 -------d2bx + (2.2)

и остаток

Остаток

Таким образом, остаток равен младшей цифре числа в системе счис-

ления с основанием Н, т. е. d0. В результате деления в остатке может

оказаться более одной десятичной цифры, если b больше 10. Однако

поскольку остаток всегда меньше Н, то его значение будет соответст-

вовать цифре d0.

Если процесс деления повторить для целого частного (2.2), мы

получим снова целое частное

в остаток

Остаток ( — ) = d.

\ ь / 1

В этом случае остаток соответствует следующей справа цифре числа

с основанием системы Ь. Легко видеть, что, повторяя описанный

2 2 ПРЕОБРАЗОВАНИЯ ЧИСЕЛ

27

процесс вплоть до нулевого частного, мы получим все цифры урав-

нения (2.1). (Напомним, что остаток следует каждый раз представ-

лять цифрой в системе счисления с основанием Ь.) Очевидно, что

процесс завершится после конечного числа шагов.

Разберем описанную процедуру на примере перевода десятичного

числа 52 в эквивалентную двоичную форму. Вычисления проводятся

многократным делением на 2:

2)26

2)13

2)6

2)3

2)1

О

Остаток

0 = do

0 = ^

1 = ^

о==а3

i = d$

Следовательно, 5210= 1101002.

В качестве второго примера рассмотрим перевод десятичного

числа 58506 в шестнадцатеричную систему. Последовательные деления

на 16 дают

16)58506 Остаток ЦифрьВой еинВол, эквивалентный остатку

16)3656 10 А = 40

16)228 8 8 = dt

16)14 4 4 = d2

0 14 E = d3

Следовательно, 58506ю =Е48А16.

Процедура перевода правильной десятичной дроби в систему

счисления с основанием b должна быть несколько иной. Обозначим

через NF десятичную дробь, соответствующую полиному

где^_ь d_2, . . ,,d_m— цифры, которые нужно определить. Поскольку

полином и NF обозначают одну и ту же величину, то имеет место

равенство

N,=d_Ab^ + d^b^ + • • • + d_mb~m (2.3)

Умножая обе части равенства на Ь, получим

bNP =d^1b^ + d_2b-‘1 + • • • + d_mb~m+l

= <1 + <2b"1+ • • • + d_mb~"l + 1 (2.4)

= d-i + N'f

28

ГЛ. 2. СИСТЕМЫ СЧИСЛЕНИЯ И АРИФМЕТИКА

Произведение состоит из целой части d_t и дробной части N'F. Целая

часть эквивалентна старшей цифре нашей исходной дроби в системе

счисления с основанием Ь. Как и ранее, легко видеть, что целая часть,

соответствующая d_lf лежит в диапазоне от 0 до b—1, и, следова-

тельно, для систем с основанием, большим 10, мы должны в соответ-

ствующих случаях в качестве цифр брать буквы.

Если провести те же действия над дробной частью результата (2.4),

т. е. умножить его на Ь, то можно будет определить следующую цифру

разложения дроби, заданного (2.3). А именно, поскольку

= + • • • +й-^,л + 2

= d_2 + d_3b~'+ • • • + d_rnb~m+2

= d_2 + N”F

то целая часть произведения соответствует d_2. Очевидно, повторяя

описанный процесс, мы сможем определить последующие цифры

числа в системе по основанию Ь. Процесс естественно прекращается,

если получается нулевая дробная часть. Однако в отличие от процесса

преобразования целых чисел, всегда заканчивающегося через конеч-

ное число шагов, процесс преобразования десятичной дроби может

быть бесконечным. Другими словами, представление десятичной

дроби с конечным числом цифр может иметь бесконечное число цифр

в системе счисления с другим основанием. Поэтому в любом случае

процесс преобразования останавливают при достижении требуемой

точности.

Приведем два примера преобразования десятичных дробей. Сна-

чала рассмотрим перевод числа 0.6875 в двоичную форму:

2 х 0.6875 = 13750 :.d^ = 1

2 x 0375 =0.750 AcL2 = 0

2 x 0.75 = 1.50 ; а’_3 = 1

2x0.5 =1.0 /.<L4=1

В результате мы получаем 0.687510=0.10112.

Теперь переведем десятичную дробь 0.8435 в шестнадцатеричную

систему. Нужно выполнить следующую цепочку умножений:

16 х 0.8435 = 13.496

16 х 0.496 = 7.936

16 х 0.936 = 14.976

поскольку D— это

= D шестнадцатеричная цисрра^

обозначающая десятичное

. т - число 13

..d_2 = 7

;. J-з = Е

16 X 0.975 = 15.616 = F

Остановив процесс в этом месте, мы получим 0.8435i0=O.D7EF...i6,

2.3. ПРЕОБРАЗОВАНИЯ 2—8 И 2 — 16

29

На этом примере видно, что процесс преобразования бесконечен, по-

скольку третья цифра дробной части на всех шагах равна 6.

Для смешанных десятичных чисел целая и дробная части обраба-

тываются порознь. Целая часть преобразуется последовательными

делениями, а дробная — последовательными умножениями. Получа-

ющееся в результате смешанное число записывается в виде этих де}х

частей разделенных точкой.

2.3. ДВОИЧНО-ВОСЬМЕРИЧНЫЕ И ДВОИЧНО-

ШЕСТНАДЦАТЕРИЧНЫЕ ПРЕОБРАЗОВАНИЯ

Описанные в предыдущем разделе методы позволяют преобразо-

вывать числа из системы счисления с одним произвольным основанием

bi в систему с другим произвольным основанием Ь2. Для этого до-

статочно сначала преобразовать число из системы bi в десятичную

форму, а затем из десятичной — в систему Ь2. Существуют обобщения

рассмотренных методов для прямого перевода из системы в систему

при произвольных основаниях. В общем случае процедуры прямого

перевода неудобны для выполнения вручную, поскольку они требуют

недесятичной арифметики. Однако между двоичной системой, с одной

стороны, и системами с основанием, являющимся степенью двойки,

с другой, существуют простые прямые методы преобразования. Это

относится, в частности, к двоично-восьмеричным и двоично-шестнад-

цатеричным преобразованиям.

Рассмотрим двоичное число

N = ••• dsd1d6d5d^d3d2dld0 . d_id_2d-3 ”*

Его десятичный эквивалент мы получим, записав полином

• • J828 4- J727 4- db26 4- d525 4- d42* 4- d,23 4- d222

+ d,2l + Jo2° + d^2~1 + d-22~2 + d.32-3 •••

С помощью простых группировок полином приводится к виду

• • • + (J822 + </72* + J62°)26

+ (d522 + J42‘ + </32°)23

+ (d222 + ^2* + <?O2°)2°

+ (d_122 + <i_221+</_320)2-3 + -"

= •• +W822 +J72* + </62°)82

+ (d522 + d42l + J32°)8‘

+ (J222 + dt2l + </02°)8°

+ (</_I22+</_221 +d_32°)8-J +•••

30

ГЛ 2 СИСТЕМЫ СЧИСЛЕНИЯ И АРИФМЕТИКА

Это выражение содержит степени числа 8 и имеет форму восьмерич-

ного числа. Внутри каждой пары скобок содержится двоичное раз-

ложение десятичного числа, лежащего в диапазоне от 0 до 7. Если

величину, заключенную в каждой паре скобок, записать в виде вось-

меричной цифры (а она совпадает с эквивалентной десятичной цифрой),

то перевод из двоичной в восьмеричную систему будет завершен.

Таким образом, чтобы преобразовать двоичное число в восьмерич-

ную форму, нужно объединить двоичные цифры в группы по 3 бита,

продвигаясь от разделительной точки вправо и влево. При необхо-

димости в начале и в конце исходного числа нужно добавить нули.

Затем каждая группа из 3 битов заменяется эквивалентной восьме-

ричной цифрой. Результат будет восьмеричным представлением ис-

ходного двоичного числа. Например, биты двоичного числа 11011001.

1011 группируются следующим образом:

0И0И 001.1011рр2

Замена каждой группы битов восьмеричным эквивалентом дает вось-

меричное число 331.548.

Описанная процедура легко обращается для перевода восьмерич-

ных чисел в двоичные. Например, отправляясь от восьмеричного

числа 57.2, получим

57.28 = 101И1.0102

Можно построить аналогичные процедуры для преобразований между

двоичной и шестнадцатеричной системами. Каждой шестнадцатеричной

цифре будет соответствовать группа из четырех битов. Чтобы пре-

образовать, например, двоичное число 1011100101.112 в шестнадца-

теричную систему, биты группируются по четыре от точки вправо и

влево, а в начале и в конце добавляются нули:

pqioiiioowi.iigOi

Преобразование завершается заменой каждой группы эквивалентной

шестнадцатеричной цифрой:

001011100101.11002 = 2Е5.С1<?

Обратная процедура позволит переводить числа из шестнадцатерич-

ной системы в двоичную.

Как уже упоминалось в предыдущей главе, компьютеры обычно

работают в двоичной системе. Однако из-за простоты рассмотренных

выше процедур и стремления к уменьшению количества цифр в чис-

лах при записи их на бумаге удобнее все числа считать восьмерич-

ными или шестнадцатеричными. В этом и кроется причина их ши-

рокого использования при работе с компьютерами.

2.4. ДВОИЧНАЯ АРИФМЕТИКА

31

2.4. ДВОИЧНАЯ АРИФМЕТИКА

Четыре основные арифметические операции, а именно сложение,

вычитание, умножение и деление, можно выполнять в позиционной

системе счисления с любым основанием. Поскольку компьютеры, как

правило, работают в двоичной системе, для нас важно понимать именно

двоичную арифметику. Хотя основной упор в последующем изложении

будет сделан на двоичной арифметике, читатель сможет легко обоб-

щить соответствующие процедуры на случай системы с любым другим

основанием.

Таблица 2.3

Правила сложения двух

двоичных цифр

«-ь ь ъ

О 1

0 1

1 0 и 1 переноса

В табл. 2.3 даны правила сложения двух двоичных цифр. Заме-

тим, что при двоичном сложении 1 + 1 возникает бит переноса и что

бит суммы при этом равен О п.

Чтобы сложить пару двоичных чисел, следует применить правило

табл. 2.3 многократно, отправляясь от пары младших разрядов, так,

как это обычно делается при десятичном сложении. После сложения

пары младших цифр и получения значения младшего разряда суммы

складывается следующая пара цифр с учетом переноса из младшего

разряда. При этом получается значение следующего разряда суммы

и, возможно, перенос. Описанный процесс повторяется нужное число

раз. Следующий пример поясняет сказанное:

111 1

ion.ioi2

+ И 10.0012

* 11001.но2

Переносы

Слагаемое

Слагаемое

Сумма.

Вообще, когда сложение двух цифр в системе по основанию b дает величину,

превышающую или равную основанию системы, сумма принимается равной этой ве-

личине по модулю Ь, и возникает перенос в следующий разряд.

32

ГЛ. 2. СИСТЕМЫ СЧИСЛЕНИЯ И АРИФМЕТИКА

Таблица 2.5

Правила умноженья двух

двоичных цифр

Таблица 2.4

Прав: ла вычитания двух

двоичных цифр

Двоичное вычитание обратно двоичному сложению. Правила

вычитания даны в табл. 2.4. Легко видеть, что в случае вычитания

большей цифры из меньшей необходимо произвести «заем» в более

старшей соседней позиции. При десятичном вычитании, если в по-

зиции п возникает необходимость «заема», то вычитается 1 из (п+1)-й

цифры уменьшаемого, а в позицию п «приносится» величина 10 (т. е.

основание системы). Это же правило работает и для двоичного вычи-

тания с той лишь разницей, что из позиции п+1 в позицию п «при-

носится» величина 2 (т. е. основание системы). При этом нужно

вычесть 1 из цифры уменьшаемого в позиции п+1. Таким образом,

как показано в табл. 2.4, при вычитании 1 из 0 разность после заема

оказывается равной 1. Следующий пример поясняет сказанное:

010 Изменение уменьшаемого 8результате заема

JW0.112 Уменьшаемое

— 111.012 Вычитаемое

11.102 Разность

В табл. 2.5 приведены правила умножения двух двоичных цифр.

Умножение двух многоразрядных чисел проводится аналогично

умножению десятичных чисел, а именно сначала вычисляются частные

произведения множимого на отдельные разряды множителя, а затем

эти частные произведения суммируются, разумеется, в двоичной си-

стеме. Принцип двоичного умножения легко проследить на следую-

щем примере:

11 012 Множимое

х 1012 Множители

I Частные

0000 произведения

1101 J

10000.012 Произведение

2.5 ДВОИЧНЫЕ ЧИСЛА СО ЗНАКОМ

33

Наконец, двоичное деление также аналогично делению десятич-

ному. Здесь последовательно подбирается очередная искомая цифра

частного и на нее умножается делитель. Полученное произведение

вычитается из делимого для проверки правильности подобранной

цифры. Входящие в двоичное деление операции двоичного умножения

и вычитания мы уже рассмотрели. Процесс двоичного деления даже

проще хорошо знакомого нам процесса десятичного деления, поскольку

при подборе очередной цифры частного нужно рассматривать только

две возможности (0 или 1). Ниже следует пример двоичного деления:

ПО 1012 Частное

Делитель 112) 101000002 Делимое

100

-и

100

—11 j

10

-00,

100

-и

12 Остаток

2.5. ДВОИЧНЫЕ ЧИСЛА СО ЗНАКОМ

Все числа, рассмотренные нами до сих пор, предполагались не

имеющими знака, т. е. положительными. Однако весь предыдущий

опыт общения с числами говорит о том, что нужны как положитель-

ные, так и отрицательные числа. Понятно, что ввести понятие числа

со знаком можно, просто добавив к числу соответствующий символ.

Однако, имея в виду ЭВМ, полезно рассмотреть и другие способы

представления чисел со знаком.

Для людей, работающих с ЭВМ, важны обычно следующие три

способа представления чисел со знаком: в прямом, обратном и в

дополнительном коде. В этом разделе мы остановимся на всех трех.

Причем, поскольку разделительная точка в явном виде не присут-

ствует в микрокомпьютерных словах с данными, мы ограничимся

только целыми двоичными числами.

Прямой код

Можно считать, что количество разрядов, отведенных для «машин-

ного числа», фиксировано и известно. Более того, поскольку вся

информация в компьютере представляется в виде нулей и единиц,

2 № 592

34

ГЛ. 2. СИСТЕМЫ СЧИСЛЕНИЯ И АРИФМЕТИКА

можно с помощью этих же символов представлять и знак числа. На-

прашивающийся вариант — зарезервировать один разряд, скажем

старший, в качестве знакового и считать, что 0 соответствует положи-

тельным, а 1 — отрицательным числам, остальные же разряды ис-

пользовать для представления абсолютной величины числа в двоич-

ной системе.

Таблица 2.6

Представление чисел в прямом, обратном и дополнительном

четырехразрядном двоичном коде

Старший разряд — знаковый; запятая, отделяющая знаковый разряд,

введена только для наглядности и не является частью кода.

Де с я тшчнзе число СО Прямой код Обратный код Дополните/ib ныц код

4-7 0.111 0.1 II 0,111

+ 6 0,110 0,110 0.110

4-5 OJOI 0.101 0,101

4-4 0,100 0,100 0.100

4-3 0,011 0,011 0,011

4-2 0,010 0,010 0,010

+ 1 0,001 0,001 0,001

0 10,0001 11,0001 j 0.000 [ luilf 0.000

— 1 1,001 1,110 1.111

-2 1,010 1,101 1.110

-3 1,011 1.100 1.101

-4 1,100 гон ' 1.100

-5 1J01 1,010 1.0И

1,110 1,001 1,010

-7 1.111 1.000 1.001

-8 — —» 1,000

Такое представление чисел со знаком и называется представле-

нием в прямом коде. В табл. 2.6 приведены в качестве примера деся-

тичные числа со знаком и их эквивалентные представления в прямом

четырехразрядном двоичном коде. Старший бит служит для обозна-

чения знака, а остальные 3 бита в двоичной форме задают абсолют-

ную величину числа. Запятую в числах, приведенных в таблице,

нужно воспринимать лишь как разделитель, облегчающий чтение

и отделяющий знак от абсолютной величины. В машинном слове

никакой запятой, конечно, нет. Заметим, что нуль в прямом коде

имеет два представления.

Легко видеть, что для n-разрядного прямого двоичного кода Х~

• • dQ, где старшая цифра соответствует знаку, эквива-

лентное десятичное число Хщ, представляемое этим кодом, равно зна*

2.5. ДВОИЧНЫЕ ЧИСЛА СО ЗНАКОМ'

35

чению полинома

(- l)‘/«-i(d„_22«-2 + d„_32”-’+ • • • +d„2’)

Диапазон чисел, представимых в n-разрядном двоичном коде, опре-

деляется соотношениями

1— 1

Обратный код

Несмотря на естественность прямого кода для человека, в ЭВМ

он применяется относительно редко. В ЭВМ положительные 'числа

обычно представляются так же, как в прямом коде, а отрицательные —

в виде дополнений, т. е. путем сдвига по числовой оси исходного числа

на некоторую константу. А именно если z—положительное число,

то —z представляется в виде X — z, где К таково, что разность по-

ложительна. Обратный код отличается от дополнительного только

выбором значения X.

Пусть Х10 — десятичное число со знаком, которое мы хотим пред-

ставить в обратном коде. Будем считать, что мы ищем /г-разрядное

представление, включая знак, т. е. часть, отводимую для абсолютной

величины, будем считать (п—1)-разрядной. ЕслиХю^О, то обратный

код содержит ,0 в старшем, знаковом разряде и обычное двоичное

представление Х1о в остальных п—1 разрядах. Таким образом, для

положительных чисел обратный код в точности совпадает с прямым.

Если же Х1о^О, то знаковый разряд содержит 1, а остальные раз-

ряды содержат двоичное представление числа

2"-1-1-|Х10| (2.5)

Чтобы пояснить сказанное, рассмотрим положительное число

+ 1310- Выбрав шестибитовое (или шестиразрядное) представление,

включая знак, т. е. считая п=6, мы получим обратный код, равный

0,011012. Заметим, что под абсолютную величину числа отводится

5 разрядов. Запятая, как и раньше, отделяет знаковый разряд. В ма-

шине этот разделитель отсутствует. Теперь рассмотрим отрицательное

число —1310. По-прежнему считаем представление шестибитовым,

включая знак. Поскольку в пятиразрядном представлении |—1310| =

= 131о=011012 и 25—1ю=11111, то в соответствии с (2.5) мы получим

(26”i—1 —13)10 = (11111—01101)2= 100102

Добавив шестой, знаковый бит, мы получим шестиразрядный

обратный код для —13ю, равный 1,100102. Другие примеры пред-

ставления чисел в обратном коде можно найти в табл. 2.6. Следует

отметить (и это видно в таблице), что в обратном коде нуль имеет два

представления.

На самом деле, всякий раз, когда для некоторой положительной

величины 2И, , имеющей (п—1)-разрядное двоичное представление,

2*

36

ГЛ. 2. СИСТЕМЫ СЧИСЛЕНИЯ И АРИФМЕТИКА

выполняется вычисление в соответствии с (2.5), его называют обраще-

нием М. Относительно обратного кода числа со знаком обращением

называют операцию, состоящую в применении (2.5) к «величинной»

части кода и в замене значения знакового разряда на противополож-

ное. Таким образом, применительно к рассмотренному примеру мы

будем говорить, что 1,100102 есть результат обращения 0,011012.

Рассмотрим процесс обращения отрицательного числа на примере

числа —131о. Мы показали, что обратный код этого числа есть 1,100102.

Поскольку величинная часть/ т. е. 100102, соответствует 181Л и по-

скольку мы рассматриваем шестиразрядные представления, приме-

нение соотношения (2.5) дает

(2е-1 — 1 —18)10 = (11111 —10010)2 = 011012

Добавляя инвертированное значение знакового разряда, мы получаем

результат обращения кода 1,100102, равный 0,011012=+ 131п. Легко

видеть, что обращение кода эквивалентно замене знака представ-

ляемого этим кодом числа на противоположный.

Правило обращения для обратного кода можно сформулировать

проще. А именно для обращения нужно заменить каждый 0 на 1,

а каждую 1 на 0, включая знаковый разряд. Это хорошо видно на

рассмотренных примерах, где +1310 представлялось в виде 0,011012,

а —1310 — в виде 1,100102.

Легко видеть, что если X—dn_idn_2 есть п-разрядный дво-

ичный обратный код, то десятичный эквивалент представляемого им

числа Х10 задается полиномом

(1 -2^)dn^ +^22«’2+ • * • +d02°

Диапазон чисел, представимых в этом коде, определяется соот-

ношениями

Нужно обратить внимание, что знаковый разряд имеет отрицатель-

ный весовой множитель.

Дополнительный код

Этот код используется в микрокомпьютерах чаще всего. Пусть

Х10 обозначает десятичное число со знаком, которое мы хотим пред-

ставить в дополнительном n-разрядном коде, т. е. мы отводим, как

и'раньше, 1 разряд на знак и п— 1 на абсолютную величину. Если

Х10>0, то так же, как для прямого и обратного кодов, мы имеем 0

в знаковом разряде и обычное двоичное представление числа Хю

в остальных п—1 разрядах. Если же Хю<0, то мы имеем 1 в знаковом

разряде, а в остальных п—1 разрядах двоичный эквивалент числа

|Х10| (2.6)

2.5 ДВОИЧНЫЕ ЧИСЛА СО ЗНАКОМ

37

Чтобы пояснить применение (2.6), рассмотрим снова число —1310.

Представим его в шестиразрядном дополнительном коде. Поскольку

|—13ю I = 1 Зю=01101 о, в пятиразрядном представлении, и 2105= 1000002,

то в соответствии с (2.6) мы получим

(26-1 — i3)io = (ЮОООО — 01101)2 = 100112

в пятиразрядном представлении. Добавляя шестой знаковый разряд,

получаем дополнительный код числа —13ю, равный 1,100112. Из

табл. 2.6, где приведены представления чисел во всех рассмотренных

кодах, видно, что 0 в дополнительном коде имеет единственное пред-

ставление.

Поскольку у нуля здесь только одно представление, диапазон

представимых чисел шире, чем в прямом и обратном кодах. Знаковый

разряд можно, как и раньше, интерпретировать как разряд с отри-

цательным весовым множителем, поскольку для л-разрядного двоич-

ного дополнительного кода X=dn_1dn_2 • • • d0 представляемое им

десятичное число Хи> задается полиномом

-2"-Чп_^п_22"-*+ • • • +d02<> (2.7)

Диапазон чисел, представленных в этом коде, равен

—2"-х<Х10^2"-х — 1

Всякий раз, когда для некоторой положительной величины М

проводится вычисление (2.6), результат называют дополнением М.

Применительно к дополнительному коду взятием дополнения называют

операцию, состоящую в применении вычисления (2.6) к величинной

части кода и инвертировании значения знакового разряда. Переход

к дополнению кода эквивалентен замене знака, представляемого ко-,

дом числа, на противоположный.

Вспомним, что дополнительный код для —13ю равен 1,100112.

Поскольку величинная часть кода, т. е. 10011, соответствует 19ю

и поскольку мы рассматриваем шестиразрядные коды, применение

(2.6) дает (26-х—19)10 = (100000 —10011)2 = 011012 в пятиразрядном’

представлении. Добавляя противоположное значение знакового раз-

ряда, получим дополнение для кода 1,100112, равное 0,011012= + 13ib.

Сходство выражений (2.5) и (2.6) служит основой для общего

алгоритма взятия дополнительного кода. Сначала нужно выполнить

обращение, как описано выше, путем замены 0 и 1 в коде соответст-

венно на 1 и 0, а затем прибавить к результату 1. Сумма и будет до-

полнительным кодом числа х).

Х) Другой общий алгоритм перехода к дополнению формулируется следующим

образом: Просматриваем код справа налево, начиная с младшей цифры, и оставляем

неизменными все нули до первой встретившейся единицы и саму эту единицу. Все

остальные нули и единицы, включая знаковый разряд, заменяем соответственно на

единицы и нули.

38

ГЛ. 2. СИСТЕМЫ СЧИСЛЕНИЯ И АРИФМЕТИКА

Следует обратить внимание на то, что диапазоны чисел, пред-

ставленных в дополнительном и обратном кодах, не совпадают.

И поскольку в обратном коде нет представления для +2"“1, то при

помощи описанного алгоритма мы не сможем получить представ*

ления для —2"’1 в дополнительном коде. Однако такое представ-

ление существует и единственно:

100-0

п — 1 нулей

что следует из (2.7).

2.6. СЛОЖЕНИЕ И ВЫЧИТАНИЕ ЧИСЕЛ СО ЗНАКОМ

Представление чисел в обратном и дополнительном кодах широко

используется в компьютерах. При этих представлениях операции

сложения и вычитания чисел с произвольными знаками допускают

простую реализацию. Мы уже отмечали в предыдущем разделе, что

обращение кода (или взятие его дополнения) равносильно изменению

знака представляемого числа п. Таким образом, операцию вычитания

можно свести к сложению с предварительным обращением кода вы-

читаемого. Более того, в этом разделе мы покажем, что сложение для

чисел со знаками реализуется просто сложением их кодов как поло-

жительных чисел, т. е. с помощью обычной операции сложения,

рассмотренной в разд. 2.4, которая проводится над всеми разрядами

кодов, включая и знаковые. Таким образом, оказывается, что если

числа представлены в компьютере в обратном или дополнительном

коде, то нет необходимости иметь электронные схемы одновременно

и для сумматора, и для вычитателя.

Сложение и вычитание в дополнительном коде

Начнем со сложения в дополнительном коде. Предположим, что

оба числа имеют n-разрядное представление. В этом случае коды

обоих чисел суммируются по правилам двоичного сложения, рас-

смотренным в разд. 2.4, разряд за разрядом, включая старшие, зна-

ковые разряды кодов. Возможный перенос из старшего разряда от-

брасывается. Мы получим правильный результат, т. е. правильное

представление в дополнительном коде алгебраической суммы чисел,

коды которых суммировались, при условии, что алгебраическая

сумма принадлежит диапазону представимых чисел, т. е. если —2Л“1^

Х) Единственное исключение мы отмечали для числа — 2п~* в «-разрядном допол-

нительном коде.

t.G. СЛОЖЕНИЕ И ВЫЧИТАНИЕ ЧИСЕЛ СО ЗНАКОМ

39

<хумма^2',~1—1. Описанный алгоритм поясняется приведенными

ниже примерами с пятиразрядными кодами:

Пример

Слагаемое

Слагаемое

Сумма

( + 6) = 0,0110

4-(-4)^ 4-1,1100

(+2)-jj 0,0010

*—Перенос

игнорируется

Пример-

Слагаемое (4- 6) - 0,0110

Слагаемое 4-(—13) 4-1,0011 ;

Сумма {гЪ- 1,1001-’

Пример

Слагаемое

Слагаемое

Сумма

(-3)^ 1ДЮ1

4-(-11)=^ 4-1,0101

(-14) =2] 1,0010

*-----Перенос

игнорируется

Если оба слагаемых имеют одинаковый знак, то может случиться,

что их алгебраическая сумма выйдет за границы диапазона чисел;,

представимых в коде данной разрядности. Такое событие называется

переполнением, и его нужно фиксировать. Вообще говоря, можно

утверждать, что переполнение происходит тогда и только тогда, когда

коды слагаемых имеют одинаковое значение знаковых разрядов, а

код суммы имеет другое значение знакового разряда. Другой рас-

пространенный способ определения переполнения опирается на зна-

чения переноса в знаковый разряд Cs и из знакового разряда С$+/.

В частности, переполнение происходит тогда и только тогда, когда

либо (1) С5=0 и C5+i=l, либо (2) С5=1 и C5+i=0.

Мы уже отмечали раньше, что вычитание можно выполнить, сна;

чала взяв дополнительный код вычитаемого, а затем сложив это до;

полнение с кодом уменьшаемого. Следующие примеры помогут по-

нять, как это делается:

Р Уменьшаемое (4-12)— 0,1100 0,1100

Вычитаемое Г(+7)- —0,0111/^.^4-1,1001

Разность (+5) - JJ 0,0101

---Перенос

игнорируется

40

ГЛ. 2. СИСТЕМЫ СЧИСЛЕНИЯ И АРИФМЕТИКА

Пример

Уменьшаемое (--14)=* 1,0010 1,0010

Вычитаемое - (- 3) - -1,1101 вдополнкод^ +0,0011

Разность (-11)= ’ 1,0101

Сложение и вычитание в обратном ходе

Хотя в большинстве микрокомпьютеров применяется дополни-

тельный код, можно воспользоваться и обратным. В нем также можно

выполнять алгебраическое сложение и вычитание. Алгоритм сло-

жения формулируется так. Коды слагаемых, включая знаковые

разряды, суммируются по правилам сложения двоичных чисел без

знака. Если в результате сложения возникает перенос из старшего

(знакового) разряда, он прибавляется к младшему разряду получен-

ной суммы. Такой перенос называют круговым переносом, а сложение,

в котором предусмотрен круговой перенос, называют циклическим

сложением.

В результате получается правильный обратный код алгебраиче-

ской суммы для чисел, представляемых кодами слагаемых, если

только не произойдет переполнения. Как и для дополнительного кода,

переполнение происходит тогда и только тогда, когда оба слагаемых

немеют одинаковые знаки, а знак суммы оказывается противополож-

ным. Так же как и в дополнительном коде, переполнение можно оп-

ределять по переносам в и из знакового разряда, но делать это надо

до прибавления кругового переноса.

Заметим, что алгоритм сложения в обратном коде тот л<е, что и в

дополнительном, с единственным отличием: перенос из знакового

разряда должен быть прибавлен к результату. Следующие примеры

поясняют алгоритм (числа в них представлены в пятиразрядном об-

ратном коде):

Пример

Слагаемое

Слагаемое

СуММО

(+14)= 0,1110

+ (—3)= +1,1100

ДО,1010

+ 1 = Круговой

(+11)= 0,1011 перенос

Пример

Слагаемое (+ 9) = 0,1001

Слагаемое + (-14)= +1,0001

Сумма (~5)= 1,1010

2.7 ДЕСЯТИЧНАЯ АРИФМЕТИКА

41

Вычитание в обратном коде также выполняется путем обращения

кода вычитаемого и его последующего сложения с кодом уменьшаемого.

Следующий пример поясняет эту операцию:

Пример

Умень шаемое (—6) =

'Вычитаемое — (—13) =

1,1001 1,1001

-1,001.0 +0,1101

Разность ( + 7) =

110,0110

+ 1 = Круговой

“адш леренос

2.7. ДВОИЧНО-КОДИРОВАННЫЕ ДЕСЯТИЧНЫЕ ЧИСЛА

И ДЕСЯТИЧНАЯ АРИФМЕТИКА

Популярность двоичной системы счисления в вычислительной

технике объясняется простотой и надежностью электронных схем,

работающих с числами, имеющими только две цифры. Для человека

эта система неудобна, и поэтому иногда желательно, чтобы вычисли-

тельная система работала с десятичными числами. Для сочетания

простоты двоичной системы с удобствами десятичной применяют

схемы, в которых цифры десятичной системы кодируются группами