Author: Сапожников Вл.В. Сапожников В.В.

Tags: организация производственного процесса производственное планирование управление качеством компьютерные технологии железнодорожный транспорт автоматика техническая диагностика

ISBN: 5-89035-123-0

Year: 2004

АВТОМАТИКА ГЕЛЕМЕХАНИКА И СВЯЗЬ

НА ЖЕЛЕЗНОДОРОЖНОМ ТРАНСПОРТЕ

ЫСШЕЕ

УДК 658.5:681.3

ББК 39.275

С 195

q 195 Сапожников В.В., Сапожников Вл.В. Основы технической

диагностики: Учебное пособие для студентов вузов ж-д.

транспорта. М.: Маршрут, 2004. — 318 с.

ISBN 5-89035-123-0

Изложены основные понятия и методы технической диагностики.

Описаны модели неисправностей логических схем. Рассмотрены мето-

ды построения тестов для комбинационных схем и схем с памятью. Изло-

жена теория контроля контактных схем. Даны основные структуры фун-

кционального диагностирования микропроцессорных систем и систем

непрерывного типа.

Учебное пособие предназначено для студентов вузов железнодорож-

ного транспорта по специальности Автоматика, телемеханика и связь

на железнодорожном транспорте и может быть полезно аспирантам и

инженерно-техническим работникам.

УДК 658.5: 681.3

ББК 39.275

Книгу написали: В.В.Сапожников— главы 1, 2и5; Вл.В.Са-

пожников — введение, главы 3, 7 и 8; Сапожников В. В. и Сапожни-

ков Вл. В, — главы 4 и 6.

Рецензенты: начальник отдела организации разработок и вне-

дрения новых технических средств Департамента автоматики и теле-

механики ОАО «РЖД» Е.А. Гоман; заведующий кафедрой «Транспорт-

ная связь» РГОТУПСа, д-р техн, наук, проф. В. М. Алексеев.

ISBN 5-89035-123-0

© Сапожников В.В., Сапожников Вл.В., 2004

© Издательство «Маршрут», 2004

© УМЦ МПС России, 2004

ВВЕДЕНИЕ

Техническая диагностика является областью науки о распозна-

вании состояний технических объектов. Эта задача возникает при

производстве изделий на заводах и затем при их технической эксп-

луатации При выпуске изделия на заводе необходимо убедиться в

его исправности. Это означает, что изделие должно удовлетворять

всем требованиям нормативно-технической и конструкторской

документации. Если какое-то требование не выполняется, то изде-

лие бракуется. Процент годности выпускаемой продукции являет-

ся главным показателем качества производства.

В процессе эксплуатации технического объекта необходимо конт-

ролировать его работоспособность. При возникновении отказов

объект теряет способность выполнять свои основные функции. В этом

случае требуется зафиксировать факт отказа, определить место его

возникновения и осуществить замену неисправного элемента или

блока. Впоследствии такие блоки могут ремонтироваться специа-

лизированными бригадами в ремонтно-технологических участках.

В процессе эксплуатации возникают также проблемы предска-

зания состояния объекта в будущем (проблема прогноза) и опреде-

ления состояния объекта в прошлом (проблема генезиса). В пер-

вом случае за счет фиксации предотказных состояний прогнозиру-

ется возможность отказа объекта и осуществляются мероприятия

по его предотвращению. Определение состояния объекта в про-

шлом требуется при анализе надежности и качества эксплуатации

объекта, при сборе статистических данных, а также при разборе

возникших инцидентов и происшествий.

Указанные задачи решаются с помощью тестового и функциональ-

ного диагностирования. Тестовое диагностирование применяется,

когда объект не используется по назначению. На объект подаются

входные тестовые воздействия и фиксируется его реакция, которая

сравнивается с эталонной. При функциональном диагностировании

тестовыми воздействиями являются рабочие входные воздействия.

В различных разделах технической диагностики разрабатываются:

- диагностические модели объектов и модели неисправностей;

- методы построения проверяющих и диагностических тестов;

- алгоритмы диагностирования;

3

- технические средства диагностирования;

- структуры контролепригодных объектов;

- способы автоматизации процессов диагностирования;

- методы обработки диагностической информации;

- методы оценки полноты и эффективности тестирования.

При эксплуатации устройств железнодорожной автоматики,

телемеханики и связи решение проблем технического диагности-

рования имеет первостепенное значение, поскольку эти устройства

являются обслуживаемыми и восстанавливаемыми. При их отка-

зах может произойти задержка поездов и в худшем случае наруше-

ние безопасности движения. Перед эксплуатационным и обслужи-

вающим персоналом (инженерами и электромеханиками) стоят за-

дачи контроля и поддержания исправного состояния устройств, а

в случае возникновения отказов — быстрого их обнаружения и ус-

транения. Решение этих задач усложняют особенности эксплуата-

ции таких устройств: непрерывный характер работы; длительный

срок службы (15—20 лет); широкое распространение по всей стра-

не; сложные климатические, динамические и электромагнитные

условия работы.

Релейные системы, составляющие пока еще основную массу ап-

паратуры железнодорожной автоматики, имеют хорошую диагно-

стируемость, поскольку реле — это элемент, состояние которого

можно наблюдать визуально. По этой причине оперативная инфор-

мация, выносимая в виде световой индикации на пульты-табло,

служит и достаточно полной диагностической информацией. Ис-

пользование такой информации удобно при организации регла-

ментного (профилактического) обслуживания. При этом работы

по контролю и поддержанию исправности устройств осуществля-

ются периодически во времени по заранее составленному графику.

Если возникает отказ, то бригада электромехаников немедленно

занимается его устранением. Среднее время восстановления уст-

ройств по сети дорог (включая время прибытия на место по-

вреждения) составляет от 30 мин до 1 ч.

При эксплуатации современных микроэлектронных и компью-

терных систем целесообразен переход к восстановительной стра-

тегии обслуживания. Эти системы имеют существенно более высо-

кую надежность, чем релейные, и не требуют профилактического

4

контроля. В то же время устранение неисправностей в них на поря-

док сложнее, поэтому необходимо применение отказоустойчивых

и легко диагностируемых устройств. Для таких систем предпочти-

тельно сервисное обслуживание, когда поиск повреждений и ре-

монт микроэлектронной аппаратуры осуществляются в специали-

зированных центрах.

Таки$л образом, техническое диагностирование является важ-

ной составляющей в ежедневной практике инженеров в области

железнодорожной автоматики, телемеханики и связи. В данном

пособии рассмотрены основные понятия технической диагности-

ки и модели неисправностей. Изложена теория контроля контакт-

ных схем и методы диагностирования комбинационных схем и схем

с памятью. Рассмотрены основные способы функционального ди-

агностирования дискретных систем.

Учебное пособие предназначено для студентов вузов железнодо-

рожного транспорта по специальности Автоматика, телемеханика

и связь на железнодорожном транспорте и может быть полезно ас-

пирантам и инженерно-техническим работникам в данной области.

5

Глава 1

ОСНОВЫ ТЕОРИИ ТЕХНИЧЕСКОЙ

ДИАГНОСТИКИ

1.1. Основные понятия и определения

Под технической диагностикой понимается область знаний, ох-

ватывающая теорию, методы и средства определения техническо-

го состояния объекта. Техническое состояние характеризуется в

определенный момент времени при заданных условиях внешней

среды значениями параметров, установленных технической доку-

ментацией на объект.

Процесс определения технического состояния объекта назы-

вается диагностированием. Результат диагностирования, т.е. зак-

лючение о техническом состоянии объекта, называется диагнозом

[2, 11, 14, 19, 20, 35].

В общем случае различают три типа задач по определению со-

стояния технического объекта. Задача диагноза —- это определение

состояния, в котором находится объект в настоящий момент вре-

мени. Она возникает при решении вопроса о работоспособности и

исправности объектов, поиске в них неисправностей, при провер-

ке устройств после их изготовления. Задача прогноза состоит в пред-

сказании состояния, в котором окажется технический объект в не-

который последующий момент времени. Такая задача часто реша-

ется при эксплуатации устройств железнодорожной автоматики, те-

лемеханики и связи, имеющих длительный срок службы. При этом

определяется периодичность профилактических проверок и ремон-

тов с целью предсказания и недопущения выхода устройств из строя.

Задача генезиса заключается в определении состояния, в котором на-

ходился технический объект ранее. Правильное решение згой задачи

важно для систем железнодорожной автоматики при определении

причин отказов систем с целью их дальнейшего предупреждения.

На практике наиболее часто решается задача диагноза. Более

того, при решении задач прогноза и генезиса всегда приходится

решать и задачу диагноза. Наряду с технической диагностикой па-

раллельно развиваются и тесно связаны с ней техническое прогно-

зирование и техническая генетика.

6

Технический объект (система, машина, прибор, узел и т.п.), для

которого решается задача распознавания состояния, называется

объектом диагностирования (ОД).

В качестве ОД могут выступать любые технические системы,

которые удовлетворяют двум условиям: могут находиться, по край-

ней мере, в двух взаимоисключающих и различимых состояниях

(например, работоспособном и неработоспособном); в них можно

выделить элементы, каждый из которых также характеризуется

указанными различимыми состояниями.

Главной отличительной особенностью объекта технического

диагностирования является то, что его состояние в целом рассмат-

ривается как функция, зависящая от состояний входящих в него

элементов. Примером ОД может служить система электрической

централизации (ЭЦ), которая предназначена для управления стрел-

ками и сигналами на станции. Она имеет работоспособные и нера-

ботоспособные состояния. К работоспособным относится состоя-

ние, при котором возможны задание, замыкание, размыкание и

отмена всех маршрутов. ЭЦ имеет много неработоспособных со-

стояний, при которых невозможны перевод каких-либо стрелок,

открытие сигнала при замкнутом маршруте и т.д. В качестве эле-

ментов ЭЦ содержит блоки (рис. 1.1), которые имеют работоспо-

собные и неработоспособные состояния. Блоки, в свою очередь,

являются ОД, так как в качестве элементов они имеют реле, тоже

имеющие работоспособное и неработоспособное состояния. По-

иск неисправности в блочной системе ЭЦ состоит из двух этапов.

Сначала систему рассматривают как совокупность блоков, где

находится неисправный блок. Затем последний анализируют как

совокупность реле и на-

ходят неисправное реле.

Понятие «состояние

ОД» является ключевым в

технической диагностике.

Состояние ОД оценивает-

ся по диагностическим

признакам. Диагностичес-

ким признаком (ДП) назы-

вается параметр или ха-

Реле

Рис. 1.1. Система электрической централи-

зации как объект диагностирования

7

рактеристика, используемые при диагностировании. В качестве

параметров могут выступать значения сигналов (физические вели-

чины) какого-либо рода на отдельных выходах системы или во

внутренних контрольных точках. В системах железнодорожной

автоматики, телемеханики и связи (системах ЖАТС) в качестве

параметров наиболее часто используются напряжение, сила тока,

частота тока, сопротивление цепи, мощность и др. Характеристи-

ки, представляющие собой зависимость одной физической вели-

чины от другой, используются при диагностировании устройств

связи, рельсовых цепей и в других случаях.

При диагностировании сложных многофункциональных систем

управления (к ним относятся многие системы железнодорожной

автоматики) в качестве параметра специального вида можно рас-

сматривать возможность системы выполнять те или иные отдель-

ные заданные функции: например, возможность управления стрел-

ками и светофорами.

Диагностические признаки делят на основные и вспомогатель-

ные. Основные характеризуют выполнение системой заданных фун-

кций, а вспомогательные — удобство эксплуатации, внешний вид

и т.п. Каждому состоянию ОД соответствует определенное значе-

ние диагностического признака.

Диагностические признаки выбираются в результате анализа

диагностической модели, под которой понимается формальное

описание ОД (в аналитической, табличной, графической и других

формах), учитывающее изменение его состояний.

Различают четыре вида состояний ОД: исправные, неисправные,

работоспособные и неработоспособные. Систему называют wc-

правной, если она соответствует всем предъявляемым к ней требо-

ваниям (фиксируются в нормативной документации), когда все ее

параметры, как основные, так и вспомогательные, находятся в пре-

делах заданной нормы. Выход за эти пределы любого параметра

означает, что система неисправна.

Система находится в работоспособном состоянии, если ее основ-

ные параметры находятся в пределах заданной нормы и она пра-

вильно выполняет заданные функции. Выход хотя бы одного ос-

новного параметра за пределы заданной нормы переводит систе-

му в множество неработоспособных состояний. Утрату работоспо-

8

собности также называют отказом. Работоспособная система мо-

жет быть как исправной, так и неисправной. Исправная система

всегда работоспособна. Неисправная система может быть как ра-

ботоспособной, так и неработоспособной. Неработоспособная

система всегда неисправна.

Диаграмма состояний ОД показана на рис. 1.2. Полное множе-

ство возможных состояний

W-АиВиС,

где А — множество состояний исправных систем; В — множе-

ство состояний неисправных, но работоспособных систем; С —

множество состояний отказавших систем.

Множества состояний работоспособных и неисправных систем

соответственно

В области построения систем ЖАТС важнейшей задачей явля-

ется синтез контролепригодных систем с повышенным уровнем

надежности. Их построение связано с введением большого числа

состояний 5, G В. При этом система строится таким образом, что-

бы при всех наиболее вероятных отказах ее элементов (частич-

ных отказах) был невозможен переход системы из множества со-

стояний А в множество С, а система оказывалась бы в множестве

состояний В. В этом случае си-

стема продолжает выполнять

свои основные функции (мо-

жет быть с ухудшенными пока-

зателями), но имеется возмож-

ность зафиксировать возник-

шую неисправность и устра-

нить ее, тем самым предупре-

див потерю системой рабо-

тоспособности. На рис. 1.3

приведен граф переходов меж-

ду состояниями системы с уче-

том процесса диагностирования.

Рис. 1.2. Диаграмма состояний ОД

9

На рис. 1.4 представлена структу-

Рис. 1.3. Граф переходов между

состояниями объекта диагности-

рования

ра системы управления стрелками

и сигналами на станции. Она пре-

дусматривает три уровня управле-

ния. Первый уровень соответству-

ет полной автоматизации управле-

ния, при котором задача перевода

стрелок и включения светофоров

решается автоматически при по-

мощи средств вычислительной тех-

ники на основе заданного графи-

ка движения поездов и информа-

ции о фактическом выполнении

этого графика. При выходе из строя системы автоматического уп-

равления осуществляется переход на уровень частичной автомати-

зации управления, при котором в процесс управления включается

оператор. Последний путем определенных операций на пульте уп-

равления осуществляет установку и отмену маршрутов движения

поездов. При этом сохраняется возможность автоматического пе-

ревода стрелок, а также обеспечивается проверка необходимых ус-

1 уровень

2 уровень

3 уровень

Рис. 1.4. Структура современной системы управления стрелками

и сигналами на станции

10

ловий безопасности. Переход с первого уровня управления на вто -

рой связан с потерей эффективности управления (увеличение вре-

мени установки маршрута, появление возможности ошибок опе-

ратора и др.). Если отказывают одновременно системы полной и

частичной автоматизации, то осуществляется переход на индиви-

дуально^ управление стрелками и сигналами. В этом случае для

перевода каждой стрелки и включения каждого светофора от опе-

ратора требуется отдельное воздействие на пульте управления, что

еще более снижает эффективность управления. Неотъемлемой частью

системы автоматизации управления являются устройства диагности-

рования, которые обеспечивают фиксацию и обнаружение неисправ-

ностей и позволяют эксплуатировать систему длительное время так,

чтобы избегать третьего уровня управления.

Если ОД находится в работоспособном состоянии и выполняет

заданные функции, то говорят, что объект функционирует штатно.

Если объект выполняет часть функций, находясь в неработоспо-

собном состоянии, то говорят, что он функционирует нештатно.

Поэтому наряду с полным отказом, приводящим к полной потере

работоспособности, различают частичный отказ, который приво-

дит к потере работоспособности и нештатному функционирова-

нию. Например, полный отказ схемы управления стрелкой зак-

лючается в невозможности ее перевода из одного положения в дру-

гое. Система ЭЦ имеет частичные отказы, когда теряется возмож-

ность установки некоторых (но не всех) маршрутов.

Относительно отдельных элементов различают также третий тип

отказа — перемежающийся отказ. Такой отказ попеременно исче-

зает, а затем снова появляется. Это затрудняет определение место-

положения отказавшего элемента, так как при проверке системы, в

которую входит элемент, она может оказаться работоспособной, а

через некоторое время неработоспособной.

Причиной потери работоспособности является дефект (от лат.

defectus -г- изъян, недочет, недостаток). В ОД, состоящем из несколь-

ких элементов, дефектом являются отказ элемента, нарушение свя-

зи или появление связи между элементами. В электронной аппара-

туре иногда дефект определяют как неисправность. Тогда под ис-

правным ОД понимают объект, в котором нет ни одного дефекта

(неисправности). Неисправный ОД содержит хотя бы один дефект.

В системах с избыточностью (структурной, временной, информа-

ционной) не всякая неисправность приводит к потере работоспособ-

ности. Для этого может потребоваться накопление неисправностей,

которые возникают последовательно во времени. В тех случаях, ког-

да в системе возникла неисправность, но система не потеряла рабо-

тоспособность, говорят, что запас работоспособности снизился, а сле-

довательно, повысилась вероятность отказа системы в дальнейшем.

1.2. Задачи технической диагностики

При диагностировании решаются задачи точного определения

состояния, в котором находится система, или установления мно-

жества состояний, в одном из которых она находится. Это опреде-

ляется тем, какая задача ставится при исследовании ОД. Различа-

ют пять задач диагностирования.

Первая задача диагностирования — проверка исправности, при

которой решается задача обнаружения в объекте любой неисправ-

ности, переводящей ОД из множества исправных состояний А в

множество неисправных состояний (см Рис- 1 -2). Она возника-

ет при изготовлении устройств на заводах, включении их после дол-

гого хранения или ремонта. При введении в эксплуатацию уст-

ройств ЖАТС (например, при регулировке и пуске ЭЦ) проверяют

все элементы, узлы, цепи, источники питания и изоляцию. Часто

это очень трудоемкий процесс, для упрощения которого необхо-

димо применять методы технического диагностирования.

Вторая задача диагностирования — проверка работоспособнос-

ти, при которой решается задача обнаружения тех неисправностей,

которые переводят ОД из множества работоспособных систем в

множество отказавших систем С. Во время проверки работоспособ-

ности можно оставлять необнаруженными неисправности, не пре-

пятствующие применению системы по назначению. Например, при

наличии резервирования система может быть работоспособна, не-

смотря на наличие неисправностей в резервных элементах. Поэтому

данная задача является менее детальной, чем проверка исправнос-

ти, и может быть решена более простыми методами. Проверка ра-

ботоспособности осуществляется при включении объекта в работу

или при профилактических осмотрах, а также когда имеется огра-

ничение на время, отведенное для проверки устройств.

12

Третья задача диапюстирования — проверка правильности функ-

ционирования — решается во время работы ОД. При этом достаточно

следить за тем, чтобы в объекте не появились неисправности, нару-

шающие ее нормальную работу в настоящий момент времени, и ис-

ключить недопустимое для нормальной работы влияние неисправно-

стей. Проверка правильности функционирования позволяет делать

вывод о правильной работе ОД только в данном режиме и в данный

момент времени. Указанная задача имеет важное значение для уст-

ройств железнодорожной автоматики, выполняющих ответственные

функции по регулированию движения поездов. В них надо следить за

тем, чтобы искажение алгоритма функционирования не приводило к

опасным последствиям в поведении объекта управления.

Четвертая задача диагностирования — поиск неисправностей

(дефектов), при котором решается проблема точного указания в

объекте неисправного элемента или множества элементов, среди

которых находится неисправный элемент. Поиск дефектов может

осуществляться в неисправных, неработоспособных и в неправиль-

но функционирующих устройствах во время наладки при произ-

водстве и во время ремонта при эксплуатации и хранении. Резуль-

татом процесса поиска неисправностей является разбиение мно-

жества состояний (если исследуется неисправный объект) или

множества состояний С (если исследуется неработоспособный

объект) на классы неразличимых между собой (или эквивалентных)

состояний, а также соответствующих им неисправностей. Эквива-

лентными неисправностями называются такие, которые нельзя от^~

личить друг от друга при принятом для исследования устройства

способе диагностирования. При этом решается вопрос — в каком

из классов эквивалентных состояний находится ОД: Число клас-

сов определяет ту степень детализации, которая достигается при

поиске неисправностей. Ее называют глубиной диагноза (поиска).

Например, в любой блочной системе дефекты всех элементов,

входящих в один блок, образуют в большинстве случаев один класс

эквивалентных неисправностей. Поиск неисправностей в этом слу-

чае ведется до неисправного блока, замена которого на исправ-

ный обеспечивает восстановление работоспособности системы.

Пятая задача диагностирования — прогнозирование состояния*

ОД, для решения которой изучается характер изменения диагнос-

13

тических параметров и на основе сформировавшихся тенденций

предсказываются значения параметров в будущий момент времени.

Эффективность диагностирования ОД достигается в том случае,

когда задачи диагностирования учитываются на всех этапах жиз-

ни технического объекта (рис. 1.5). При проектировании решают-

ся общие вопросы организации системы диагностирования. На ос-

нове анализа ОД составляется ее диагностическая модель, проек-

тируются технические средства диагностирования (СД), а также

оценивается эффективность диагностирования.

При изготовлении объекта целесообразно одновременно изго-

товлять и СД. При этом главной задачей является обеспечение всех

требований, предъявляемых к ОД и СД. При сборке и наладке ОД

может возникать задача поиска дефектов. На заключительной ста-

дии осуществляется выходной контроль и производится проверка

исправности объекта.

Рис. 1.5. Диагностирование на всех этапах жизни технического объекта

14

В процессе эксплуатации диагностирование ведется непрерыв-

но или периодически с целью контроля правильности функциони-

рования или работоспособности объекта. В случае необходимос-

ти осуществляются прогнозирование или поиск возникшего дефек-

та для выполнения профилактических или восстановительных ра-

бот. Диагностирование на этом этапе позволяет обоснованно при-

нимать*решения об использовании объекта в требуемый момент

времени.

1.3. Тесты диагностирования

Объект диагноза ОД представляют в виде устройства (рис. 1.6),

имеющего входы и доступные для наблюдения выходы. Процесс

диагностирования представляет собой последовательность опера-

ций, каждая из которых предусматривает подачу на входы объек-

та некоторого воздействия и определения на выходах реакции на

это воздействие. Такую элементарную операцию называют про-

веркой л. В качестве выходов наблюдения могут служить основ-

ные или рабочие выходы системы, а также и дополнительные (кон-

трольные) выходы.

Совокупность проверок,, дозволяющую решать, какую-либо из

задач диагноза^ называют тестом: Т = тгъ л7, ... ,л„. Под длиной

1' X’ ’ л — —

теста L понимают число входящих в него проверок.

По назначению тесты цедят на проверяющие и диагностичес-

кие^рс^еряющийдестпроверок, позвсь

ляющая обнаружить в системе любую неисправность из заданного

спиСка \множсства). Проверяющий тест решает задачи проверки

исправности системы (в этом случае в список неисправностей вклю-

чают все возможные в системе неисправности) и проверки рабо-

тоспособности (в список включают только те неисправности, ко-

торые приводят к отказу системы).

Диагностическим тест Тд

это совокупность проверок, по-

зволяющая указать месго-ыеис-

правностис точностью до клас-

сов^кшдаадатных неисправно-

стей. Он_позволяет решать, за-

дачу поиска неисправностей.

Входы

Выходы

Рис. 1.6. Объект диагноза ОД

15

Важной характеристикой процедур диагностирования является

полнота обнаружения неисправностей, задающая долю гаранти-

рованно обнаруживаемых неисправностей относительно всех за-

данных или рассматриваемых неисправностей объекта диагноза.

Любая диагностическая процедура (а также и тест диагноза) обя-

зательно связывается с определенным, строго фиксированным спис-

ком неисправностей, обнаружение которых обеспечивается при ее

проведении. Это фактически определяет ограничение, накладыва-

емое на процесс обнаружения неисправностей, и в конечном итоге

определяет глубину диагностирования.

По полноте обнаружения неисправностей различают одиноч-

ный, кратный и полный тесты. Одиночный тест обнаруживает в

ycfpuiiClBc все одииичггйёЛюврсждения входящих в него элемен-

тов. Кратный тест обнаруживает все возможные совокупности из

к одиночных неисправностей элементов, причем тест кратности к

должен фиксировать не только все совокупности из к одиночных

неисправностей, но и все неисправности меньшей кратности, в том

числе все одиночные неисправности. Полный тест обнаруживает

неисправности любой кратности. Использование того или иного

теста определяется решаемой задачей диагноза. Так, при исследо-

вании устройства, в котором неисправность возникла в процессе

функционирования, как правило, используют одиночные тесты, так

как вероятность возникновения одновременно нескольких неис-

правностей невелика. По сравнению с одиночными полные тесты

имеют гораздо большую длину и поэтому требуют для испытания

устройства больше времени. Их применяют при контроле устройств

в процессе изготовления, когда вероятность одновременного су- ,

шествования нескольких повреждений повышается из-за дефектов

комплектующих изделий и ошибок в монтаже и настройке.

Независимости от длины разпичяют тр.ивиальный, минималь-

ный и минимизированный тесты. Тривиальный тест, содержащий

все возможные для данной системы проверки, имеет максималь-

нуюдлину. Применение тривиального теста предусматривает пол-

ное моделирование работы устройства. Наименьшее число прове-

рок имеет минимальный тест Tm|n. Он обеспечивает решение за-

данной задачи диагноза, при этом для данного устройства не су-

ществует другого теста с меньшим числом проверок.

16

Построение Tmin требует больших вычислений, поэтому на

практике чаще строят минимизированные тесты, имеющие длину,

близкую к длине минимальных тестов.

С помощью теста строится процедура диагностирования, в ос-

нове которой лежат алгоритм диагностирования, представляющий

собой последовательность элементарных проверок, составляющих

тест, и правила анализа результатов этих проверок. Алгоритм ди-

агностирования реализуется средствами диагностирования.

1.4. Математические модели объектов диагноза

Объекты диагноза подразделяют на два класса. Непрерывные (ана-

логовые) объекты имеют такие входные, внутренние и выходные сиг-

налы, которые могут принимать значения из некоторых непрерывных

множеств значений, а время, в котором дается описание объекта, от-

считывается непрерывно Дискретные объекты имеют такие сигналы,

значения которых задаются на конечных множествах, а время отсчи-

тывается дискретно. Возможны также гибридные системы, в которых

одни сигналы являются непрерывными, а другие — дискретными.

Кроме того, объекты диагноза делят на комбинационные и после-

довательные. Комбинационные, или объекты без памяти, характе-

ризуются взаимно однозначным соответствием между входными и

выходными сигналами. Последовательные, или объекты с памятью,

имеют выходные сигналы, значения которых зависят не только от

значений входных сигналов, но и от времени.

В железнодорожной автоматике применяют системы всех ука-

занных типов. Рельсовые цепи являются непрерывными система-

ми без памяти; аналоговая система регулирования скорости дви-

жения отцепа на сортировочной горке — непрерывной системой с

памятью. В качестве дискретных комбинационных систем можно

рассматривать схемы управления огнями светофоров, а в качестве

дискретных систем с памятью — схемы замыкания и размыкания

маршрутов в любой системе ЭЦ.

Для построения тестов и алгоритмов диагноза необходимо иметь

формальное описание объекта и его поведения в исправном и неис-

правном состояниях. Такое формальное описание называют матема-

тической моделью объекта диагноза. Различают модели с явным и не-

явным описанием неисправностей. Явная модель объекта диагноза со-

17

стоит из описаний его исправной и всех неисправных модификаций.

Неявная модель содержит описание исправного объекта, математичес-

кие модели его физических неисправностей и правила получения по

ним всех неисправных модификаций объекта. Выбор модели является

важным элементом процесса организации процедуры диагноза.

Наиболее общий характер имеет модель ОД [36] в виде таблицы

функции неисправностей (ТФН) (табл. 1.1).

Таблица 1.1

Проверка Результат Л проверки д ля системы, находящейся в состоянии

5() 51 « а 5,

л, л2 • * л/ • а S3 . . . S5 . . . *3 S3 О д о к, о — ’ Сс; ‘ 1 ’ • « 4 « » а • • • • » • • » • « я/ Ri • я; о • ♦ * • • • • * • • a w а а • а as сеГ

Эта таблица является явной моделью и может быть построена

для объекта любой физической природы. В строках таблицы ука-

зывают все возможные проверки лу, которые могут быть исполь-

зованы в процедуре диагностирования, а следовательно, включе-

ны в тест. Графы таблицы соответствуют исправному и всем

возможным неисправным состояниям: Sj, ••• Каждое не-

исправное состояние соответствует одной неисправности (одиноч-

ной или кратной) из заданного класса неисправностей, относи-

тельно которого строится тест. Физический смысл состояний и

проверок определяется конкретными особенностями объекта ди-

агноза. На пересечении У-й графы и j-й строки проставляется ре-

зультат R1 j-й проверки для системы, находящейся в У-м состоя-

нии. Если значение проверки /?/ в объекте с j-й неисправностью

18

совпадает с ее значением в исправном объекте, то в таблице запи-

сывается значение /?/ = 1; в противном случае записывается зна-

• *

чение RJ = 0. Таким образом, информация в ТФН записывается в

двоичном коде.

В табл. 1.2 приведен конкретный пример ТФН. Графа 50 всегда

заполняется одними единицами. Если две графы заполнены оди-

наково, то они соответствуют эквивалентным неисправностям и

могут быть объединены. В табл. 1.2 такими являются графы53 и

54. Если во всех элементах графы проставлены единицы (напри-

мер, графа 5g), то она соответствует неисправности, которая не мо-

жет быть обнаружена принятым методом диагностирования. Та-

кая графа исключается из ТФН. На основании указанных свойств

строится преобразованная ТФН (табл. 1.3), из которой также ис-

ключается графа 5q.

Таблица 1.2

5, 5, -е* S3 $4 $5 s6 Sy 5's

Я1 1 0 1 0 0 1 1 0 1

1 0 0 0 0 1 1 1 1

1 1 1 0 0 1 0 0 1

1 1 1 0 0 0 0 1 1

1 0 1 0 0 0 1 1 1

Таблица 1.3

51 S2 Л4 s5 $6 Sy

JQ 0 1 0 1 1 0

П2 0 0 0 1 1 1

«3 1 1 0 1 0 0

л4 1 1 0 0 0 1

ZS5 0 1 0 0 1 1

ТФН содержит всю необходимую информацию для получения

тестов, которые находят с помощью специально математической

обработки таблицы.

19

Рассмотрим процесс получения проверяющего теста Тп. По пре-

образованной ТФН (см. табл. 1.3) составляется таблица покрытий

(табл. 1.4), для чего в элементах таблицы, где проставлен 0, запи-

сывают знак покрытия (х), а те элементы, где проставлена 1, остав-

ляют незаполненными. Решается задача получения минимального

покрытия. Определяется такое минимальное множество строк таб-

лицы

что каждая графа имеет знак покрытия хотя

бы в одной строке этого множества. Тогда это множество состав-

ляет проверяющий тест.

Осуществляется сокращение таблицы покрытия. Для этого для

каждой графы Sj находится множество Q(S^, включающее в себя

те строки, на пересечении с которыми в графе проставлен знак

покрытия. Для табл. 1.4 имеем: 2(S]) = {л|?л2, л5}, ^(52) =

2(S3, S4) = {лр л2, л3, л4, л5}, (2(55) = {л4, л5}, 2(S6) = {л3, л4},

Q(Sy) = {Лр л3}. Если Q(Sp) с Q(St), то графуS{ исключают из

таблицы покрытий. Если Q(Sp) — Q(St), то исключается одна

(любая) из граф S Sr В табл. 1.4 исключают графы Sj [так как

(2(5{) с 6(52)] и (53, [так как Q(S3, S^) с 6(52)]. В результате

образуется сокращенная таблица покрытий (табл. 1.5). ’

Таблица 1.4

$1 s2 S3, S4 S5 $6 s7

X X х

Hz X X X

л3 X X X

л4 X X X

X X X

Таблица 1.5

s2 $5 s6 s7

Л1 X

я2 X

Лз X X

*4 X X

X

20

По сокращенной таблице покрытий составляется следующее

логическое выражение:

(1.1)

** f-

где 5 — множество граф таблицы; — проверки,

входящие в множество Q(St).

Оно преобразуется по законам алгебры логики, при этом осуще-

ствляются раскрытие всех скобок и удаление избыточных элементов^

По табл. 1.5 получаем

е(Т) = и2 (я4 V Л5 )(л3 V Л4 Хтг, V Л3) =

— Л2Л3Л4 V Л2Л3Л5 V Л1Л2Л4-

(1.2)

Полученное выражение представляет собой дизъюнкцию конъ-

юнкций. Каждая конъюнкция соответствует одному из возможных

проверяющих тестов. Тест образуется как множество проверок,

входящих в конъюнкцию. Из (1.2) следует, что в рассматриваемом

примере существуют три теста одинаковой длины:

Тп, {Я2,7С3,Я4^; Тп, ^2,71:3’Я5^; Тп, Ц»Л2,Я4^

Для построения диагностического теста Тд по таблице покры-

тий (см. табл. 1.4) составляется диагностическая таблица покры-

тий (табл. 1.6). Она содержит граф, где к — число граф исход-

ной таблицы покрытий. Каждая графа соответствует одному со-

четанию (S? S-) из двух неисправных состояний, включенных в

табл. 1.4. В табл. 1.6 эти состояния расположены в столбик. В гра-

фе, соответствующей сочетанию (Sy, Sy), проставляется знак покры-

тия во всех строках, где этот знак расположен в графах St и Sy, кро-

ме тех строк, в которых знак покрытия записан в обеих графах.

Знаки покрытия в графе (Sy, S,) указывают те проверки, при помо-

щи которых при диагностировании можно различить друг от дру-

га неисправные состояния Sy и Sj.

21

Таблица Тб

Si, $3 5ь 55 5b 5б 5„ 57 52, 53 52. S, 52, 56 52, 5s 53, 56 5з, 57 55, 56 55, 57 5б, 5?

TTj X X X X X X X X X

X X X X X X X X X

Дз X X X X X X X X X

л4 X X X X X X X X X

X X X X X X X X X

Диагностическая таблица покрытий преобразуется по указан-

ным выше правилам в сокращенную таблицу (табл. 1.7).

Таблица 1.7

"\5 71^\ 5Ь 52 5ь 53 52, 57 S3, s7 55, 56 5е, 57

7lj X X X

"2 X X

X X X

.... Л4 X X X

"5 X X X

Различают два вида диагностического теста. Тест использу-

ется в том случае, когда заведомо известно, что объект неиспра-

вен, и поэтому решается одна задача — обнаружение неисправно-

го элемента. В этом случае по сокращенной таблице составляется

выражение вида (1.1), которое преобразуется с целью получения

всех возможных диагностических тестов.

По табл. 1.7 получаем

С(Т) = ( л1 v л5)(л3 v л4)( л, v л2 v л3 )(л2 v л4 v л5 ) х

V Л[Л4 Л5 V

УЛ-ЛЛ. V Л.Л-Л..

2 4 5 1 2 4

х(л- УлДл. V Л.) = Л. Л, Л, УЛ.Л.Л

J J А 1 -1

(1.3)

По выражению (1.3) определяем следующие варианты диагнос-

тического теста:

22

По диагностическому тесту составляется словарь неисправнос-

тей, позволяющий фиксировать неисправность при помощи вы-

полнение формальной процедуры. Словарь неисправностей пред-

ставляет собой таблицу, являющуюся частью сокращенной ТФН

(см. табл. 1.3). В эту таблицу входят строки, соответствующие про-

веркам, входящим в Тд, и графы, соответствующие классам экви-

валентных неисправностей.

В табл. 1.8 представлен словарь неисправностей, составленный

для теста = {т^, л4, л5}. Словарь неисправностей не содержит

одинаково заполненных граф, но может содержать графу, запол-

ненную одними единицами. По результатам всех входящих в таб-

лицу проверок определяется неисправный элемент.

Таблица 1.8

\5 51 5? 53,54 s, 5б 57

0 1 0 1 1 0

л4 1 1 0 0 0 1

S 0 1 0 0 1 1

2

Диагностический тест второго вида Т применяется в том слу-

г

чае, когда совмещаются в едином процессе проверка исправности

и поиск неисправностей в объекте. При этом диагностический тест

составляется по построенному ранее одному из вариантов прове-

ряющего теста. Сокращенная диагностическая таблица покрытия

(см. табл. 1.7) подвергается дальнейшему сокращению, для чего из

нес исключаются столбцы, в которых проставлен знак покрытия

хотя бы в одной строке, входящей в проверяющий тест. Напри-

мер, рассмотрим табл. 1.7 и проверяющий тест ^2, л4)

uJr

В табл. 1.7 исключаются все графы, кроме графы с сочетанием со-

стояний (S5, S^), в результате получаем табл. 1.9. По этой таблице

составляется выражение (1.1) и определяется необходимое число

23

проверок, которыми необходимо дополнить проверяющий тест,

чтобы получить диагностический.

В данном случае существует два варианта теста:

{, 712 * Л3 ’ ^4 )

Т2

Д1

Таблица 1.9

$5, s6

... 7С1

712

71? X

Т14

X

Таблица 1.10

So Si & S3, S4 Ss s7

71, 1 0 1 0 1 1 0

Л2 ... 1 0 0 0 1 1 1

тц 1 1 1 0 1 0 0

«4 1 1 1 0 0 0 1

В табл. 1.10 приведен словарь неисправностей для первого из

них. В этом случае в таблицу включается графа, соответствующая

исправному состоянию объекта Sq.

Недостатком ТФН являются ее большие размеры, так как чис-

ло столбцов таблицы определяется общим числом возможных не-

исправностей в ОД. Кроме того, если результат проверки в ТФН

записывается в двоичной форме, то она является логической моде-

лью ОД. В ряде случаев логическая модель существенно упрощает

объект и поэтому не позволяет решить некоторые из задач техни-

ческого диагностирования. Однако ТФН очень наглядна и удоб-

на для анализа любого устройства и ее часто используют как не-

посредственно, так и в сочетании с другими моделями. Эффектив-

ным оказывается применение явных моделей, разработанных для

узкого класса объектов.

24

Для непрерывных систем используют модели в виде графов при-

чинно-следственных связей или диаграмм прохождения сигналов,

а также топологические модели. Для дискретных систем приме-

няют таблицы истинности, логические сети, альтернативные гра-

фы, эквивалентную нормальную форму представления булевых

функций, таблицы переходов-выходов многотактных схем и ин-

терактивные модели. Выбор модели влияет на глубину и трудо-

емкость процесса диагностирования. Указанные модели будут рас-

смотрены далее при анализе ОД различного вида.

Глава 2

СИСТЕМЫ ДИАГНОСТИРОВАНИЯ

2.1. Функциональные схемы систем

диагностирования

При решении какой-либо задачи диагностирования исследуе-

мый объект подвергается некоторым испытаниям. В общем случае

процесс диагностирования представляет собой многократную по-

дачу на объект (см. рис. 1.6) определенных входных воздействий,

многократное измерение и анализ ответов (выходных сигналов или

реакций) на эти воздействия, которые могут поступать на входы

объекта от средств диагностирования (СД) или являться внешними

(рабочими) сигналами, определяемыми алгоритмом функциониро-

вания устройства. Измерение и анализ ответов объекта всегда осу-

ществляется средствами диагностирования. Взаимодействующие

между собой ОД и СД образуют систему диагностирования [8]

Различают два вида систем диагностирования (рис. 2.1).

Система тестового диагностирования (рис. 2.1, а) предусматри-

вает подачу воздействий на ОД со стороны СД. Других воздействий

на ОД не поступает. Поэтому как состав, так и последовательность

подачи этих воздействий можно выбирать исходя из условий эф-

фективной организации процесса диагностирования. При этом

каждое очередное воздействие можно назначать в зависимости от

ответов объекта на предыдущие воздействия. Воздействия в такой

системе называют тестовыми.

а б Рабочие

диагностирования

диагностирования

Рис. 2.1. Системы диагностирования технического состояния ОД:

а — тестовое диагностирование; б— функциональное диагностирование

26

Результаты

диагностирования

В системе функционального диагностирования (рис. 2.1, б) СД не

формирует воздействий на ОД. На ОД и СД поступают рабочие воз-

действия, предусмотренные алгоритмом функционирования объекта.

Система диагностирования действует в процессе рабочего функциони-

рования ОД и решает задачи правильности функционирования и поис-

ка неисправностей, нарушающих нормальное функционирование.

В функциональной схеме системы тестового диагностирования

(рис. 2.2, а) блок управления (БУ) служит для хранения алгоритма ди-

агностирования и управ-

ления работой средств

диагностирования. Ис-

точник воздействий (ИВ)

вырабатывает воздей-

ствия Oj в виде элемен-

тарных проверок, вхо-

дящих в тест, и в соот-

ветствии с алгоритмом

диагностирования в оп-

ределенной последова-

тельности подает их че-

рез устройство связи

(УС) на объект диа! но-

за (ОД), а также на мо-

дель объекта диагноза

(МОД). Блок МОД вы-

рабатывает информа-

цию о возможных тех-

нических состояниях

ОД в виде возможных

результатов Ь* элемен-

тарных проверок, вхо-

дящих в тест. од в ответ

на воздействие aj фор-

мирует фактические ре-

зультаты bj элементар-

ных проверок, которые

б

Результаты

диагностирования

Рис. 2.2. Схемы систем тестового (а)

и функционального (б) диагностирования

27

через УС и измерительное устройство (ИУ) поступают на вход бло-

ка расшифровки результатов (БРР). В этом блоке сравниваются ре-

зультаты элементарных проверок, снимаемых с выходов ОД и фор-

мируемых МОД. Результат сравнения запоминается в БРР, после

чего БУ назначает очередную элементарную проверку, входящую

в тест. Если назначение очередной проверки зависит от результата

предыдущей, то между блоками БРР и БУ устанавливается прямая

связь (показана штриховой линией). После прохождения всего или

части теста блок БРР формирует результаты диагностирования.

В функциональной схеме системы функционального диагнос-

тирования (рис. 2.2, б) рабочие воздействия л- поступают на ос-

новные входы ОД, с которого снимаются сигналы yj управления

средствами диагностирования и сигналы Ь- ответов ОД на воз-

действия aj. Сигналы управляют блоками БУ и МОД в зависи-

мости от режима работы объекта, при этом на входы МОД посту-

пают воздействия cij. Между блоками БРР и ОД устанавливается

прямая связь, (показана пунктиром), если ОД должен быть выклю-

чен из работы при отрицательных результатах диагностирования.

В конечном итоге процедура диагностирования сводится к срав-

нению работы идеального устройства (задается моделью ОД) и

реального исследуемого устройства. Число неисправностей в ре-

альном устройстве, как правило, велико, поэтому процедура диаг-

ностирования сложна и требует большого числа измерительных и

вычислительных операций. Для проведения процедуры диагнос-

тирования требуется решение следующих основных задач: выбор

и построение модели ОД, синтез теста, построение алгоритма ди-

агностирования, синтез и реализация средств диагностирования.

2.2. Функциональное диагностирование

Представим схему системы функционального диагностирования

(см, рис. 2.2, б) в виде схемы из двух блоков (рис. 2.3). В ней вся

дополнительная аппаратура объединена в едином блоке — схеме

контроля (СК). Результатом диагностирования является сигнал

ошибки, который формируется при возникновении дефекта в ОД, а

также, может быть, и в самой СК

Для оценки эффективности функционального диагностирова-

ния используется специальная характеристика — достоверность

28

результата работы D. Это веро-

ятность, с которой оценивается

истинность результата, получае-

мого на выходе ОД. Достовер-

ность D отражает как надежност-

ные характеристики ОД и СК, так

и информационные возможности

используемого метода контроля. рис 23 Блок-схема функциональ-

В общем случае могут иметь ного диагностирования

место три возможных события:

ОД с контролем работает правильно; ОД с контролем показывает

наличие ошибки (ошибки могут обнаруживаться либо только в ОД,

либо как в ОД, так и в СК); о работе ОД с контролем нельзя ска-

зать ничего определенного (неопределенный результат). В самом

деле, если объект работает правильно или используемый метод

контроля позволяет обнаружить ошибку, то такой результат пра-

вильно отражает истинное состояние ОД. Если ошибка произош-

ла, а используемый метод контроля не смог ее обнаружить, или

если ошибки нет, а схема контроля показывает наличие ошибки,

то об истинном состоянии ОД с контролем ничего сказать невоз-

можно. В этом случае имеет место неопределенность.

Указанные три события образуют полную группу событий. Обо-

значим вероятности их появления соответственно Роо(/) и

Рнр(г). Тогда

^пр (0 + Роо (О + ^нр W “ 1*

(2.1)

Из данной формулы следует, что достоверность

^пр(0+^оо(0” 1 ^HpW

(2.2)

Для нахождения вероятности появления каждого из событий

необходимо учитывать обнаруживающую способность выбранно-

го метода контроля и вид его реализации. Под методом контроля

понимают математический метод, обеспечивающий проверку пра-

вильности функционирования ОД. Под видом контроля понима-

ют способ аппаратной или программной реализации выбранного

метода контроля.

29

Обозначим через /?обн вероятность, характеризующую способ-

ность применяемого метода контроля обнаруживать ошибки.

Она зависит от глубины охвата контролем заданного ОД и са-

мой схемы контроля, а также кратности обнаруживаемых дефек-

тов. Способ вычисления /?обн определяется используемым мето-

дом контроля.

Рассмотрим, например, случай контроля дискретного устрой-

ства (ДУ) с использованием корректирующих кодов. При этом ДУ

строится таким образом, что при всех возможных входных воздей-

ствиях на выходах ДУ формируются двоичные векторы, соответ-

ствующие разрешенным кодовым словам. Неисправность обнару-

живается тогда, когда она приводит к появлению на выходах ДУ

двоичного вектора, не принадлежащего заданному коду. Общее

число возможных искажений «-разрядного кодового вектора

а _ 2" - 1 - Поэтому значение робн вычисляется по формуле

! N

Ро6и ~ ~ уГГс (2-3)

где N — мощность множества разрешенных кодовых

слов; /V = ,к — число информационных разрядов кода.

Обозначим через рисх(0 вероятность безотказной работы ис-

ходного объекта диагноза, а через рк(/) — вероятность безотказ-

ной работы схемы контроля. В дальнейшем в обозначениях веро-

ятностей будем опускать обозначение времени /, так как безот-

казность и достоверность оцениваются за один и тот же период

времени /.

Для нахождения величин Рпр, Роо и Рнр будем использовать

таблицу истинности булевых функций (табл. 2.1), соответствующих

событиям, отвечающим указанным вероятностям. Булевы функции

определим следующим образом. Если ОД работает правильно, то

придадим этому событию значение р - 1; в противном случае зна-

чение р = 0. Событию, когда выбранный метод контроля позво-

ляет обнаруживать дефекты, привоим значение р = 1, а событию, ког-

да выбранным методом контроля дефекты не обнаруживаются—зна-

чение р ~ 0.

30

Таблица 2.1

№ п/п Риск А Роон Роо Р нр

1 0 0 0 0 0 1

2 0 0 1 0 1 0

3 0 1 0 0 0 1

4 * 0 1 1 0 1 0

5 1 0 0 0 0 1

6 1 0 1 0 1 0

7 1 1 0 1 0 0

8 1 1 1 1 0 0

В таблице отражены восемь возможных случаев сочетаний не-

зависимых событий, отражаемых вероятностями рисх, рк и робн.

Например, в шестой строке таблицы указаны значения рисх= 1,

рк= 0 и робн= 1 • Эта строка соответствует случаю, когда исход-

ный ОД работает правильно (Рисх= 1), схема контроля отказала

(рк= 0), а метод контроля обнаружил этот отказ (/>обн~ 1). Данное

событие имеет результатом появление на выходе СК сигнала

ошибки (см. рис. 2.3). Поэтому в графе pw, который соответству-

ет событию обнаружения ошибок, в шестой строке проставляет-

ся единичное значение функции. Такое же значение записывается

в строках 2 и 4, где робн= I и имеют место дефекты в ОД или СК.

В столбце Р единичное значение функции проставляется толь-

ко в строках 7 и 8, которые соответствуют случаю, когда и ОД, и

СК работают правильно. В столбце Рнр единичное значение фун-

кции заносится в строки, где робн= 0, кроме седьмой строки, в

которой рисх- 1 и рк~ 1.

Из таблицы следует, что

пр = ^исх^к^обн V ^исх^к^обн’

оо ^исх^к^обн V ^исх^к^7обн V ^исх^к^обн’

(2.4)

нр Рисх^к^обн V ^исх^к^обн V ^исх^к^обн’

От булевых функций осуществляется переход к вероятност-

ным выражениям. При этом сначала производится упрощение

31

выражений (2.4) по законам алгебры логики без использования

закона повторения. Соответствующие преобразования дают сле-

дующие выражения:

e Р Р \

пр 1 исх'к’

' р _ v р р р ;

оо 'исх' ООН 'исх^к'оон

(2.5)

= Р - (Р V р р

нр Г O()HV7HCX 1 исхЛ к

При переходе к вероятностным выражениям знак дизъюнкции

заменяется знаком сложения, а переменная р заменяется выраже-

нием 1 -р. В результате получаем;

= Р Р \

пр * исх^к*

Роо = обн^ Aicx + ЛгсхЛэбн^

(2.6)

Лф “ обн ^исх^к ) •

Из (2.6) следует, что достоверность ОД с аппаратным контролем

“ I ^нр ~ ^обн + ^ИСХ^К ^ИСХ^К^обн •

(2-7)

Если контроль отсутствует (в этом случае рк - 1 и робн = 0), то

достоверность ОД без контроля

D = р . (2.8)

1 исх

Выигрыш в достоверности при использовании контроля

дг>_ок -О = робн -р,кх(1-/’к)-А,сх/’к/’об1,- <2-9)

Однако выигрыш в достоверности сопровождается проигры-

шем в надежности и увеличением сложности устройства. Введе-

ние контроля снижает вероятность безотказной работы ОД с кон-

тролем. Действительно, вероятность правильной работы ОД со

схемой контроля Рпр равна вероятности безотказной работы ОД

со схемой контроля, ^ОДЮ т е-

32

родк = Рпр - РтхРк- (2.10)

Л

Тогда проигрыш в безотказности

г

ДР = р - р р . О 11)

ГИСХ 2 ИСХЛ К

Усложнение объекта характеризуется коэффициентом

п

ИСХ

о -------

п '

к

(2.12)

где лисх и лк — число элементов соответственно в исходном ус-

тройстве и схеме контроля.

При решении конкретных задач возникает вопрос о допус-

тимом коэффициенте избыточности. Существует стандартный

способ построения СК — метод дублирования (рис. 2.4). В этом

случае СК включает в себя второй комплект ОД и схему срав-

нения выходных сигналов обоих комплектов СС. Для схемы

дублирования

дуб

п

ИСХ < |

п + пгг,

исх СС

где iiqq — число элементов в схеме сравнения.

На практике стремятся получить системы диагностирования со

сложностью о > о дуб. Наилучшими считаются варианты систем с

о > 10 (контрольное

шает 10 %), достаточно

хорошими — с о&4

(не более 25 %). Увели-

чение выигрыша в до-

стоверности, как пра-

вило. требует услож-

нения контрольного

оборудования.

Входы

Рис. 2.4. Схема дублирования ОД

33

Из формул (2.9) и (2.11) следует, что чем выше /?обн, тем больше

выигрыш в достоверности, при этом проигрыш в безотказности

остается на прежнем уровне. Поэтому следует применять более со-

вершенные методы контроля. Однако существует определенная вза-

имосвязь между робн и так как более совершенные методы кон-

троля требуют более сложного контрольного оборудования.

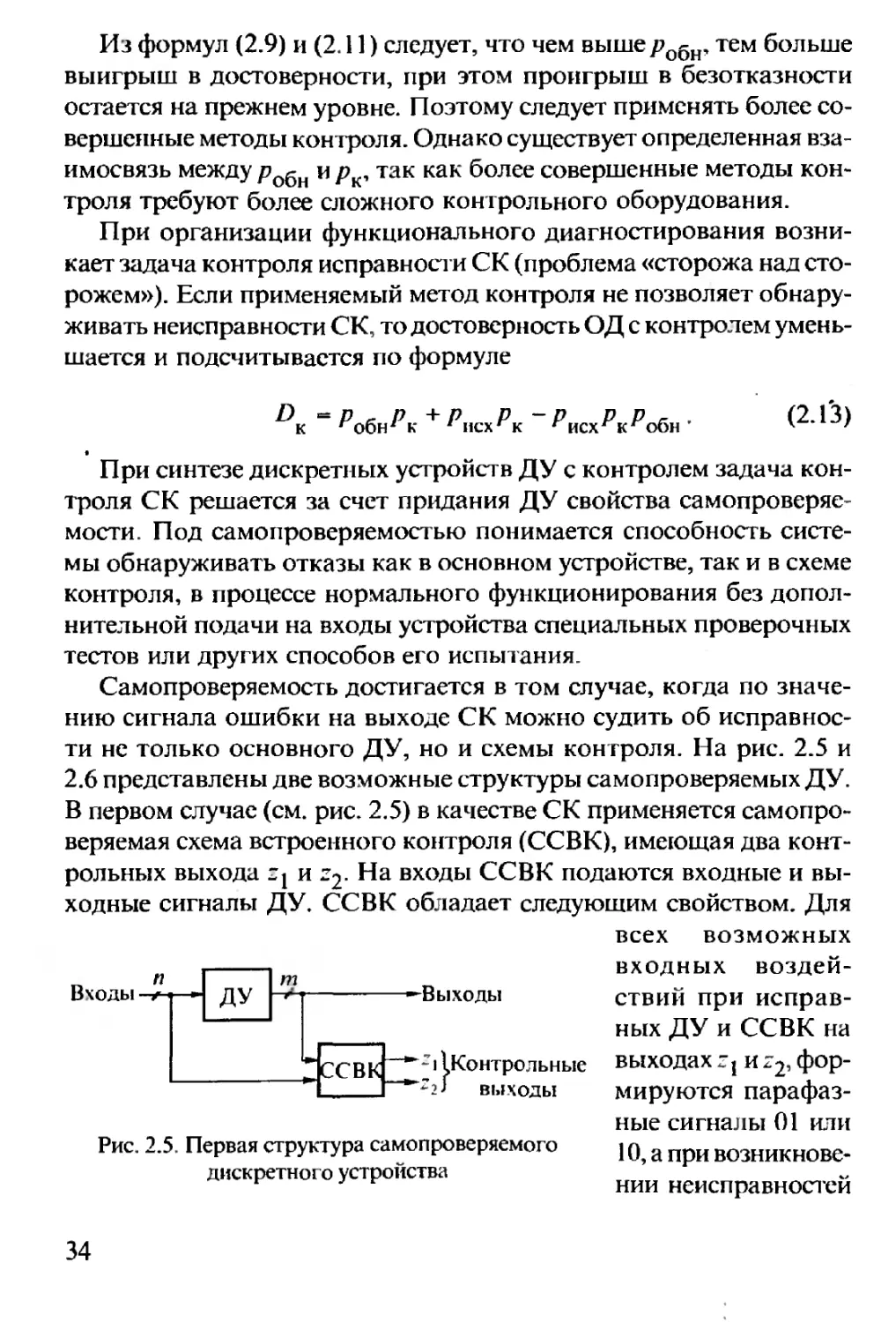

При организации функционального диагностирования возни-

кает задача контроля исправности СК (проблема «сторожа над сто-

рожем»). Если применяемый метод контроля не позволяет обнару-

живать неисправности СК, то достоверность ОД с контролем умень-

шается и подсчитывается по формуле

в ^обн^к + ^исх^к^обн '

(2.13)

При синтезе дискретных устройств ДУ с контролем задача кон-

троля СК решается за счет придания ДУ свойства самопроверяе-

мости. Под самопроверяемостью понимается способность систе-

мы обнаруживать отказы как в основном устройстве, так и в схеме

контроля, в процессе нормального функционирования без допол-

нительной подачи на входы устройства специальных проверочных

тестов или других способов его испытания.

Самопроверяемость достигается в том случае, когда по значе-

нию сигнала ошибки на выходе СК можно судить об исправнос-

ти не только основного ДУ, но и схемы контроля. На рис. 2.5 и

2.6 представлены две возможные структуры самопроверяемых ДУ.

В первом случае (см. рис. 2.5) в качестве СК применяется самопро-

веряемая схема встроенного контроля (ССВК), имеющая два конт-

рольных выхода Zj и z2- На входы ССВК подаются входные и вы-

ходные сигналы ДУ. ССВК обладает следующим свойством. Для

Входы -г

т

ДУ

Выходы

-1 (Контрольные

z2i ВЫХОДЫ

Рис. 2.5. Первая структура самопроверяемого

дискретного устройства

всех возможных

входных воздей-

ствий при исправ-

ных ДУ и ССВК на

выходах и z2, фор-

мируются парафаз-

ные сигналы 01 или

10, а при возникнове-

нии неисправностей

34

в ДУ или ССВК—не-

парафазные сигналы

00 или 11. Появление

непарафазного сиг-

нала на выходе

ССВК является при-

знаком наличия не-

исправности. В дан-

п

Входы -t-

- Выходы

ССВК- Z|

Рис. 2.6. Вторая структура самопроверяемого

дискретного устройства

ной структуре исходное ДУ не подвергается изменениям, а вся из-

быточность, которая является ценой за свойство обнаружения от-

казов, полностью вносится во внутреннюю структуру ССВК.

Характерной особенностью второй структуры самопроверяемо-

го ДУ (см. рис. 2.6) является то, что избыточность вносится во внут-

реннюю структуру самого ДУ. Для этого либо модифицируется

структура исходного устройства, либо по заданным условиям ра-

боты непосредственно синтезируется избыточное ДУ. При этом

улучшается контролепригодность ДУ, и оно приобретает такие

свойства, которые позволяют легко фиксировать неисправности

только по значениям основных или специальных контрольных вы-

ходов. Как правило. на этих выходах формируются двоичные векто-

ра, принадлежащие какому-либо коду с обнаружением ошибок. Тог-

да ССВК реализуется в виде тестера, задача которого состоит в опре-

делении факта принадлежности кодового вектора заданному коду.

На практике используются обе указанные структуры самопро-

веряемых ДУ.

2.3. Тестовое диагностирование

При организации тестового диагностирования основной являет-

ся задача построения тестов. Для дискретных объектов можно вы-

делить три этапа в развитии теории построения тестов. Для первого

этапа характерным было стремление получать минимальные или

оптимизированные тесты на основе представления комбинационных

объектов таблицами истинности, а последовательных объектов —

таблицами переходов и выходов. Основной моделью дефектов был

класс константных неисправностей, включающий в себя для релей-

но-контактных схем обрывы и короткие замыкания контактов, а для

схем на функциональных элементах — фиксацию в константы сиг-

35

налов на входах и выходах элементов. Основные методы построе-

ния тестов были основаны на переборе вариантов, в большинстве

случаев использовались таблицы функций неисправностей.

Второй этап развития теории построения тестов характерен пе-

реходом к структурным и структурно-аналитическим моделям дис-

кретных объектов, разработкой новых методов обработки этих

моделей и отказом от задач получения минимальных тестов. Рас-

ширяется класс рассматриваемых неисправностей, в том числе ис-

следуются вопросы обнаружения коротких замыканий в схемах на

функциональных элементах, а также проблемы обнаружения неис-

правностей в программируемых логических матрицах. Развитие

новых методов в теории построения тестов вызывалось главным

образом увеличением размерности практических задач.

Третий этап развития теории построения тестов связан с появле-

нием больших и сверхбольших интегральных схем, микропроцессор-

ных наборов и других элементов высокого уровня интеграции. Высо-

кая размерность задач привела к необходимости функционального

представления дискретных объектов на макроуровне и рассмотрения

функциональных неисправностей взамен константных. Начинает раз-

виваться также вероятностный подход к построению тестов.

В настоящее время широко применяют тесты, представляющие

собой псевдослучайные последовательности входных воздействий.

Такие псевдослучайные тесты генерируются регистром (Р) сдвига с

обратными связями (рис. 2.7, а), что существенно сокращает затраты

на аппаратуру для реализации генера юра тестов, так как не требует-

ся память для хранения последних. Однако анализатор (А) ответов

Рис. 2.7. Схема систем вероятностного диагностирования

36

ОД в системе вероятностного диагностирования имеет такую же

сложность, что и в системе детерминированного диагностирова-

ния (см. рис. 2.2, а). С целью его упрощения осуществляется сжа-

тие длинных выходных последовательностей, формируемых на вы-

ходах ОД, при помощи специальных сигнатурных анализаторов

СА (рис. 2.7, б), которые представляют собой также регистры сдвига

с обратными связями или счетчики. Применение СА позволяет эф-

фективно тестировать сложные вычислительные системы.

Для непрерывных объектов существует гораздо более широкое мно-

гообразие физических принципов f

лизации по сравнению с дискрет-

ными объектами. Это затрудняет разработку общих теоретических и

методических подходов к построению тестов для непрерывных сис-

тем. Для каждого типа последних по этой причине используются соб-

ственные математические модели и методы построения тестов.

Системы тестового диагностирования, представленные на

рис. 2.2, а и 2.7, используются в те промежутки времени, когда ОД

не выполняет своих основных функций. 11ри этом решаются задачи

контроля исправности и поиска дефектов. Однако тестовое диагно-

стирование может также применяться для контроля ОД в процессе

функционирования, если в этом процессе можно выделить такие

моменты, когда на входы ОД не поступают рабочие входные воз-

действия и выходы могут быть отключены от объектов управления.

Структурная схема тестового диагностирования приведена на

рис. 2.8. Запоминающее устройство (ЗУ) хранит тесты и эталонные

реакции, которые поступают на входы ОД и анализатора по ко-

Рис. 2.8. Структурная схема тестового диагностирования

37

uapnani гл

Рис. 2.9. Временные диаграммы включения

тестового диагностирования

Вариант Б

мандам со стороны

схемы управления.

Результаты тестиро-

вания используются

для организации

взаимосвязи между

ОД и объектом уп-

равления ОУ.

Возможны два варианта организации тестового диагностиро-

вания, которые проиллюстрированы временными диаграммами на

рис. 2.9. Вариант А предусматривает первоначальное включение

основного рабочего режима (время /р), после чего подается прове-

ряющий тест (время /д). Полученный при выполнении рабочего ре-

жима результат запоминается до окончания процесса прохождения

теста. Если тест не фиксирует наличие неисправности, то дается

разрешение на дальнейшее использование указанного результата.

При применении варианта Б сначала осуществляется подача тес-

та (время /д), а затем реализуется рабочий режим (время Zp). Выход-

ной результат работы ОД оценивается по результату тестирования.

Для анализа режимов тестирования используется коэффициент

избыточного времени

При кв -1 достоверность функционирования ОД с тестовым

контролем для вариантов А и Б одинакова; при кв > 1 выше досто-

верность варианта А, а при кв < 1 — достоверность варианта Б.

Как правило, Ав > 1, но вариант А часто не может быть использо-

ван, так как не всегда есть возможность задерживать выходную ин-

формацию после прохождения рабочего режима.

Наиболее часто используется вариант Б, когда ОД тестируется

перед его использованием. Если *р » /д, то наряду с тестировани-

ем применяют и аппаратный контроль, который за время / в ре-

альном масштабе времени определяет работоспособность ОД. Та-

кой комбинированный контроль позволяет эффективно эксплуа-

38

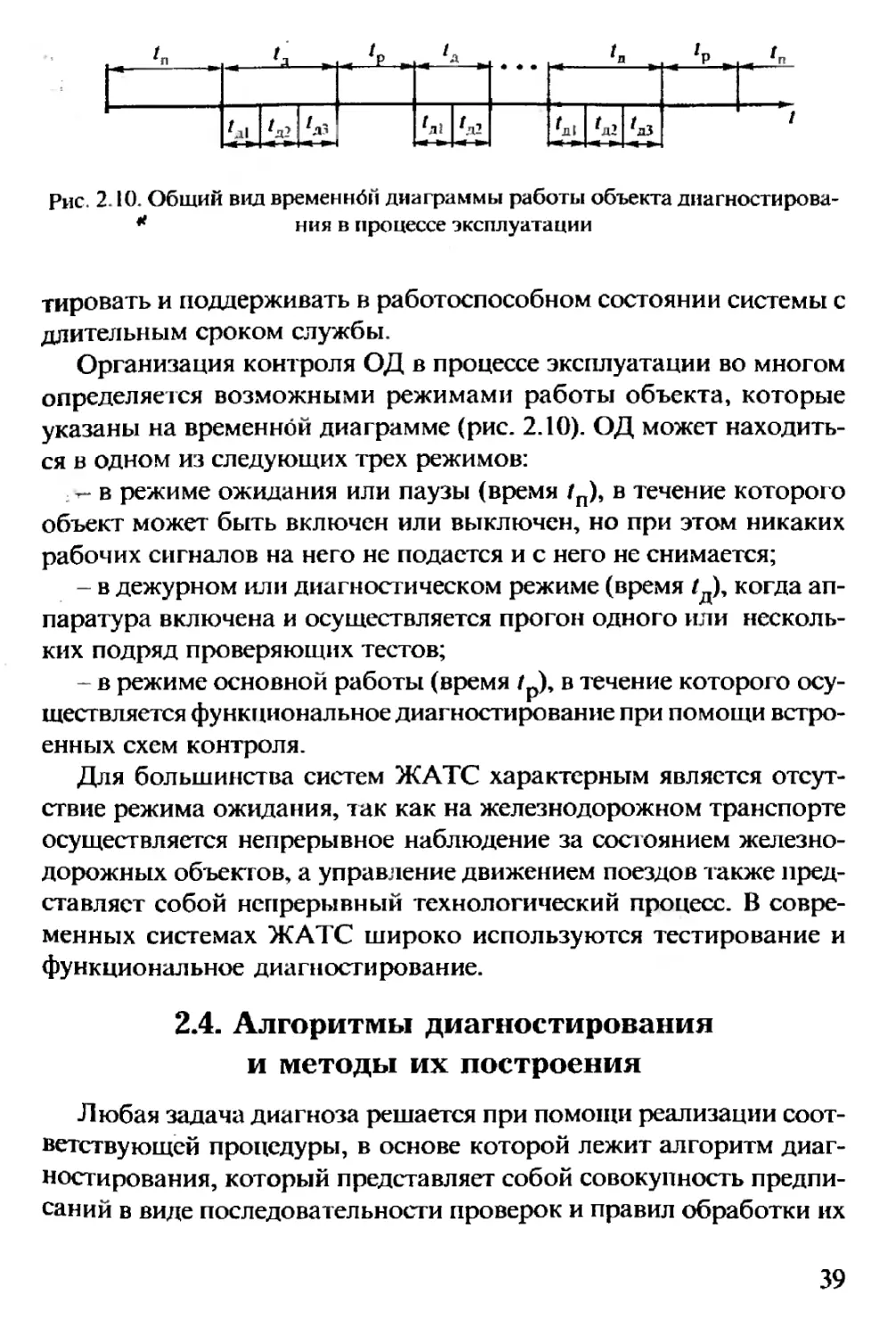

Рис. 2.10. Общий вид временной диаграммы работы объекта диагностирова-

* ния в процессе эксплуатации

тировать и поддерживать в работоспособном состоянии системы с

длительным сроком службы.

Организация контроля ОД в процессе эксплуатации во многом

определяемся возможными режимами работы объекта, которые

указаны на временной диаграмме (рис. 2.10). ОД может находить-

ся в одном из следующих трех режимов:

:'т- в режиме ожидания или паузы (время /п), в течение которого

объект может быть включен или выключен, но при этом никаких

рабочих сигналов на него не подастся и с него не снимается;

- в дежурном или диагностическом режиме (время /д), когда ап-

паратура включена и осуществляется прогон одного или несколь-

ких подряд проверяющих тестов;

- в режиме основной работы (время /р), в течение которого осу-

ществляется функциональное диагностирование при помощи встро-

енных схем контроля.

Для большинства систем ЖАТС характерным является отсут-

ствие режима ожидания, так как на железнодорожном транспорте

осуществляется непрерывное наблюдение за состоянием железно-

дорожных объектов, а управление движением поездов также пред-

ставляет собой непрерывный технологический процесс. В совре-

менных системах ЖАТС широко используются тестирование и

функциональное диагностирование.

2.4. Алгоритмы диагностирования

и методы их построения

Любая задача диагноза решается при помощи реализации соот-

ветствующей процедуры, в основе которой лежит алгоритм диаг-

ностирования, который представляет собой совокупность предпи-

саний в виде последовательности проверок и правил обработки их

39

Рис. 2.11. Классификация алгоритмов

диагностирования

результатов для получе-

ния общего результата

диагностирования. Раз-

личают алгоритмы про-

верки исправности, ра-

ботоспособности и по-

иска неисправности. Их

строят на основе соответ-

ствующих тестов и слова-

рей неисправностей. На

рис. 2.11 приведена клас-

сификация алгоритмов

диагностирования, в со-

ответствии с которой

можно выделить три

вида алгоритмов: безусловный с безусловной остановкой, безусловный

с условной остановкой и условный с условной остановкой.

Безусловный алгоритм задает одну фиксированную последо-

вательность проведения проверок, при этом информация о тех-

ническом состоянии объекта фиксируется и обрабатывается пос-

ледовательно независимо от результатов предыдущих проверок.

В условном алгоритме предусматривается назначение каждой после-

дующей проверки в зависимости от результата анализа предыду-

щих проверок.

Если заключение о техническом состоянии объекта может быть

сделано только после проведения всех проверок, предусмотренных

алгоритмом, то такой алгоритм называют алгоритмом с безуслов-

ной остановкой. Если выдача результата диагностирования возмож-

на после выполнения каждого или некоторых промежуточных ша-

гов алгоритма, то последний называют алгоритмом с условной ос-

тановкой. Условный алгоритм всегда является алгоритмом с ус-

ловной остановкой.

Наиболее распространенными формами представления алго-

ритмов диагностирования являются таблицы и древовидные гра-

фы. Безусловные алгоритмы с безусловной остановкой представ-

ляются в виде таблиц, в качестве которых, например, выступают

словари неисправностей (см. табл. L8 и 1.10). В этом случае по-

40

иск неисправного элемента требует выполнения всего множества

проверок, включенных в тест, с фиксацией их результатов. На

основе анализа полной совокупности этих результатов делается

вывод о месте неисправности.

Безусловный алгоритм с условной остановкой представляется в

виде графа. Рассмотрим, например, граф (рис. 2.12, а), который

моделирует алгоритм поиска неисправности по табл. 2.2. Корне-

вая вершина графа представляет множество S = всех

рассматриваемых технических состояний объекта, а остальные вер-

шины — подмножества состояний, выделяемые в результате деле-

ния множества S и его подмножеств по результатам элементарных

проверок. Висячие вершины соответствуют подмножествам экви-

валентных состояний. Исходящими из вершин дугами изобража-

ются элементарные проверки, а заходящими дугами — результаты

этих проверок. Заданный алгоритм предусматривает подачу про-

верок в фиксированной последовательности — (так,

как они расположены в табл. 2.2). Однако выполнение алгоритма

может быть остановлено на любом этапе, если выделилось под-

Рис. 2.12. Схемы безусловного (а) и условного (б) алгоритмов диагностирования

& &&&

41

множество состояний, соответствующее висячей вершине. Так, на

первом этапе алгоритма при выполнении проверки получение

результата 0 останавливает алгоритм, так как выделено подмно-

жество эквивалентных состояний {5р . В противном случае при-

меняют проверку л2 и алгоритм продолжается.

Таблица 2.2

Проверка Результат R проверки для системы, находящейся в состоянии

Xj S2 S3 $5 s6 $7

Л] 0 1 1 1 1 1

ль 1 0 1 1 1 1

0 1 0 1 0 1

Л7 0 1 0 1 i 0

Условные алгоритмы также представляются в виде графов. По-

строение условного алгоритма начинается с выбора первой про-

верки. В зависимости от исхода первой проверки Jij множество воз-

можных состояний 51 делится на два подмножества, после чего вы-

бираются проверки (они могут быть разными), разделяющие эти

подмножества. Выбор проверок продолжается до тех пор, пока

множество 5 не будет разделено на отдельные подмножества экви-

валентных состояний. На рис. 2.12, б приведен условный алгоритм,

построенный по табл. 2.2.

Для одного и того же словаря неисправностей может быть

построено значительное количество безусловных и условных ал-

горитмов диагностирования. Каждый из них будет обладать оп-

ределенными особенностями. Например, условный алгоритм

(рис. 2.12, б) имеет преимущество по сравнению с безусловным

алгоритмом (рис. 2.12, а), которое состоит в том, что в первом

любая неисправность может быть обнаружена не более чем за три

шага алгоритма, в то время как во втором может потребоваться

выполнение и четырех шагов алгоритма. Но, с другой стороны,

безусловный алгоритм дает возможность обнаружить неисправ-

ность уже при выполнении первого шага, а в условном алгоритме

такой возможности нет.

При решении практических задач возникает проблема выбо-

ра оптимального алгоритма диагностирования. При этом фор-

42

аудируются либо ограничения на алгоритм, либо критерий оп-

тимальности, в которых отражаются конкретные практические

условия применения алгоритма. В качестве ограничения на ал-

горитм могут выступать: заданное время, в течение которого дол-

жна быть обнаружена любая неисправность; максимально до-

пустимуе число шагов алгоритма; ограничения, определяющие

необходимость обнаружения на первых шагах алгоритма неко-

торых указанных неисправностей и т.п. В качестве критерия оп-

тимальности может рассматриваться средняя стоимость обна-

ружения отказавшего элемента, вероятность обнаружения при

ограниченной стоимости или стоимость с заданной вероятнос-

тью и т.д. В этом случае каждый алгоритм, заданный соответ-

ствующим графом, характеризуется определенным значением

критерия оптимальности.

При оптимизации алгоритма, как правило, учитывают три фак-

тора: вероятности отказов элементов модели объекта (или вероят-

ности попадания системы в рассматриваемые состояния); стоимость

каждой проверки, под которой понимается некоторое относитель-

ное число, отражающее в условных единицах затраты труда, време-

ни, сложность действий, необходимую аппаратуру и т.п., требую-

щиеся для проведения проверки; объем информации, который дает

каждая проверка. Вероятности о гказов элементов задаются при про-

ектировании ОД на этапе выбора элементной базы. Стоимости про-

верок определяются на основе специального анализа объекта диаг-

ноза. При этом выбирается самая сложная проверка и ее стоимость

оценивается в 100 условных единиц. Все остальные проверки ран-

жируются относительно самой сложной проверки и им сопоставля-

ются соответствующие оценочные стоимости. Информация о состо-

янии объекта, которую можно получить при выполнении той или

другой проверки, содержится в таблицах, соответствующих слова-

рям неисправностей.

Наиболее общим критерием оптимальности является средняя сто-

имость выполнения алгоритма. Рассмотрим алгоритмы, заданные

графами на рис. 2.12. Зададим вероятности состояний:

Р(51)я=р(52) = р(56)=о,2 и M^3) = P(54) = /X55) = p(S7)=0,l,a

также стоимости проверок: ф^) = 50, с(л2)= 40, с(я6)= 30, с(л7)= 20.

43

Средняя стоимость выполнения алгоритма

C(S)= Е c(S)p(S)f Е р(5.) = 1, (2.14)

S.eS 1 1 S.eS 1

где S — множество всех состояний системы; c(Sp — суммарная

стоимость всех проверок, выполнение которых необходимо для

выделения состояния S- в соответствии с данным алгоритмом; сум-

ма вероятностей состояний равна единице, так как алгоритм приме-

няется тогда, когда система находится в одном из состояний Si е S.

В условном алгоритме (см. рис. 2.12, б) для выделения, напри-

мер, состояния необходимо последовательно применить провер-

ки 7Г6, Л7 и щ. Поэтому

<4^3 ) = с(.п6) + с( Л7) + <( Л]).

В целом для данного алгоритма имеем

с, (S) = [с(л,) + с( л6 ) + С(л7 ) + p(S3 ) + p(S\)] +

+ ) + с( л6 )]p(S2 ) + [с(л2 ) + с( л6 ) + с( Л7 )][^(S5 ) + p(s7)] +

+ [с(л6) + с(л7)М56) = 82.

Различные алгоритмы сравнивают по численному значению C(S).

Например, для безусловного алгоритма (см. рис. 2.12, a) C2(S) = 103,

и поэтому он хуже условного алгоритма (см. рис. 2.12, б), так как

С2(5) > С[(5). Очевидно, что при других соотношениях между ве-

роятностями p(St) и стоимостями с(лД безусловный алгоритм мо-

жет оказаться предпочтительнее условного. Для нахождения алго-

ритма с минимальной стоимостью C(S) используют перебор вари-

антов или принципы динамического программирования, что свя-

зано со сложными вычислительными процедурами. Поэтому на

практике часто применяют некоторые решающие правила (упрощен-

ные подходы), которые позволяют находить близкие к оптималь-

ным алгоритмы. Часто возникает такая задача. Имеется система,

состоящая из п элементов, один из которых неисправен. Для каждо-

го элемента известны вероятность р{ возникновения неисправности

и стоимость его проверки л, (в большинстве случаев в качестве с{

44

выступает время проверки элемента). В этом случае последователь-

ность проверок в алгоритме устанавливается в соответствии с по-

рядком соотношений р{ > Pz!c2> -• > рп !сп • При этом, если

после проведения п - 1 проверки неисправный элемент не обнару-

а п

жен, тго/вследствиетого что S pr- = 1, за неисправный принимается

1=1

последний элемент и его не проверяют.

При построении алгоритмов диагностирования существенное

значение имеет количество информации, содержащееся в провер-

ках. Частично это учитывается и при оптимизации алгоритмов с

помощью выражения (2.14). Более полный учет позволяет получить

метод, основанный на теории информации.

Диагностирование — это, по сути, процесс получения информа-

ции о состоянии объекта. Перед началом процесса диагностирова-

ния объект, с точки зрения наблюдателя, характеризуется большой

степенью неопределенности состояния. Она будет тем больше, чем

больше число возможных состояний и чем меньше разброс их ве-

роятностей. Неопределенность состояния системы S = } харак-

теризуется ее энтропией H(S). Если система из п элементов может

быть неисправной в результате отказа только одного какого-либо

z-го элемента с условной вероятностью отказа pj2 то

п

H(S) = -Ypilog2pj,

<=1

п

(2.15)

Значения pi определяются на основе статистических данных о

надежности элементов системы.

Для энтропии характерны следующие свойства:

1) H(S) > 0;

2) энтропия системы, имеющей п равновероятных состояний,

H(S) = - S р. log- р = п-— log- п = log2 п;

{=1 1 Л 1 п z

3) эшропия системы максимальна, если ее состояния равновероятны;

4) если pt = 1, то H(S) = 0.

45

Каждая проверка л,- содержит некоторое количество информа-