Text

Б. ГОЛДСУОРТ

ПРОЕКТИРОВАНИЕ

цифровых

логических

устройств

Digital Logic Design

B. Holdsworth, BSc(Eng), MSc, FIEE

Senior Lecturer in Electronics,

Chelsea College, University of London

Butterworths

London Boston Durban Singapore Sydney Toronto Wellington

Б.ГОЛДСУОРТ

ПРОЕКТИРОВАНИЕ

цифровых

логических

устройств

Перевод с английского

канд. техн, наук М. В. Сергиевского

Под редакцией

д-ра техн, наук проф. Ю. И. Толчеева

МОСКВА

• МАШИНОСТРОЕНИЕ»

1965

ББК 32.973.2

Г60

УДК 681.325.5.001.2 = 03.20= 82

Голдсуорт Б.

Г60 Проектирование цифровых логических устройств/Пер.

с англ. М. В. Сергиевского; Под ред. Ю. И. Топчеева. — М.:

Машиностроение, 1985. — 288 с., ил.

В пер,: 1 р. 60 к.

Книга английского специалиста представляет собой введение в теорию и прак-

тику проектирования комбинационных логических схем, дискретных устройств с па-

мятью и микропроцессоров на базе микросхем со средним уровнем интеграции.

Для инженеров, проектирующих устройства дискретной автоматики и цифровых

вычислительных машин.

2404000000-017 8 ББК 32.973.2

038 (01)-85 0 6Ф7.3

© Butterworth & Со (Publishers),

Ltd, 1982

© Перевод на русский язык,

«Машиностроение», 1985 г,

ОГЛАВЛЕНИЕ

Предисловие ......................................................

1. Булева алгебра ................................................

1.1. Введение ..............................................

1.2. Логика переключателя...................................

1.3. Функция И..............................................

1.4. Функция ИЛИ............................................

1.5. Функция НЕ.............................................

1.6. Реализация булевых функций с помощью переключательных

и электронных схем..........................................

1.7. Теорема идемпотентности................................

1.8. Теоремы объединения и пересечения .....................

1.9. Теорема избыточности или поглощения....................

1.10. Определение дополнения функции........................

1.11. Теоремы перестановки, сочетания и распределения.......

1.12. Теорема согласования .................................

Упражнения .................................................

2. Карты Карно и упрощение функций...............................

2.1. Введение ..............................................

2.2. Конъюнкции и дизъюнкции................................

2.3. Канонические формы.....................................

2.4. Булевы функции двух переменных ........................

2.5. Карты Карно ...........................................

2.6. Представление булевых функций с помощью карт Карно. . ,

2.7. Упрощение булевых функций..............................

2.8. Отрицание функции......................................

2.9. Термы, «не доставляющие беспокойства»..................

2.10. Представление и упрощение конъюнктивных нормальных форм

Упражнения .................................................

3. Элементы И—НЕ и ИЛИ—НЕ ........................................

3.1. Введение ..............................................

3.2. Функция И—НЕ...........................................

3.3. Реализация функций И или ИЛИ с помощью элементов И—НЕ

3.4. Реализация дизъюнктивных нормальных форм с помощью эле-

ментов И—НЕ.................................................

3.5. Функция ИЛИ—НЕ.........................................

3.6. Реализация функций ИЛИ и И на основе элементов ИЛИ—НЕ

3.7. Реализация конъюнктивных нормальных форм с помощью эле-

ментов ИЛИ—НЕ...............................................

3.8. Реализация дизъюнктивных нормальных форм с помощью эле-

ментов ИЛИ—НЕ...............................................

3.9. Расширение элементов.................................. •

3.10. Смешанные схемы ......................................

3.11. Элементы с тремя состояниями..........................

3.12. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ ............................;

Упражнения .......................

4. Проектирование комбинационных логических схем..................

4.1. Введение ...............................................

4.2. Полусумматор............................................

4.3. Полный сумматор.........................................

4.4. Четырехразрядный сумматор параллельного действия....

4.5. Сумматор с ускоренным переносом ........................

4.6. Полное вычитающее устройство............................

4.7. Дополнительный код......................................

4.8. Обратный код............................................

4.9. Двоичное представление чисел............................

4.10. Использования дополнительного кода для сложения и вычита-

ния чисел ...................................................

4.11. Двоичное умножение.....................................

4.12. Преобразования кодов ..................................

4.13. Преобразователь из двоичного кода в код Грея...........

4.14. Классификаторы прерываний..............................

4.15. Метод формирования цепочки.............................

Упражнения ..................................................

5. Однобитовые элементы памяти ...................................

5.1. Введение................................................

5.2. Т-триггер...............................................

5.3. 57?-триггер.............................................

5.4. УК-триггер..............................................

5.5. D-триггер ..............................................

5.6. Запирание триггера......................................

Упражнения ..................................................

6. Счетчики ......................................................

6.1. Введение ...............................................

6.2. Двоичный счетчик........................................

6.3. Счетчик по модулю 4 ..................................

6.4. Счетчик по модулю 8 ..................................

6.5. СчеТчнк по модулю 2N................................

6.6. Одновременная и последовательная подача сигналов на входы

элементов счетчика ..........................................

6.7. Синхронные счетчики обратного счета.....................

6.8. Счетчик по модулю 5 ....................................

6.9. Двоично-десятичный счетчик..............................

6.10. Двоично-десятичный счетчик обратного счета ............

6.11. Десятичный счетчнк, использующий код Грея..............

6.12. Реверсивные счетчики по модулю 16 .....................

6.13. Асинхронные двоичные счетчики..........................

6.14. Асинхронный десятичный счетчик.........................

6.15. Асинхронные счетчики с автоматическим сбросом..........

6.16. Счетчики на интегральных схемах .......................

6.17. Каскадирование счетчиков на интегральных схемах........

Упражнения ..................................................

7. Сдвиговые регистры и генераторы................................

7.1. Введение ...............................................

7.2. Четырехразрядный сдвиговый регистр с параллельной загрузкой

7.3. Четырехразрядный регистр для сдвига влево и вправо....

7.4. Использование сдвиговых регистров в качестве счетчиков . . .

7-5. Универсальная диаграмма состояний сдвиговых регистров . .

7.6. Проектирование десятичного счетчика.................

7.7. Генераторы последовательностей на сдвиговом регистре....

7.8. Кольцевой счетчик.......................................

7.9. Счетчик Дж.онсрна . , ; ............. . < ,

7.10. Сдвиговые регистры с обратной связью типа ИСКЛЮЧАЮЩЕЕ

ИЛИ...................................................... 134

Упражнения .................................................. 139

8. Синхронные последовательные схемы............................. 140

8.1. Введение................................................. 140

8.2. Анализ синхронной последовательной схемы................. 140

8.3. Процедура проектирования синхронных последовательных схем 144

8.4. Проектирование устройства обнаружения последовательности цифр 151

8.5. Автоматы Мура и Мили..................................... 153

8.6. Импульсные синхронные схемы ................................. 156

8.7. Сокращение состояний ........................................ 157

8.8. Кодирование состояний.................................... 163

Упражнения .................................................. 168

9. Асинхронные схемы............................................. 171

9.1. Введение.................................................... 171

9.2. Задача определения числа посетителей музея ................. 171

9.3. Гонки и циклы............................................... 175

9.4. Противогоночное кодирование для автомата с тремя состояниями 177

9.5. Задача о подаче воды в водонапорную башню................... 178

9.6. Противогоночное кодирование для автомата с четырьмя состоя-

ниями ........................................................ 180

9.7. Устройство обнаружения последовательности................... 183

Упражнения ...................•................................... 188

10. Логическое проектирование на основе ИМС со средним уровнем интег-

рации .............................................................. 191

10.1. Введение............................................... 191

10.2. Устройство выбора линии передачи информации или мульти-

плексор ....................................................... 191

10.3. Мультиплексор как генератор логических функций........... 194

10.4. Дешифраторы и демультиплексоры........................... 200

10.5. Применение дешифраторов.................................. 201

10.6. Постоянные запоминающие устройства (ПЗУ)................. 205

10.7. Методы адресации для ПЗУ................................. 206

10.8. Проектирование последовательных схем с помощью ПЗУ . . . 209

10.9. Программируемые логические матрицы (ПЛМ)............. 211

10.10. Проектирование последовательных схем на ПЛМ............. 216

10.11. Арифметические устройства на ИМС со средним уровнем инте-

грации ........................................................ 217

10.12. Десятичное сложение с помощью сумматоров иа ИМС со сред-

ним уровнем интеграции ........................................ 221

Упражнения .................................................... 223

11. Ситуации риска в логических схемах................................ 226

11.1. Введение ................................................ 226

11.2. Явления временной задержки в логических элементах........ 226

11.3. Условия возникновения выбросов........................... 226

11.4. Возникновение ситуаций статического риска в комбинационных

схемах ........................................................ 228

11.5. Устранение статического риска............................ 230

11.6. Построение гарантированных от риска комбинационных схем 233

11.7. Анализ схем для обнаружения ситуаций риска............... 235

11.8. Ситуации динамического риска............................. 237

11.9. Ситуации существенного риска............................. 239

Упражнения .................................................... 240

12. Введение в микропроцессоры........................................ 242

12.1. Введение............................................. 242

12.2. Двоичное умножение................................... 243

12.3. Аппаратура, необходимая для реализации устройства двоичного

умножения ..................................................... 243

12.4. Двоичное устройство умножения........................ 245

12.5. Схемы алгоритмов ......................................... 246

12.6. Устройство двоичного умножения, управляемое программой 248

12.7. Длина слова.......................................... 249

12.8. Счетчик программы.................................... 250

12.9. Команды н счетчик команд............................. 251

12.10. Шестнадцатеричная система представления чисел..... 253

12.11. Сравнение упрощенного микропроцессора с реальным. . . . 254

12.12. Обобщенная структурная схема микропроцессорной системы 255

12.13. Программирование для микропроцессоров ............. 258

Ответы к упражнениям.................................................. 259

Список литературы.................................................... 283

Предметный указатель.................................................. 285

ПРЕДИСЛОВИЕ

Книга создана на основе курса лекций, читаемых студентам факультета элек-

троники в колледже Челси, и материалов недельных курсов по цифровому проекти-

рованию, регулярно проводимых в том же институте для инженеров и научных ра-

ботников. По существу книга является учебным пособием, но она также будет по-

лезна всем инженерам, которые, не имея специального образования в области про-

ектирования цифровых устройств, в своей деятельности постоянно сталкиваются

с ним. Содержание книги найдут полезным будущие абитуриенты, которые зани-

маются электроникой перед поступлением в университет, и студенты, добивающиеся

степени магистра по методам проектирования цифровых устройств, ранее не изучав-

шие этот предмет.

В течение последних десяти лет методам проектирования цифровых устройств

уделялось возрастающее внимание, и в настоящее время они входят в учебные про-

граммы большинства университетов и политехнических институтов. Сначала при

проектировании использовались дискретные компоненты, но в последние десять лет

стали широко применяться схемы с малым и средним уровнями интеграции. Это

позволило упростить процесс проектирования и свести его к задаче сборки устройств

из интегральных схем. Совсем недавно появились большие интегральные схемы,

что дало возможность разрабатывать микропроцессоры. В связи с этим уже сейчас

можно выделить два альтернативных метода проектирования цифровых устройств,

основанных на использовании схем с «жесткой» логикой и на применении микро-

процессоров. Первый подход требует знания методов проектирования, которые из-

ложены в данной книге, в то время как второй подход является программным способом

решения той же проблемы. На завершающей стадии анализа проектного задания

необходимо выбрать один из этих двух подходов, используя экономический крите-

рий.

Однако на практике при решении многих задач обычно сочетают оба подхода.

Поэтому следует добиваться, чтобы проектировщики обладали хорошими знаниями

по булевой алгебре и умели применять ее методы для решения задач проектирования

Цифровых устройств. Кроме того, проектировщик должен обладать глубокими зна-

ниями методов программирования. По мнению автора, студент, владеющий фунда-

ментальными знаниями по проектированию устройств с «жесткой» логикой как ком-

бинационного, так и последовательного типов, легче перейдет к проектированию

на базе микропроцессоров.

Книга состоит из 12 глав. Первые три главы составляют вводную часть,

в которой изложены основы, знание которых необходимо для решения задач, харак-

терных для комбинационной логики. В первой главе описываются основные поло-

жения булевой алгебры. Гл. 2 посвящена использованию карт Карно и методам

минимизации булевых функций. Хотя методы минимизации теряют свое значение

из-за появления схем со средним уровнем интеграции, автору кажется, что для

читателя будет более чем полезным развить собственные навыки работы со схемами.

Гл. 3 посвящена использованию элементов ИЛИ — НЕ и И — НЕ. В настоящее

время большинство интегральных схем с малым уровнем интеграции проектируется

с помощью элементов И — НЕ и ИЛИ — НЕ, а не на элементах И, ИЛИ и НЕ.

Поэтому в гл. 3 описана реализация булевых функций на основе именно этих эле-

ментов. В гл. 4 ставится и решается ряд проблем, обычно возникающих при проек-

тировании комбинационных схем.

Главы, начиная с пятой, связаны с проектированием последовательных схем.

В гл. 5 описываются свойства и приводятся характеристические уравнения триг-

геров различных типов. Материал этой главы в тесной связи с материалом предыду-

щих глав используется для разработки методов проектирования в гл. 6—9. Гл. 6

и 7 посвящены проектированию синхронных и асинхронных счетчиков на основе

дискретных триггеров и сдвиговых регистров. В гл. 8 анализируются синхронные

последовательные схемы и предлагается универсальная процедура их проектирова-

ния. Гл. 9 посвящена проектированию асинхронных логических схем и реализации

их с помощью схем последовательного действия, построенных на элементах И — НЕ.

В гл. 10 исследуются свойства ряда схем со средним уровнем интеграции и по-

казывается, как они могут быть использованы при проектировании комбинационных

и последовательных устройств. В гл. И описываются условия возникновения си-

туаций статического и динамического риска в комбинационных схемах и ситуаций

риска в последовательных схемах. В гл. 12 показано, что микропроцессор является

ничем иным, как довольно сложным синхронным устройством последовательного

действия.

В заключение хочу поблагодарить всех, кто помогал мне при подготовке этой

книги. Прежде всего выражаю признательность проф. Д. Зиссосу из университета

Калгари, привившему мне интерес к проектированию цифровых логических уст-

ройств. Затем хочу поблагодарить студентов, с чьей помощью мне удалось подгото-

вить материал, который лег в основу этой книги. Наконец, благодарю жену за

перепечатку рукописи и остальных членов семьи за доброжелательное отношение

к моей работе.

1. БУЛЕВА АЛГЕБРА

1.1. Введение

Как правило, в цифровых системах используются два уровня

напряжения электрических сигналов, например, 5 и О В. Электри-

ческие устройства, применяемые в таких системах, обычно рассчи-

таны только на эти два уровня напряжения. Нужное напряжение

обеспечивается источниками питания. Так, биполярный транзи-

стор, не проводящий ток в системе, обеспечивающей напряжение 5 В,

поддерживает между коллектором и эмиттером напряжение около

5 В. Однако, когда транзистор открывается и начинает проводить

ток, при подходящем выборе нагрузки можно считать, что напря-

жение между коллектором и эмиттером приблизительно равно 0.

Следовательно, цифровая система может быть описана как двоич-

>ная, и двум используемым уровням напряжения можно поставить

в соответствие двоичные значения 0 и 1. Два состояния, определен-

ные таким способом, можно интерпретировать логически как наличие

и отсутствие определенного условия.

В прошлом столетии английский священник Дж. Буль разрабо-

тал специальную алгебру, которая оказалась очень удобной для

представления ситуации, описанной выше. Впоследствии эта ветвь

математики получила название булевой алгебры — дискретной ал-

гебры, которая оперирует с переменными, принимающими только

два значения: 0 или 1. В ней существует множество правил и ряд

теорем, которые дают возможность оперировать булевыми выраже-

ниями.

Знание булевой алгебры необходимо для выполнения любой

работы, связанной с проектированием цифровых систем. В этой

главе будут рассмотрены правила и даны формулировки теорем бу-

левой алгебры. Ясное понимание принципов, лежащих в ее основе,

позволит применять алгебраический подход для решения задач про-

ектирования, и поэтому исключительно важно для каждого, кто

предполагает заниматься проектированием цифровых систем.

1.2. Логика переключателя

Рассмотрим переключатель, показанный на рис. 1.1, а. Этот

переключатель связывает между собой две точки: Р и Q. Состояние

переключателя может быть выражено с помощью булевой перемен-

ной А, которая может принимать два значения 0 и 1. Если переклю-

чатель разомкнут, то Л = 0, а если замкнут, то А = 1. Состояние

соединения PQ может быть выражено с помощью булевой перемен-

р ___ /1 о

о ........-о л о---------°

а)

Переключатель

разомкнут

Переключатель

замкнут

б)

Рис. 1.1. Переключатель:

а — простейшая переключательная контактная схема; б — таблица истинности

ной Д которая принимает одно из двух значений: 0 или 1. Если связи

между точками Р и Q нет, то f = 0, если есть — f = 1. Эти резуль-

таты сведены в таблицу (рис. 1.1, б). Такого рода таблицы называются

таблицами истинности. При просмотре таблицы, изображенной на

рис. 1.1, б, ясно, что

f = A.

Уравнения такого типа называются булевыми, а переменные f и А —

булевыми или двоичными переменными, так как они могут принимать

только два значения: 0 или 1.

1.3. Функция И

Два переключателя х и у соединены последовательно и связы-

вают точки Р и Q (рис. 1.2, а). Пусть состояния переключателей вы-

ражаются с помощью двух булевых переменных А и В. Если переклю-

чатель х разомкнут, то А = 0, если замкнут, то Л = 1. Аналогично,

В = 0 или В = 1 в зависимости от того, разомкнут или замкнут

переключатель у. Как и в случае одного переключателя, состояние

соединения PQ выражается с помощью булевой переменной f, зна-

чение которой зависит от наличия связи между точками Р и Q.

Существует четыре возможные комбинации значений перемен-

ных А и В. Они сведены в таблицу истинности, приведенную на

рис. 1.2, б. Например, если переключатели х и у разомкнуты, то

А = О, В = 0, и связи между точками Р и Q нет. Следовательно,

f == 0. С другой стороны, если х и у замкнуты, то Л = 1, В = 1

и, следовательно, f == 1.

Рис. 1.2. Функция И:

а — переключательная контактная схема, реализующая функцию И; б — таблица истин-

ности функции И; в — правила двоичного и булевого умножения (прав.: Ы =1)

Рис. 1.3. Условное обозначение элемента И

f= Ав

Таблица истинности, изображенная на рис. 1.2, б, является таб-

лицей истинности функции И. Ее иногда называют функцией буле-

вого умножения и алгебраически записывают в виде

f = А-В,

где «точка», интерпретируется как И. Обычно точку опускают, и

уравнение записывают в виде

f = АВ.

Правила булевого умножения тождественны правилам двоичного

умножения. Они приведены на рис. 1.2, в.

В цифровых системах функция И реализуется с помощью элек-

тронной схемы, называемой элементом И. На рис. 1.3 показано ус-

ловное обозначение элемента И. На выходе этого элемента получаем

логическую «1» только в том случае, если значениями его двух вхо-

дов являются логические «1». Для всех других комбинаций входов

значением функции f является логический «О».

1.4. Функция ИЛИ

На рис. 1.4, а два переключателя х и у соединены параллельно

и связывают точки Р и Q. Состояния переключателей и соедине-

ния PQ выражаются с помощью булевых переменных А, В и f соот-

ветственно. На рис. 1.4, б показана таблица истинности этой схемы.

Если оба переключателя х и у разомкнуты, то А — О, В = 0 и ясно,

что связи между точками Р и Q нет; следовательно, f = 0. С другой

стороны, если переключатель х замкнут, а у разомкнут, то Л = 1,

В = 0, и связь между точками Р и Q осуществляется с помощью

переключателя х; следовательно, f — 1.

Таблица, изображенная на рис. 1.4, б, является таблицей истин-

ности функции ИЛИ. Функцию ИЛИ иногда называют функцией

булевого сложения. Анализ таблицы истинности показывает, что

между точками Р и Q существует связь, если переключатель х замк-

нут или переключатель у замкнут или оба переключателя замкнуты.

0+0=0 0+0=0

0 + 1 = 1 0 + 1=1

1 +0 = 1 1+0 = 1

1+1=1 1 + 1 =0 Перенос 1

булево Двоичное

сложение сложение

Рис. 1,4. Функция ИЛИ:

И)

а — переключательная контактная схема, реализующая функцию ИЛИ; б — таблица истин-

ности функции ИЛИ; в правила двоичного и булевого сложения

4

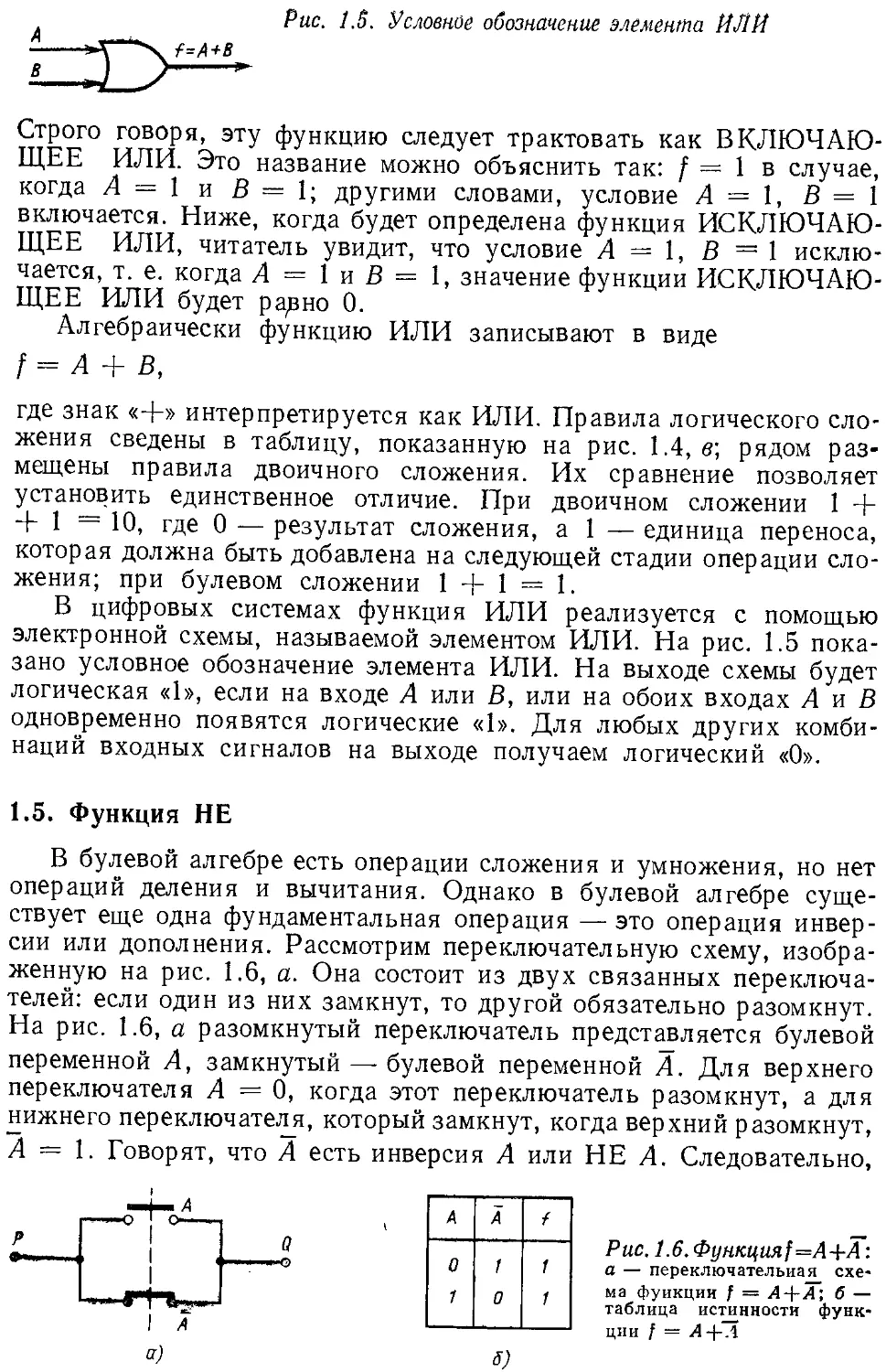

Рис. 1.6. Условное обозначение элемента ИЛИ

В

f-A+B

Строго говоря, эту функцию следует трактовать как ВКЛЮЧАЮ-

ЩЕЕ ИЛИ. Это название можно объяснить так: f = 1 в случае,

когда А = 1 и В = 1; другими словами, условие А = 1, В = 1

включается. Ниже, когда будет определена функция ИСКЛЮЧАЮ-

ЩЕЕ ИЛИ, читатель увидит, что условие А = 1, В — 1 исклю-

чается, т. е. когда А = 1 и В = 1, значение функции ИСКЛЮЧАЮ-

ЩЕЕ ИЛИ будет ра^но 0.

Алгебраически функцию ИЛИ записывают в виде

f = А + В,

где знак «+» интерпретируется как ИЛИ. Правила логического сло-

жения сведены в таблицу, показанную на рис. 1.4, в; рядом раз-

мещены правила двоичного сложения. Их сравнение позволяет

установить единственное отличие. При двоичном сложении 1 +

+ 1 — 10, где 0 — результат сложения, а 1 — единица переноса,

которая должна быть добавлена на следующей стадии операции сло-

жения; при булевом сложении 1 + 1 = 1.

В цифровых системах функция ИЛИ реализуется с помощью

электронной схемы, называемой элементом ИЛИ. На рис. 1.5 пока-

зано условное обозначение элемента ИЛИ. На выходе схемы будет

логическая «1», если на входе А или В, или на обоих входах А и В

одновременно появятся логические «1». Для любых других комби-

наций входных сигналов на выходе получаем логический «0».

1.5. Функция НЕ

В булевой алгебре есть операции сложения и умножения, но нет

операций деления и вычитания. Однако в булевой алгебре суще-

ствует еще одна фундаментальная операция —это операция инвер-

сии или дополнения. Рассмотрим переключательную схему, изобра-

женную на рис. 1.6, а. Она состоит из двух связанных переключа-

телей: если один из них замкнут, то другой обязательно разомкнут.

На рис. 1.6, а разомкнутый переключатель представляется булевой

переменной А, замкнутый—-булевой переменной А. Для верхнего

переключателя А = 0, когда этот переключатель разомкнут, а для

нижнего переключателя, который замкнут, когда верхний разомкнут,

А = 1. Говорят, что А есть инверсия А или НЕ А. Следовательно,

А А

0 1 / 0 1 1

Рис. 1.6. Функция1=А+А:

а — переключательная схе-

ма функции f » Л4-Л; б —

таблица истинности функ-

ции f — Л+Д

Рис. 1-7. Функция f =

= А-А:

а — переключательная схе-

ма функции f = А А; б —

таблица истиииости функ-

ции f = А • А

черта над булевой переменной А означает инверсию (или отрица-

ние) переменной. _

Таблица истинности функции f = А + А приведена на

рис. 1.6, б. Когда А ~ 0 и А = 1, то f = 1; аналогично, когда А = 1

и А = 0, то f = 1. Это означает, что связь между точками сущест-

вует всегда и не имеет значения, какой переключатель — верхний или

нижний замкнут. Следовательно, уравнение для этой схемы выгля-

дит

А + А = 1;

это уравнение — алгебраическая запись теоремы дополнительности.

Уравнение, двойственное по отношению к любому булевому

уравнению, получается заменой каждого знака «+» на «» и заменой

всех 1 на 0 и наоборот. По отношению к вышеприведенному уравне-

нию эта процедура приводит к

А-А = 0.

Переключательная контактная схема, соответствующая этому урав-

нению, показана на рис. 1.7, а, а таблица истинности этой схемы —

на рис. 1.7, б.

Инвертор может быть реализован с помощью электронной схемы,

условное обозначание которой приведено на рис. 1.8. Если на входе

схемы логический «0», то на выходе логическая «1» и наоборот. Если

два инвертора связаны последовательно, как показано на рис. 1.9,

то вход второго инвертора А, а его выход — инверсия от А, которая

может быть записана как А. Однако очевидно, что двойная инвер-

сия приводит к тому, что на выходе второго инвертора тот же сигнал,

что и на входе первого, поэтому

А = А.

Рис. 1.8. Условное обозначение инвертора

Рис. 1.9. Схема, иллюстрирующая теорему двойного отрицания

1.6. Реализация булевых функций с помощью переключательных

и электронных схем

Теперь появилась возможность представлять булевы функ-

ции, используя переключательные и электронные схемы. При реа-

лизации булевых функций переключательными контактными схе-

мами знаку «+» соответствует пара параллельных ветвей, знаку

«•» — последовательное соединение переключателей, а знаку «—» —

замкнутый переключатель. Например, функция

f = АВ + ВС

может быть реализована на основе переключательных контактных

схем (рис. 1.10, а) и на основе электронных схем (рис. 1.10, б).

Более сложная булева функция, например,

f = А (В + С) + BD

может быть реализована так, как показано на рис. 1.11, а и 1.11, б.

1.7. Теорема идемпотентности

В теореме утверждается, что

А + А = А.

Ясно, что если А — 1, то уравнение приводят к виду

1 + 1 = 1.

Рис. 1.10. Функция, f ~ АВАгВС:

а — реализация функции f = ABA-ВС с помощью переключателей; б — реализация функ-

ции f = АВ—ВС с помощью логических элементов

Рис. 1.11. Реализация функции f = А (В + С) 4- BD:

а — с помощью переключательных схем; б — с помощью логических элементов

т

I

Рис. 1.12. Иллюстрация теоремы идемпотентности с помощью переключательных

схем:

а — реализация f — АЦ-А; б — реализация f = А-А

Если же А = 0, то

0 + 0 = 0.

Оба эти результата согласуются с правилами булевого сложения,

приведенными на рис. 1.4, в.

Существует двойственная форма теоремы идемпотентности. Она

может быть получена посредством применения правил, сформулиро-

ванных выше. Ее вид А-А = А.

Если А = 1, то выражение будет иметь вид

1-1 = 1.

Если же А = 0, то

0-0 = 0.

Два последних результата согласуются с правилами булевого ум-

ножения, приведенными на рис. 1.2, в.

Для иллюстрации теоремы на рис. 1.12 приведены две переключа-

тельные контактные схемы.

1.8. Теоремы объединения и пересечения

В этих теоремах утверждается, что

. А + 0 = А, ) .. А + 1 = 1, ]

а) ’ I и б) I

Л-1 = A j А-0 = 0. |

Представим читателю возможность самому доказать справедливость

этих теорем.

1.9. Теорема избыточности или поглощения

В этой теореме утверждается, что

А + АВ = А.

Ниже приведено одно из доказательств этого утверждения:

А + АВ = А-1 + АВ

= А (В + В) + АВ

= AB + AB + AB

= AB + ЛВ

= А (В + B)

= A.

Говорят, что функция f = Л-1 + AB выражена в виде суммы про-

изведений (конъюнкций) или в дизъюнктивной нормальной форме.

Например, терм АВ является конъюнкцией двух переменных А

и В и, следовательно, называется конъюнктивным термом.

Таким образом, в теореме утверждается, что в любой булевой

функции, которая выражена в дизъюнктивной нормальной форме,

конъюнкция, содержащая все переменные другой конъюнкции,

является лишней. Это позволяет удалять лишние конъюнкции.

Например, из функции

f = AD 4- ABD + ACD

могут быть удалены термы ABD и ACD, поскольку они содержат

обе переменные, присутствующие в AD. Тогда функция примет вид

f = AD.

На рис. 1.13 приведена иллюстрация теоремы с помощью пере-

ключательных контактных схем. Очевидно, что наличие связи

между точками Р и Q не зависит от того, замкнут или разомкнут

переключатель В: следовательно, переключатель В лишний. Уравне-

ние, двойственное по отношению к уравнению А = А + АВ,

имеет вид

А = А (Л + В).

Переключательная контактная схема, иллюстрирующая это соот-

ношение, приведена на рис. 1.14.

р ““ О

0—0

Рис. 1.13. Переключательные контактные схемы, иллюстрирующие теорему по-

глощения А = А +ЛВ

Рис. 1.14. Иллюстрация двойственной формы теоремы поглощена : с помощью

переключательных схем

1.10. Определение дополнения функции

Дополнение булева выражения может быть Получено заменой

переменной ее дополнением в соответствующем двойственном выра-

жении. Например, для f = А + ВС двойственная форма имеет вид

fd = А (В + С),

а дополнение или инверсия функции

7= А (В + С).

Что это действительно дополнение функции f, может быть подтвер-

ждено с помощью таблицы истинности, изображенной на рис. 1.15.

Просмотр столбцов 9 и 10 этой таблицы показывает, что А (В + С)

является дополнением А + ВС. Две переключательные контактные

схемы, соответствующие дополняющим друг друга функциям, изобра-

жены на рис. 1.16.

Теперь рассмотрим базисные функции И или ИЛИ. Функция,

двойственная по отношению к функции f = АВ,

fd = A + В.

Дополнение функции получают заменой переменных их дополне-

ниями в двойственной форме

f = А + В.

Рис±1.15. Таблица истинности, подтверждающая, что f~

= А (В -|- С) является инверсией f = А + ВС

Рис. 1.16. Дополняющие друг друга схемы

f=A(B+C)

Рис. 1.17. Дополнения функций И и ИЛИ:

а — дополнение функции И; б — дополнение функции ИЛИ

Аналогично, функцию, двойственную по отношению к f = А + В,

определяют как

fd = АВ,

и дополнение функции f имеет вид

f = АВ.

Таким образом дополнение функции И — это функция ИЛИ, опе-

рандами которой являются дополнения переменных, присутствую-

щих в И; и наоборот, дополнение функции ИЛИ — это функция И,

операндами которой являются дополнения переменных, присутствую-

щих в ИЛИ. Процедура дополнения функций И и ИЛИ иллюстри-

руется с помощью электронных схем (рис. 1.17).

Так как дополнением функции f = АВ является функция f =

= А + В и f'= АВ, то, следовательно,

АВ = А + В.

Аналогично, поскольку дополнение f = А + В задается в виде

f = АВ и f = А + В, то, следовательно,

А + В = АВ.

Эти два выражения являются двумя формами теоремы де Моргана.

В более общем виде теорема де Моргана записывается

АВ ... N = А + В^--------1- N;

А + В ++ N = Л-В ... N.

1.11. Теоремы перестановки, сочетания и распределения

Кроме теорем, которые уже были рассмотрены ранее, существуют

также теоремы перестановки, сочетания и распределения. Алгебраи-

ческая запись этих теорем приводится ниже:

А + В = В + А,

АВ = ВА

(перестановка);

А + (В + С) = (Л + В) + С,

А (ВС) = (ЛВ) С

Л + ВС = (Л + В) (Л + С),

Л (В + С) = АВ + АС

(сочетание);

(распределение).

Наиболее полезной из всех этих теорем является первая форма

теоремы распределения. В частности, она необходима в процессе

минимизации булевых функций.

1.12. Теорема согласования

Если функция, например, / = АС + ВС содержит переменную С

в одном терме и ее дополнение в другом, то необязательную конъюнк-

цию или терм согласования формируют следующим образом: берут

булево произведение оставшихся переменных, в данном случае это

переменные А и В. Далее терм согласования может быть добавлен

к первоначальной функции f, что дает новую функцию

f = АС + ВС + АВ.

Значения /' равны соответствующим значениям f для всех воз-

можных комбинаций значений переменных А, В и С. Таблицы истин-

ности для f и f приведены на рис. 1.18. Просмотр столбцов таблицы

для f и показывает, что значения этих функций идентичны для

всех возможных значений переменных А, В и С.

Равенство f — f может быть доказано и алгебраически:

f — АС + ВС + АВ = АС + ВС + АВ (С + С) =

= АС + ВС + АВС + АВС =

= ДС(1 + В) + ВС(1 + Д),

однако 1 + А = 1 + В = 1 и, следовательно,

АС + ВС = f.

В связи с этим терм согласования может быть определен как

терм, присутствие которого в булевой функции не изменяет ее зна-

чения. Поэтому терм АВ в булевой функции [' = АС Д- ВС Д- АВ

является лишним. Однако термы согласования все-таки полезны,

так как введение их в булеву функцию может привести к исключе-

ние. 1.13. Доказательство теоремы согласования

с помощью таблицы истинности

Например, для

f = С + АВС

терм согласования имеет вид АВ. Добавляя его к /, получаем

f = С + АВС + АВ.

Применяя теорему поглощения, устанавливаем, что терм АВС

лишний и что его можно исключить. Тогда

f=C + AB.

Важно отметить, что длина терма АВ меньше длины удаленного

терма АВС.

Метод, заключающийся в определении термов согласования и

добавления их к функции без изменения ее значения, очень полезен

для проектировщиков цифровых систем. В последующих главах

будет показано, как этот метод может быть использован для устра-

нения ситуаций динамического риска в комбинационных схемах.

Упражнения*

У 1.1. Найти отрицание для каждого из следующих выражений:

a) А = А + ВС;

б) f2 = А (В + Q + BD (А + Q;

в) /3 = [АВ + С (А + DE)] [В + АС (Ё+ ВО)].

Результаты не упрощать.

У1 .2. Упростить выражения, используя метод, основанный на применении

термов согласования:

a) АС + BCD + АВС + ACD;

б) f2 = В х АВ + ACD + АС;

в) А = BCD + ABD + ABC + ABD + ACD.

У1.3. Составить таблицы истинности для следующих функций и из таблиц

истинности получить выражения для инверсных функций:

а) А = А + ВС;

б) А = Ас вс 4- АВ;

в) А = BD + АС + BD;

г) А = BD + А С + BD.

У1.4. Преобразовать следующие выражения, используя теорему де Моргана:

а) А = А + В + АВС-АС;

б) А = (АВ 4-ВС) + (ВС + АВ);

в) А = (АВ + ВС) (АС + АС).

* См. ответы в конце книги — Прим. ред.

У 1.5. Для следующих булевых функций нарисовать переключательные кон-

тактные схемы и реализовать их с помощью элементов И/ИЛИ:

а) Д= 4 + B(C+D);

б) h = И + В) (В + С) + (АВ + С);

в) /з = (Л + В + С) (А + D) + ВС + А (В + D) (С + D).

У1.6. Доказать следующие утверждения:

а) АВ + АВ = (Г+ В) (Л + В);

б) (АВ + С) В = АВС + АВС + АВС;

в) ВС + AD = (В + Л) (В + D) (Л + Q (С + £>);

г) АВ + ЛВС+ АВ = А.

2. КАРТЫ КАРНО И УПРОЩЕНИЕ ФУНКЦИЙ

2.1. Введение

Одна из задач проектировщика цифровых устройств, собираемых

из дискретных элементов, состоит в минимизации их числа, необхо-

димого для реализации булевой функции. Чем меньше количество

используемых логических элементов, тем ниже стоимость устрой-

ства. Упрощение может быть проведено и чисто алгебраическим пу-

тем, но это достаточно трудоемкий процесс, и к тому же проектиров-

щик не всегда может быть уверен, что простейшее решение действи-

тельно получено. Гораздо легче использовать способ упрощения,

основанный на составлении для булевых функций карт Карно, и

применения ряда простых правил для получения минимальной

формы. Этот метод очень удобен для функций, зависящих не более

чем от шести переменных. Для более сложных функций лучшие ре-

зультаты дают метод Квайна—Мак-Класки и итерационный метод

упрощения, основанный на использовании термов согласования.

Сейчас, когда существуют схемы со средним и большим уровнем

интеграции, задача минимизации функций не так важна, как прежде,

когда для реализации булевых функций использовались дискретные

элементы. Поскольку знание приемов минимизации позволит глубже

понять методы, используемые для преобразования булевых выра-

жений, они и предлагаются вниманию читателей.

2.2. Конъюнкции и дизъюнкции

Конъюнкцией (Р-термом) п переменных называется логическое

произведение всех п переменных, в котором любая переменная

может быть представлена также своим пополнением. В случае двух

переменных А и В существуют четыре возможные комбинации пере-

менных (рис. 2.1). К-аждой такой комбинации соответствует свой

Р-терм, который может быть получен следующим образом. Рассмо-

трим первую строку таблицы, представленной на рисунке. Для

нее А = О, В = 0 и, следовательно, АВ 1. Искомый Р-терм

формируем из таких значений переменных, которые делают зна-

чение Р-терма равным 1, следовательно, Ро = АВ. Оставшиеся три

Р-терма получаем тем же самым путем.

Дизъюнкцией (S-термом) п переменных называется логическая

сумма всех п переменных, в которой любая переменная может быть

представлена также своим дополнением. S-терм формируем на ос-

нове таких значений переменных, которые делают значение S-терма

равным нулю.

Так как Ро = АВ = 1 и Ро = АВ = 0 для А = 0 и В = О,

то Рп = Sn = А + В = 0 для А = 0 и В = 0. Таким образом мо-

гут быть получены еще три S-терма. Для трех переменных А, В

и С существует восемь возможных комбинаций переменных и, следо-

вательно, существует восемь Р-термов и восемь S-термов. В случае п

переменных существует 2п воз-

можных комбинаций значений

этих переменных и, следовательно,

существует 2'! Р-термов и 2" S-тер-

мов. Ясно, что число Р- и S-тер-

мов быстро растет с ростом п.

Сформулируем одно важное

свойство Р-термов: сумма всех Р-

термов равна единице, т. е.

2«-1

S Pi = 1.

i=0

А В Р-термы S-термы

0 0 Р = АВ So = А + В

0 1 Ру = АВ Sx = А + В

1 0 Рг = АВ S2 = А + В

1 1 Р3= АВ S3 ~ А + В

Рис. 2.1. Р- и S-термы двух перемен-

ных

Здесь используется операция булевого сложения. Уравнение, двой-

ственное по отношению к вышеприведенному, имеет вид

2«-1

Пй = о,

«=о

где операция умножения является булевым умножением.

В случае двух переменных логическую сумму всех Р-термов оп-

ределяем так:

S = АВ + АВ + АВ + АВ = А (В + В) + А (В + В) =

= А + А = 1.

Выражение, двойственное для суммы, имеет вид

(Я + В) (Д + В) (Д + В) (А + В) = 0

и представляет собой произведение всех возможных сумм термов

для двух переменных.

2.3. Канонические формы

Если булева функция записывается в виде суммы Р-термов или

произведения S-термов, то говорят, что она представлена в канони-

ческой форме. Так, функция

А = ДВС + АВС + АВС

представлена в канонической S—Р форме *, а функция

А = (А + В + С) (Я + В + С) (Я + В + Q

в канонической Р—S форме *.

* В советской научной литературе приняты термины: совершенная дизъюнк-

тивная нормальная форма и совершенная конъюнктивная нормальная форма. —

Роим- пер.

2.4. Булевы функции двух переменных

Количество булевых функций двух переменных ограничено.

Каждая булева функция состоит из определенного числа Р-термов,

например,

f = АВ + АВ

является булевой функцией двух переменных, содержащей два

из четырех возможных Р-термов. Все булевы функции двух перемен-

ных могут быть получены следующим образом. Обозначим присут-

ствие Р-терма в функции 1, а отсутствие 0. Например, если Р-терм

АВ присутствует в функции, то в соответствующей строке записы-

ваем 1, а если отсутствует — то 0. В случае, когда все четыре Р-

терма отсутствуют, столбец состоит из 0000 (рис. 2.2), и, следова-

тельно, булева функция будет иметь вид fn = 0.

В первую позицию каждого столбца можно записать либо 0,

либо 1. Во вторую позицию, соответствующую второй строке, то же.

Таким образом, существует четыре разных способа заполнения сим-

волами 0 и 1 первых двух строк. Для четырех строк число, способов

возрастает до 2' = 16. Все эти способы заполнения таблицы пока-

заны на рис. 2.2 и все 16 булевых функций двух переменных могут

быть немедленно получены. Они приведены на рис. 2.3.

Р-термы fo в В А В /в А А А А /10 /11 /12 /13 /14 /15

Ро= ЛВ 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

Рх= АВ 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

Р2= АВ 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

Р3= АВ 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

Рис. 2.2. Таблица, служащая для определения всех булевых функций двух

переменных

/о= о /1= АВ /а = АВ fa = А В=АВ Ноль И И (НЕ В) Тож- дество И (НЕ Л) О’** II II II II II 1 II Й 1 col । -4~ Со 11 f “ + 4^ II to tol Тождество ИСКЛЮ- ЧАЮЩЕЕ ИЛИ ИЛИ ИЛИ—НЕ Совпадение £ W w** w** Li' Ч1 °i II м £ tol tel HE ИЛИ (HE B) HE ИЛИ (HEA) И-НЕ Единица

Рис. 2.3. Шестнадцать булевых функций двух переменных

С увеличением числа переменных быстро растет и число булевых

функций. Для трех булевых переменных число возможных булевых

функций равно 28 = 256, для четырех 216 = 65536, для' п — 22п.

2.5. Карты Карно

Как показано выше, для двух булевых переменных существуют

четыре Р-терма. Эти термы могут быть удобно размещены на карте

(рис. 2.4). Карта представляет собой квадрат, разделенный на че-

тыре ячейки, по одной на каждый Р-терм. Строки карты связаны

с переменной А, столбцы — с переменной В. Следовательно, распо-

ложенная слева вверху ячейка соответствует Р-терму, являюще-

муся конъюнкцией А и В, т. е. АВ, а расположенная справа внизу

ячейка — терму АВ, помеченному Р3. Такого рода карта называется

картой Карно.

Карты Карно размечают различными способами. Во-первых,

каждая ячейка может содержать индекс Р-терма, которому она

ответствует (рис. 2.5, а). Например, в ячейку, расположенную

слева вверху, записывают 0, являющийся индексом Р-терма, соот-

ветствующего этой ячейке. Во-вторых, в ячейку карты можно запи-

сать двоичное представление индекса (рис. 2.5, б).

В случае трех переменных карта содержит восемь ячеек, по од-

ной для каждого Р-терма (рис. 2.6, а). Переменная А связывается

с двумя строками карты, а переменные В и С — с четырьмя столб-

цами. Существуют четыре комбинации возможных значений пере-

менных В и С и каждой комбинации соответствует отдельный стол-

бец карты. Карты заполняют таким образом, что два соседних столбца

всегда связаны либо с самой переменной, либо с ее отрицанием.

Анализируя рис. 2.6, а, можно заметить, что первые два столбца

связаны с В, второй и третий — с С, а третий и четвертый — с В.

По какой причине карта Карно заполняется именно таким образом,

будет видно в дальнейшем при изложении метода минимизации бу-

левых функций. Карта Карно для четырех переменных изображена

на рис. 2.6, б. Поскольку для четырех переменных существует 16

Р-термов, карта разделена на 16 ячеек. Каждая ячейка содержит

индекс того Р-терма, которому она соответствует.

£ $ 'Л

Рис. 2.4. Карта Карно для двух переменных

Рцс. 2.5. Разлучные способы заполнения карты Карно

\gc \C27 01

A \ 0 0 0 1 11 10 AB \ 00 01 1 1 10

Чо' к

ч»

a)

0 1 3 г

ч 5 7 6

12 13 15 14

8 3 11 10

£F(10)

EF(11)

Рас. 2.6. Карты Карно для:

a — трех переменных; б — четырех переменных: в — пяти переменных; г — шести перемен*

ных

В случае пяти переменных целесообразно использовать две 16-

ячеечные карты (рис. 2.6, в), а не одну 32-ячеечную. Карты, распо-

ложенные на рисунке, справа, соответствуют истинному значению

переменной Е, а карты, расположенные слева, — дополнению Е,

т. е. Е. В случае шести переменных для размещения 64 термов по-

требуется уже четыре 16-ячеечные карты. Эти четыре карты изобра-

жены на рис. 2.6, г. Каждая карта связана с одной из четырех воз-

можных комбинаций значений переменных Е и F.

2.6. Представление булевых функций с помощью карт Карно

Для функции двух переменных карта Карно содержит четыре

ячейки, по одной для каждого Р-терма. Изображение функции

f = АВ с помощью карты Карно показано на рис. 2.7, а. В первую

верхнюю ячейку карты записывают «1».

Рассмотрим теперь функцию двух переменных А и В, f = А.

Применяя теорему дополнительности, получаем

f = А (В + В) = АВ + АВ.

Эта функция изображена на рис. 2.7, б. Заполнены только нижние

ячейки карты. Следовательно, при представлении с помощью карты

Карно функции двух переменных, зависящей только от одной из них,

заполняют две соседние ячейки.

Так как для трех переменных существуют восемь Р-термов, для

функции трех переменных f (А, В, С) потребуется восьмиячеечная

карта Карно (рис. 2.8, а). На этой карте изображена функция f =

= АВС + АВС. Поскольку помеченные «1» ячейки карты не яв-

ляются соседними, два составляющих функцию Р-терма не могут

быть объединены и, следовательно, функция f не может быть упро-

щена.

На рис. 2.8, б изображена карта Карно, представляющая состоя-

щий из двух переменных терм ВС; на этой карте заполнены только

две ячейки. Анализ карты показывает, что терм ВС является логи-

ческой суммой Р-термов АВС и АВС, т. е.

f —~АВС + АВС = (А + А) ВС;

f = ВС.

Состоящий из одной переменной терм занимает четыре соседние

ячейки на карте, предназначенной для представления функций,

зависящих от трех переменных. Например, карта Карно для терма

f = С изображена на рис. 2.8, в. Кажется, что четыре ячейки, по-

меченные «1», не являются соседними. Однако, если свернуть карту

Рис. 2.7. Представление с по-

мощью карты Карно функции:

а - f = АВ; 6-/ = ЛВ+Ла' =

а)

6)

Рис. 2.8. Представление с по-

мощью карты Карно функции:

a — f = АВС+~АВС; б - f =

= ВС; в — f = С

Рис. 2.9. Представление с пол

a — f — TECD; б - f ~ ACD; в

в вертикальный цилиндр, то будет видно, что первый и последний

столбцы расположены рядом.

На карте Карно, рассчитанной на представление функций, за-

висящих от четырех переменных, Р-терм также занимает одну

ячейку (рис. 2.9, а). В связи с этим термы, состоящие из трех, двух

и одной переменной, при размещении на карте Карно займут две,

четыре и восемь ячеек, соответственно, как показано на рис. 2.9, б,

в, г. Анализ рис. 2.9, г показывает, что, во-первых, верхняя и ниж-

няя строки карты Карно могут считаться соседними и, во-вторых,

как и в случае с картой Карно для трех переменных, первый и пос-

ледний столбцы также могут считаться соседними.

2.7. Упрощение булевых функций

Процесс упрощения булевых функций с помощью карт Карно

основан на поиске соседних заполненных ячеек. Поясним это на

примере функции

f = 20, 1, 2, 3, 4, 6, 7, 8, 12, 13.

Здесь функция f представлена в виде логической суммы Р-термов,

каждый из которых заменен стоящим под знаком суммы индексом.

Изображение функции с помощью карты Карно показано на рис. 2.10.

На карте можно выделить четыре группы соседних ячеек: три группы

содержат по четыре ячейки и одна группа — две ячейки. Четыре

ячейки в верхней строке карты соответствуют терму АВ, четыре

ячейки первого столбца — терму CD, четыре ячейки справа вверху —

терму АС и, наконец, две соседние ячейки — терму АВС. Следова-

тельно, после упрощения функция примет вид

f = АВ + CD + АС + АВС.

Термы, входящие в состав упрощенной функции, обычно называют

главными импликантами.

Теперь стало ясным, почему переменные С и D, а также А и В

связаны со строками и столбцами именно таким способом, как опи-

сано выше. Используемый способ

гарантирует, что ячейки, связанные

с переменными С, С, D и D, всегда

принадлежат двум соседним столб-

цам, в то время как ячейки, свя-

занные с переменными А,А,ВнВ,

всегда принадлежат соседним стро-

кам. Если бы переменные были свя-

заны с ячейками карты в строгом

соответствии с числовым порядком,

определяемым двоичными кода-

ми 00, 01, 10 и 11, тогда ячейки,

связанные, например, с D, не

принадлежали бы соседним столб-

цам, и процесс упрощения не мог

функции f — АВ + CD + ДС-Ь

+ АВС

Puc_2.ll, Карта Карно_для функции f = BDE Ц- BDE + CDE + ВСЕ + ДВС+

+ ДСР + ACDE + ABDE

бы быть сведен к обнаружению соседних заполненных ячеек карты

Карно.

Упрощение функций, зависящих от пяти переменных, — не-

сколько более сложный процесс. Рассмотрим функцию

f = £0, 1, 2, 3, 4, 5, 10, 11, 13, 14, 15, 16, 20, 21, 24, 25,

26, 29, 30, 31.

Представляющая ее карта Карно изображена на рис. 2.11. Ниже

приведена процедура упрощения этой функции.

1. Сначала описанным ранее способом находим упрощенные

формы представления для двух функций fp и fE, соответствующих

левой и правой частям карты Карно на рис. 2.11:

f-g =~BDE + BDE + ACDE + АВСЁ-,

fE = CDE + BCE + ABDE + ABCE.

2. Второй шаг заключается в поиске таких главных импликант

двух функций и fE, которые можно объединить. В результате по-

лучим упрощенную форму логической суммы двух функций

?Ё + ?Е-

Например, АВСЕ — главная импликанта и АВСЕ — главная

импликанта fE. Эти две импликанты можно объединить, получив

в результате терм, состоящий из трех переменных АВС. Также

возможно дополнить функцию f-£ несущественной главной импли-

кантой ACDE. Объединив ее с главной импликантой ACDE функ-

ции fE, получим терм ACD. Этот процесс можно изобразить так:

fe = BDE + BDE + ACDE +

ABC

A CD

= CDE + BCE + ABDE +

Таким образом, упрощенная форма функции имеет вид

f = BDE + BDE + CDE + ВСЕ + ABC + ACD +

+ ACDE + ABDE.

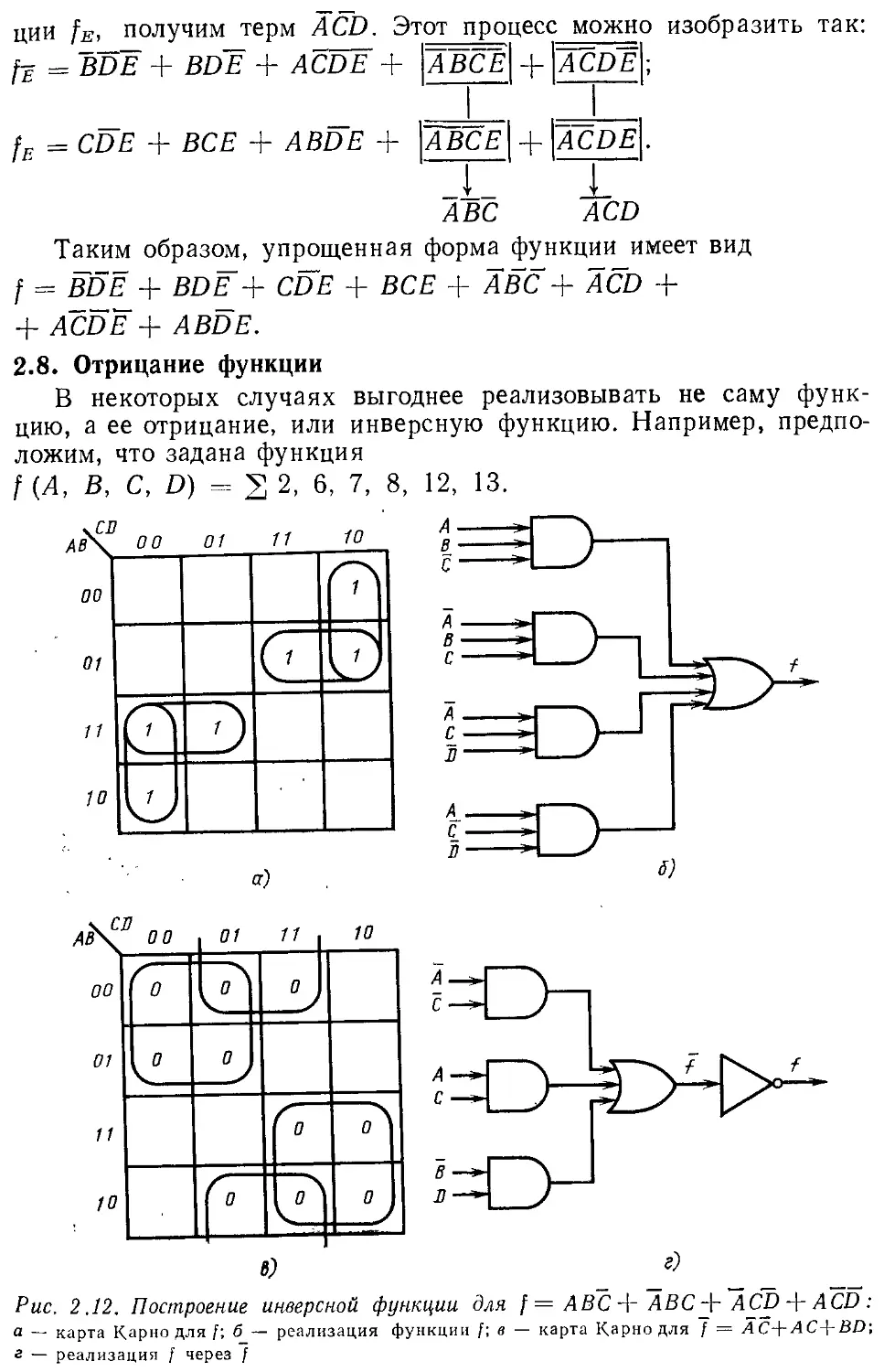

2.8. Отрицание функции

В некоторых случаях выгоднее реализовывать не саму функ-

цию, а ее отрицание, или инверсную функцию. Например, предпо-

ложим, что задана функция

f (Л, В, С, D) = 2 2, 6, 7, 8, 12, 13.

Рис. 2.12. Построение инверсной функции для f = АВС + АВС + ACD + ACD :

а — карта Карно для f; б_— реализация функции f; в — карта Карно для 7 = A C+AC-\-BD;

з — реализация f через f

Эта функция изображена на рис. 2.12, а. Ее упрощенная форма

имеет вид

f = АВС + АВС + ACD + ACD.

Для реализации этой функции потребуются четыре схемы И с тремя

входами и одна схема ИЛИ с четырьмя входами (рис. 2.12, б). Кроме

того, требуется 17 соединительных проводников.

Отрицание функции f может быть представлено так: незаполнен-

ные ячейки карты, показанной на рис. 2.12, а, заполняют 0. Резуль-

тат показан на рис. 2.12, в. Упрощенную форму функции f получаем

в результате анализа карты Карно, изображенной на рис. 2.12, в:

7 =АС + АС + BD.

Реализация f показана на рис. 2.12, г. Для того чтобы получить

первоначальную функцию, необходимо инвертировать сигнал на

выходе. Это делают с помощью инвертора. Таким образом, аппарат-

ное обеспечение включает три схемы И с двумя входами, одну

схему ИЛИ с тремя входами и один инвертор; кроме того, требуется

еще 11 соединительных проводников.

2.9. Термы, «не доставляющие беспокойства»

Следует отметить, что при решении некоторых логических задач

определенные комбинации переменных могут никогда не использо-

ваться. Например, для представления десятичных цифр часто ис-

пользуют код NBCD (рис. 2.13, а). Это четырехбитовый код с 16

возможными комбинациями, но только десять из них применяют на

практике. Оставшиеся шесть комбинаций, а именно 1010, 1011,

1100, 1101, 1110 и 1111, появиться не могут и, следовательно, могут

быть использованы для целей упрощения представления функций.

Такие термы называют «.термами, не доставляющими беспокойства».

Для распознавания цифр, представленных в NBCD-коде, исполь-

зуют декодирующее логическое устройство (рис. 2.13, б). Очевидно,

что для его реализации потребуется десять независимых схем, по

одной для каждой цифры.

Для определения функций, реализуемых каждой схемой, исполь-

зуют карту Карно, изображенную на рис. 2.13, в. На этой карте

термы, «не доставляющие беспокойства», помечают символами «d»,

а оставшиеся десять ячеек — десятичными цифрами, соответствую-

щими кодам ячеек. Например, ячейка, определяемая термом ~ABCD-

0000, помечается десятичной цифрой «0». Найти комбинации этой

ячейки с ячейками, помеченными «d», не удается. Следовательно,

0 = A BCD.

Аналогично, ячейка, помеченная десятичной цифрой 1, не может

быть объединена с хотя бы одной ячейкой, помеченной «d». Поэтому

1 = ABCD.

Рис. 2.13. Дешифратор для кода NBCD:

а — код NBCD-, б — структурная схема дешифратора; в — карта Карно, служащая для

определения логических функций, реализуемых дешифратором; г — реализация дешифратора

Однако ячейка, помеченная десятичной цифрой «2», может быть

объединена с ячейкой, помеченной «d», как это показано на рис. 2.13, в.

Следовательно,

2 = BCD.

Функции, соответствующие оставшимся десятичным цифрам, могут

быть найдены тем же самым путем. Приведем их:

3 = BCD; 5 = BCD- 7 = BCD; 9 = AD;

4 = BCD; 6 = BCD; 8 = AD.

Реализация всех найденных десяти функций показана на

рис. 2.13, г.

Это декодирующее логическое устройство является примером

комбинационной логической схемы. Любая комбинационная логи-

ческая схема характеризуется тем, что ее выход полностью опреде-

ляется сигналами на входах.

2.10. Представление и упрощение конъюнктивных нормальных

форм

Известно, что конъюнктивную нормальную форму непосредст-

венно представить на карте Карно нельзя, если найдено ее отрица-

ние, которое будет уже дизъюнктивной нормальной формой, то его

непосредственно представить на карте Карно все-таки можно. За-

полняя непомеченные ячейки этой карты, мы тем самым получим

отрицание инверсной функции, т. е. искомую функцию.

Например,

f = А + В

Функция, двойственная к /, имеет вид

Ь = А-В.

И, наконец, отрицание функции f есть

f = АВ.

Функция f может быть представлена с помощью карты Карно

обычным способом; только ячейку, соответствующую терму АВ,

помечают «0», поскольку строят карту Карно для инверсной функ-

ции. Эта функция изображена на рис. 2.14, а. Непомеченные ячейки

карты Карно соответствуют дополнению инверсной функции, т. е.

функции f = А + В. Карта! Карно'” функции f изображена на

рис. 2.14, б. Ячейки карты заполняют «1», поскольку речь идет

об искомой функции, которую необходимо представить с помощью

карты Карно.

Рассмотрим процесс заполнения карты Карно для дизъюнктив-

ных нормальных форм, зависящих от трех переменных. Пусть за-

Рис. 2.15. Карты Карно для функции:

a-f= АВС + ВС; б - f = (А + В + С) (В + С)

Функция, двойственная к f, имеет вид

fd = АВС + ВС,

а инверсная функция

J = АВС + ВС.

Эта функция изображена на рис. 2.15, а, а ее отрицание (т. е. иско-

мая функция) — на рис. 2.15, б.

Инверсная функция может быть упроще_на при использовании

методов, изложенных выше. Поскольку для f существуют две глав-

ные импликанты, она может быть представлена в виде

Т= ~АВ А-~ВС.

Проведя инвертирование этого выражения, перейдем снова к конъ-

юнктивной нормальной форме. Эта новая форма будет минимальной.

В данном случае двойственная форма инверсной функции будет

иметь вид

Id = (Л + В) (В + С),

а отрицание инверсной функции

f = (Л + В) (В + С).

Это и есть минимальная конъюнктивная нормальная форма выраже-

ния, задаваемого функцией

f = (Л + В + С) (В + С).

Упражнения

У2.1. Представить следующие булевы функции в канонической форме:

a) fi = АВ + С;

б) f2 = АВ+АС+ АВС;

в) f3 = В + CD + ABD + ABCD.

У2.2. Упростить следующие булевы функции, зависящие от трех переменных:

a) fi = Pi + Р2 + Pi, + Ре;

6) fi = Ро + Pi + Pi + Ps + Pi',

B) f»~ + P„ + e + Pt

У2.3. а. Выразить функцию трех переменных f = Ро + Pt в совершенной конъ-

юнктивной нормальной форме.

б. Представить функцию трех переменных f = SoSiS2SeSeS7 в совершенной дизъ-

юнктивной нормальной форме.

в. Определить отрицание функции / = Р3 + Ps + Ра + Р7 и выразить его в со-

вершенной дизъюнктивной нормальной форме.

У2.4. Минимизировать выражение, заданные в совершенной дизъюнктивной

нормальной форме:

a) ft (Д, В, С) = £0, 1, 3, 4, 6, 7;

б) h (Л, В, С, D) = 2°, 1, 2, 3, 7, 8, 9, 11, 12, 15;

в) h (Л, В, С, D) = ПО, 4, 5, 6, 7, 8, 9, 10;

г) ft (А, В, С, D, Е) = £°, 1, 3, 5, 6, 7, 8, 9, 10, 15, 16, 20, 21, 22, 23,

24, 25, 28, 29, 30, 31.

У2.5. Минимизировать следующие функции, используя, где это возможно,

термы, «не доставляющие беспокойства» ТНБ:

a) f (Д, В, С) = J 3, 5 + ТНБ (0, 7);

б) f (Д, В, Q = 2 1, 2, 3, 5, 6, 7, 10, И + ТНБ (9, 12, 15);

в) f (Д, В, С, О) = П 0, 4, 7, 11, 14 + ТНБ (6, 8, 9, 13);

г) f (Д, В, С, D) = 2 4. 5, 6, 7, 12, 14, 16, 20, 21, 24, 26, 27, 31 +

+ ТНБ (0, 11, 19, 22, 30).

У2.6. Определить минимальную дизъюнктивную нормальную форму следующих

функций:

a) f (Д, В, С) = 2 °- *> 2- 5, 7<

б) f (д, в, с, D) = 2°- 9> 10> и;

в) f (Д, В, С, D, Е)= 2 1- 2, 5, 6, 10, II, 14, 15, 16, 17, 20, 21;

г) f (Д, В, С, D) = 25, 7, 9, 10, 11 + ТНБ (2, 13, 15).

У2.7. Найти минимальную дизъюнктивную нормальную форму логического

произведения F=Ff F2 следующих пар функций:

a) Ft (Д, В, С, D) = 2 1, 3, 5, 7; F2 (А, В, С, D) = 2 2, 3, 6, 7;

б) Ft (Д, В, С, О) = 2 1. 3, 5, 6, 8, 10, 11, 12, 13;

F2(A, В, С, D) = 2 0, 3, 5, 8, 9, 11, 13, 15;

в) Ft (Д, В, С) = П 0, 3, 6, 7; F2 (Д, В, Q = П 1, 3, 7.

У2.8. Код XS3 (см. таблицу на стр. 36) используется для представления деся-

тичных цифр. Разработать для него декодирующее логическое устройство.

3. ЭЛЕМЕНТЫ И — НЕ И ИЛИ — НЕ

3.1. Введение

В предыдущих двух главах рассматривались только элементы И,

ИЛИ и НЕ. На практике многие логические схемы реализуются на

основе элементов И—НЕ и ИЛИ—НЕ, поскольку именно эти эле-

менты являются базисными для большинства серий ТТЛ-и КМОП-

логик. Правда, в этих сериях существуют элементы И и ИЛИ, но

их выбор существенно ограничен и они стоят дороже. Более того,

элементы И и ИЛИ имеют большее время задержки, поскольку со-

стоят из большего числа каскадов, чем элементы И—НЕ и ИЛИ—НЕ.

К тому же, элементы И и ИЛИ имеют более высокую мощность рас-

сеяния.

В связи с этим в данной главе речь пойдет об использовании эле-

ментов И—НЕ и ИЛИ—НЕ для реализации булевых функций.

В процессе проектирования логических устройств будут использо-

ваться именно эти элементы, пока не возникнут веские причины для

их замены.

3.2. Функция И — НЕ

Функция И—НЕ определяется

f = АВ.

Таблица истинности этой функции показана на рис. 3.1, а, а услов-

ное обозначение функции И—НЕ с двумя входами дано на

рис. 3.1, б. Анализ таблицы истинности показывает, что если на

одном или обоих входах элемента И—НЕ логический «О», то на его

выходе будет логическая «1». Сформулируем общее правило, харак-

теризующее работу элемента И—НЕ, имеющего произвольное число

входов: если хотя бы на одном входе элемента — логический «О»,

то на выходе — логическая «1».

Представление функции И—НЕ, зависящей от двух переменных,

с помощью карты Карно показано на рис. 3.1, в. Все ячейки карты,

исключая одну, соответствующую терму АВ, помечаются «1». Из

материала второй главы ясно, что эти три ячейки представляют до-

полнение терма АВ, т. е. АВ.

Анализ таблицы истинности показывает, что функция И—НЕ

может быть также представлена как

f = АВ + АВ + АВ = А + АВ = А + В.

Следовательно,

АВ = А + В.

Это равенство является одной из форм теоремы де Моргана.

Две строки таблицы истинности, обведенные штриховой линией,

характеризуют состояние элемента И—НЕ, когда на входе А

a)

Рис. 3.1. Функция И—НЕ:

а — таблица истинности функции И—НЕ; б — условное обозначение элемента И—НЕ;

в — карта Карно функции И — НЕ; г — использование элемента И—НЕ в качестве инвертора

постоянно присутствует логическая «1». Просмотр этих строк пока-

зывает, что если В = 0, то f = 1 и если В = 1, то f = 0. Другими

словами, сигнал на выходе является инверсией сигнала на входе.

Следовательно, элемент И—НЕ можно рассматривать как инвертор

в том случае, когда на всех входах, кроме одного, имеются логиче-

ские «1» (рис. 3.1, г).

3.3. Реализация функций И и ИЛИ с помощью элементов И—НЕ

Реализация функции И осуществляется достаточно просто с по-

мощью двух последовательно соединенных элементов И—НЕ; пер-

вый выполняет операцию И—НЕ, а второй используется как инвер-

тор (рис. 3.2).

На рис. 3.3, а изображена карта Карно для функции ИЛИ.

Просмотр карты показывает, что отрицанию функции ИЛИ соответ-

ствует одна ячейка, помеченная «0». Следовательно,

f = АВ,

откуда

f = ТЁ.

Анализ этого уравнения показывает, что функция ИЛИ может

быть выражена с помощью операции И—НЕ, выполняемой над

А ' , - ___

8 J у, Рис. 3.2. Реализация функции И с по-

»I у | у мощью элементов И—НЕ

f-A+B

V)

Рис. 3.3. Реализация функции ИЛИ с помощью элементов И—НЕ:

а — карта Карио для функции ИЛИ; б — схема реализации

отрицаниями переменных. На рис. 3.3, б представлена реали-

зация функции ИЛИ на основе элементов И—НЕ.

3.4. Реализация дизъюнктивных нормальных форм

с помощью элементов И — НЕ

Функция f = АВ + CD считается выраженной в дизъюнктив-

ной нормальной форме. На рис. 3.4, а показана реализация этой

функции с помощью элементов И/ИЛИ. На этом же рисунке выде-

лены два уровня расположения элементов в схеме: на первом уровне

размещен элемент ИЛИ, па втором — два элемента И. Данную схему

можно преобразовать в схему, построенную на элементах И—НЕ,

используя правила, изложенные в п. 3.3. Процедура преобразова-

ния показана на рис. 3.4, б. Первый блок, обведенный штриховыми

линиями, представляет собой два элемента И, а второй — элемент

ИЛИ. Можно заметить, что в обеих ветвях схемы присутствуют по

два одновходовых элемента И—НЕ, которые будут производить двой-

ную инверсию сигналов АВ и CD. Поэтому четыре элемента И—НЕ

являются лишними (на рис. 3.4, б они перечеркнуты). После удале-

ния этих элементов схема принимает вид, приведенный на рис. 3.4, в.

Из рассмотренного примера ясно, что схемы, построенные на эле-

ментах И/ИЛИ, очень просто (практически «один к одному») преобра-

зовать в схемы, реализуемые на элементах И—НЕ.

Даже функция более сложного вида, такая, как

f = (Л + BD) С + (С 4- D) (А 4- С) В,

может быть представлена в дизъюнктивной нормальной форме

f = PQ 4- SRT,

где Р = А 4- BD-, S = С + D; Q = С; R = А 4- С‘ Т = В.

ИроВень 2 Уровень 1

HAB+CD

Рис. 3.4. Реализация f = ABA-CD

с помощью элементов И—НЕ:

а — реализация f на элементах И/ИЛИ;

б — преобразование схемы на элемен-

тах И/ИЛИ в схему на элементах

И — НЕ; в — результирующая схема

Рис. 3.5. Реализация f = (А + BD) С + (С + D) (Д + С) В на элементах И—НЕ:

а — план реализации f; б — реализация С + D на элементах И—НЕ; в — реализация f

Реализация f — PQ + SRT показана на рис. 3.5, а. Для того чтобы

реализовать терм С + D на элементах И—НЕ, требуется одна схема

И—НЕ с входами, представляющими отрицания переменных, ко-

торые необходимо получить на выходе (рис. 3.5, б). На рис. 3.5, в

представлена полная схема, используемая для реализации искомой

функции.

Описанные методы представления булевых функций с помощью

элементов И—НЕ не обязательно приводят к минимальной реали-

зации. Однако иногда, используя процесс факторизации *, доста-

точно просто получить реализацию на элементах И—НЕ, состоя-

щую из меньшего числа элементов.

В качестве примера возьмем функцию

/ = АС + АВ + CD.

Непосредственная реализация этой функции приводит к схеме, изоб-

раженной на рис. 3.6, а, которая требует следующих элементов

И—НЕ: одного с тремя входами, трех с двумя входами и двух с од-

ним входом (на практике элементы И—НЕ, значения всех входов

которых равны логической «1», используются в качестве инверторов).

Однако эта же функция может быть представлена в виде

f = А (В + С) + CD

* Под факторизацией автор понимает процесс изменения записи булевой функ-

ции, основанный на выделении общих сомножителей. — Прим. пер.

Рис. 3.6. Три способа (а, б, в) реализации функции f= ДС+ВДЦ-CD на элемен-

тах И—НЕ

и реализована на элементах И—НЕ так, как показано на рис. 3.6, б.

Кроме того, функцию f можно представить и так:

f = С (Л + D) + ЛВ.

Тогда для реализации потребуется восемь элементов И—НЕ

(рис. 3.6, в).

Очевидно, что для реализации схемы, показанной на рис. 3.6, б,

потребуется меньше элементов И—НЕ, чем для схем, представлен-

ных на рис. 3.6, а и 3.6, в. Зиссос предложил формальный метод

определения минимальной по числу элементов И—НЕ реализации

при условии соблюдения ограничений, накладываемых на число

входов. Этот метод основан на использовании принципа слияния,

дающего возможность преобразовать выражения в скобках, напри-

мер (Л + В) (Л + С), к виду Л + ВС. В одних случаях слияние

позволяет уменьшить число элементов в схеме, в других же, наобо-

рот, приводит к их увеличению. Метод Зиссоса позволяет определить

влияние процесса слияния на количество элементов И—НЕ, необ-

ходимых для реализации схемы логической функции.

3.5. Функция ИЛИ — НЕ

Функция ИЛИ—НЕ определяется так:

f “ Л + В.

Таблица истинности этой функции показана на рис. 3.7, а, а услов-

ное обозначение элемента ИЛИ—НЕ с двумя входами — на

Рис. 3.7. Функция ИЛИ—НЕ:

а — таблица истинности функции ИЛИ —НЕ; б — условное обозначение элемента ИЛИ —НЕ;

в — карта Карно для функции^ИЛИ —НЕ; г —'использование^элемеита ИЛИ —НЕ в ка-

честве инвертора

рис. 3.7, б. Анализ таблицы истинности показывает, что если на од-

ном или на обоих входах логическая «1», то на выходе элемента будет

логический «О». На основании этого можно сформировать общее пра-

вило для элементов ИЛИ--НЕ, имеющих произвольное число вхо-

дов: если хотя бы на одном входе имеется логическая «1», то на вы-

ходе — логический «О». На рис. 3.7, в изображена карта Карно для

функции ИЛИ—НЕ, зависящей от двух переменных. Ее анализ позво-

ляет определить еще один способ представления функции ИЛИ—НЕ:

f = АВ - А + В.

Две обведенные штриховой линией строки таблицы истинности

характеризуют состояние элемента ИЛИ—НЕ с двумя входами,

когда на входе А присутствует логический «О». Анализ двух этих

строк показывает, что если В = 0, то f = 1 и если В — 1, то f = 0.

Следовательно, элемент ИЛИ—НЕ с одним активным входом дей-

ствует как инвертор (рис. 3.7, г).

Следует отметить, что для любых элементов надо стремиться не

оставлять свободными неиспользуемые входы. Неиспользуемые

входы элементов И—НЕ можно связать с логической «1», а элемен-

тов ИЛИ—НЕ — с логическим «0». Кроме того, неиспользуемые

входы элементов И—НЕ и ИЛИ—НЕ могут быть соединены с одним

из используемых входов. Эти два способа иллюстрируются на

рис. 3.8.

3.6. Реализация функций ИЛИ и И на основе элементов ИЛИ—НЕ

Реализация функции ИЛИ осуществляется путем последователь-

ного соединения двух элементов ИЛИ—НЕ, как это показано на

рис. 3.9, а. В этой схеме первый элемент выполняет операцию

Рис. 3.8. Способы нагружения неиспользуемых входов элементов:

а — И —НЕ; б - ИЛИ —НЕ

A

7

f*AtB-A8

Рис. 3.9. Реализация с помощью элементов ИЛИ—HE функции:

a — ИЛИ; б — И

ИЛИ—НЕ над двумя входными переменными Л и В, в то время как

второй элемент действует как инвертор.

Схема, реализующая функцию И, строится следующим образом.

Так как для ее реализации могут использоваться только элементы

ИЛИ—НЕ, на выходе последнего элемента ИЛИ—НЕ должно быть

значение функции / = АВ (рис. 3.9, б). Для того чтобы получить

такой выходной сигнал, входами элемента ИЛИ—НЕ должны быть А

и В, поскольку А + В — АВ. Завершая формирование схемы, перед

элементом ИЛИ—НЕ вводим два таких же элемента, выполняющих

операцию отрицания над переменными Л и В, соответственно.

Не встретится принципиальных трудностей при обобщении этого

правила на случай п переменных, т. е. на тот случай, когда на выходе

надо получить произведение п булевых переменных. Тогда у послед-

него элемента ИЛИ—НЕ должно быть и входов, по одному для каж-

дой переменной, содержащейся в произведении. Сигнал, подавае-

мый на каждый вход, будет отрицанием соответствующей перемен-

ной, т. е. если на выходе нужен сигнал С, то на входе должен быть

сигнал С.

3.7. Реализация конъюнктивных нормальных форм

с помощью элементов ИЛИ — НЕ

Функции, имеющие вид f = (Л -f- В) (С -f- D), называются двух-

уровневыми конъюнктивными нормальными формами. Реализация

функции f с помощью элементов И/ИЛИ приведена на рис. 3.10, а.

Применяя г равила, изложенные в предыдущем параграфе, преобра-

зуем эту схему в схему на элементах ИЛИ—НЕ (рис. 3.10, б). Ее

анализ показывает, что по два элемента ИЛИ—НЕ в каждой ветви

являются лишними, так как они производят двойную инверсию

сигнала. Эти элементы перечеркнуты на рис. 3.10, б. На рис. 3.10, в

изображена простейшая форма схемы на элементах ИЛИ—НЕ.

Таким образом, можно сделать вывод, что схемы на элементах И/ИЛИ

«один к одному» преобразовываются в схемы на элементах ИЛИ—НЕ.

3.8. Реализация дизъюнктивных нормальных форм

с помощью элементов ИЛИ — НЕ

Чтобы реализовать функцию, выраженную в дизъюнктивной

нормальной форме, на элементах ИЛИ—НЕ, ее сначала следует пре-

образовать в конъюнктивную нормальную форму. Например, пред-

6).

Рис. 3.10. Реализация функции f = (ЛЦ-В) (C+-D) с помощью элемен-

тов ИЛИ—НЕ:

а — реализация функции f на элементах И/ИЛИ; б — преобразование схемы на элемен-

тах И/ИЛИ в схему из элементов ИЛИ—НЕ; в — результирующая схема

Рис. 3.11. Реализация f— Y,0, 1, 3, 4, 5, 8, 12, 13, 15_на^элементах ИЛИ—НЕ:

а — карта Карно функции f; б — упрощение функции f" — CD -j- ABC + ABC; в — реали-

зация f (С + D) (Я J- В + С) (Д 4- В 4- D)

положим, что на элементах ИЛИ—НЕ требуется реализовать функ-

цию

f SO, 1, 3, 4, 5, 8, 12, 13, 15.

Первым шагом будет построение для этой функции карты Карно

(рис. 3.11, а). Как обычно, ячейки карты помечаем «1». Отрицание

функции можно получить, заполняя свободные ячейки карты Карно

«О», как показано на рис. 3.11, б.

Минимальная форма отрицания функции, получаемая в резуль-

тате анализа карты Карно (см. рис. 3.11, б), имеет вид

/ = CD + АВС + ABD.

Следовательно,

L = (С + D) (Д + В + С) (Л + В + D)

и _ _ _

/ = (С + D) (Л + В + С) (Л + В + D).

Это и есть минимальная конъюнктивная нормальная форма ис-

комой булевой функции. Ее схема, построенная на элементах ИЛИ—

НЕ, приведена на рис. 3.11, в.

3.9. Расширение элементов

Число входов элемента И—НЕ можно увеличить двумя спосо-

бами: с помощью схем И, реализуемых на элементах И—НЕ

(рис. 3.12, а), и за счет использования непосредственно самих эле-

ментов И (рис. 3.12, б). Для увеличения числа входов элемента

ИЛИ—НЕ применяют аналогичные методы (рис. 3.12, в).

Рис. 3.12. Методы увеличения числа входов элементов И—НЕ и ИЛИ—НЕ:

а — расширение входов элемента И — НЕ с помощью схем И, реализованных иа элементах

И — НЕ; б — расширение входов элемента И —НЕ с помощью элементов И; в — расширение

входов элемента ИЛИ —НЕ с помощью схем ИЛИ, реализованных иа элементах ИЛИ —НЕ

Возможность расширения числа входов зависит от типа элемента

и от принятых в данной серии ограничений. Например, в некоторых

сериях ТТЛ-логики допускается не более восьми входов для эле-

мента И—НЕ. Следовательно, применение первого метода позволит

расширить число входов элемента И—НЕ до 64. Но, с другой сто-

роны, элементы И этой же серии могут иметь не более четырех вхо-

дов, и это означает, что применение второго метода позволит про-

вести расширение только до 32 входов.

3.10. Смешанные схемы

На рис. 3.13, а показана схема, выполняющая операцию

И—ИЛИ—НЕ. Эту схему легко реализовать в ряде серий ТТЛ-ло-

1ики. Схема И—ИЛИ—НЕ двухуровневая: на первом уровне рас-

положен элемент ИЛИ—НЕ, который выполняет функцию опера-

ции логического умножения и отрицания; на втором уровне — два

элемента И. В случае необходимости схема И—ИЛИ—НЕ может ис-

полнять функции элемента ИЛИ—НЕ. Для этого надо просто умень-

шить число входов обоих элементов И до одного, как это показано

на рис. 3.13, б. С другой стороны, если на входы элементов И подать

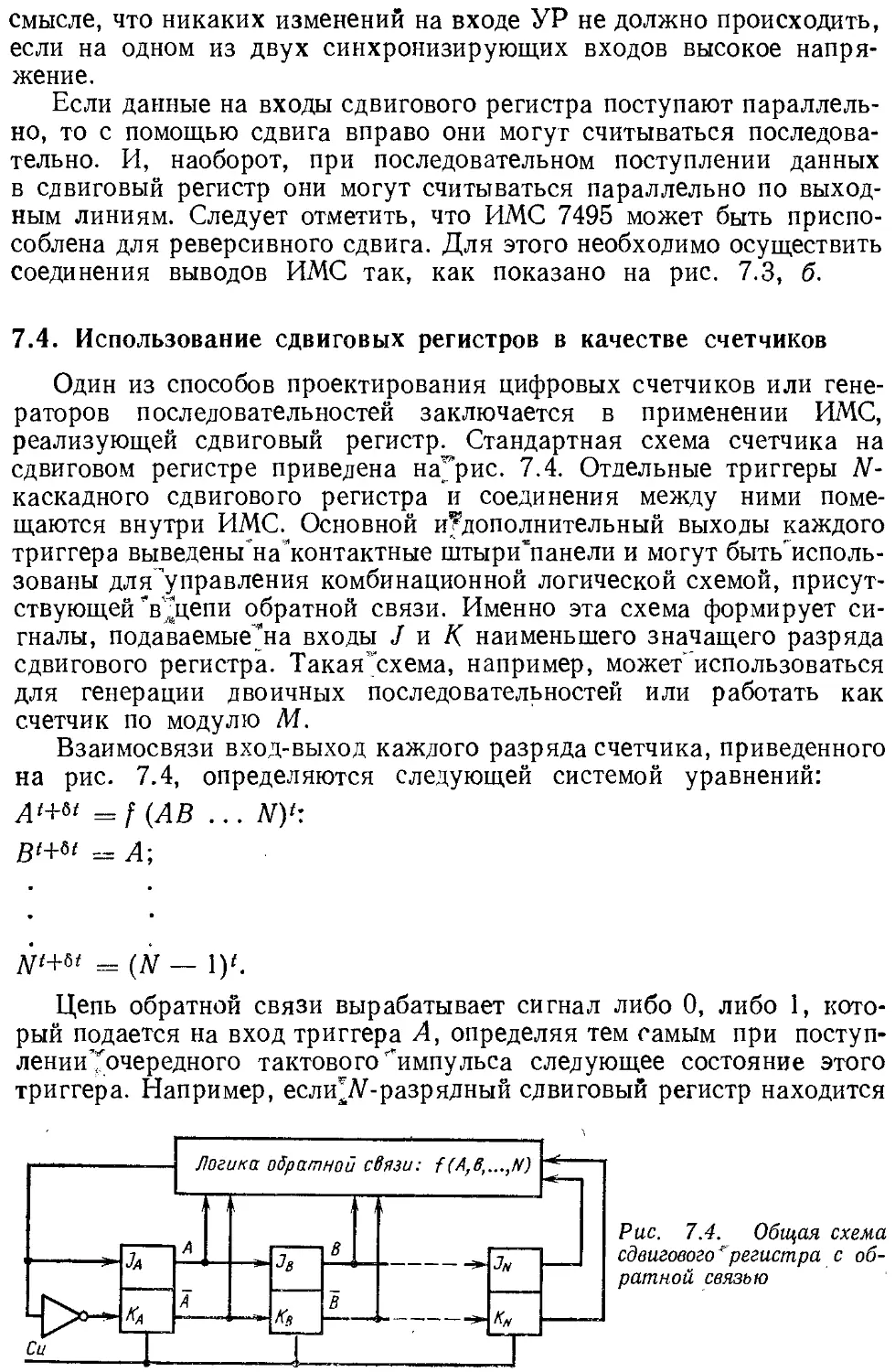

отрицания переменных, то схема И—ИЛИ—НЕ будет работать как

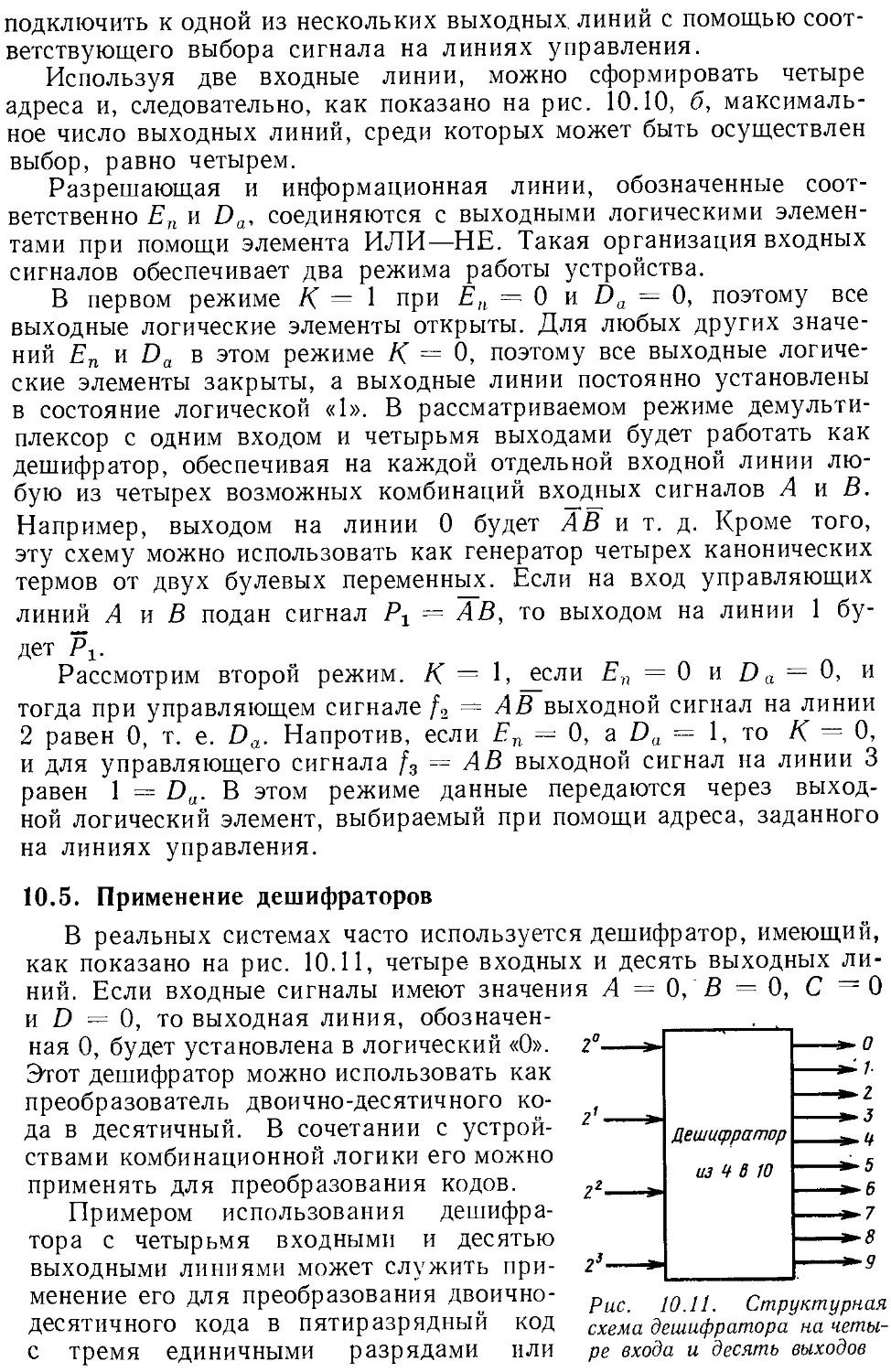

элемент И.